# SLB ECLIPSE<sup>®</sup> WITH AMD 3D V-CACHE<sup>™</sup> TECHNOLOGY RESERVOIR ENGINEERING SIMULATOR

Powered by 4th Gen AMD EPYC<sup>™</sup> Processors with AMD 3D V-Cache<sup>™</sup> technology

**June 2023**

### AT A GLANCE

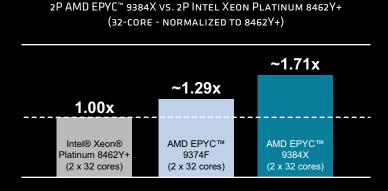

2P systems powered by 32-core 4th Gen AMD EPYC<sup>™</sup> processors with AMD 3D V-Cache<sup>™</sup> technology demonstrate outstanding per-core competitive performance uplifts on SLB ECLIPSE<sup>®</sup>.

### PERFORMANCE HIGHLIGHTS

A single 2P 32-core 4th Gen AMD EPYC 9384X system with AMD 3D V-Cache technology demonstrates a ~1.71 uplift vs. a single 2P 32-core Intel® Xeon® 8462Y+ system on SLB ECLIPSE.

### **KEY TAKEAWAYS**

A 2P server powered by 4th Gen AMD EPYC 9384X processors delivered a SLB ECLIPSE competitive performance uplift of ~1.71x compared to a 2P server powered by a Intel Xeon Platinum 8462Y+ (32-core) processors. SLB ECLIPSE boundedness can take advantage of the large AMD 3D V-Cache sizes.

4th Gen AMD EPYC 9004X processors with AMD 3D V-Cache technology are available in 1P and 2P configurations and feature:

- Up to 1,152MB L3 cache vs. 384MB in standard 4th Gen AMD EPYC processors.

- Up to 4 links of Gen 3 Infinity Fabric<sup>™</sup> at up to 32 Gbps.

- 12 memory channels that support up to 6TB of DDR5-4800 memory.

- Support for PCIe<sup>®</sup> Gen 5 at up to 32 Gbps.

- AVX-512 instruction support for enhanced HPC and ML performance.

- AMD Infinity Guard technology to defend your data.<sup>2</sup>

### **IN THIS BRIEF**

- AMD 3D V-Cache<sup>™</sup> Technology.....Page 2

- System Configuration.....Page 2

- Test Methodology.....

Page 3

| • | For Additional Information | Page 3 |

|---|----------------------------|--------|

| • | References                 | Page 3 |

## AMD 3D V-CACHE™ TECHNOLOGY

Some AMD EPYC 9004 Series Processors include AMD 3D V-Cache<sup>™</sup> die stacking technology that enables more efficient chiplet integration. AMD 3D Chiplet architecture stacks L3 cache tiles vertically to provide up to 96MB of L3 cache per die (and up to 1152 MB L3 Cache per socket) while still providing socket compatibility with standard AMD EPYC<sup>™</sup> 9004 Series Processor models.

AMD EPYC 9004 Series Processors with AMD 3D V-Cache technology employ industry-leading logic stacking based on copper-tocopper hybrid bonding "bumpless" chip-on-wafer process to enable over 200X the interconnect densities of current 2D technologies (and over 15X the interconnect densities of other 3D technologies using solder bumps),<sup>3,4</sup> which can translate to lower latency, higher bandwidth, and greater power and thermal efficiencies.

### SYSTEM CONFIGURATION

| AMD SYSTEM CONFIGURATION |                                                                  |                              |  |  |

|--------------------------|------------------------------------------------------------------|------------------------------|--|--|

| CPUs                     | 2 x AMD EPYC 9374F                                               | 2 x AMD EPYC 9384X           |  |  |

| Frequency: Base   Boost⁵ | 3.85 GHz   4.10 GHz (up to)                                      | 2.55 GHz   3.70 GHz (up to)  |  |  |

| Cores                    | 32 cores/socke                                                   | et (64 threads)              |  |  |

| L3 Cache                 | 256 MB per CPU                                                   | 768 MB per CPU               |  |  |

| Memory                   | 1.5 TB (24x) Dual-Rank<br>DDR5 4800 64 GB DIMMs 1 DPC            |                              |  |  |

| NIC                      | 25 Gb HDR Ethernet CCX512-A                                      | A ConnectX-5 (fw 16.35.2000) |  |  |

| InfiniBand               | 200 Gb ConnectX-6                                                | VPI (fw 20.35.2000)          |  |  |

| Storage: OS   Data       | Samsung MZQL21T9HCJR-00A07 1.92 TB                               |                              |  |  |

| BIOS Version             | 100                                                              | J7D                          |  |  |

| BIOS Settings            | SMT=OFF; NPS=4; Determinism=Power                                |                              |  |  |

| OS                       | RHEL 8.7 (kernel 4.18.                                           | 0-425.3.1.el8.x86_64)        |  |  |

| OS Settings              | amd_iommu=ON; iommu=pt; mitigation<br>THP=on; CPU governor=Perfo |                              |  |  |

Table 1: AMD system configurations

| INTEL SYSTEM CONFIGURATION |                                                                                                                                                                      |  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CPUs                       | 2x Intel Xeon Platinum 8462Y+                                                                                                                                        |  |  |  |

| Frequency: Base   Boost    | 2.40 GHz   4.10 GHz (up to)                                                                                                                                          |  |  |  |

| Cores                      | 32 cores per socket<br>(64 threads)                                                                                                                                  |  |  |  |

| L3 Cache                   | 60 MB per CPU                                                                                                                                                        |  |  |  |

| Memory                     | 1.0 TB (16x) Dual-Rank DDR5 4800 64 GB DIMMs 2 DPC                                                                                                                   |  |  |  |

| NIC                        | 25 Gb Ethernet CCX512-A ConnectX-5 (fw 16.35.2000)                                                                                                                   |  |  |  |

| InfiniBand                 | 200 Gb HDR ConnectX-6 VPI (fw 20.35.2000)                                                                                                                            |  |  |  |

| Storage: OS   Data         | Samsung MZQL21T9HCJR-00A07 1.92 TB                                                                                                                                   |  |  |  |

| BIOS Version               | ESE110Q-1.10                                                                                                                                                         |  |  |  |

| BIOS Settings              | Hyperthreading=Off, Profile = Maximum Performance                                                                                                                    |  |  |  |

| 05                         | RHEL 8.7 (kernel 4.18.0-425.3.1.el8.x86_64)                                                                                                                          |  |  |  |

| OS Settings                | processor.max_cstate=1; intel_idle.max_cstate=0; iommu=pt mitigations=off; clear caches;<br>NUMA Balancing=0; randomize_va_space 0; THP=0N; CPU Governor=Performance |  |  |  |

Table 2: Intel system configurations

### **TEST METHODOLOGY**

SLB's ECLIPSE industry-reference simulator provide a standard set of benchmarks that represent typical usage and cover a range of problem sizes that can be used to evaluate the performance of different platforms running ECLIPSE. The uplift is calculated as the ratio of the systems under test (*sut*) to the reference system (*ref*). In this Summary Brief, the Intel Xeon 8462Y is the *ref* and the 4th Gen AMD EPYC 9384X with 3D V-Cache is the *sut*. The total amount of variability between individual runs was < 1%. The systems tested were configured as shown in Tables 1 and 2, above.

## FOR ADDITIONAL INFORMATION

Please see the following additional resources for more information about 4th Gen AMD EPYC features, architecture, and available models:

• <u>AMD EPYC<sup>™</sup> 9004 Series Processors</u>

• <u>AMD EPYC<sup>™</sup> Products</u>

• <u>AMD EPYC<sup>™</sup> Tuning Guides</u>

### REFERENCES

- "Technical Computing" or "Technical Computing Workloads" as defined by AMD can include: electronic design automation, computational fluid dynamics, finite element analysis, seismic tomography, weather forecasting, quantum mechanics, climate research, molecular modeling, or similar workloads. GD-204

- 2. AMD Infinity Guard features vary by EPYC<sup>™</sup> Processor generations. Infinity Guard security features must be enabled by server OEMs and/or Cloud Service Providers to operate. Check with your OEM or provider to confirm support of these features. Learn more about Infinity Guard at <u>https://www.amd.com/en/technologies/infinity-guard</u>. GD-183

- Based on calculated areal density and based on bump pitch between AMD hybrid bond AMD 3D V-Cache stacked technology compared to AMD 2D chiplet technology and Intel 3D stacked micro-bump technology. EPYC-026

- 4. Based on AMD internal simulations and published Intel data on "Foveros" technology specifications. EPYC-027

- 5. Maximum boost for AMD EPYC processors is the maximum frequency achievable by any single core on the processor under normal operating conditions for server systems. EPYC-18

#### **AUTHORS**

Alvaro Fernandez and Ashok Manikonda contributed to this Performance Brief.

#### **RELATED LINKS**

- <u>SLB INTERSECT</u>\*

- <u>SLB ECLIPSE\*</u>

- <u>SLB Delfi Petrotechnical Suite</u>\*

- AMD EPYC<sup>™</sup> Processors

- AMD EPYC Technical Briefs

\*Links to third party sites are provided for convenience and unless explicitly stated, AMD is not responsible for the contents of such linked sites and no endorsement is implied.

### BOOST PERFORMANCE WITH AMD EPYC

AMD EPYC<sup>™</sup> processors are built to handle large scientific and engineering datasets - ideal for compute-intensive modeling and advanced analysis techniques. Leveraged by many of the world's largest, most scalable data centers and supercomputers, AMD EPYC<sup>™</sup> enables fast time-to-results for HPC.

#### "ZEN 4" CORE & SECURITY FEATURES

Support for up to:

- 96 physical cores, 192 threads

- 1152 MB of L3 cache per CPU

- 96 MB of L3 cache per CCD

- 6 TB of DDR5-4800 memory

- Up to 128 1P, up to 160 2P PCIe® Gen 5 lanes

Infinity Guard security features<sup>2</sup>

Secure Boot

• Encrypted memory with SME

#### **SLB ECLIPSE**

The ECLIPSE industry-reference simulator is a feature-rich, comprehensive reservoir. ECLIPSE offers a complete and robust set of numerical solutions for fast and accurate prediction of dynamic behavior for all types of reservoirs and development schemes thanks to its extensive capabilities, robustness, speed, parallel scalability, and superb platform coverage.

#### DISCLAIMERS

The information contained herein is for informational purposes only and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual proper ty rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.

#### **COPYRIGHT NOTICE**

©2023 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, EPYC, Infinity Fabric, AMD 3D V-Cache, and combinations thereof are trademarks of Advanced Micro Devices, Inc. INTERSECT software is a joint product collaboration of Chevron, TotalEnergies, and SLB. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.