# **TUNING GUIDE AMD EPYC 9004**

# **RDBMS**

Publication 57996

Revision 1.3

Issue Date June, 2023

#### © 2023 Advanced Micro Devices, Inc. All rights reserved.

The information contained herein is for informational purposes only and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.

#### **Trademarks**

AMD, the AMD Arrow logo, AMD EPYC, 3D V-Cache, and combinations thereof are trademarks of Advanced Micro Devices, Inc. MySQL is a trademark of Oracle and/or its affiliates. The MariaDB® mark is a trademark of MariaDB Corporation Ab. The mariadb.org, MariaDB Foundation and MariaDB Server marks are exclusively licensed to the MariaDB Foundation. Other product names and links to external sites used in this publication are for identification purposes only and may be trademarks of their respective companies.

\* Links to third party sites are provided for convenience and unless explicitly stated, AMD is not responsible for the contents of such linked sites and no endorsement is implied.

| Date       | Version | Changes                                                   |  |

|------------|---------|-----------------------------------------------------------|--|

| July, 2022 | 0.1     | Initial NDA partner release                               |  |

| Sep, 2022  | 0.2     | Jpdated BIOS information                                  |  |

| Nov, 2022  | 1.0     | Initial public version                                    |  |

| Dec, 2022  | 1.1     | Minor errata corrections                                  |  |

| Mar, 2023  | 1.2     | Added 97xx OPN and AMD 3D V-Cache™ technology information |  |

| Jun, 2023  | 1.3     | Second public release                                     |  |

#### **Audience**

This tuning guide is intended for a technical audience such as RDBMS application architects, production deployment, and performance engineering teams who have:

- A background in configuring servers.

- Administrator-level access to both the server management Interface (BMC) and the OS.

- Familiarity with both the BMC and OS-specific configuration, monitoring, and troubleshooting tools.

#### **Authors**

Muhammad Ashfaq and Sylvester Rajasekaran

Note: All of the settings described in this Tuning Guide apply to all AMD EPYC 9004 Series Processors of all core counts with or without AMD 3D V-Cache $^{\text{TM}}$  except where explicitly noted otherwise.

ii 57996 - 1.3

# **Table of Contents**

Note: If you are running Microsoft® SQL Server, then please see the Microsoft® SQL Server Tuning Guide for AMD EPYC™ 9004 Series Processors.

| Chapter 1 | Introduction                                             |          |

|-----------|----------------------------------------------------------|----------|

| 1.1       | CPU Selection Guidelines for RDBMS                       | 2        |

| Chautau 3 | AMD EDVEN COOK Carries Durantum                          | _        |

| Chapter 2 | AMD EPYC™ 9004 Series Processors                         |          |

| 2.1       | General Specifications                                   | 3        |

| 2.2       | Model-Specific Features                                  | 3        |

| 2.3       | Operating Systems                                        | 4        |

| 2.4       | Processor Layout                                         |          |

| 2.5       | "Zen 4" Core                                             |          |

| 2.6       | Core Complex (CCX)                                       |          |

| 2.7       | Core Complex Dies (CCDs)                                 |          |

| 2.8       | AMD 3D V-Cache™ Technology                               | 6        |

| 2.9       | I/O Die (Infinity Fabric™)                               |          |

| 2.10      | Memory and I/O                                           | 8        |

| 2.11      | Visualizing AMD EPYC 9004 Series Processors (Family 19h) | <u>C</u> |

|           | 2.11.1 Models 91xx-96xx ("Genoa")                        |          |

|           | 2.11.2 Models 97xx ("Bergamo")                           | 10       |

| 2.12      | NUMA Topology                                            | 10       |

|           | 2.12.1 NUMA Settings                                     |          |

| 2.13      | Dual-Socket Configurations                               | 12       |

| Chapter 3 | BIOS Defaults Summary                                    | 13       |

| 3.1       | Processor Core Settings                                  | 1/       |

| 3.2       | Power Efficiency Settings                                |          |

| 3.3       | NUMA and Memory Settings                                 |          |

| 3.4       | Infinity Fabric Settings                                 |          |

| 3.5       | PCIe, I/O, Security, and Virtualization Settings         |          |

| 3.6       | Higher-Level Settings                                    |          |

| 5.0       |                                                          |          |

| Chapter 4 | BIOS Settings for RDBMS                                  | 2        |

| 4.1       | BIOS Settings for Maximizing Performance                 |          |

| 4.2       | Memory                                                   |          |

| 4.3       | Network                                                  |          |

| 4.4       | Storage                                                  |          |

| Chapter 5  | MySQL - Additional Configuration Settings23                                                                                                                                                                                                                                                                                           |            |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| 5.1        | Tuning my.cnf Parameters                                                                                                                                                                                                                                                                                                              |            |  |  |

| Chapter 6  | MariaDB - Additional Configuration Settings                                                                                                                                                                                                                                                                                           | 25         |  |  |

| 6.1        | Tuning my.cnf Parameters                                                                                                                                                                                                                                                                                                              | 25         |  |  |

| Chapter 7  | Resources                                                                                                                                                                                                                                                                                                                             | 27         |  |  |

| 7.1<br>7.2 | Linux Tuning Considerations 7.1.1 Storage 7.1.1.1 MDADM Striped Partitions 7.1.1.2 Linux Logical Volume Manager (LVM) Striped Partitions 7.1.2 Linux Configuration 7.1.2.1 Linux Huge Pages 7.1.2.2 Required /etc/sysctl.conf Kernel Parameters 7.1.2.3 tuned-adm Profile 7.1.2.4 XFS Filesystem Mount Options For Additional Reading | 2728292931 |  |  |

| Chapter 8  | Processor Identification                                                                                                                                                                                                                                                                                                              |            |  |  |

| 8.1<br>8.2 | CPUID Instruction                                                                                                                                                                                                                                                                                                                     | 36         |  |  |

## Chapter

1

# Introduction

Relational databases such as MySQL and MariaDB can deliver high performance with proper configuration and tuning. This Tuning Guide gives best practices for:

- CPU selection

- · Memory sizing

- · BIOS tuning

- Tuning OS- and database-specific parameters

Note: Storage and networking also affect performance.

Please review the BIOS & Workload Tuning Guide for AMD EPYC™ 9004 Series Processors (available from AMD EPYC Tuning Guides) before tuning your system for specific databases and workloads.

If you are running Microsoft® SQL Server, then please see the *Microsoft® SQL Server Tuning Guide for AMD EPYC™ 9004 Series Processors* (available from AMD EPYC Tuning Guides).

57996 - 1.3

#### 1.1 CPU Selection Guidelines for RDBMS

4th Gen AMD EPYC™ processors deliver high IOPS and throughput for all databases. Selecting the right CPU is important for archiving optimal database application performance. Table 1-1 recommends CPUs based on database size, concurrent users, and performance requirements.

| Workload<br>Characteristics | Workload<br>Type                                                                                                                                                                                                                                                                                                             | Size/# of Users             | Cores | Processor              | Memory |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------|------------------------|--------|

| Small                       | DSS                                                                                                                                                                                                                                                                                                                          | • Up to 300 GB              | 8     | 1 x EPYC 16-core       | 128GB  |

|                             |                                                                                                                                                                                                                                                                                                                              | Up to 5 concurrent users    |       |                        |        |

| Medium                      | DSS                                                                                                                                                                                                                                                                                                                          | • Up to 300GB - 1TB         | 16    | 1 x EPYC 16-core       | 256GB  |

|                             |                                                                                                                                                                                                                                                                                                                              | Up to 10 concurrent users   |       | or<br>2 x EPYC 16-core |        |

| Large                       | DSS                                                                                                                                                                                                                                                                                                                          | Up to >1TB                  | 32    | 1x EPYC 32-core        | 512GB  |

|                             |                                                                                                                                                                                                                                                                                                                              | Up to 20 concurrent users   |       | or<br>2 x EPYC 16-core |        |

| Small                       | OLTP                                                                                                                                                                                                                                                                                                                         | • Up to 250GB               | 16    | 1 x EPYC 16-core       | 256GB  |

|                             |                                                                                                                                                                                                                                                                                                                              | Up to 50 concurrent users   |       | or<br>2 x EPYC 16-core |        |

| Medium                      | OLTP                                                                                                                                                                                                                                                                                                                         | • Up to 250GB-500GB         | 32    | 1 x EPYC 32-core       | 512GB  |

|                             |                                                                                                                                                                                                                                                                                                                              | Up to 100 con current users |       | or<br>2 x EPYC 16-core |        |

| Large                       | OLTP                                                                                                                                                                                                                                                                                                                         | Up to 500GB-1TBU            | 64    | 1 x EPYC 64-core       | 1-2TB  |

|                             |                                                                                                                                                                                                                                                                                                                              | Up to 200 con current users |       | or<br>2 x EPYC 32-core |        |

| Clouds                      | Each Cloud Service Provider (CSP) in your geographical region has different cloud instance/VM sizes to suit your choice of database workloads. Please refer to your selected CSP instance offerings to determine the instance with the best mix of vCPU cores, memory, storage, and networking for your particular workload. |                             |       |                        |        |

Table 1-1: Selecting the right 4th Gen AMD EPYC 9004 processors for various workloads

AMD recommends using 8, 16, or 32 vCPUs with 1:8 vCPU to memory ratio VMs with appropriate attached storage for optimal cloud laaS performance.

# Chapter

7

# AMD EPYC™ 9004 Series Processors

AMD EPYC™ 9004 Series Processors represent the fourth generation of AMD EPYC server-class processors. This generation of AMD EPYC processors feature AMD's latest "Zen 4" based compute cores, next-generation Infinity Fabric, next-generation memory & I/O technology, and use the new SP5 socket/packaging.

## 2.1 General Specifications

AMD EPYC 9004 Series Processors offer a variety of configurations with varying numbers of cores, Thermal Design Points (TDPs), frequencies, cache sizes, etc. that complement AMD's existing server portfolio with further improvements to performance, power efficiency, and value. Table 1-1 lists the features common to all AMD EPYC 9004 Series Processors.

| Common Features of all AMD EPYC 9004 Series Processors |                       |  |  |  |

|--------------------------------------------------------|-----------------------|--|--|--|

| Compute cores                                          | Zen4-based            |  |  |  |

| Core process technology                                | 5nm                   |  |  |  |

| Maximum cores per Core Complex (CCX)                   | 8                     |  |  |  |

| Max memory per socket                                  | 6 TB                  |  |  |  |

| Max # of memory channels                               | 12 DDR5               |  |  |  |

| Max memory speed                                       | 4800 MT/s DDR5        |  |  |  |

| Max lanes Compute eXpress Links                        | 64 lanes CXL 1.1+     |  |  |  |

| Max lanes Peripheral Component Interconnect            | 128 lanes PCle® Gen 5 |  |  |  |

Table 2-1: Common features of all AMD EPYC 9004 Series Processors

## 2.2 Model-Specific Features

Different models of 4th Gen AMD EPYC processors have different feature sets, as shown in Table 1-2.

| AMD EPYC 9004 Series Processor (Family 19h) Features by Model         |                   |                |  |  |

|-----------------------------------------------------------------------|-------------------|----------------|--|--|

| Codename                                                              | "Genoa"*          | "Bergamo"*     |  |  |

| Model #                                                               | 91xx-96xx         | 97xx           |  |  |

| Max number of Core Complex Dies (CCDs)                                | 12                | 8              |  |  |

| Number of Core Complexes (CCXs) per CCD                               | 1                 | 2              |  |  |

| Max number of cores (threads)                                         | 96 (192)          | 128 (256)      |  |  |

| Max L3 cache size (per CCX)                                           | 1,152 MB (96 MB)◆ | 256 MB (16 MB) |  |  |

| Max Processor Frequency   4.4 GHz◆◆   3.15 GHz                        |                   |                |  |  |

| Includes +AMD 3D V-Cache (9xx4X) and ++high-frequency (9xx4F) models. |                   |                |  |  |

Table 2-2: AMD EPYC 9004 Series Processors features by model

\*GD-122: The information contained herein is for informational purposes only and is subject to change without notice. Timelines, roadmaps, and/or product release dates shown herein and plans only and subject to change. "Genoa" and "Bergamo" are codenames for AMD architectures and are not product names.

#### 2.3 Operating Systems

AMD recommends using the latest available targeted OS version and updates. Please see <u>AMD EPYC™ Processors</u> <u>Minimum Operating System (OS) Versions</u> for detailed OS version information.

#### 2.4 Processor Layout

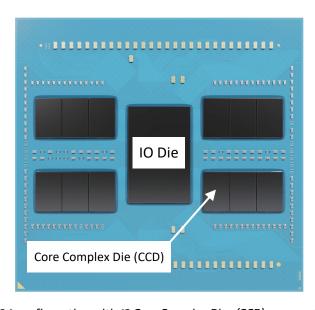

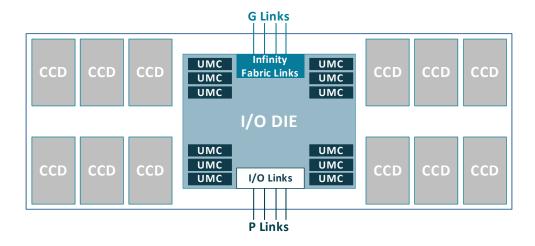

AMD EPYC 9004 Series Processors incorporate compute cores, memory controllers, I/O controllers, RAS (Reliability, Availability, and Serviceability), and security features into an integrated System on a Chip (SoC). The AMD EPYC 9004 Series Processor retains the proven Multi-Chip Module (MCM) Chiplet architecture of prior successful AMD EPYC processors while making further improvements to the SoC components.

The SoC includes the Core Complex Dies (CCDs), which contain Core Complexes (CCXs), which contain the "Zen 4"-based cores. The CCDs surround the central high-speed I/O Die (and interconnect via the Infinity Fabric). The following sections describe each of these components.

Figure 2-1: AMD EPYC 9004 configuration with 12 Core Complex Dies (CCD) surrounding a central I/O Die (IOD)

#### 2.5 "Zen 4" Core

AMD EPYC 9004 Series Processors are based on the new "Zen 4" compute core. The "Zen 4" core is manufactured using a 5nm process and is designed to provide an Instructions per Cycle (IPC) uplift and frequency improvements over prior generation "Zen" cores. Each core has a larger L2 cache and improved cache effectiveness over the prior generation. Each "Zen 4" core includes:

- Up to 32 KB of 8-way L1 I-cache and 32 KB of 8-way of L1 D-cache

- Up to a 1 MB private unified (Instruction/Data) L2 cache.

Each core supports Simultaneous Multithreading (SMT), which allows 2 separate hardware threads to run independently, sharing the corresponding core's L2 cache.

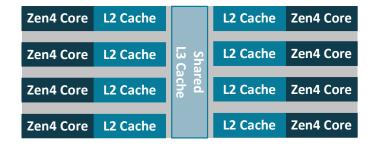

### 2.6 Core Complex (CCX)

Figure 2-2 shows a Core Complex (CCX) where up to eight "Zen 4"-based cores share a L3 or Last Level Cache (LLC). Enabling Simultaneous Multithreading (SMT) allows a single CCX to support up to 16 concurrent hardware threads.

Figure 2-2: Top view of 8 compute cores sharing an L3 cache (91xx-96xx models)

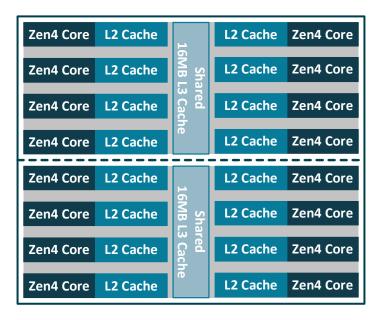

## 2.7 Core Complex Dies (CCDs)

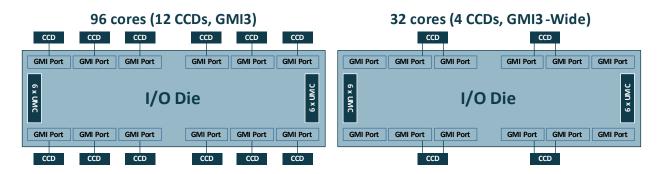

The Core Complex Die (CCD) in an AMD EPYC 9xx4 Series Processor may contain either one or two CCXs, depending on the processor (91xx-96xx "Genoa" vs. 97xx "Bergamo"), as shown in Figure 2-5.

Figure 2-3: 2 CCXs in a single 4th Gen AMD EPYC 97xx CCD

Each of the Core Complex Dies (CCDs) in a 97xx model AMD EPYC 9004 Series Processor contains two CCXs (Figure 2-5):

Table 2-3: CCXs per CCD by AMD EPYC model

You can disable cores in BIOS using one or both of the following approaches:

- Reduce the cores per L3 from 8 down to 7,6,5,4,3,2, or 1 while keeping the number of CCDs constant. This approach increases the effective cache per core ratio but reduces the number of cores sharing the cache.

- Reduce the number of active CCDs while keeping the cores per CCD constant. This approach maintains the advantages of cache sharing between the cores while maintaining the same cache per core ratio.

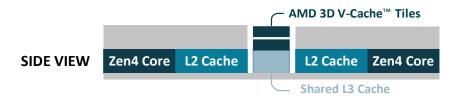

## 2.8 AMD 3D V-Cache™ Technology

AMD EPYC 9xx4X Series Processors include AMD 3D V-Cache™ die stacking technology that enables 97xx to achieve more efficient chiplet integration. AMD 3D Chiplet architecture stacks L3 cache tiles vertically to provide up to 96MB of L3 cache per die (and up to 1 GB L3 Cache per socket) while still providing socket compatibility with all AMD EPYC™ 9004 Series Processor models.

AMD EPYC 9004 Series Processors with AMD 3D V-Cache technology employ industry-leading logic stacking based on copper-to-copper hybrid bonding "bumpless" chip-on-wafer process to enable over 200X the interconnect densities of current 2D technologies (and over 15X the interconnect densities of other 3D technologies using solder bumps), which translates to lower latency, higher bandwidth, and greater power and thermal efficiencies.

Figure 2-4: Side view of vertically-stacked central L3 SRAM tiles

| AMD EPYC 9004 Series Processors | 9xx4  | 9004X<br>(with 3D V-Cache) |

|---------------------------------|-------|----------------------------|

| Max Shared L3 Cache per CCD     | 32 MB | 96 MB                      |

Table 2-4: L3 cache by processor model

Different OPNs also may have different numbers of cores within the CCX. However, for any given part, all CCXs will always contain the same number of cores.

#### 2.9 I/O Die (Infinity Fabric™)

The CCDs connect to memory, I/O, and each other through an updated I/O Die (IOD). This central AMD Infinity Fabric™ provides the data path and control support to interconnect CCXs, memory, and I/O. Each CCD connects to the IOD via a dedicated high-speed Global Memory Interconnect (GMI) link. The IOD helps maintain cache coherency and additionally provides the interface to extend the data fabric to a potential second processor via its xGMI, or G-links. AMD EPYC 9004 Series Processors support up to 4 xGMI (or G-links) with speeds up to 32Gbps. The IOD exposes DDR5 memory channels, PCIe® Gen5, CXL 1.1+, and Infinity Fabric links.

All dies (chiplets) interconnect with each other via AMD Infinity Fabric technology. Figure 2-6 (which corresponds to Figure 2-2, above) shows the layout of a 96-core AMD EPYC 9654 processor. The AMD EPYC 9654 has 12 CCDs, with each CCD connecting to the IOD via its own GMI connection.

Figure 2-5: AMD EPYC 9654 processor internals interconnect via AMD Infinity Fabric (12 CCD processor shown)

AMD also provides "wide" OPNs (e.g. AMD EPYC 9334) where each CCD connects to two GMI3 interfaces, thereby allowing double the Core-to-I/O die bandwidth.

Figure 2-6: Standard vs. Wide GMI links

The IOD provides twelve Unified Memory Controllers (UMCs) that support DDR5 memory. The IOD also presents 4 'Plinks' that the system OEM/designer can configure to support various I/O interfaces, such as PCIe Gen5, and/or CXL 1.1+.

> 7 57996 - 1.3

#### 2.10 Memory and I/O

Each UMC can support up to 2 DIMMs per channel (DPC) for a maximum of 24 DIMMs per socket. OEM server configurations may allow either 1 DIMM per channel or 2 DIMMs per channel. 4th Gen AMD EPYC processors can support up to 6TB of DDR5 memory per socket. Having additional and faster memory channels compared to previous generations of AMD EPYC processors provides additional memory bandwidth to feed high-core-count processors. Memory interleaving on 2, 4, 6, 8, 10, and 12 channels helps optimize for a variety of workloads and memory configurations.

Each processor may have a set of 4 P-links and 4 G-links. An OEM motherboard design can use a G-link to either connect to a second 4th Gen AMD EPYC processor or to provide additional PCIe Gen5 lanes. 4th Gen AMD EPYC processors support up to eight sets of x16-bit I/O lanes, that is, 128 lanes of high-speed PCIe Gen5 in single-socket platforms and up to 160 lanes in dual-socket platforms. Further, OEMs may either configure 32 of these 128 lanes as SATA lanes and/or configure 64 lanes as CXL 1.1+. In summary, these links can support:

- Up to 4 G-links of AMD Infinity Fabric connectivity for 2P designs.

- Up to 8 x16 bit or 128 lanes of PCIe Gen 5 connectivity to peripherals in 1P designs (and up to 160 lanes in 2-socket designs).

- Up to 64 lanes (4 P-links) that can be dedicated to Compute Express Link (CXL) 1.1+ connectivity to extended memory.

- Up to 32 I/O lanes that can be configured as SATA disk controllers.

#### 2.11 **Visualizing AMD EPYC 9004 Series Processors (Family 19h)**

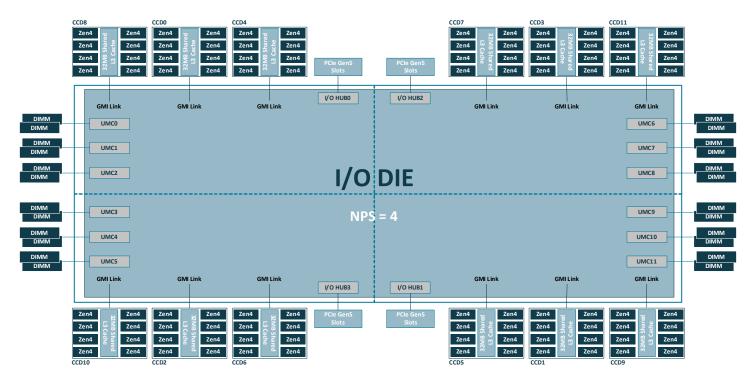

This section depicts AMD EPYC 9004 Series Processors that have been set up with four nodes per socket (NPS=4). Please see "NUMA Topology" on page 10 for more information about nodes.

#### Models 91xx-96xx ("Genoa") 2.11.1

4th Gen AMD EPYC 9004 processors with model numbers 91xx-96xx have up to 12 CCDs that each contain a single CCX, as shown below.

Figure 2-7: The AMD EPYC 9004 SoC consists of up to 12 CCDs and a central IOD for 91xx-96xx models, including "X" OPNs

57996 - 1.3 9

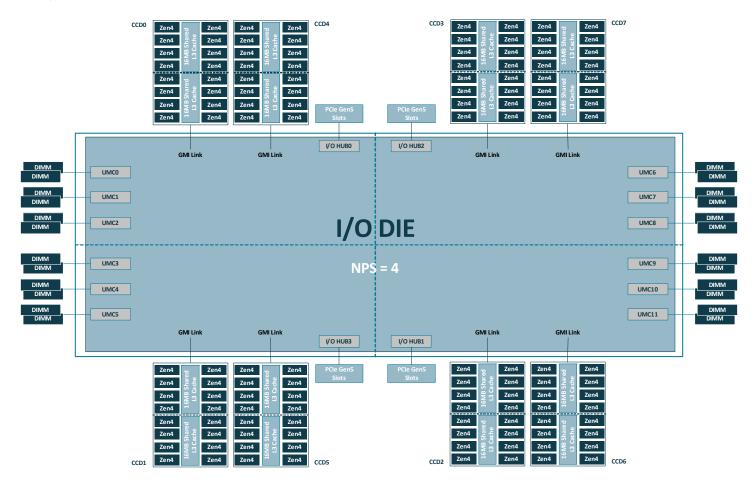

#### 2.11.2 Models 97xx ("Bergamo")

97xx 4th Gen AMD EPYC 9004 Series Processors with model numbers 97xx have up to 8 CCDs that each contain two CCXs, as shown below.

Figure 2-8: The AMD EPYC 9004 System on Chip (SoC) consists of up to 8 CCDs and a central IOD for 97xx models

### 2.12 NUMA Topology

AMD EPYC 9004 Series Processors use a Non-Uniform Memory Access (NUMA) architecture where different latencies may exist depending on the proximity of a processor core to memory and I/O controllers. Using resources within the same NUMA node provides uniform good performance, while using resources in differing nodes increases latencies.

#### 2.12.1 NUMA Settings

A user can adjust the system **NUMA Nodes Per Socket** (NPS) BIOS setting to optimize this NUMA topology for their specific operating environment and workload. For example, setting NPS=4 as shown in "Memory and I/O" on page 8 divides the processor into quadrants, where each quadrant has 3 CCDs, 3 UMCs, and 1 I/O Hub. The closest processor-memory I/O distance is between the cores, memory, and I/O peripherals within the same quadrant. The furthest distance is between a core and memory controller or IO hub in cross-diagonal quadrants (or the other processor in a 2P configuration). The locality of cores, memory, and IO hub/devices in a NUMA-based system is an important factor when tuning for performance.

The NPS setting also controls the interleave pattern of the memory channels within the NUMA Node. Each memory channel within a given NUMA node is interleaved. The number of channels interleaved decreases as the NPS setting gets more granular. For example:

- A setting of NPS=4 partitions the processor into four NUMA nodes per socket with each logical quadrant configured as its own NUMA domain. Memory is interleaved across the memory channels associated with each quadrant. PCIe devices will be local to one of the four processor NUMA domains, depending on the IOD quadrant that has the corresponding PCIe root complex for that device.

- A setting of NPS=2 configures each processor into two NUMA domains that groups half of the cores and half of the memory channels into one NUMA domain, and the remaining cores and memory channels into a second NUMA domain. Memory is interleaved across the six memory channels in each NUMA domain. PCIe devices will be local to one of the two NUMA nodes depending on the half that has the PCIe root complex for that device.

- A setting of NPS=1 indicates a single NUMA node per socket. This setting configures all memory channels on the processor into a single NUMA node. All processor cores, all attached memory, and all PCIe devices connected to the SoC are in that one NUMA node. Memory is interleaved across all memory channels on the processor into a single address space.

- A setting of NPS=0 indicates a single NUMA domain of the entire system (across both sockets in a two-socket configuration). This setting configures all memory channels on the system into a single NUMA node. Memory is interleaved across all memory channels on the system into a single address space. All processor cores across all sockets, all attached memory, and all PCIe devices connected to either processor are in that single NUMA domain.

You may also be able to further improve the performance of certain environments by using the LLC (L3 Cache) as NUMA BIOS setting to associate workloads to compute cores that all share a single LLC. Enabling this setting equates each shared L3 or CCX to a separate NUMA node, as a unique L3 cache per CCD. A single AMD EPYC 9004 Series Processor with 12 CCDs can have up to 12 NUMA nodes when this setting is enabled.

Thus, a single EPYC 9004 Series Processor may support a variety of NUMA configurations ranging from one to twelve NUMA nodes per socket.

Note: If software needs to understand NUMA topology or core enumeration, it is imperative to use documented Operating System (OS) APIs, well-defined interfaces, and commands. Do not rely on past assumptions about settings such as APICID or CCX ordering.

> 57996 - 1.3 11

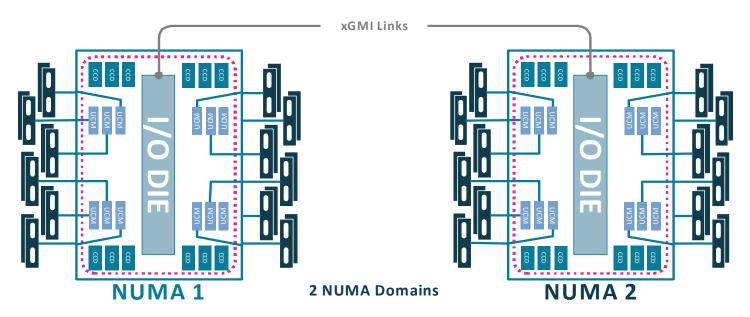

#### 2.13 Dual-Socket Configurations

AMD EPYC 9004 Series Processors support single- or dual-socket system configurations. Processors with a 'P' suffix in their name are optimized for single-socket configurations (see the "Processor Identification" chapter) only. Dual-socket configurations require both processors to be identical. You cannot use two different processor Ordering Part Numbers (OPNs) in a single dual-socket system.

Figure 2-9: Two EPYC 9004 Processors connect through 4 xGMI links (NPS1)

In dual-socket systems, two identical EPYC 9004 series SoCs are connected via their corresponding External Global Memory Interconnect [xGMI] links. This creates a high bandwidth, low latency interconnect between the two processors. System manufacturers can elect to use either 3 or 4 of these Infinity Fabric links depending upon I/O and bandwidth system design objectives.

The Infinity Fabric links utilize the same physical connections as the PCIe lanes on the system. Each link uses up to 16 PCIe lanes. A typical dual socket system will reconfigure 64 PCIe lanes (4 links) from each socket for Infinity Fabric connections. This leaves each socket with 64 remaining PCIe lanes, meaning that the system has a total of 128 PCIe lanes. In some cases, a system designer may want to expose more PCIe lanes for the system by reducing the number of Infinity Fabric G-Links from 4 to 3. In these cases, the designer may allocate up to 160 lanes for PCIe (80 per socket) by utilizing only 48 lanes per socket for Infinity Fabric links instead of 64.

A dual-socket system has a total of 24 memory channels, or 12 per socket. Different OPNs can be configured to support a variety of NUMA domains.

# Chapter

5

# **BIOS Defaults Summary**

This chapter provides high-level lists of the default AMD EPYC 9004 BIOS settings and their default values. Please see Chapter 4 of the BIOS & Workload Tuning Guide for AMD EPYC™ 9004 Series Processors (available from AMD EPYC Tuning Guides) for detailed descriptions. Later chapters in this Tuning Guide discuss the BIOS options as they relate to a specific workload or set of workloads.

Note: The default setting names and values described in this chapter are the AMD default names and values that serve as recommendations for OEMs. End users must confirm their OEM BIOS setting availability and options.

AMD strongly recommends that customers download and install the latest BIOS update for your AMD EPYC 9004 Series Processor-based server from your platform vendor. BIOS updates often help customers by providing new and updated features, bug fixes, enhancements, security features, and other improvements. These improvements can help your system software stability and dependency modules (such as hardware, firmware, drivers, and software) by giving you a more robust environment to run your applications.

## 3.1 Processor Core Settings

| Name                    | Default | Description                                                                                                     |

|-------------------------|---------|-----------------------------------------------------------------------------------------------------------------|

| SMT Control             | Auto    | Enabled/Auto: Two hardware threads per core.                                                                    |

|                         |         | Disabled: Single hardware thread per core.                                                                      |

| L1 Stream HW Prefetcher | Auto    | Enabled/Auto: Enables the prefetcher.                                                                           |

|                         |         | Disabled: Disables the prefetcher.                                                                              |

| L1 Stride Prefetcher    | Auto    | Enabled/Auto: Enables the prefetcher.                                                                           |

|                         |         | Disabled: Disables the prefetcher.                                                                              |

| L1 Region Prefetcher    | Auto    | Enabled/Auto: Enables the prefetcher.                                                                           |

|                         |         | Disabled: Disables the prefetcher.                                                                              |

| L1 Burst Prefetch Mode  | Auto    | Enabled/Auto: Enables the prefetcher.                                                                           |

|                         |         | Disabled: Disables the prefetcher.                                                                              |

| L2 Stream HW Prefetcher | Auto    | Enabled/Auto: Enables the prefetcher.                                                                           |

|                         |         | Disabled: Disables the prefetcher.                                                                              |

| L2 Up/Down Prefetcher   | Auto    | Enabled/Auto: Enables the prefetcher.                                                                           |

|                         |         | Disabled: Disables the prefetcher.                                                                              |

| Core Performance Boost  | Auto    | Enabled/Auto: Enables Core Performance Boost.                                                                   |

|                         |         | Disabled: Disables Core Performance Boost.                                                                      |

| BoostFmaxEn             | Auto    | Auto: Use the default Fmax                                                                                      |

|                         |         | Manual: User can set the boost Fmax                                                                             |

| BoostFmax               | Auto    | Specify the boost Fmax frequency limit to apply to all cores (MHz in decimal)                                   |

| Global C-State Control  | Auto    | Enabled/Auto: Controls IO based C-state generation and DF C-states, including core processor C-States           |

|                         |         | Disabled: AMD strongly recommends not disabling this option because this also disables core processor C-States. |

Table 3-1: Processor core BIOS settings

| X3D | Auto | Enables or disables AMD 3D V-Cache™ technology on Cache Optimized (9004X) processors.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |      | <ul> <li>Auto: Enabled on an AMD EPYC 9004 Series processor with AMD<br/>3D V-Cache™ technology, enabling this option enables the AMD<br/>3D V-Cache module in the CCD to increase the total size of the L3<br/>cache memory to 96MB</li> </ul>                                                                                                                                                                                                                                                                                                   |

|     |      | • <b>Disabled:</b> Disabling this option reduces the L3 cache in the CCD to 32MB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |      | Note: This option only applies to AMD EPYC 9004 Series Processors with AMD 3D V-Cache technology.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |      | Note: AMD engineers performed extensive internal testing and validation for various applications using the X3D BIOS option found in AMD EPYC 9xx4X processors with AMD 3D V-Cache technology. This testing and validation cannot cover all applications or use cases. Testing has shown AMD 3D V-Cache to be beneficial for most workloads, however AMD recommends that you test and evaluate the benefits of enabling or disabling the X3D BIOS option for your application workloads in your environment and proceeding based on those results. |

Table 3-1: Processor core BIOS settings

# 3.2 Power Efficiency Settings

| Name                    | Default | Description                                                                                                        |

|-------------------------|---------|--------------------------------------------------------------------------------------------------------------------|

| Power Profile Selection | Auto    | Auto/0: High-performance mode                                                                                      |

|                         |         | • 1: Efficiency mode                                                                                               |

|                         |         | 2: Maximum I/O performance mode                                                                                    |

| Determinism Control     | Auto    | Auto: Use default performance determinism settings.                                                                |

|                         |         | Manual: Specify custom performance determinism settings.                                                           |

| Determinism Enable      | Auto    | Auto: Performance.                                                                                                 |

|                         |         | • 1: Power.                                                                                                        |

| TDP Control             | Auto    | Auto: Use platform- and OPN-default TDP.                                                                           |

|                         |         | Manual: Set custom configurable TDP.                                                                               |

| TDP                     | OPN Max | This option appears once the user sets the TDP Control to Manual.                                                  |

|                         |         | Values 85-400: Set configurable TDP, in watts.                                                                     |

| PPT Control             | Auto    | Enables or disables the <b>PPT</b> control.                                                                        |

|                         |         | Auto: Automatically set PPL in watts.                                                                              |

|                         |         | Manual: Specify a custom PPL.                                                                                      |

| PPT                     | OPN Max | This option appears once the user sets the <b>PPT Control</b> to <b>Manual</b> .                                   |

|                         |         | Values 85-400: Set configurable PPT, in watts.                                                                     |

| СРРС                    | Auto    | Enabled/Auto: Allows the OS to make performance/power optimization requests using ACPI CPPC.                       |

|                         |         | <ul> <li>Disabled: Prevents the OS from making performance/power optimization requests using ACPI CPPC.</li> </ul> |

Table 3-2: Power efficiency BIOS settings

# 3.3 NUMA and Memory Settings

| Name                                                         | Default  | Description                                                                                                                                                                                                                                               |

|--------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LLC as NUMA Domain<br>(ACPI SRAT L3 Cache as<br>NUMA Domain) | Disabled | <ul> <li>Disabled (recommended): Both NUMA nodes (cpubind) and<br/>memory interleaving (membind) are determined by the NPS<br/>setting.</li> </ul>                                                                                                        |

|                                                              |          | Enabled: Overrides the NPS setting for # of NUMA nodes by mapping each LLC as a NUMA node. This does not impact the memory interleaving                                                                                                                   |

| Nodes Per Socket (NPS)                                       | 1        | Memory Interleaving: The NPS setting always determines the memory interleaving regardless of whether LLC as NUMA is Enabled or Disabled.                                                                                                                  |

|                                                              |          | # of NUMA nodes (if <b>LLC as NUMA Domain</b> is <b>Disabled</b> ):                                                                                                                                                                                       |

|                                                              |          | NPS1/Auto: One NUMA node per socket (Most cloud providers use this as it provides consistent average memory latency to all the accesses within a socket).                                                                                                 |

|                                                              |          | NPS2: Two NUMA nodes per socket.                                                                                                                                                                                                                          |

|                                                              |          | NPS4: Four NUMA nodes per socket                                                                                                                                                                                                                          |

|                                                              |          | NPSO (not recommended): Only applicable for dual-socket systems. A single NUMA node is created for the whole two-socket platform.                                                                                                                         |

|                                                              |          | AMD recommends either NPS1 or NPS4 depending on your use case.                                                                                                                                                                                            |

|                                                              |          | <b>Windows systems:</b> Make sure that the number of logical processors per NUMA node is <=64. You can do this by using NPS2 or NPS4 instead of the default NPS1.                                                                                         |

| Memory Target Speed                                          | Auto     | Auto: Determine the maximum memory speed based on SPD information from populated DIMMs and platform memory speed support.                                                                                                                                 |

|                                                              |          | Alternatively, you can select:                                                                                                                                                                                                                            |

|                                                              |          | <ul> <li>Values 3200-5600 MT/s: Run the DRAM memory target clock<br/>speed at the specified speed. The DRAM memory target is the<br/>DDR rate.</li> </ul>                                                                                                 |

|                                                              |          | Your OEM system default value may vary.                                                                                                                                                                                                                   |

| Memory Interleaving                                          | Auto     | Auto/Enable: Enables memory interleaving.                                                                                                                                                                                                                 |

|                                                              |          | Disable: Allows for disabling memory interleaving. The NUMA Nodes per Socket setting will be honored regardless of this setting. AMD strongly recommends not disabling this setting because most production deployments benefit from memory interleaving. |

Table 3-3: NUMA and memory BIOS settings

# 3.4 Infinity Fabric Settings

| Name                             | Default | Description                                                                                                                                                                                                                                                                                                    |

|----------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-4 xGMI Link Max Speed          | Auto    | <ul> <li>12 Gbps</li> <li>16 Gbps</li> <li>17 Gbps</li> <li>18 Gbps</li> <li>20 Gbps</li> <li>22 Gbps</li> <li>23 Gbps</li> <li>24 Gbps</li> <li>25 Gbps/Auto</li> <li>26 Gbps</li> <li>27 Gbps</li> <li>28 Gbps</li> <li>30 Gbps</li> <li>32 Gbps</li> <li>Your OEM system default value may vary.</li> </ul> |

| xGMI Link Width Control          | Auto    | <ul> <li>Auto: Use the default xGMI link width controller settings.</li> <li>Manual: Specify a custom xGMI link width controller setting.</li> </ul>                                                                                                                                                           |

| xGMI Force Link Width<br>Control | Auto    | <ul> <li>Unforce: Do not force the xGMI to a fixed width.</li> <li>Force: Use the xGMI link to the user-specified width.</li> </ul>                                                                                                                                                                            |

| xGMI Force Link Width            | Auto    | <ul> <li>0: Force xGMI link width to x4.</li> <li>1: Force xGMI link width to x8.</li> <li>2: Force xGMI link width to x16.</li> </ul>                                                                                                                                                                         |

| xGMI Max Link Width Control      | Auto    | <ul> <li>Auto: Use the default xGMI link width controller settings.</li> <li>Manual: Specify a custom xGMI link with controller setting.</li> </ul>                                                                                                                                                            |

| xGMI Max Link Width              | Auto    | <ul> <li>0: Set max xGMI link width to x8.</li> <li>1: Set max xGMI link width to x16.</li> </ul>                                                                                                                                                                                                              |

| APBDIS                           | Auto    | <ul> <li>O/Auto: Dynamically switch the Infinity Fabric P-state based on link usage.</li> <li>1: Enabled fixed Infinity Fabric P-state control.</li> </ul>                                                                                                                                                     |

| DfPstate Range Support           | Auto    | <ul> <li>Auto: If this feature is enabled, the range value setting should follow the rule that MaxDfPstate&lt;=MinDfPstate. Otherwise, it will not work.</li> <li>Enable: Add the values MaxDfPstate &amp; MinDfPstate.</li> <li>Disable: No MaxDfPstate &amp; MinDfPstate option.</li> </ul>                  |

Table 3-4: Infinity Fabric BIOS settings

| DF C-States | Auto | Controls DF C-states.                                                                                |  |

|-------------|------|------------------------------------------------------------------------------------------------------|--|

|             |      | <ul> <li>Disabled: Prevents the AMD Infinity Fabric from entering a low-<br/>power state.</li> </ul> |  |

|             |      | <ul> <li>Enabled/Auto: Allows the AMD Infinity Fabric to enter a low-<br/>power state.</li> </ul>    |  |

Table 3-4: Infinity Fabric BIOS settings

#### PCIe, I/O, Security, and Virtualization Settings 3.5

| Name                     | Default    | Description                                                                                                                                 |

|--------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Local APIC Mode          | Auto(0x02) | xAPIC: Use xAPIC, supports up to 255 cores.                                                                                                 |

|                          |            | x2APIC: Supports more than 255 cores.                                                                                                       |

|                          |            | Auto: The system will choose the mode that best fits the number of active cores in the system.                                              |

|                          |            | Compatibility: Threads below 255 run in xAPIC with xAPIC ACPI structures, and threads 255 and above run in x2 mode with x2 ACPI structures. |

|                          |            | XApicMode (0x01): Forces legacy xAPIC mode.                                                                                                 |

|                          |            | X2ApicMode (0x02): Forces x2APIC mode independent of thread count.                                                                          |

| PCIe Speed PMM Control   | Auto       | O: Dynamic link speed determined by power management functionality.                                                                         |

|                          |            | • 1: Static Target Link Speed (Gen4); sets the maximum idle link speed to 16 GT/s.                                                          |

|                          |            | • Auto/2: Static Target Link Speed (Gen5); sets the maximum idle link speed to 32 GT/s, thereby disabling the feature).                     |

| PCIe ARI Support (SRIOV) | Auto       | Enabled/Auto: Enables Alternative Routing ID interpretation.                                                                                |

|                          |            | Disabled: Disables Alternative Routing ID interpretation.                                                                                   |

| PCIe Ten Bit Tag Support | Auto       | Enabled/Auto: Enables PCIe 10-bit tags for supported devices.                                                                               |

|                          |            | Disabled: Disables PCIe 10-bit tags for all devices.                                                                                        |

| IOMMU                    | Auto       | Enabled/Auto: Enables IOMMU. AMD recommends setting this to pt:pass-through in the Linux kernel settings.                                   |

|                          |            | Disabled: Disables IOMMU.                                                                                                                   |

| AVIC                     | Disabled   | Advanced Virtual Interrupt Controller.                                                                                                      |

|                          |            | Disabled: Disables AVIC.                                                                                                                    |

|                          |            | Enabled: Enables AVIC.                                                                                                                      |

| x2AVIC                   | Disabled   | x2AVIC is an extension of the advanced virtual interrupt controller. This feature currently requires a custom AMD Linux kernel.             |

|                          |            | Disabled: Disables x2AVIC.                                                                                                                  |

|                          |            | Enabled: Enables x2AVIC.                                                                                                                    |

Table 3-5: PCIe, I/O, security, and virtualization BIOS settings

57996 - 1.3 19

| TSME    | Auto     | <ul> <li>Auto/Disabled: Disables transparent secure memory encryption.</li> <li>Enabled: Enables transparent secure memory encryption.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEV     | Disabled | In a multi-tenant environment (such as a cloud), Secure Encrypted Virtualization (SEV) mode isolates virtual machines from each other and from the hypervisor.                                                                                                                                                                                                                                                                                                                                                                        |

|         |          | Disabled: SEV is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         |          | Enabled: SEV is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SEV-ES  | Disabled | Secure Encrypted Virtualization-Encrypted State (SEV-ES) mode extends SEV protection to the contents of the CPU registers by encrypting them when a virtual machine stops running. Combining SEV and SEV-ES can reduce the attack surface of a VM by helping protect the confidentiality of data in memory.  • Disabled: SEV-ES is disabled.                                                                                                                                                                                          |

|         |          | Enabled: SEV-ES is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SEV-SNP | Disabled | Secure Encrypted Virtualization-Secure Nested Paging (SEV-SNP) mode builds on SEV and SEV-ES by adding strong memory integrity protection to create an isolated execution environment that helps prevent malicious hypervisor-based attacks such as data replay and memory re-mapping. SEV-SNP also introduces several additional optional security enhancements that support additional VM use models, offer stronger protection around interrupt behavior, and increase protection against recently-disclosed side channel attacks. |

|         |          | Disabled: SEV-SNP is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |          | Enabled: SEV-SNP is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 3-5: PCIe, I/O, security, and virtualization BIOS settings

## 3.6 Higher-Level Settings

The system powers on to an initial state, after which succeeding software layers may affect system settings:

- 1. System firmware validates basic hardware functionality and allows users to change various settings via the BIOS Setup menus.

- 2. UEFI provides a shell environment that allows users to further interact with the system.

- 3. The operating system or hypervisor is the next software layer that provides control over system hardware.

- 4. Lastly, certain applications can also affect underlying hardware.

Each of the lines above may alter settings made by prior line, and some user changes require a reboot to take effect.

Please refer to your OEM documentation and/or applicable AMD Tuning Guide(s) for further guidance.

## Chapter

4

# **BIOS Settings for RDBMS**

Table 4-1 describes the BIOS options that most impact performance for common RDBMS systems. Please see the BIOS & Workload Tuning Guide for AMD EPYC™ 9004 Series Processors (available from AMD EPYC Tuning Guides) for additional BIOS setting information.

The **NUMA Nodes per Socket** setting is a trade-off between minimizing local memory latency for NUMA- aware or highly parallelizable workloads versus maximizing per-core memory bandwidth for non-NUMA friendly workloads. The greater the number of memory channels interleaved, the higher the memory throughput is for certain memory operations. Increasing the number of NUMA nodes per socket will decrease the memory channels per NUMA node and decrease both throughput and latency. There are multiple L3 caches in the NUMA domain, even when NPS=4. The **ACPI SRAT L3 Cache as NUMA Domain** setting further splits the NUMA domains such that each L3 cache has its own domain. Enabling this option uses the **NUMA Nodes per Socket** setting to determine memory interleaving granularity.

## 4.1 BIOS Settings for Maximizing Performance

| Name                | Value                                 | Description                                                                                                                                                                                                                                               |

|---------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSME                | Disabled                              | Transparent Secure Memory Encryption (TSME) provides hardware memory encryption of all data stored on system DIMMs and increases memory latency by 5-7ns.                                                                                                 |

| Determinism Control | Manual                                | Enables the <b>Determinism Slider</b> control.                                                                                                                                                                                                            |

| Determinism Enables | Disable<br>performance<br>determinism | Ensures maximum performance for each CPU in a large population of identically-configured CPUs by only throttling CPUs when they reach the same TDP.                                                                                                       |

| cTDP Control        | Manual                                | Setting <b>Configurable Thermal Design Power</b> (TDP) to <b>Manual</b> allows you to modify the platform CPU cooling limit.                                                                                                                              |

| cTDP                | OPN Max                               | Set TDP in watts.                                                                                                                                                                                                                                         |

| PPT Control         | Manual                                | Setting <b>PPL</b> to <b>Manual</b> allows you to modify the CPU Power Dissipation Limit.                                                                                                                                                                 |

| PPT                 | OPN Max                               | Set PPT in watts.                                                                                                                                                                                                                                         |

| SMT Control         | Auto                                  | Enables Symmetric Multithreading (SMT), which allows two hardware threads per core.                                                                                                                                                                       |

|                     |                                       | You must enable AMD x2APIC with support more than 383 threads if you are using a system with dual 96-core AMD EPYC 9004 Series Processors. If you are running dual 96-core processors and your OS does not support AMD x2APIC, then you must disable SMT. |

Table 4-1: Recommended BIOS settings

| NUMA Node per Socket<br>(NPS)        | Varies by<br>RDBMS and<br>workload | Determines the number of NUMA nodes between which to split the memory channels. Higher numbers reduce memory channels per NUMA node and lower both memory throughput and latency.                                                                                                                                                                                                                                                              |

|--------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACPI SRAT L3 Cache as<br>NUMA Domain | Varies by<br>RDBMS and<br>workload | Specifies whether or not to report each L3 cache to the OS as a NUMA domain. Allowing processes that use the same data to be scheduled on the set of CPUs that share an L3 cache increases the L3 cache hit rate.                                                                                                                                                                                                                              |

| Power Profile Selection              | Maximum IO<br>Performance<br>Mode  | Select <b>Maximum IO Performance Mode</b> to enable the maximum I/O performance if the number of NUMA nodes per socket is set to either 1 or 4.                                                                                                                                                                                                                                                                                                |

| X3D                                  | Enabled                            | In an AMD EPYC 9004 processor with AMD 3D V-Cache technology, this option enables the AMD 3D V-Cache module in the CCD to increase the total size of the L3 cache memory to 96MB. Disabling this option reduces the L3 cache in the CCD to 32MB. AMD recommends enabling this option, if available and if doing so benefits your workload after testing. This option is only available on AMD EPYC 9004 Series Processors with AMD 3D V-Cache. |

Table 4-1: Recommended BIOS settings (Continued)

## 4.2 Memory

RDBMS systems generally consume large amounts of memory. AMD EPYC 9004 Series Processors have 12 memory channels per CPU socket to increase both the total addressable memory per socket and the memory throughput per socket. Enabling large pages in the OS can improve system performance by reducing the amount of system resources required to access page table entries. The size of the large pages varies from platform to platform. You can enable large pages on Linux based systems in one of the following two ways:

- Explicitly set the vm.nr\_hugepages parameter in /etc/sysctl.conf, as described in <u>"Linux Tuning Considerations" on page 27</u>.

- Implicitly use transparent huge pages.

Relational databases on Linux prefer transparent huge pages, while most other vendors prefer explicitly defined huge pages.

#### 4.3 Network

Tuning and configuring the RDBMS system's network is crucial for quickly getting information in and out of the RDBMS. Tuning also prevents the network from consuming all system resources. This is less critical in smaller systems that run transactions and queries directly on the local server. Please see the Linux® Network Tuning Guide for AMD EPYC™ 9004 Series Processors or Windows® Network Tuning Guide for AMD EPYC™ 9004 Series Processors (available from AMD EPYC Tuning Guides), as appropriate, for OS-specific network tuning instructions.

#### 4.4 Storage

AMD EPYC 9004 Series Processors support PCle® Gen 5 connections with double the I/O bandwidth of PCle Gen 4. All normal RDMBS I/O tuning rules still apply, such as separating the log devices from data devices and splitting I/O across the remaining devices, controllers, PCle bus, etc. Please see the I/O-related information in the MongoDB® Tuning Guide for AMD EPYC™ 9004 Series Processors (available from AMD EPYC Tuning Guides) for additional instructions.

# Chapter **5**

# MySQL - Additional Configuration Settings

This chapter contains MySQL tuning recommendations. You can download MySQL from <a href="https://support.oracle.com/">https://support.oracle.com/</a>\* and install it as instructed in <a href="https://dev.mysql.com/doc/refman/8.0/en/installing.html">https://dev.mysql.com/doc/refman/8.0/en/installing.html</a>\*. Be sure to download and install the latest version. MySQL database configurations are defined in <a href="https://exchapter.org/">/etc/my.cnf</a>. Table 5-1 lists the tunable parameters. Please also see <a href="https://exchapter.org/">"Linux Tuning Considerations"</a> on page 27 for additional Linux tuning considerations.

## 5.1 Tuning my.cnf Parameters

| Name                         | Value                                                | Description                                                                                                                         |

|------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| datadir                      | Directory to store<br>database data and<br>log files | This is the database directory mounted on the RAID volume created during initial setup.                                             |

| innodb_buffer_pool_size      | 70%-80% of total<br>RAM                              | Based on the amount of RAM available                                                                                                |

| Innodb_buffer_pool_instances | 64                                                   | Number of regions the InnoDB buffer pool is divided into.<br>Reduces contention because different threads write to<br>cached pages. |

| max_connections              | 4000                                                 | Maximum number of allowed connections (plus 1 for SUPER account).                                                                   |

| Innodb_log_buffer_size       | 1G                                                   | Enables large transactions to run without needing to write the log to disk before the transactions commit.                          |