# Preliminary Processor Programming Reference (PPR) for AMD Family 17h Model 31h, Revision B0 Processors

# **Legal Notices**

# © 2018-2020 Advanced Micro Devices, Inc. All rights reserved.

The information contained herein is for informational purposes only, and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.

#### Trademarks:

AMD, the AMD Arrow logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

AGESA is a trademark of Advanced Micro Devices, Inc.

AMD Virtualization is a trademark of Advanced Micro Devices, Inc.

AMD-V is a trademark of Advanced Micro Devices, Inc.

Adobe is a registered trademark of Adobe.

Infinity Fabric is a trademark of Advanced Micro Devices, Inc.

Linux is a registered trademark of Linus Torvalds.

Microsoft is a registered trademark of Microsoft Corporation.

PCI Express is a registered trademark of PCI-SIG Corporation.

PCIe is a registered trademark of PCI-SIG Corporation.

Windows is a registered trademark of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

Reverse engineering or disassembly is prohibited.

USE OF THIS PRODUCT IN ANY MANNER THAT COMPLIES WITH THE MPEG ACTUAL OR DE FACTO VIDEO AND/OR AUDIO STANDARDS IS EXPRESSLY PROHIBITED WITHOUT ALL NECESSARY LICENSES UNDER APPLICABLE PATENTS. SUCH LICENSES MAY BE ACQUIRED FROM VARIOUS THIRD PARTIES INCLUDING, BUT NOT LIMITED TO, IN THE MPEG PATENT PORTFOLIO, WHICH LICENSE IS AVAILABLE FROM MPEG LA, L.L.C., 6312 S. FIDDLERS GREEN CIRCLE, SUITE 400E, GREENWOOD VILLAGE, COLORADO 80111.

# **List of Chapters**

- 1 Overview

- 2 Core Complex (CCX)

- 3 Reliability, Availability, and Serviceability (RAS) Features

- 4 Advanced Platform Management Link (APML)

- 5 SB Temperature Sensor Interface (SB-TSI)

- 6 Northbridge IO (NBIO)

- 7 DXIO

- **8** Miscellaneous Information

List of Namespaces List of Definitions Memory Map - MSR Memory Map - SMN

# **Table of Contents**

| Over | view                                                 |  |  |  |

|------|------------------------------------------------------|--|--|--|

| 1.1  | Intended Audience                                    |  |  |  |

| 1.2  | Reference Documents                                  |  |  |  |

|      | 1.2.1 Documentation Conventions                      |  |  |  |

| 1.3  | Adobe® Reader                                        |  |  |  |

|      | 1.3.1 Adobe® Reader Configuration                    |  |  |  |

|      | 1.3.1.1 Open Hyperlink Document in New Window        |  |  |  |

|      | 1.3.1.2 Show Toolbars                                |  |  |  |

|      | 1.3.1.3 Show "Previous View" and "Next View" Buttons |  |  |  |

|      | 1.3.2 Adobe® Reader Usage                            |  |  |  |

|      | 1.3.2.1 Searching a Multiple Volume PPR              |  |  |  |

|      | 1.3.2.2 Cross-References and Hyperlinks              |  |  |  |

|      | 1.3.2.3 Expand Current Bookmark                      |  |  |  |

| 1.4  | Conventions                                          |  |  |  |

|      | 1.4.1 Numbering                                      |  |  |  |

|      | 1.4.2 Arithmetic And Logical Operators               |  |  |  |

|      | 1.4.2.1 Operator Precedence and Associativity        |  |  |  |

|      | 1.4.3 Register Mnemonics                             |  |  |  |

|      | 1.4.3.1 Logical Mnemonic                             |  |  |  |

|      | 1.4.3.2 Physical Mnemonic                            |  |  |  |

|      | 1.4.4 Register Format                                |  |  |  |

|      | 1.4.4.1 A Register is a group of Register Instances  |  |  |  |

|      | 1.4.4.2 Register Physical Mnemonic, Title, and Name  |  |  |  |

|      | 1.4.4.3 Full Width Register Attributes               |  |  |  |

|      | 1.4.4.4 Register Description                         |  |  |  |

|      | 1.4.4.5 Register Instance Table                      |  |  |  |

|      | 1.4.4.5.1 Content Ordering in a Row                  |  |  |  |

|      | 1.4.4.5.2 Multiple Instances Per Row                 |  |  |  |

|      | 1.4.4.5.3 MSR Access Method                          |  |  |  |

|      | 1.4.4.5.3.1 MSR Per-Thread Example                   |  |  |  |

|      | 1.4.4.5.3.2 MSR Range Example                        |  |  |  |

|      | 1.4.4.5.4 BAR Access Method                          |  |  |  |

|      | 1.4.4.5.4.1 BAR as a Register Reference              |  |  |  |

|      | 1.4.4.5.5 PCICFG Access Method                       |  |  |  |

|      | 1.4.4.5.5.1 PCICFG Bus Implied to be 00h             |  |  |  |

|      | 1.4.4.5.6 Data Port Access Method                    |  |  |  |

|      | 1.4.4.6 Register Field Format                        |  |  |  |

|      | 1.4.4.7 Simple Register Field Format                 |  |  |  |

|      | 1.4.4.8 Complex Register Field Format                |  |  |  |

|      | 1.4.4.9 Field Name is Reserved                       |  |  |  |

|      | 1.4.4.10 Field Access Type                           |  |  |  |

|      | 1.4.4.10.1 Conditional Access Type Expression        |  |  |  |

|      | 1.4.4.11 Field Reset                                 |  |  |  |

|      | 1.4.4.12 Field Initialization                        |  |  |  |

|      | 1.4.4.13 Field Check                                 |  |  |  |

|      | 1.4.4.14 Field Valid Values                          |  |  |  |

| 1.5  | Definitions                                          |  |  |  |

| 1.6  | Changes Between Revisions and Product Variations     |  |  |  |

| . –  | 1.6.1 Revision Conventions                           |  |  |  |

| 1.7  | Package                                              |  |  |  |

|      | 1.7.1 Package type                                                            |

|------|-------------------------------------------------------------------------------|

| 1.8  | Processor Overview                                                            |

| 1.0  | 1.8.1 Features                                                                |

| 1.9  | System Overview                                                               |

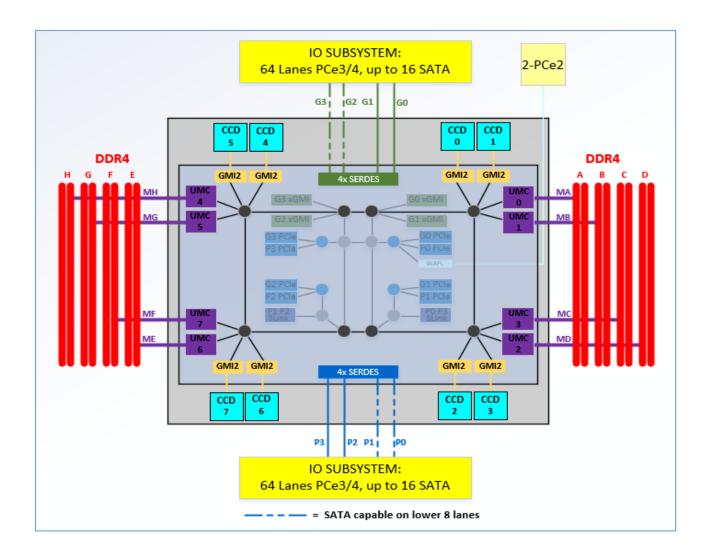

| _,_  | 1.9.1 SP3 MCM Server Single-Socket                                            |

|      | 1.9.1.1 SP3 1P Memory Support                                                 |

|      | 1.9.1.2 SP3 1P I/O Support                                                    |

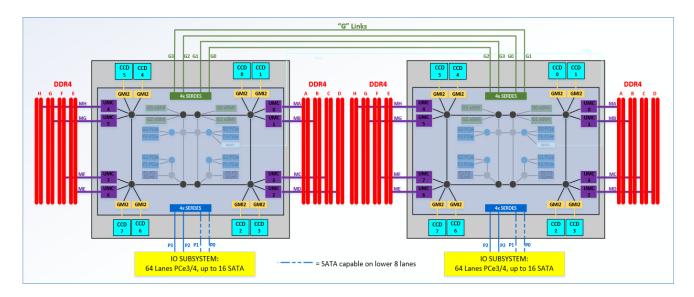

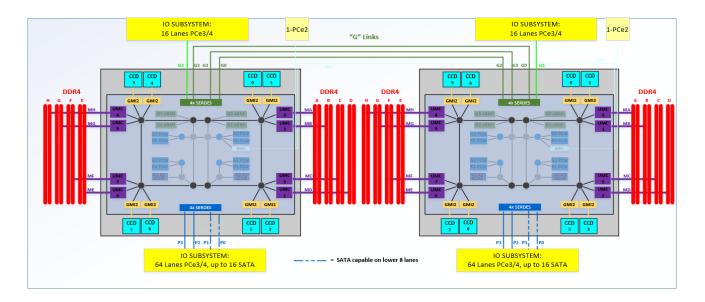

|      | 1.9.2 SP3 MCM Server Dual-Socket                                              |

|      | 1.9.2.1 SP3 2P Coherent Interconnect Topology                                 |

|      | 1.9.2.2 SP3 2P Memory Support                                                 |

|      | 1.9.2.3 SP3 2P I/O Support                                                    |

| Core | Complex (CCX)                                                                 |

| 2.1  | Processor x86 Core                                                            |

|      | 2.1.1 Core Functional Information                                             |

|      | 2.1.2 Core Definitions                                                        |

|      | 2.1.3 Secure Virtual Machine Mode (SVM)                                       |

|      | 2.1.3.1 BIOS support for SVM Disable                                          |

|      | 2.1.3.1.1 Enable AMD Virtualization <sup>TM</sup>                             |

|      | 2.1.3.1.2 Disable AMD Virtualization™                                         |

|      | 2.1.3.1.3 Disable AMD Virtualization <sup>TM</sup> , with a user supplied key |

|      | 2.1.4 Memory Encryption                                                       |

|      | 2.1.5 Effective Frequency                                                     |

|      | 2.1.6 Address Space                                                           |

|      | 2.1.6.1 Virtual Address Space                                                 |

|      | 2.1.6.2 Physical Address Space                                                |

|      | 2.1.6.3 System Address Map                                                    |

|      | 2.1.6.3.1 Memory Access to the Physical Address Space                         |

|      | 2.1.6.3.1.1 Determining Memory Type                                           |

|      | 2.1.7 Configuration Space                                                     |

|      | 2.1.7.1 MMIO Configuration Coding Requirements                                |

|      | 2.1.7.2 MMIO Configuration Ordering                                           |

|      | 2.1.7.3 Processor Configuration Space                                         |

|      | 2.1.8 PCI Configuration Legacy Access                                         |

|      | 2.1.9 System Software Interaction With SMT Enabled                            |

|      | <ul><li>2.1.10 Register Sharing</li><li>2.1.11 Timers</li></ul>               |

|      | 2.1.11 Timers 2.1.12 Interrupts                                               |

|      | 2.1.12 Interrupts 2.1.12.1 System Management Mode (SMM)                       |

|      | 2.1.12.1.1 SMM Overview                                                       |

|      | 2.1.12.1.2 Mode and Default Register Values                                   |

|      | 2.1.12.1.3 SMI Sources And Delivery                                           |

|      | 2.1.12.1.4 SMM Initial State                                                  |

|      | 2.1.12.1.5 SMM Save State                                                     |

|      | 2.1.12.1.6 System Management State                                            |

|      | 2.1.12.1.7 Exceptions and Interrupts in SMM                                   |

|      | 2.1.12.1.8 The Protected ASeg and TSeg Areas                                  |

|      | 2.1.12.1.9 SMM Special Cycles                                                 |

|      | 2.1.12.1.10 Locking SMM                                                       |

|      | 2.1.12.2 Local APIC                                                           |

|      | 2.1.12.2.1 Local APIC Functional Description                                  |

|      | 2.1.12.2.1.1 Detecting and Enabling                                           |

|      | 2.1.12.2.1.2 APIC Register Space                                              |

|      | 2.1.12.2.1.3 ApicId Enumeration Requirements                                  |

3.1.3 3.1.3.1

|     | 2.1.12.2.1.4   | Physical Destination Mode                          |

|-----|----------------|----------------------------------------------------|

|     | 2.1.12.2.1.5   | Logical Destination Mode                           |

|     | 2.1.12.2.1.6   | Interrupt Delivery                                 |

|     | 2.1.12.2.1.7   | Vectored Interrupt Handling                        |

|     | 2.1.12.2.1.8   | Interrupt Masking                                  |

|     | 2.1.12.2.1.9   | Spurious Interrupts                                |

|     | 2.1.12.2.1.10  | Spurious Interrupts Caused by Timer Tick Interrupt |

|     | 2.1.12.2.1.11  | Lowest-Priority Interrupt Arbitration              |

|     | 2.1.12.2.1.12  | Inter-Processor Interrupts                         |

|     | 2.1.12.2.1.13  | APIC Timer Operation                               |

|     | 2.1.12.2.1.14  | Generalized Local Vector Table                     |

|     | 2.1.12.2.1.15  | State at Reset                                     |

|     | 2.1.12.2.2 Lo  | ocal APIC Registers                                |

|     | 2.1.13 CPUID   | nstruction                                         |

|     | 2.1.13.1 CPU   | D Instruction Functions                            |

|     | 2.1.14 MSR Re  |                                                    |

|     | 2.1.14.1 MSR   | s - MSR0000_xxxx                                   |

|     | 2.1.14.2 MSR   | s - MSRC000_0xxx                                   |

|     | 2.1.14.2.1 IVI | SRS - MSRC000_2XXX                                 |

|     |                | s - MSRC001_0xxx                                   |

|     |                | s - MSRC001_1xxx                                   |

|     |                | ance Monitor Counters                              |

|     |                | MC Assignments                                     |

|     |                | rmance Measurement                                 |

|     |                | Increment per Cycle Events                         |

|     |                | Performance Monitor Counters                       |

|     |                | oating Point (FP) Events                           |

|     |                | S Events                                           |

|     |                | and BP Events                                      |

|     |                | E Events                                           |

|     |                | X (SC) Events                                      |

|     |                | 2 Cache Events                                     |

|     |                | ache Performance Monitor Counters                  |

|     |                | 3 Cache PMC Events                                 |

|     |                | on Based Sampling (IBS)                            |

|     |                | and Serviceability (RAS) Features                  |

| 3.1 | Machine Check  |                                                    |

|     | 3.1.1 Overview |                                                    |

|     | _              | cy Machine Check Architecture                      |

|     |                | ine Check Architecture Extensions                  |

|     |                | of MCA Information                                 |

|     |                | ror Management                                     |

|     |                | nult Management                                    |

|     |                | Check Registers                                    |

|     |                | al Registers                                       |

|     |                | ine Check Banks                                    |

|     |                | egacy MCA Registers                                |

|     |                | egacy MCA MSRs                                     |

|     |                | CAX Registers                                      |

|     |                | CAX MSRs                                           |

|     | 3.1.2.3 Acce   | ss Permissions                                     |

Machine Check Errors

**Error Severities**

|      | 3.1.3.2                               | Exceptions and Interrupts                |

|------|---------------------------------------|------------------------------------------|

|      | 3.1.3.3                               | Error Codes                              |

|      | 3.1.3.4                               | Extended Error Codes                     |

|      | 3.1.3.5                               | DOER and SEER State                      |

|      | 3.1.3.6                               | MCA Overflow Recovery                    |

|      | 3.1.3.7                               | MCA Recovery                             |

|      | 3.1.4                                 | Machine Check Features                   |

|      | 3.1.4.1                               | Error Thresholding                       |

|      | 3.1.4.2                               | Error Simulation                         |

|      | 3.1.5                                 | Software Guidelines                      |

|      | 3.1.5.1                               | Recognizing MCAX Support                 |

|      | 3.1.5.2                               | Communicating MCAX Support               |

|      | 3.1.5.3                               | Machine Check Initialization             |

|      | 3.1.5.4                               | Determining Bank Count                   |

|      | 3.1.5.5                               | Determining Bank Type                    |

|      | 3.1.5.6                               | Recognizing Error Type                   |

|      | 3.1.5.7                               | Machine Check Error Handling             |

| 3.2  | Machin                                | e Check Architecture Implementation      |

|      | 3.2.1                                 | Implemented Machine Check Banks          |

|      | 3.2.2                                 | Implemented Machine Check Bank Registers |

|      | 3.2.3                                 | Mapping of Banks to Blocks               |

|      | 3.2.4                                 | Decoding Error Type                      |

|      | 3.2.5                                 | MCA Banks                                |

|      | 3.2.5.1                               | LS                                       |

|      | 3.2.5.2                               | IF                                       |

|      | 3.2.5.3                               | L2                                       |

|      | 3.2.5.4                               | DE                                       |

|      | 3.2.5.5                               | EX                                       |

|      | 3.2.5.6                               | FP                                       |

|      | 3.2.5.7                               | L3 Cache                                 |

|      | 3.2.5.8                               | CS                                       |

|      | 3.2.5.9                               | PIE                                      |

|      | 3.2.5.10                              |                                          |

|      | 3.2.5.11                              |                                          |

|      | 3.2.5.12                              | PSP                                      |

|      | 3.2.5.13                              | SMU                                      |

|      | 3.2.5.14                              |                                          |

|      | 3.2.5.15                              |                                          |

| A -1 | 3.2.5.16                              | PCIE                                     |

|      | <b>incea Piai</b><br>Overvie          | tform Management Link (APML)             |

| 4.1  | 4.1.1                                 | ew<br>Definitions                        |

| 4.2  |                                       | s Characteristics                        |

| 4.2  | 4.2.1                                 | SMBus Protocol Support                   |

|      | 4.2.1                                 | **                                       |

| 4.3  |                                       | I2C Support occasion                     |

| 4.5  | 4.3.1                                 | SBI Processor Pins                       |

|      | 4.3.1.1                               | Physical Layer Characteristics           |

|      | 4.3.1.1                               | Processor States                         |

| 4.4  | SBI Pro                               |                                          |

| 7.4  | 4.4.1                                 |                                          |

|      |                                       | SBI Error Detection and Recovery         |

|      | 4.4.2.1                               | Error Detection  Error Detection         |

|      | · · · · · · · · · · · · · · · · · · · |                                          |

|   |      | 4.4.2.1.1  | ACK/NAK Mechanism                                                      |

|---|------|------------|------------------------------------------------------------------------|

|   |      | 4.4.2.1.2  | Bus Timeouts                                                           |

|   |      | 4.4.2.2    | Error Recovery                                                         |

|   |      | 4.4.2.2.1  | SBI Bus Reset                                                          |

|   | 4.5  | SBI Phy    | ysical Interface                                                       |

|   |      | 4.5.1      | SBI SMBus Address                                                      |

|   |      | 4.5.2      | SBI Bus Timing                                                         |

|   |      | 4.5.3      | Pass-FET Option                                                        |

| 5 |      | _          | re Sensor Interface (SB-TSI)                                           |

|   | 5.1  | Overvie    |                                                                        |

|   |      | 5.1.1      | Definitions                                                            |

|   | 5.2  |            | Protocol                                                               |

|   |      | 5.2.1      | SB-TSI Send/Receive Byte Protocol                                      |

|   |      | 5.2.1.1    |                                                                        |

|   |      | 5.2.2      | SB-TSI Read/Write Byte Protocol                                        |

|   |      | 5.2.3      | Alert Behavior                                                         |

|   |      | 5.2.4      | Atomic Read Mechanism                                                  |

|   |      | 5.2.5      | SB-TSI Temperature and Threshold Encodings                             |

|   |      | 5.2.6      | SB-TSI Temperature Offset Encoding                                     |

|   | 5.3  |            | Physical Interface                                                     |

|   |      | 5.3.1      | SB-TSI SMBus Address                                                   |

|   |      | 5.3.2      | SB-TSI Bus Timing                                                      |

|   |      | 5.3.3      | SB-TSI Bus Electrical Parameters                                       |

|   |      | 5.3.4      | Pass-FET Option                                                        |

|   | 5.4  |            | Registers                                                              |

| 6 | Nort | hbridge I0 | O (NBIO)                                                               |

|   | 6.1  | IOHC       |                                                                        |

|   |      | 6.1.1      | Definitions                                                            |

|   |      | 6.1.2      | Peer-to-Peer Support                                                   |

|   |      | 6.1.2.1    | Peer-to-Peer Synchronization                                           |

|   |      | 6.1.2.1.1  | Peer-to-Peer Status Polling                                            |

|   |      | 6.1.2.1.2  | Writing Data and Flag to a Peer                                        |

|   |      | 6.1.2.1.3  | Signaling via the CPU                                                  |

|   |      | 6.1.2.1.4  | Unsupported Peer-to-Peer Synchronization Methods                       |

|   |      | 6.1.2.2    | Peer-to-Peer Interaction with PCIe® ACS                                |

| 7 | DXI  |            |                                                                        |

|   | 7.1  |            | Registers                                                              |

|   |      | 7.1.1      | PCS_DXIO Registers                                                     |

| 8 |      |            | Information                                                            |

|   | 8.1  |            | LLCNTL0 Register                                                       |

|   | 8.2  |            | SMUIO::SMUSVI0_TEL_PLANE0 and SMU::SMUIO::SMUSVI1_TEL_PLANE0 Registers |

|   | 8.3  | SMU::T     | THM::THM_TCON_CUR_TMP Register                                         |

# **List of Figures**

| Figure 1: | Adobe® Reader Hyperlink Opens New Window Configuration |

|-----------|--------------------------------------------------------|

| Figure 2: | Adobe® Reader Select Between Opened Files              |

Figure 3: Adobe® Reader Show Toolbars Configuration

Figure 4: Adobe® Reader Prev/Next Buttons

Figure 5: Adobe® Reader Searching a Multiple Volume PPR

Figure 6: Adobe® Reader Expand Current Bookmark Button

Figure 7: Register Physical Mnemonic, Title, and Name

Figure 8: Full Width Register Attributes

Figure 9: Register Description

Figure 10: Register Instance Table: Content Ordering in a Row

Figure 11: Register Instance Table: MSR Example

Figure 12: Register Instance Table: MSR Range Example

Figure 13: Register Instance Table: BAR as Register Reference Figure 14: Register Instance Table: Bus Implied to be 00h

Figure 15: Register Instance Table: Data Port Select

Figure 16: Simple Register Field Example

Figure 17: Register Field Sub-Row for {Reset, Access Type, Init, Check}

Figure 18: Register Field Sub-Row for Description

Figure 19: Register Field Sub-Row for Valid Value Table

Figure 20: Register Field Sub-Row for Valid Bit Table

Figure 21: 1P System Block Diagram

Figure 22: 2P System Block Diagram, with 4 xGMI links Figure 23: 2P System Block Diagram, with 3 xGMI links

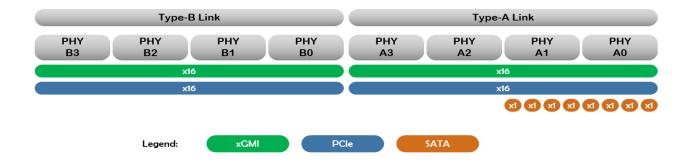

Figure 24: Link Capabilities

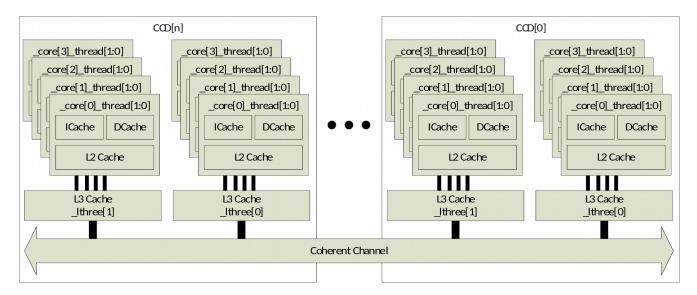

Figure 25: Register Sharing Domains

Figure 26: Instance Parameters

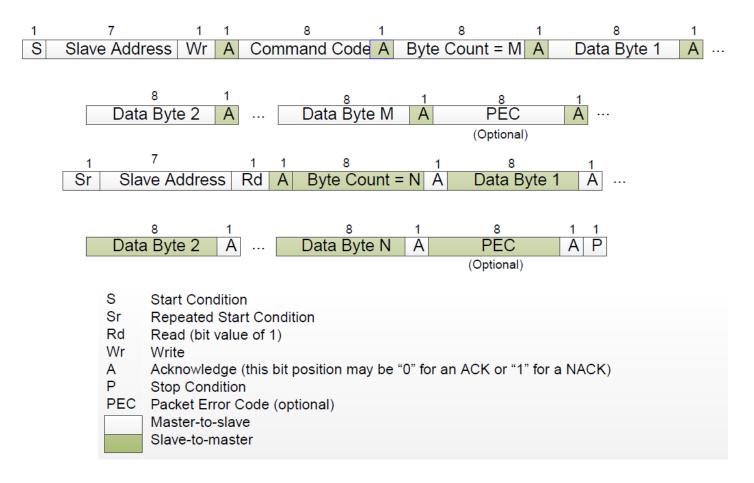

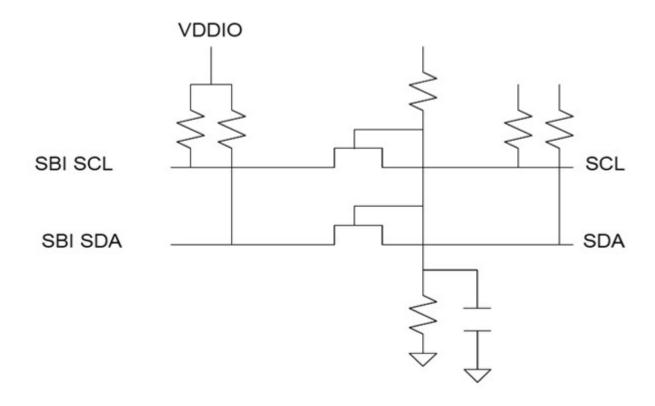

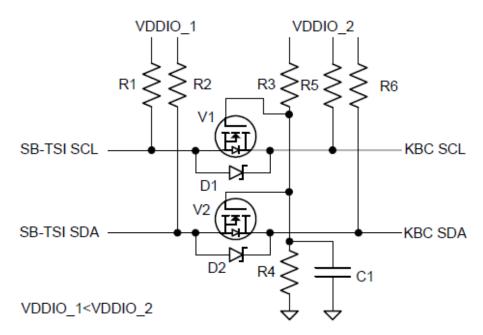

Figure 27: SBI Transmission Protocol Figure 28: Pass FET Implementation

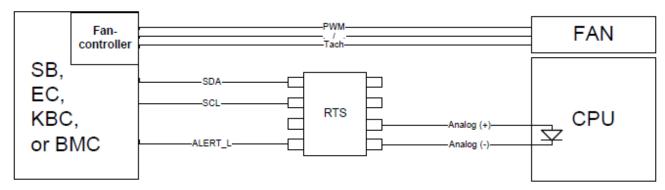

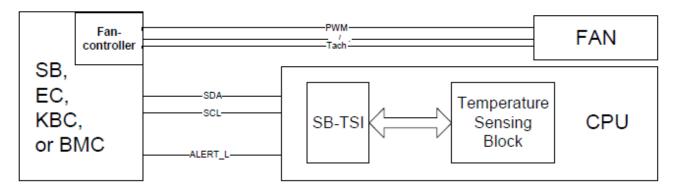

Figure 29: RTS Thermal Management Example Figure 30: SB-TSI Thermal Management Example

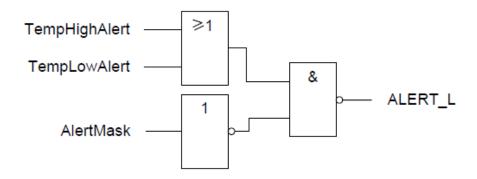

Figure 31: Alert Assertion Diagram

Figure 32: Pass FET Implementation

Table 49:

Table 50:

MCA ADDR DE

MCA SYND DE

# **List of Tables**

Table 1: Reference Documents Listing Arithmetic and Logical Operator Definitions Table 2: Table 3: **Function Definitions** Table 4: Operator Precedence and Associativity Table 5: Register Mnemonic Definitions Table 6: **Logical Mnemonic Definitions** Table 7: Physical Mnemonic Definitions Table 8: AccessType Definitions Table 9: Reset Type Definitions Table 10: **Init Type Definitions Definitions** Table 11: Table 12: Package Definitions Table 13: SP3 1P Capabilities SP3 2P Capabilities Table 14: Table 15: **Definitions** Table 16: SMM Initial State Table 17: SMM Save State Table 18: **ICR Valid Combinations** Table 19: DF PERF CTL EventSelect[13:6] - Infinity Fabric™ Component DF\_PERF\_CTL EventSelect[5:0] - Component Performance Event Table 20: Guidance for Common Performance Statistics with Complex Event Selects Table 21: **PMC** Definitions Table 22: Machine Check Terms and Acronyms Table 23: Table 24: Legacy MCA MSR Layout Table 25: MCAX MSR Layout MCAX Implementation-Specific Register Layout Table 26: **Error Overwrite Priorities** Table 27: Table 28: Error Scope Hierarchy **Error Code Types** Table 29: Error code: transaction type (TT) Table 30: Table 31: Error codes: cache level (LL) Error codes: memory transaction type (RRRR) Table 32: Table 33: Blocks Capable of Supporting MCA Banks Mapping of Blocks to MCA IPID[HwId] and MCA IPID[McaType] Table 34: Legacy MCA Registers Table 35: Table 36: MCAX Registers Table 37: Core MCA Bank to Block Mapping Table 38: Non-core MCA Bank to Block Mapping Table 39: MCA\_STATUS\_LS Table 40: MCA ADDR LS MCA\_SYND\_LS Table 41: Table 42: MCA STATUS IF MCA ADDR IF Table 43: Table 44: MCA SYND IF Table 45: MCA STATUS L2 MCA\_ADDR\_L2 Table 46: Table 47: MCA\_SYND\_L2 Table 48: MCA STATUS DE

Table 96:

```

Table 51:

MCA_STATUS_EX

Table 52:

MCA ADDR EX

MCA_SYND_EX

Table 53:

Table 54:

MCA_STATUS_FP

Table 55:

MCA ADDR FP

Table 56:

MCA SYND FP

MCA STATUS L3

Table 57:

Table 58:

MCA_ADDR_L3

Table 59:

MCA_SYND_L3

Table 60:

MCA_STATUS_CS

Table 61:

MCA ADDR CS

Table 62:

MCA SYND CS

Table 63:

MCA_STATUS_PIE

Table 64:

MCA ADDR PIE

Table 65:

MCA SYND PIE

Table 66:

MCA STATUS UMC

Table 67:

MCA_ADDR_UMC

Table 68:

MCA_SYND_UMC

Table 69:

MCA_STATUS_PB

Table 70:

MCA ADDR PB

MCA SYND PB

Table 71:

Table 72:

MCA STATUS PSP

Table 73:

MCA ADDR PSP

Table 74:

MCA_SYND_PSP

Table 75:

MCA_STATUS_SMU

Table 76:

MCA ADDR SMU

Table 77:

MCA_SYND_SMU

Table 78:

MCA_STATUS_MP5

Table 79:

MCA ADDR MP5

Table 80:

MCA SYND MP5

Table 81:

MCA_STATUS_NBIO

Table 82:

MCA_ADDR_NBIO

Table 83:

MCA_SYND_NBIO

Table 84:

MCA_STATUS_PCIE

MCA ADDR PCIE

Table 85:

Table 86:

MCA SYND PCIE

Table 87:

APML Definitions

Table 88:

SB-TSI Definitions

SB-TSI CPU Temperature and Threshold Encoding Examples

Table 89:

SB-TSI Temperature Offset Encoding Examples

Table 90:

Table 91:

SB-TSI Address Encodings

Table 92:

Link Definitions

Table 93:

RMT PLLCNTL0 REG

Table 94:

SMU::SMUIO::SMUSVIO TEL PLANEO REG

SMU::SMUIO::SMUSVI1 TEL PLANE0 REG

Table 95:

```

SMU::THM::THM\_TCON\_CUR\_TMP REG

#### 1 Overview

#### 1.1 Intended Audience

This document provides the processor behavioral definition and associated design notes. It is intended for platform designers and for programmers involved in the development of BIOS functions, drivers, and operating system kernel modules.

#### 1.2 Reference Documents

Table 1: Reference Documents Listing

| Term     | Description                                                                                                                |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| docAPM1  | AMD64 Architecture Programmer's Manual Volume 1: Application Programming, order# 24592.                                    |  |  |

| docAPM2  | AMD64 Architecture Programmer's Manual Volume 2: System Programming, order# 24593.                                         |  |  |

| docAPM3  | AMD64 Architecture Programmer's Manual Volume 3: Instruction-Set Reference, order# 24594.                                  |  |  |

| docAPM4  | AMD64 Architecture Programmer's Manual Volume 4: 128-Bit and 256-Bit Media Instructions, order# 26568.                     |  |  |

| docAPM5  | AMD64 Architecture Programmer's Manual Volume 5: 64-Bit Media and x87 Floating-Point Instructions, order# 26569.           |  |  |

| docACPI  | Advanced Configuration and Power Interface (ACPI) Specification. <a href="http://www.acpi.info">http://www.acpi.info</a> . |  |  |

| docJEDEC | JEDEC Standards. <a href="http://www.jedec.org">http://www.jedec.org</a> .                                                 |  |  |

| docPCIe  | PCI Express® Specification. <a href="http://www.pcisig.com">http://www.pcisig.com</a> .                                    |  |  |

| docPCIlb | PCI Local Bus Specification. <a href="http://www.pcisig.com">http://www.pcisig.com</a> .                                   |  |  |

| docRevG  | Revision Guide for AMD Family 17h Models 30h-3Fh Processors, order# 56323.                                                 |  |  |

| docSSP3  | Functional Data Sheet (FDS) for Socket SP3 Processors, order# 55426.                                                       |  |  |

| docSMB   | System Management Bus (SMBus) Specification. <a href="http://www.smbus.org">http://www.smbus.org</a> .                     |  |  |

#### 1.2.1 **Documentation Conventions**

When referencing information found in external documents listed in Reference Documents, the "=>" operator is used. This notation represents the item to be searched for in the reference document. For example:

docExDoc => Header1 => Header2

is to have the reader use the search facility when opening referenced document "docExDoc" and search for "Header2". "Header2" may appear more than once in "docExDoc", therefore, referencing the one that follows "Header1". In that case, the easiest way to get to Header2 is to use the search to locate Header1, then again to locate "Header2".

#### 1.3 Adobe® Reader

This section describes how to configure and use Adobe® Reader for the PPR PDFs.

Adobe Reader is the recommended tool for viewing PPR pdfs and can be downloaded at <a href="https://get.adobe.com/reader/">https://get.adobe.com/reader/</a>.

# 1.3.1 Adobe® Reader Configuration

This section describes how to configure Adobe Reader for the PPR PDFs.

## 1.3.1.1 Open Hyperlink Document in New Window

The Open Hyperlink Document in New Window setting opens a new window for a hyperlink, instead of opening the hyperlink document in the same window.

Only when deselected are previously opened files visible in the Windows® pull-down menu.

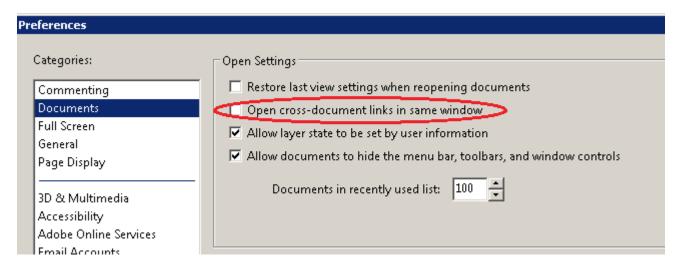

#### Edit->Preferences:

- Documents

- Open Settings:

- Deselect: Open cross-document links in same window

Figure 1: Adobe® Reader Hyperlink Opens New Window Configuration

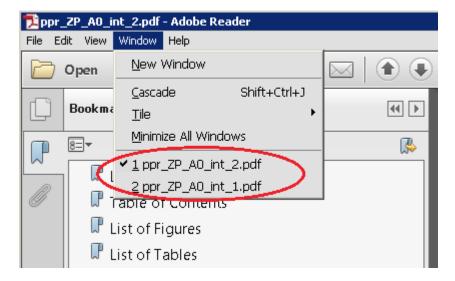

Figure 2 shows how when hyperlinking from volume 2 to volume 1, that volume 2 is left open. The check indicates the foreground window.

Figure 2: Adobe® Reader Select Between Opened Files

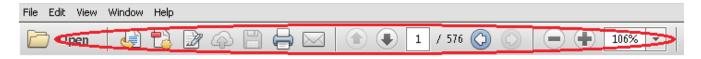

#### 1.3.1.2 Show Toolbars

If Toolbars is not shown:

- View->Show/Hide->Toolbar Items->Show Toolbars

- The toolbar is needed to see the "Previous View" and "Next View" buttons.

Figure 3: Adobe® Reader Show Toolbars Configuration

# 1.3.1.3 Show "Previous View" and "Next View" Buttons

If the "Previous View" (left arrow) and "Next View" (right arrow) buttons are not shown:

• Right click on toolbar-> Page Navigation-> select "Previous View" and "Next View" items.

Figure 4: Adobe® Reader Prev/Next Buttons

#### 1.3.2 Adobe® Reader Usage

This section describes how to use Adobe Reader for the PPR PDFs.

NOTE: PDF's are distributed in zip format. In order to search and hyperlink between PDF volumes, the zip contents must be extracted to a folder.

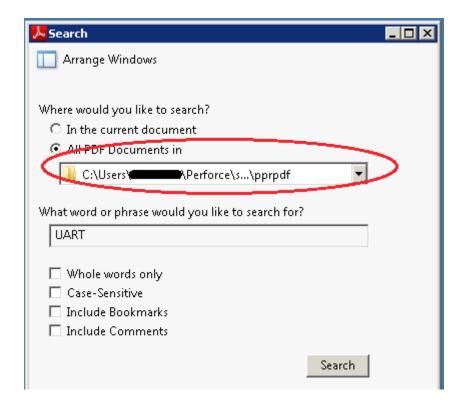

## 1.3.2.1 Searching a Multiple Volume PPR

The PPR is a multiple PDF document and searching all PDFs is performed as follows:

- The zip of PDF files must be extracted to a directory where the search will be performed. A sesarch across multiple PDF files can not be performed from within a zip of PDF's.

- Open search by selecting Edit -> Advanced Search (Shift+Ctrl+F)

- Select "All PDF Documents in" and select "Browse for Location...", which opens the "Browse For Folder" window.

- In the "Browse For Folder" window, select the folder that contains the PPR PDFs that need to be searched, and select OK.

Figure 5: Adobe® Reader Searching a Multiple Volume PPR

# 1.3.2.2 Cross-References and Hyperlinks

A cross-reference is a link to a location within the same PDF. A hyperlink is a link to a location within a different PDF.

- For cross-references, use "Previous View" to return from the current location to the previous location.

- Hyperlinks between documents leave the current location unchanged in the PDF that contained the hyperlink.

- In order for hyperlinks to work properly the zip of PDF's must be extracted to a directory. Hyperlinks will not function within a zip of PDF's.

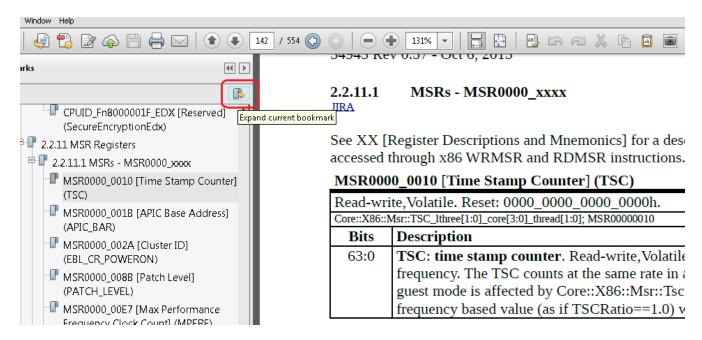

# 1.3.2.3 Expand Current Bookmark

The bookmark pane can highlight the current bookmark associated with the viewer pane by selecting the "expand current bookmark" button, as shown below.

Figure 6: Adobe® Reader Expand Current Bookmark Button

#### 1.4 Conventions

# 1.4.1 Numbering

- Binary numbers: Binary numbers are indicated either by appending a "b" at the end (e.g., 0110b) or by verilog syntax (e.g., 4'b0110).

- Hexadecimal numbers: Hexadecimal numbers are indicated by appending an "h" to the end (e.g., 45F8h) or by verilog syntax (e.g., 16'h45F8).

- Decimal numbers: A number is decimal if not specified to be binary or hex.

- Exception: Physical register mnemonics are implied to be hex without the h suffix.

- Underscores in numbers: Underscores are used to break up numbers to make them more readable. They do not imply any operation (e.g., 0110\_1100).

#### 1.4.2 Arithmetic And Logical Operators

In this document, formulas generally follow Verilog conventions for logic equations.

Table 2: Arithmetic and Logical Operator Definitions

| Operator | Definition                                                                                           |  |  |

|----------|------------------------------------------------------------------------------------------------------|--|--|

| {}       | Concatenation. Curly brackets are used to indicate a group of bits that are concatenated together.   |  |  |

|          | Each set of bits is separated by a comma (e.g., {Addr[3:2], Xlate[3:0]} represents a 6-bit values;   |  |  |

|          | the two MSBs are Addr[3:2] and the four LSBs are Xlate[3:0]).                                        |  |  |

|          | Bitwise OR (e.g., 01b   10b == 11b).                                                                 |  |  |

|          | Logical OR (e.g., 01b    10b == 1b). It treats a multi-bit operand as 1 if >= 1 and produces a 1-bit |  |  |

|          | result.                                                                                              |  |  |

| &        | Bitwise AND (e.g., 01b & 10b == 00b).                                                                |  |  |

| &&       | Logical AND (e.g., 01b && 10b == 1b). It treats a multi-bit operand as 1 if >= 1 and produces a 1-   |  |  |

|          | bit result.                                                                                          |  |  |

| ^           | Bitwise exclusive-OR (e.g., $01b \land 10b == 11b$ ). Sometimes used as "raised to the power of" as |  |  |

|-------------|-----------------------------------------------------------------------------------------------------|--|--|

|             | well, as indicated by the context in which it is used (e.g., $2^2 = 4$ ).                           |  |  |

| ~           | Bitwise NOT (also known as one's complement). (e.g., $\sim$ 10b == 01b).                            |  |  |

| !           | Logical NOT (e.g., !10b == 0b). It treats a multi-bit operand as 1 if >= 1 and produces a 1-bit     |  |  |

|             | result.                                                                                             |  |  |

| <, <=, >,   | Relational. Less than, Less than or equal, greater, greater than or equal, equal, and not           |  |  |

| >=, ==, !=  | equal.                                                                                              |  |  |

| +, -, *, /, | Arithmetic. Addition, subtraction, multiplication, division, and modulus.                           |  |  |

| %           |                                                                                                     |  |  |

| <<          | Bitwise left shift. Shift left first operand by the number of bits specified by the 2nd             |  |  |

|             | operand (e.g., 01b << 01b == 10b).                                                                  |  |  |

| >>          | Bitwise right shift. Shift right first operand by the number of bits specified by the 2nd           |  |  |

|             | operand (e.g., 10b >> 01b == 01b).                                                                  |  |  |

| ?:          | Ternary conditional (e.g., condition? value if true: value if false).                               |  |  |

*Table 3: Function Definitions*

| Term  | Description                                                                                                       |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------|--|--|

| ABS   | ABS(integer expression): Remove sign from signed value.                                                           |  |  |

| FLOOR | FLOOR(integer expression): Rounds real number down to nearest integer.                                            |  |  |

| CEIL  | CEIL(real expression): Rounds real number up to nearest integer.                                                  |  |  |

| MIN   | MIN(integer expression list): Picks minimum integer or real value of comma separated list.                        |  |  |

| MAX   | MAX(integer expression list): Picks maximum integer or real value of comma separated list.                        |  |  |

| COUNT | COUNT(integer expression): Returns the number of binary 1's in the integer.                                       |  |  |

| ROUND | ROUND(real expression): Rounds to the nearest integer; halfway rounds away from zero.                             |  |  |

| UNIT  | UNIT(register field reference): Input operand is a register field reference that contains a valid values table    |  |  |

|       | that defines a value with a unit (e.g., clocks, ns, ms, etc). This function takes the value in the register field |  |  |

|       | and returns the value associated with the unit (e.g., If the field had a valid value definition where 1010b was   |  |  |

|       | defined as 5 ns). Then if the field had the value of 1010b, then UNIT() would return the value 5.                 |  |  |

| POW   | POW(base, exponent): POW(x,y) returns the value x to the power of y.                                              |  |  |

# 1.4.2.1 Operator Precedence and Associativity

This document follows C operator precedence and associativity. The following table lists operator precedence (highest to lowest). Their associativity indicates in what order operators of equal precedence in an expression are applied. Parentheses are also used to group subexpressions to force a different precedence; such parenthetical expressions can be nested and are evaluated from inner to outer (e.g., " $X = A \parallel !B \&\& C$ " is the same as " $X = A \parallel (!B) \&\& C$ ").

*Table 4: Operator Precedence and Associativity*

| Operator   | Description                             | Associativity |

|------------|-----------------------------------------|---------------|

| !, ~       | Logical negation/bitwise complement     | right to left |

| *, /, %    | Multiplication/division/modulus         | left to right |

| +, -       | Addition/subtraction                    | left to right |

| <<,>>      | Bitwise shift left, Bitwise shift right | left to right |

| < , <=, >, | Relational operators                    | left to right |

| >=, ==, != |                                         |               |

| &          | Bitwise AND                             | left to right |

| ٨          | Bitwise exclusive OR                    | left to right |

|            | Bitwise inclusive OR                    | left to right |

| &&         | Logical AND                             | left to right |

|    | Logical OR          | left to right |

|----|---------------------|---------------|

| ?: | Ternary conditional | right to left |

# 1.4.3 Register Mnemonics

A register mnemonic is a short name that uniquely refers to a register, either all instances of that register, some instances, or a single instance.

Every register instance can be expressed in 2 forms, logical and physical, as defined below.

*Table 5: Register Mnemonic Definitions*

| Term              | Description                                                                                     |  |

|-------------------|-------------------------------------------------------------------------------------------------|--|

| logical mnemonic  | The register mnemonic format that describes the register functionally, what namespace to        |  |

|                   | which the register belongs, a name for the register that connotes its function, and optionally, |  |

|                   | named parameters that indicate the different function of each instance (e.g.,                   |  |

|                   | Link::Phy::PciDevVendIDF3). See 1.4.3.1 [Logical Mnemonic].                                     |  |

| physical mnemonic | The register mnemonic that is formed based on the physical address used to access the           |  |

|                   | register (e.g., D18F3x00). See 1.4.3.2 [Physical Mnemonic].                                     |  |

# 1.4.3.1 Logical Mnemonic

The logical mnemonic format consists of a register namespace, a register name, and optionally a register instance specifier (e.g., register namespace::register name register instance specifier).

For Unb::PciDevVendIDF3:

- The register namespace is Unb, which is the UNB IP register namespace.

- The register name is PciDevVendIDF3, which reads as PCICFG device and vendor ID in Function 3.

- There is no register instance specifier because there is just a single instance of this register.

For Dct::Phy::CalMisc2\_dct[1:0]\_chiplet[BCST,3:0]\_pad[BCST,11:0]:

- The register namespace is Dct::Phy, which is the DCT PHY register namespace.

- The register name is CalMisc2, which reads as miscellaneous calibration register 2.

- The register instance specifier is \_dct[1:0]\_chiplet[BCST,3:0]\_pad[BCST,11:0], which indicates that there are 2 DCTPHY instances, each IP for this register has 5 chiplets (0-3 and BCST), and for each chiplet 13 pads (0-11 and BCST). This register has 130 instances. (2\*5\*13)

*Table 6: Logical Mnemonic Definitions*

| Term                        | Description                                                                            |  |

|-----------------------------|----------------------------------------------------------------------------------------|--|

| register namespace          | A namespace for which the register name must be unique. A register namespace           |  |

|                             | indicates to which IP it belongs and an IP may have multiple namespaces. A             |  |

|                             | namespace is a string that supports a list of "::" separated names. The convention is  |  |

|                             | for the list of names to be hierarchical, with the most significant name first and the |  |

|                             | least significant name last (e.g., Link::Phy::Rx is the RX component in the Link       |  |

|                             | PHY).                                                                                  |  |

| register name               | A name that cannotes the function of the register.                                     |  |

| register instance specifier | The register instance specifier exists when there is more than one instance for a      |  |

|                             | register. The register instance specifier consists of one or more register instance    |  |

|                             | parameter specifier (e.g., The register instance specifier                             |  |

|                             | _dct[1:0]_chiplet[BCST,3:0]_pad[BCST,11:0] consists of 3 register instance             |  |

|                             | parameter specifiers, _dct[1:0], _chiplet[BCST,3:0], and _pad[BCST,11:0]).             |  |

| register instance parameter specifier | A register instance parameter specifier is of the form _register parameter name[register parameter value list] (e.g., The register instance parameter specifier _dct[1:0] has a register parameter name of dct (The DCT PHY instance name) and a register parameter value list of "1:0" or 2 instances of DCT PHY).                                                                                                                       |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| register parameter name               | A register parameter name is the name of the number of instances at some level of the logical hierarchy (e.g., The register parameter name dct specifies how many instances of the DCT PHY exist).                                                                                                                                                                                                                                        |  |

| register parameter value list         | The register parameter value list is the logical name for each instance of the register parameter name (e.g., For _dct[1:0], there are 2 DCT PHY instances, with the logical names 0 and 1, but it should be noted that the logical names 0 and 1 can correspond to physical values other than 0 and 1). It is the purpose of the AddressMappingTable to map these register parameter values to physical address values for the register. |  |

# 1.4.3.2 Physical Mnemonic

The physical register mnemonic format varies by the access method. The following table describes the supported physical register mnemonic formats.

*Table 7: Physical Mnemonic Definitions*

| Term   | Description                                                                          |  |

|--------|--------------------------------------------------------------------------------------|--|

| PCICFG | The PCICFG, or PCI defined configuration space, physical register mnemonic format    |  |

|        | is of the form DXFYxZZZ.                                                             |  |

| BAR    | The BAR, or base address register, physical register mnemonic format is of the form  |  |

|        | PREFIXxZZZ.                                                                          |  |

| MSR    | The MSR, or x86 model specific register, physical register mnemonic format is of the |  |

|        | form MSRXXXX_XXXX, where XXXX_XXXX is the hexadecimal MSR number.                    |  |

|        | This space is accessed through x86 defined RDMSR and WRMSR instructions.             |  |

| PMC    | The PMC, or x86 performance monitor counter, physical register mnemonic format is    |  |

|        | any of the forms {PMCxXXX, L2IPMCxXXX, NBPMCxXXX}, where XXX is                      |  |

|        | performance monitor select.                                                          |  |

| CPUID  | The CPUID, or x86 processor identification state, physical register mnemonic format  |  |

|        | is of the form CPUID FnXXXX_XXXX_EiX[_xYYY], where XXXX_XXXX is the                  |  |

|        | hex value in the EAX and YYY is the hex value in ECX.                                |  |

# 1.4.4 Register Format

A register is a group of register instances that have the same field format (same bit indices and field names).

# 1.4.4.1 A Register is a group of Register Instances

All instances of a register:

- Have the same:

- Field bit indices and names

- Field titles, descriptions, valid values.

- Register title

- Register description

- Fields may have different: (instance specific)

- Access Type. See 1.4.4.10 [Field Access Type].

- Reset. See 1.4.4.11 [Field Reset].

- Init. See 1.4.4.12 [Field Initialization].

- Check. See 1.4.4.13 [Field Check].

# 1.4.4.2 Register Physical Mnemonic, Title, and Name

A register definition is identified by a table that starts with a heavy bold line. The information above the bold line in order is:

- 1. The physical mnemonic of the register.

- A register that has multiple instances, may have instances that have different access methods, each with it's own physical mnemonic format.

- In the event that there are multiple physical mnemonic formats, the physical mnemonic format chosen is the most commonly used physical mnemonic.

- The physical mnemonic is not intended to represent the physical mnemonics of all instances of the register. It is only a visual aid to identify a register when scanning down a list, for readers that prefer to find registers by physical mnemonic. If "..." occurs in the physical mnemonic, the range is first ... last. There is no implication as to how many instances exist between first and last. See 1.4.4.5 [Register Instance Table].

- 2. The register title in brackets.

- 3. The register name in parenthesis.

| Physical Mn | Physical Mnemonic Title Name                                                                                                                                                                                                                                                                                  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MSR000      | 00_0010[Time Stamp Counter] (TSC)                                                                                                                                                                                                                                                                             |  |  |  |

| Read-wr     | Read-write, Volatile. Reset: 0000_0000_0000_0000h.                                                                                                                                                                                                                                                            |  |  |  |

| Core::X86:: | Core::X86::Msr::TSC_lthree[1:0]_core[3:0]_thread[1:0]; MSR00000010                                                                                                                                                                                                                                            |  |  |  |

| Bits        | Bits Description                                                                                                                                                                                                                                                                                              |  |  |  |

| 63:0        | TSC: time stamp counter. Read-write, Volatile. Reset: 0. The TSC increments at the P0 frequency. The TSC counts at the same rate in all P-states, all C states, S0, or S1. A read of this MSR in guest mode is affected by Core::X86::Msr::TscRateMsr. The value (TSC/TSCRatio) is the TSC P0 frequency based |  |  |  |

|             | value (as if TSCRatio == 1.0) when (TSCRatio != 1.0).                                                                                                                                                                                                                                                         |  |  |  |

*Figure 7: Register Physical Mnemonic, Title, and Name*

#### 1.4.4.3 Full Width Register Attributes

The first line that follows the bold line contains the attributes that apply to all fields of the register. This row is rendered as a convenience to the reader and replicates content that exists in the register field.

- AccessType: If all non-reserved fields of a register have the same access type, then the access type is rendered in this row.

- The supported access types are specified by 1.4.4.10 [Field Access Type].

- The example figure shows that the access type "Read-write, Volatile" applies to all non-reserved fields of the register.

- Reset: If all non-reserved fields of a register have a constant reset and are all the same type (Warm, Cold, Fixed), then the full width register reset is rendered in this row. The example figure shows the reset "0000\_0000\_0000\_0000h". See 1.4.4.11 [Field Reset].

- The value zero (0) is assumed for display purposes for all reserved fields.

- If none of the above content is rendered, then this row of the register is not rendered.

| 11201100    | ovo_voro [Time Stamp Counter] (15C)                                                                       |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------|--|--|

| Read-wr     | Read-write, Volatile, Reset: 0000_0000_0000_0000h.                                                        |  |  |

| Core::X86:: | X86::Msr::TSC_lthree[1:0]_core[3:0]_thread[1:0]; MSR00000010                                              |  |  |

| Bits        | s Description                                                                                             |  |  |

| 63:0        | TSC: time stamp counter. Read-write, Volatile. Reset: 0. The TSC increments at the P0 frequency. The      |  |  |

|             | TSC counts at the same rate in all P-states, all C states, S0, or S1. A read of this MSR in guest mode is |  |  |

|             | affected by Core::X86::Msr::TscRateMsr. The value (TSC/TSCRatio) is the TSC P0 frequency based            |  |  |

|             | value (as if TSCRatio == 1.0) when (TSCRatio != 1.0).                                                     |  |  |

Figure 8: Full Width Register Attributes

PciDevVendIDF3 [Device/Vendor ID]

MSR0000 0010 [Time Stamp Counter] (TSC)

#### 1.4.4.4 Register Description

The register description is optional and appears after the "full width register attributes" row and before the "register instance table" rows. The register description can be one or more paragraphs.

| Telbervellulbi's [berieer velluli lb] |                                 |

|---------------------------------------|---------------------------------|

|                                       | Read-only. Reset: 0000_1022h.   |

| ſ                                     | A register description.         |

|                                       | That can be multiple paragraphs |

| A registe                               | description.                                                     |  |

|-----------------------------------------|------------------------------------------------------------------|--|

| That can be multiple paragraphs.        |                                                                  |  |

| Link::Phy::Tx::PciDevVendIDF3; D18F3x00 |                                                                  |  |

| Bits                                    | Description                                                      |  |

| 31:16                                   | DeviceID: device ID. Read-only. Reset: Fixed,0000h.              |  |

| 15:0                                    | VendorID: vendor ID. Read-only. Reset: Fixed,1022h. Init: 1234h. |  |

Figure 9: Register Description

#### 1.4.4.5 Register Instance Table

The zero or more rows of 8-pt font before the Bits/Description row is the register instance table.

The register instance table can generally be described as follows:

- Each row describes the access method of one or more register instances.

- If a row describes two or more instances, then the logical instance range, left to right, corresponds to the physical range, left to right.

- The absence of register instance rows indicates that the register exists for documentation purposes, and no access method is described for the register.

Because there are multiple access methods for all the registers, each of the following subsections describes an aspect of the register instance table in isolation.

#### 1.4.4.5.1 Content Ordering in a Row

Content in a register instance table row is ordered as follows:

- The text up to the first semicolon is the logical mnemonic.

- See 1.4.3.1 [Logical Mnemonic].

- The text after the first semicolon is the physical mnemonic.

- See 1.4.3.2 [Physical Mnemonic].

• Optionally, content after the physical mnemonic provides additional information about the access method for the register instances in the row.

# BXXD00F0x000 (NB\_VENDOR\_ID)

| Read-only. Reset: 1022h.                                                                   |

|--------------------------------------------------------------------------------------------|

| Vendor ID Register                                                                         |

| IOHC::NB_VENDOR_ID_aliasHOST; BXXD00F0x000; BXX=IOHC::NB_BUS_NUM_CNTL_aliasSMN[NB_BUS_NUM] |

| IOHC::NB_VENDOR_ID_aliasSMN; NBCFGx00000000; NBCFG=13B0_0000h                              |

|                                                                                            |

Figure 10: Register Instance Table: Content Ordering in a Row

# 1.4.4.5.2 Multiple Instances Per Row

Multiple instances in a row is represented by a single dimension "range" in the logical mnemonic and the physical mnemonic.

The single dimension order of instances is the same for both the logical and physical mnemonic. The first logical mnemonic is associated with the first physical mnemonic, so forth for the 2nd, up until the last.

- Brackets indicates a list, most significant to least significant.

- The ":" character indicates a continuous range between 2 values.

- The "," character separates non-contiguous values.

- There are some cases where more than one logical mnemonic maps to a single physical mnemonic.

Note that it is implied that the MSR {lthree,core,thread} parameters are not part of a range.

#### Example:

NAMESP::REGNAME inst[BLOCK[5:0],BCST] aliasHOST; FFF1x00000088 x[000[B:6] 0001,00000000]

- There are 7 instances.

- NAMESP is the namespace.

- 6 instances are represented by the sub-range 000[B:6] 0001.

- \_instBCST corresponds to FFF1x00000088\_x00000000.

- \_inst BLOCK 0 corresponds to FFF1x00000088\_x00060001.

- .

- \_inst BLOCK 5 corresponds to FFF1x00000088\_x000B0001.

#### 1.4.4.5.3 MSR Access Method

The MSR parameters {lthree,core,thread} are implied by the identity of the core on which the RDMSR/WRMSR is being executed, and therefore are not represented in the physical mnemonic.

#### MSRs that are:

- per-thread have the {lthree,core,thread} parameters.

- per-core do not have the thread parameter.

- per-L3 do not have the {core,thread} parameters.

- common to all L3's do not have the {lthree,core,thread} parameters.

#### 1.4.4.5.3.1 MSR Per-Thread Example

An MSR that is per-thread has all three {lthree,core,thread} parameters and all instances have the same physical mnemonic.

| MSR0000 | _0010 [Time | Stamp | Counter] ( | TSC) | ĺ |

|---------|-------------|-------|------------|------|---|

|---------|-------------|-------|------------|------|---|

| Read-wri                                                            | Read-write, Volatile. Reset: 0000_0000_0000_0000h.                                                        |  |  |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| Core::X86::Msr::TSC_lthree[1:0]_core[3:0]_thread[1:0],[MSR00000010] |                                                                                                           |  |  |

| Bits                                                                | Bits Description                                                                                          |  |  |

| 63:0                                                                | TSC: time stamp counter. Read-write, Volatile. Reset: 0. The TSC increments at the P0 frequency. The      |  |  |

|                                                                     | TSC counts at the same rate in all P-states, all C states, S0, or S1. A read of this MSR in guest mode is |  |  |

|                                                                     | affected by Core::X86::Msr::TscRateMsr. The value (TSC/TSCRatio) is the TSC P0 frequency based            |  |  |

|                                                                     | value (as if TSCRatio == 1.0) when (TSCRatio != 1.0).                                                     |  |  |

Figure 11: Register Instance Table: MSR Example

#### 1.4.4.5.3.2 MSR Range Example

An MSR can exist as a range for a parameter other than the {lthree,core,thread} parameters.

In the following example the n parameter is a range. The \_n0 value corresponds to MSR0000\_0201, and so on.

# MSR0000 0201 [Variable-Size MTRRs Mask] (MtrrVarMask)

| Reset: 0000_0000_0000_0000h.                                                             |  |

|------------------------------------------------------------------------------------------|--|

| Core::X86::Msr::MtrrVarMask_n[7:0]_lthree[1:0]_core[3:0]; MSR0000_020[[F,D,B,9,7,5,3,1]] |  |

|                                                                                          |  |

Figure 12: Register Instance Table: MSR Range Example

#### 1.4.4.5.4 BAR Access Method

The BAR access method is indicated by a physical mnemonic that has the form PREFIXxNUMBER.

• Example: APICx0000. The BAR prefix is "APIC".

The BAR prefix represents either a constant or an expression that consists of a register reference.

#### 1.4.4.5.4.1 BAR as a Register Reference

A relocatable BAR is when the base of an IP is not a constant.

• The prefix NTBPRIBAR0 represents the base of the IP, the value of which comes from the register NBIFEPFNCFG::BASE ADDR 1 aliasHOST instNBIF0 func1[BASE ADDR].

#### NTBPRIBAR0x00000 (NTB\_SMU\_PCTRL0)

| Reset: 0000_0000h.                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------|

| NTB::NTB_SMU_PCTRL0_aliasHOSTPRI; NTBPRIBAR0x000000;<br>NTBPRIBAR0=NBIFEPFNCFG::BASE_ADDR_1_aliasHOST_instNBIF0_func1[BASE_ADDR] |

| NTB::NTB_SMU_PCTRL0_aliasHOSTSEC; NTBSECBAR0x100000;                                                                             |

| NTBSECBAR0=NBIFEPFNCFG::BASE ADDR 1 aliasHOST instNBIF2 func1[BASE ADDR]                                                         |

| NTB::NTB_SMU_PCTRL0_aliasSMN; NTBx00000000; NTB=0400_0000h                                                                       |

Figure 13: Register Instance Table: BAR as Register Reference

# 1.4.4.5.5 PCICFG Access Method

The PCICFG access method is indicated by a physical mnemonic that has the form DXXFXxNUMBER. There are 2 cases:

- Bus omitted and implied to be 00h.

- Bus represented as BXX and indicates that the bus is indicated by a register field.

#### Example:

- Example: D18F0x000. (The bus, when omitted, is implied to be 00h)

- Example: BXXD0F0x000. (The bus as an expression that includes a register reference)

#### 1.4.4.5.5.1 PCICFG Bus Implied to be 00h

#### Example:

• The absence of a B before the D14 implies that the bus is 0.

FCH::ITF::LPC::PciDevVendID\_aliasHOST; D14F3x000

Figure 14: Register Instance Table: Bus Implied to be 00h

#### 1.4.4.5.6 Data Port Access Method

A data port requires that the data port select be written before the register is accessed via the data port.

#### Example:

- The data port select value follows the "\_x".

- The data port select register follows the "DataPortWrite=".

```

DF::FabricBlockInstanceCount_inst[PIE0,BCST]_aliasHOST; D18F0x040_x[00050001,00000000]; DataPortWrite=DF::FabricConfigAccessControl

DF::FabricBlockInstanceCount_inst[PIE0,BCST]_aliasSMN; DFF0x000000040_x[00050001,00000000]; DFF0=0001_C000h;

DataPortWrite=DF::FabricConfigAccessControl

```

Figure 15: Register Instance Table: Data Port Select

#### 1.4.4.6 Register Field Format

The register field definition are all rows that follow the Bits/Description row. Each field row represents the definition of a bit range, with the bit ranges ordered from most to least significant. There are 2 columns, with the left column defining the field bit range, and the right column containing the field definition.

There are 2 field definition formats, simple and complex. If the description can be described in the simple one paragraph format then the simple format is used, else the complex format is used.

## 1.4.4.7 Simple Register Field Format

The simple register format compresses all content into a single paragraph with the following implied order:

- 1. Field name (required)

- Allowed to be Reserved. See 1.4.4.9 [Field Name is Reserved].

- "FFXSE" in the example figure.

- 2. Field title

- "fast FXSAVE/FRSTOR enable" in the example figure.

- 3. Field Access Type. See 1.4.4.10 [Field Access Type].

- In the example figure the access type is "Read-write".

- 4. Field Reset. See 1.4.4.11 [Field Reset].

- In the example figure the reset is warm reset and "0".

- 5. Field Init. See 1.4.4.12 [Field Initialization].

- 6. Field Check. See 1.4.4.13 [Field Check].

- 7. Field Valid Values, if the valid values are single bit (e.g., 0=, 1=). See 1.4.4.14 [Field Valid Values].

- In the example figure the 1= definition begins with "Enables" and ends with "mechanism".

- In the example figure there is no 0= definition.

- 8. Field description, if it is a single paragraph.

- In the example figure the field description begins with "This is" and ends with "afterwards".

All fields that don't exist are omitted.

14 FFXSE fast FXSAVE/FRSTOR enable Read-write Reset: 0. 1=Enables the fast FXSAVE/FRSTOR mechanism. A 64-bit operating system may enable the fast FXSAVE/FRSTOR mechanism if (Core::X86::Cpuid::FeatureExtIdEdx[FFXSR] == 1). This bit is set once by the operating system and its value is not changed afterwards.

Figure 16: Simple Register Field Example

# 1.4.4.8 Complex Register Field Format

Content that can't be expressed in the single paragraph format is broken out to a separate sub-row (a definition column row).

Additional sub-rows are added in the following order:

- 1. Complex expression for {Reset, AccessType, Init, Check}.

- 2. Instance specific {Reset,AccessType,Init,Check} values.

- 3. Description, if more than 1 paragraph.

- 4. Valid values, if more than 0=/1=. Or a Valid bit table. (see figure)

The following figure highlights a complex access type specification.

APerfReadOnly: read-only actual core clocks counter. Reset: 0. This register increments in proportion to the actual number of core clocks cycles while the core is in C0. See Core::X86::Msr::MPerfReadOnly. This register is not affected by writes to Core::X86::Msr::APERF.

AccessType: Core::X86::Msr::HWCR[EffFreqReadOnlyLock] ? Read-only, Volatile : Readwrite, Volatile.

Figure 17: Register Field Sub-Row for {Reset,AccessType,Init,Check}

The following figure highlights a complex description specification.

4 INVDWBINVD: INVD to WBINVD conversion. Read-write. Reset: 1. Check: 1. 1=Convert INVD to WBINVD.

**Description**: This bit is required to be set for normal operation when any of the following are true:

- · An L2 is shared by multiple threads.

- An L3 is shared by multiple cores.

- CC6 is enabled.

- Probe filter is enabled.

Figure 18: Register Field Sub-Row for Description

The following figure highlights a complex valid value table, used either when the field is more than 1 bit or when the definition is more than a single sentence.

| 2:1 | CpuWdtTimeBase: CPU watchdog timer time base. Read-write. Reset: 0. Specifies the time base for |                |

|-----|-------------------------------------------------------------------------------------------------|----------------|

|     | the timeout period specified in CpuWdtCountSel.                                                 |                |

|     | ValidValues:                                                                                    |                |

|     | Value                                                                                           | Description    |

|     | 00ь                                                                                             | 1.31ms         |

|     | 01b                                                                                             | 1.28us         |

|     | 10b                                                                                             | Reserved (5ns) |

|     | 11b                                                                                             | Reserved       |

Figure 19: Register Field Sub-Row for Valid Value Table

The following figure highlights a valid bit table which is used when each bit has a specific function.

|       | <u> </u>                         |                  |  |

|-------|----------------------------------|------------------|--|

| 55:52 | Reserved                         | l.               |  |

| 51:48 | SliceMask. Read-write. Reset: 0. |                  |  |

| 1     | ValidValues:                     |                  |  |

|       | Bit                              | Description      |  |

|       | [0]                              | L3 Slice 0 mask. |  |

|       | [1]                              | L3 Slice 1 mask. |  |

|       | [2]                              | L3 Slice 2 mask. |  |

|       | [3]                              | L3 Slice 3 mask. |  |

Figure 20: Register Field Sub-Row for Valid Bit Table

#### 1.4.4.9 Field Name is Reserved

When a register field name is Reserved, and it does not explicitly specify an access type, then the implied access type is "Reserved-write-as-read".

- The Reserved-write-as-read access type is:

- Reads must not depend on the read value.

- Writes must only write the value that was read.

# 1.4.4.10 Field Access Type

The AccessType keyword is optional and specifies the access type for a register field. The access type for a field is a comma separated list of the following access types.

*Table 8: AccessType Definitions*

| Term       | Description                                                                                       |  |

|------------|---------------------------------------------------------------------------------------------------|--|

| Read-only  | Readable; writes are ignored.                                                                     |  |

| Read-write | Readable and writable.                                                                            |  |

| Read       | Readable; must be associated with one of the following {Write-once, Write-1-only, Write-1-to-     |  |

|            | clear, Error-on-write}.                                                                           |  |

| Write-once | Capable of being written once; all subsequent writes have no effect. If not associated with Read, |  |

|                  | then reads are undefined.                                                                                                                                                                                                                                                                                    |  |