# AMDA

# AMD Generic Encapsulated Software Architecture (AGESATM) Interface Specification for Arch2008

Publication # 44065 Revision: 3.04

Issue Date: January 2017

#### **Specification Agreement**

This Specification Agreement (this "Agreement") is a legal agreement between Advanced Micro Devices, Inc. ("AMD") and "You" as the recipient of the attached AMD Specification (the "Specification"). If you are accessing the Specification as part of your performance of work for another party, you acknowledge that you have authority to bind such party to the terms and conditions of this Agreement. If you accessed the Specification by any means or otherwise use or provide Feedback (defined below) on the Specification, You agree to the terms and conditions set forth in this Agreement. If You do not agree to the terms and conditions set forth in this Agreement, you are not licensed to use the Specification; do not use, access or provide Feedback about the Specification.

In consideration of Your use or access of the Specification (in whole or in part), the receipt and sufficiency of which are acknowledged, You agree as follows:

- 1. You may review the Specification only (a) as a reference to assist You in planning and designing Your product, service or technology ("Product") to interface with an AMD product in compliance with the requirements as set forth in the Specification and (b) to provide Feedback about the information disclosed in the Specification to AMD.

- 2. Except as expressly set forth in Paragraph 1, all rights in and to the Specification are retained by AMD. This Agreement does not give You any rights under any AMD patents, copyrights, trademarks or other intellectual property rights. You may not (i) duplicate any part of the Specification; (ii) remove this Agreement or any notices from the Specification, or (iii) give any part of the Specification, or assign or otherwise provide Your rights under this Agreement, to anyone else.

- 3. The Specification may contain preliminary information, errors, or inaccuracies, or may not include certain necessary information. Additionally, AMD reserves the right to discontinue or make changes to the Specification and its products at any time without notice. The Specification is provided entirely "AS IS." AMD MAKES NO WARRANTY OF ANY KIND AND DISCLAIMS ALL EXPRESS, IMPLIED AND STATUTORY WARRANTIES, INCLUDING BUT NOT LIMITED TO IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, NONINFRINGEMENT, TITLE OR THOSE WARRANTIES ARISING AS A COURSE OF DEALING OR CUSTOM OF TRADE. AMD SHALL NOT BE LIABLE FOR DIRECT, INDIRECT, CONSEQUENTIAL, SPECIAL, INCIDENTAL, PUNITIVE OR EXEMPLARY DAMAGES OF ANY KIND (INCLUDING LOSS OF BUSINESS, LOSS OF INFORMATION OR DATA, LOST PROFITS, LOSS OF CAPITAL, LOSS OF GOODWILL) REGARDLESS OF THE FORM OF ACTIONWHETHER IN CONTRACT, TORT (INCLUDING NEGLIGENCE) AND STRICT PRODUCT LIABILITY OR OTHERWISE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

- 4. Furthermore, AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur.

- 5. You have no obligation to give AMD any suggestions, comments or feedback ("Feedback") relating to the Specification. However, any Feedback You voluntarily provide may be used by AMD without restriction, fee or obligation of confidentiality. Accordingly, if You do give AMD Feedback on any version of the Specification, You agree AMD may freely use, reproduce, license, distribute, and otherwise commercialize Your Feedback in any product, as well as has the right to sublicense third parties to do the same. Further, You will not give AMD any Feedback that You may have reason to believe is (i) subject to any patent, copyright or other intellectual property claim or right of any third party; or (ii) subject to license terms which seek to require any product or intellectual property incorporating or derived from Feedback or any Product or other AMD intellectual property to be licensed to or otherwise provided to any third party.

- 6. You shall adhere to all applicable U.S., European, and other export laws, including but not limited to the U.S. Export Administration Regulations ("EAR"), (15 C.F.R. Sections 730 through 774), and E.U. Council Regulation (EC) No 428/2009 of 5 May 2009. Further, pursuant to Section 740.6 of the EAR, You hereby certifies that, except pursuant to a license granted by the United States Department of Commerce Bureau of Industry and Security or as otherwise permitted pursuant to a License Exception under the U.S. Export Administration Regulations ("EAR"), You will not (1) export, re-export or release to a national of a country in Country Groups D:1, E:1 or E:2 any restricted technology, software, or source code You receive hereunder, or (2) export to Country Groups D:1, E:1 or E:2 the direct product of such technology or software, if such foreign produced direct product is subject to national security controls as identified on the Commerce Control List (currently found in Supplement 1 to Part 774 of EAR). For the most current Country Group listings, or for additional information about the EAR or Your obligations under those regulations, please refer to the U.S. Bureau of Industry and Security's website at http://www.bis.doc.gov/.

- 7. If You are a part of the U.S. Government, then the Specification is provided with "RESTRICTED RIGHTS" as set forth in subparagraphs (c) (1) and (2) of the Commercial Computer Software-Restricted Rights clause at FAR 52.227-14 or subparagraph (c) (1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.277-7013, as applicable.

- 8. This Agreement is governed by the laws of the State of California without regard to its choice of law principles. Any dispute involving it must be brought in a court having jurisdiction of such dispute in Santa Clara County, California, and You waive any defenses and rights allowing the dispute to be litigated elsewhere. If any part of this agreement is unenforceable, it will be considered modified to the extent necessary to make it enforceable, and the remainder shall continue in effect. The failure of AMD to enforce any rights granted hereunder or to take action against You in the event of any breach hereunder shall not be deemed a waiver by AMD as to subsequent enforcement of rights or subsequent actions in the event of future breaches. This Agreement is the entire agreement between You and AMD concerning the Specification; it may be changed only by a written document signed by both You and an authorized representative of AMD

#### Disclaimer

The information contained herein is for informational purposes only, and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.

#### **Trademarks**

AMD, the AMD Arrow logo, AGESA, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

HDMI is a trademark of HDMI Licensing, LLC.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Microsoft is a registered trademarks of Microsoft Corporation.

PCIe is a registered trademark of PCI-Special Interest Group (PCI-SIG).

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### Dolby Laboratories, Inc.

Manufactured under license from Dolby Laboratories.

#### **Rovi Corporation**

This device is protected by U.S. patents and other intellectual property rights. The use of Rovi Corporation's copy protection technology in the device must be authorized by Rovi Corporation and is intended for home and other limited pay-per-view uses only, unless otherwise authorized in writing by Rovi Corporation.

Reverse engineering or disassembly is prohibited.

USE OF THIS PRODUCT IN ANY MANNER THAT COMPLIES WITH THE MPEG ACTUAL OR DE FACTO VIDEO AND/OR AUDIO STANDARDS IS EXPRESSLY PROHIBITED WITHOUT ALL NECESSARY LICENSES UNDER APPLICABLE PATENTS. SUCH LICENSES MAY BE ACQUIRED FROM VARIOUS THIRD PARTIES INCLUDING, BUT NOT LIMITED TO, IN THE MPEG PATENT PORTFOLIO, WHICH LICENSE IS AVAILABLE FROM MPEG LA, L.L.C., 6312 S. FIDDLERS GREEN CIRCLE, SUITE 400E, GREENWOOD VILLAGE, COLORADO 80111.

# **AGESA**<sup>TM</sup> **Software Fundamentals**

| Chapter 1 | I     | ntroduction                          | 20 |

|-----------|-------|--------------------------------------|----|

| 1.1       | . (   | Goals                                | 20 |

| 1.2       | . A   | Audience                             | 20 |

| 1.3       | R     | Related Documents                    | 20 |

| 1.4       | r -   | erminology                           | 21 |

| Chapter 2 | L     | ogistical Matters                    | 23 |

| 2.1       | V     | Version Numbering                    | 23 |

| 2.2       | R     | delease Package                      | 24 |

| 2.3       | F     | ile Naming Convention                |    |

| 2.4       | · F   | ile headers                          |    |

| 2.5       | P     | rocedure Naming Convention           |    |

| 2.6       | i I   | nternal Documentation                | 26 |

|           | 2.6.1 | Installing the Doxygen and Dot Tools | 26 |

|           | 2.6.2 | Building the HTML files              | 26 |

| Chapter 3 | 3 I   | Design Concepts                      | 27 |

| 3.1       | I     | nterface Design Theory               | 27 |

|           | 3.1.1 | Required versus Optional Parameters  | 27 |

|           | 3.1.2 | Call Mechanics                       | 27 |

|           | 3.1.3 | Error Reporting                      | 29 |

| 3.2       | E E   | Build Design Theory                  | 29 |

|           | 3.2.1 | Control Files                        | 30 |

|           | 3.2.2 | Build Styles                         | 31 |

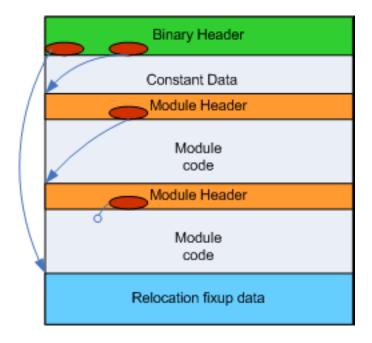

| 3.3       | E     | Sinary Image Design                  | 31 |

|           | 3.3.1 | Binary Block Structure               | 31 |

|           | 3.3.2 | Execution Environment Expectations   | 32 |

|           | 3.3.3 | Standard Header                      | 33 |

| 3.4       | - E   | Sinary Image Implementation          |    |

|           | 3.4.1 | Binary Header                        |    |

|           | 3.4.2 | Module Header                        | 36 |

|           |       |                                      |    |

| 3.5       | Integrated Debug Services         |  |

|-----------|-----------------------------------|--|

| Chapter 4 | Operational Overview              |  |

| 4.1       | AGESA <sup>TM</sup> Core Software |  |

| 4.2       | Operational Warnings              |  |

| 4.3       | Reported Errors                   |  |

| 4.        | Returned Status Codes             |  |

| 4         | 3.2 Error Logging                 |  |

# **Porting Guide for Binary Module**

| Chapter 5 | Bin  | ary Module Porting                                |    |

|-----------|------|---------------------------------------------------|----|

| 5.1       | Ove  | erview                                            |    |

| 5.2       | Ten  | ms and Definitions                                |    |

| 5.3       | The  | eory of Operation                                 |    |

| 5.        | .3.1 | Calling an AGESA <sup>TM</sup> Software Procedure | 44 |

| 5.        | .3.2 | Call-Out Operation                                |    |

| Chapter 6 | The  | e Binary Module API                               | 47 |

| 6.1       | Mal  | king Calls to Core Entry Points                   |    |

|           |      | AmdAgesaDispatcher                                |    |

| 6.2       | Han  | ndling Core Call-Out Procedures                   | 49 |

|           |      | Host RIOS Router Procedure                        | 5( |

# **Porting Guide for UEFI**

| Chapter 7  | UEFI Porting                                                    | 52             |

|------------|-----------------------------------------------------------------|----------------|

| 7.1        | Overview                                                        | 52             |

| 7.2        | Tool Set                                                        | 53             |

| 7.3        | Configuration Options                                           | 53             |

| 7          | 3.1 Build Time Options                                          | 53             |

| 7          | 3.2 Run Time Options                                            | 53             |

| 7.4        | Build Environment Installation                                  | 54             |

| Chapter 8  | The SEC Phase                                                   | 55             |

| Chapter 9  | The PEI Drivers                                                 | 56             |

| 9.1        | AmdProcessorInitPeim                                            | 57             |

| 0.2        | AmdInitResetPPI AmdInitEarlyPPI AmdInitPostPPI AmdMemoryInfoHob | 59<br>60<br>61 |

| 9.2        | AmdInitPostPeim                                                 |                |

| 9.3        | MemoryInitPPI                                                   |                |

| Chapter 10 | The DXE Driver                                                  | 66             |

|            | AgesaDxeProtocol                                                |                |

| Chapter 11 | UEFI Porting Check List                                         | 69             |

| 11.1       | Example Files                                                   | 69             |

| 11.2       | Build Control Files                                             | 69             |

| 11.3       | Environment Variables                                           | 70             |

| 11.4       | UEFI Check List                                                 | 70             |

# **API Specification**

| Chapter 12 | Introduction                                                                                                                                                                 | 71                                     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 12.1       | Platform solutions                                                                                                                                                           | 71                                     |

| 12.2       | Build Methods                                                                                                                                                                | 71                                     |

| 12.3       | Build Customization                                                                                                                                                          | 71                                     |

| Chapter 13 | Service Procedures                                                                                                                                                           | 73                                     |

| 13.1       | Stack Procedures                                                                                                                                                             | 73                                     |

|            | AMD_RESET_ENABLEMENT                                                                                                                                                         | 75<br>78                               |

| 13.2       | General Service Procedures                                                                                                                                                   |                                        |

|            | AmdCreateStruct AmdGet2DDataEye AmdGetApicId AmdGetAvailableExeCacheSize AmdGetPciAddress AmdIdentifyCore AmdIdentifyDimm AmdAddMmioMapping AmdReadEventLog AmdReleaseStruct | 83<br>85<br>88<br>90<br>92<br>94<br>96 |

| Chapter 14 | Entry Point Procedures                                                                                                                                                       | 99                                     |

| 14.1       | Recovery Branch Functions                                                                                                                                                    | 99                                     |

| 14.2       | AmdInitReset                                                                                                                                                                 |                                        |

|            | AmdInitEarly AmdInitPost AmdInitEnv AmdInitMid AmdInitLate AmdInitRtb                                                                                                        | 114<br>127<br>134<br>136               |

| 14.3       | Resume Branch Procedures                                                                                                                                                     |                                        |

|            | AmdInitResume                                                                                                                                                                | 145                                    |

| Chapter 15 | Call-Out Procedures                                                                                                                                                          | 149                                    |

| 15.1       | Requir            | red Call-Out Procedures                                                                                                                                                                                                               | 149                                           |

|------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 15.2       | Option            | AgesaAllocateBuffer AgesaDeallocateBuffer AgesaDoReset AgesaLocateBuffer AgesaReadSpd AgesaRunFcnOnAp AgesaRunFcnOnAllAps AmdLateRunApTask AgesaPcieSlotResetControl AgesaWaitForAllApsFinished AgesaIdleAnAp nal Call-Out Procedures | 152154156158161163164166                      |

|            |                   | AgesaGetIdsData AgesaHeapRebase AgesaHookBeforeDramInit AgesaHookBeforeDQSTraining AgesaExternal2dTrainVrefChange AgesaHookBeforeExitSelfRefresh AgesaGetVbiosImage AgesaFchOemCallout AgesaExternalVoltageAdjust AgesaGnbOemCallout  | 170<br>172<br>173<br>174<br>175<br>176<br>177 |

| Chapter 16 | Custon            | mizing Platforms                                                                                                                                                                                                                      | 181                                           |

| 16.1       | Build (           | Options                                                                                                                                                                                                                               | 181                                           |

| 16.2       | Build (           | Configuration Elements                                                                                                                                                                                                                | 186                                           |

| 16         | 5.2.1             | Platform Descriptive Elements                                                                                                                                                                                                         | 187                                           |

| 16         | 16.2.1.1<br>5.2.2 | Voltage Regulation Module Elements                                                                                                                                                                                                    |                                               |

| 16         | 5.2.3             | Software Table Elements                                                                                                                                                                                                               | 190                                           |

| 16         | 5.2.4             | Processor and General Elements                                                                                                                                                                                                        | 191                                           |

| 16         | 5.2.5             | Memory Elements                                                                                                                                                                                                                       | 196                                           |

|            | 16.2.5.1          | Memory Configuration Elements                                                                                                                                                                                                         | 196                                           |

| 16         | 16.2.5.2<br>5.2.6 | Memory Operations Elements                                                                                                                                                                                                            |                                               |

| 16         | 5.2.7             | HD Audio Elements                                                                                                                                                                                                                     | 209                                           |

|            | 16.2.7.1          | Analog HD Audio                                                                                                                                                                                                                       | 209                                           |

|            | 16.2.7.2          | Digital HD Audio                                                                                                                                                                                                                      |                                               |

| 16   | 5.2.8         | Graphics and PCIe <sup>®</sup> Elements     |     |

|------|---------------|---------------------------------------------|-----|

| 16   | 5.2.9         | FCH Elements                                | 216 |

| 16.3 | Custo         | omizing the Environment — Library Functions |     |

|      |               | LibAmdCpuidRead                             |     |

|      |               | LibAmdIoRead                                |     |

|      |               | LibAmdIoWrite                               |     |

|      |               | LibAmdLocateImage                           |     |

|      | LibAmdMemCopy |                                             |     |

|      |               | LibAmdMemFill                               |     |

|      |               | LibAmdMemRead                               |     |

|      |               | LibAmdMemWrite                              |     |

|      |               | LibAmdMsrRead                               |     |

|      |               | LibAmdMsrWrite                              |     |

|      |               | LibAmdPciRead                               |     |

|      |               | LibAmdPciWrite                              |     |

# **Integrated Debug Services (IDS)**

| Chapter 17 | IDS Overview                                                                                                                                                                                           | 230 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 17.1       | Goals                                                                                                                                                                                                  | 230 |

| 17.2       | Capabilities                                                                                                                                                                                           | 230 |

| 17.3       | Host Environment                                                                                                                                                                                       | 231 |

| 17.4       | Installation and Configuration                                                                                                                                                                         | 232 |

| Chapter 18 | IDS Macros                                                                                                                                                                                             | 234 |

|            | AGESA_TESTPOINT STOP_HERE ASSERT IDS_ERROR_TRAP IDS_OPTION_HOOK IDS_SKIP_HOOK IDS_HDT_CONSOLE CONSOLE IDS_HDT_CONSOLE_INIT IDS_HDT_CONSOLE_EXIT IDS_PERF_TIMESTAMP IDS_PERF_ANALYSE IDS_EXCEPTION_TRAP |     |

| Chapter 19 | IDS Configuration Controls                                                                                                                                                                             | 248 |

| 19.1       | IDS Build Switches                                                                                                                                                                                     | 248 |

| 19.2       | UI Interface Controls                                                                                                                                                                                  | 249 |

| 19         | O.2.1 Configuration Controls                                                                                                                                                                           | 249 |

|            | 19.2.1.1 Processor Core Controls                                                                                                                                                                       | 249 |

| 19         | 19.2.1.2 Memory Cache & ECC Controls                                                                                                                                                                   |     |

| 19         | P.2.3 Performance Analysis Controls                                                                                                                                                                    | 254 |

| 19.3       | Build Switch Hierarchy                                                                                                                                                                                 | 254 |

| Chapter 20 | IDS Porting                                                                                                                                                                                            | 256 |

| 20.1       | Check List                                                                                                                                                                                             | 256 |

| 20.2       | Example                                                                                                                                                                                                | 256 |

| 20.3       | Debugging Using IDS                                                                                                                                                                                    | 257 |

| Chapter 21 | HDT Console                                                                                                                                                                                            | 259 |

| AGES  | ATM /       | 1 mai      | L2   | $\alpha$ | 8                 |

|-------|-------------|------------|------|----------|-------------------|

| ALTEN | 4 1 1 1 1 / | <i>rci</i> | n /. | ()()     | $^{\prime\prime}$ |

| 44065       | Rev. 3.04  | January 2017 |

|-------------|------------|--------------|

| <del></del> | 1CCV. J.OT | January 2017 |

| 21.1 | Starting an HDT Console debug session | 259 |

|------|---------------------------------------|-----|

| 21.2 | Available Scripts                     |     |

# **Appendices**

| Appendix A | Family Specific Details                         | .263 |

|------------|-------------------------------------------------|------|

| A.1        | Family 15h Models 30h-3Fh                       | .263 |

| A.         | 1.1 Call Entries & parameters                   | .263 |

| A.2        | Family 15h Models 60h-6Fh                       | .264 |

| A.:        | 2.1 Call Entries & parameters                   | .264 |

| A.:        | 2.2 Configuration elements                      | .268 |

|            | A.2.2.1 Memory Elements                         | .268 |

|            | A.2.2.2 Thermal and Power Control Elements      | .271 |

|            | A.2.2.3 HD Audio Elements                       | .273 |

|            | A.2.2.4 Graphics and PCIe <sup>®</sup> Elements | .275 |

| A.3        | A.2.2.4.1 High Speed HDMI Controls              |      |

| A.:        | 3.1 Call Entries & parameters                   | .278 |

| A.:        | Configuration elements                          | .278 |

|            | A.3.2.1 Thermal and Power Control Elements      | .278 |

|            | A.3.2.1.1 Elements for DcTDP_V2.0               | .280 |

|            | A.3.2.2 Graphics and PCIe <sup>®</sup> Elements | .282 |

| Appendix B | Tools                                           | .284 |

| B.1        | BINUTIL2                                        | .284 |

| Appendix C | Logged Error Messages                           | .285 |

| C.1        | AGESA_SUCCESS Class                             | .285 |

| C.2        | AGESA_BOUNDS_CHK Class                          | .286 |

| C.3        | AGESA_ALERT Class                               | .287 |

| C.4        | AGESA_WARNING Class                             | .287 |

| C.5        | AGESA_ERROR Class                               | .290 |

| C.6        | AGESA_CRITICAL Class                            | .296 |

| C.7        | AGESA_FATAL Class                               | .296 |

| Appendix D | Memory Details                                  | .299 |

| D.1        | Modifying or Correcting SPD values              | .299 |

| D.2        | Specialized Platform Files                      | .299 |

|     |         | MemAGetPsCfgRHy2                        |     |

|-----|---------|-----------------------------------------|-----|

| D.3 | Advan   | MemAGetPsCfgRHy3ced DQS Training        |     |

| D.4 |         | ne Spares                               |     |

| D.5 | Platfor | m Specific Override                     | 302 |

| D   | .5.1    | Expert Overrides                        |     |

| D   | .5.1    | •                                       |     |

|     |         | MOTHER_BOARD_LAYERS                     |     |

|     |         | ON_DIMM_THERMAL_CONTROL                 |     |

|     |         | CKE_TRI_MAP                             |     |

|     |         | ODT_TRI_MAP                             | 308 |

|     |         | CS_TRI_MAP                              |     |

|     |         | NUMBER_OF_DIMMS_SUPPORTED               |     |

|     |         | NUMBER_OF_SOLDERED_DOWN_DIMMS_SUPPORTED |     |

|     |         | NUMBER_OF_CHIP_SELECTS_SUPPORTED        |     |

|     |         | NUMBER_OF_CHANNELS_SUPPORTED            |     |

|     |         | OVERRIDE_DDR_BUS_SPEED                  |     |

|     |         | DRAM_TECHNOLOGY                         |     |

|     |         | WRITE_LEVELING_SEED                     |     |

|     |         | NO_LRDIMM_CS67_ROUTING                  |     |

|     |         | DQS_ROUTING_TYPE                        |     |

|     |         | SOLDERED_DOWN_SODIMM_TYPE               |     |

|     |         | MIN_RD_WR_DATAEYE_WIDTH                 |     |

|     |         | CPU_FAMILY_TO_OVERRIDE                  |     |

| D   | .5.2    | Conditional Overrides                   |     |

|     | D.5.2.1 | Condition and Test Macros               | 323 |

|     | D.J.2.1 | CONDITION_AND                           |     |

|     |         | COND_LOC                                |     |

|     |         | COND_SPD                                |     |

|     | D.5.2.2 | Conditional Action Macros               | 326 |

|     |         | ACTION_ODT                              |     |

|     |         | ACTION_ADDRTMG                          |     |

|     |         | ACTION_ODCCTRL                          | 329 |

|     |         | ACTION_SLEWRATE                         | 330 |

|     |         | ACTION_SPEEDLIMIT                       |     |

| D   | 0.5.3   | Table Overrides                         | 331 |

|     | D.5.3.1 | Configuration Macros                    |     |

|     |         | TBLDRV_CONFIG_TO_OVERRIDE               |     |

|     |         | TBLDRV_SPEEDLIMIT_CONFIG_TO_OVERRIDE    |     |

|     |         | TBLDRV_RC2IBT_CONFIG_TO_OVERRIDE        | 335 |

|       |       | D.5.3.2              | Override Macros                                     |     |

|-------|-------|----------------------|-----------------------------------------------------|-----|

|       |       |                      | TBLDRV_CONFIG_ENTRY_SPEEDLIMIT                      |     |

|       |       |                      | TBLDRV_CONFIG_ENTRY_ODT_RTTNOM                      |     |

|       |       |                      | TBLDRV_CONFIG_ENTRY_ODT_RTTWR                       |     |

|       |       |                      | TBLDRV_CONFIG_ENTRY_ODTPATTERN                      |     |

|       |       |                      | TBLDRV_CONFIG_ENTRY_ADDRTMG                         |     |

|       |       |                      | TBLDRV_CONFIG_ENTRY_ODCCTRL                         |     |

|       |       |                      | TBLDRV_CONFIG_ENTRY_SLOWACCMODE                     |     |

|       |       |                      | TBLDRV_CONFIG_ENTRY_RC2_IBT                         |     |

|       |       |                      | TBLDRV_OVERRIDE_MR0_VR                              |     |

|       |       |                      | TBLDRV_OVERRIDE_NRO_WR TBLDRV_OVERRIDE_RC10_OPSPEED |     |

|       |       |                      | TBLDRV_CONFIG_ENTRY_LRDMM_IBT                       |     |

|       |       |                      | TBLDRV_CONFIG_ENTRY_2D_TRAINING                     |     |

|       |       |                      | TBLDRV_INVALID_CONFIG                               |     |

| Appen | dix E | Graphics             | Northbridge Details                                 | 351 |

|       | E.1   | PCIe <sup>®</sup> Po | rt Descriptor List                                  | 351 |

|       | E.2   | DDI Link             | Descriptor List                                     | 355 |

|       | E.3   | PCIe <sup>®</sup> En | gine Data                                           | 357 |

|       | E.4   | IOMMU I              | Exclusion Range Descriptor                          | 358 |

|       | E.5   | ACPI AS              | Library                                             | 358 |

|       | E.5   | 5.1 O <sub>I</sub>   | otional ACPI Callout Method                         | 365 |

|       | E.5   | 5.2 AV               | WAK and APTS Methods                                | 366 |

# **List of Figures**

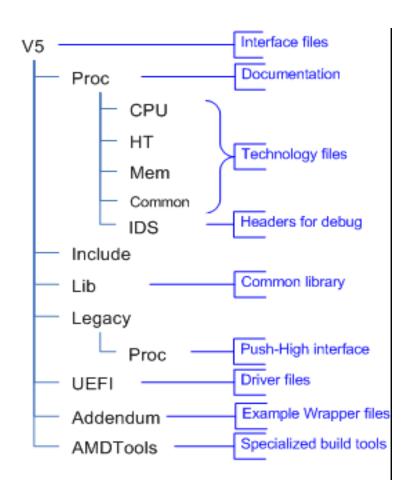

| Figure 2.1: | Package Directory Structure             | 24 |

|-------------|-----------------------------------------|----|

| Figure 3.2: | Interface Call Flow                     | 28 |

| Figure 3.3: | Build Design Diagram                    | 30 |

| Figure 3.4: | Binary Image Layout                     | 32 |

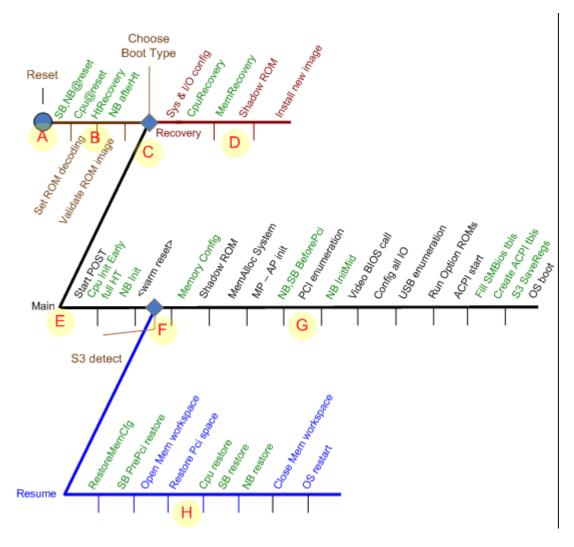

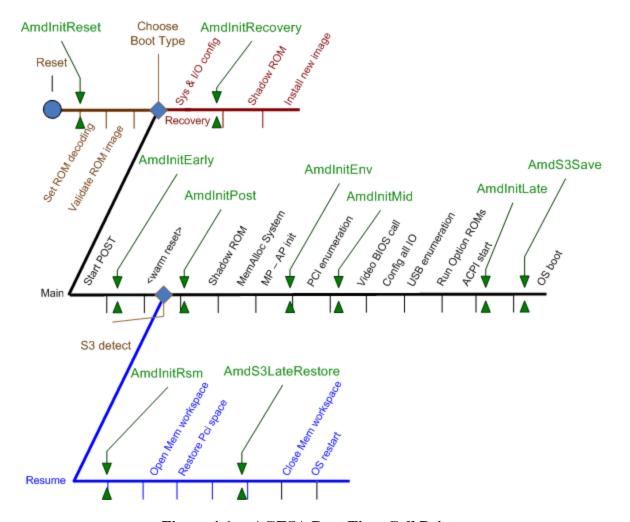

| Figure 4.5: | General Boot Time Line                  | 38 |

| Figure 4.6: | AGESA Boot Time Call Points             | 40 |

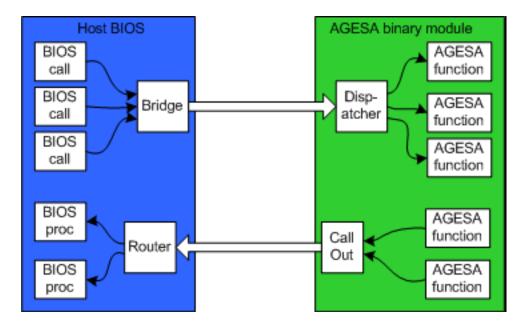

| Figure 5.7: | Funneling Overview                      | 44 |

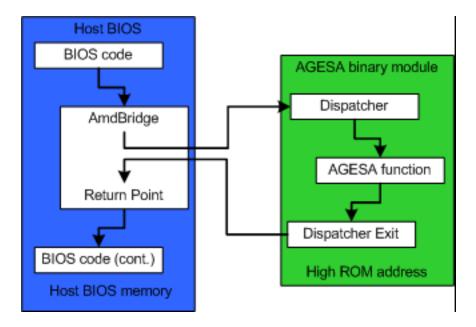

|             | Making a ROM image Call                 |    |

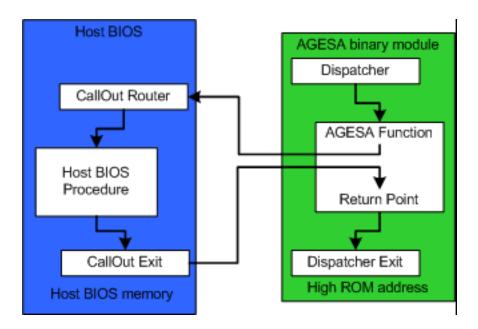

| Figure 5.9: | Handling a Call-Out                     | 46 |

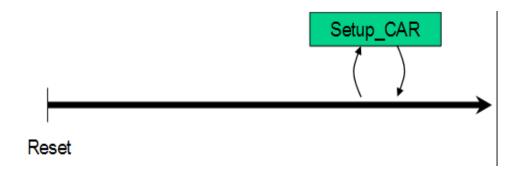

| Figure 8.1: | Overview of AMD SEC components          | 55 |

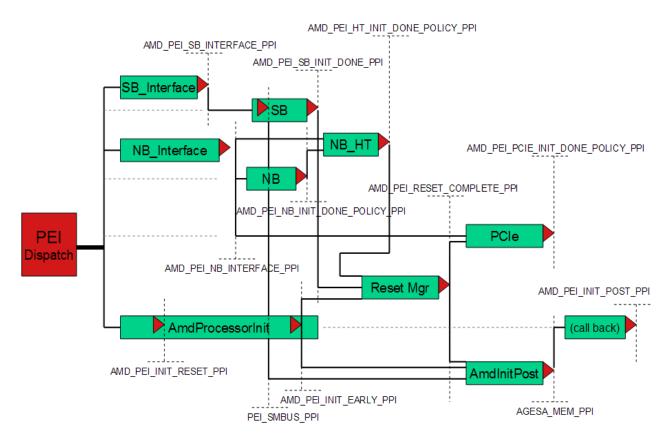

|             | Overview of AMD PEI module interactions |    |

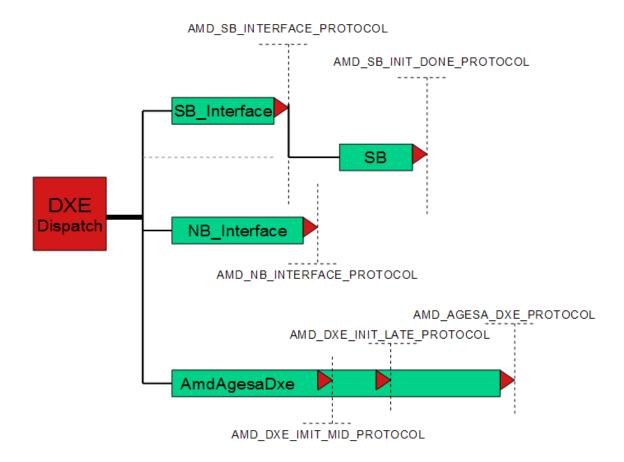

| _           | Overview of AMD DXE driver interaction  |    |

| C           | IDS overview                            |    |

### **Revision History**

Note: The latest version of the document is intended to describe the interface as it is implemented for the currently shipping processor(s). Previous generations of the spec will best describe the interface for previous generations of processors.

| Date            | Revision | Description                                                                                                                                                                                        |

|-----------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January<br>2017 | v3.04    | Public release. Updates for Family 15h Model 60-6Fh processor.                                                                                                                                     |

|                 |          | Clarified description for "BLDCFG_SYSTEM_CONFIGURATION" on page 273                                                                                                                                |

|                 |          | PLAT-6743: Add SMU Overclocking controls <ul> <li>added "SmuOverclocking" on page 266</li> <li>added "BLDCFG_SMU_OVERCLOCKING" on page 273</li> <li>removed previously deprecated text.</li> </ul> |

|                 |          | PLAT-7721: add PSO item for DQS routing type  • added "DQS_ROUTING_TYPE" on page 319                                                                                                               |

|                 |          | Plat-10407: Add the LoadPkePowerParameters to the ALIB DPTCi function  updated "Power or Thermal Parameter" on page 365                                                                            |

|                 |          | Plat-7844: BIOS pass setting to driver for HDMI  updated "High Speed HDMI Controls" on page 275                                                                                                    |

|                 |          | Added note about applicable Families for "AgesaReadSpd" on page 158                                                                                                                                |

| March 2015      | v3.02    | Public release. Updated for the Family 15h Model 60-6Fh processor.                                                                                                                                 |

|                 |          | DCR462647: Add build option for memroy extended temp range     added "EnableExtendedTemperatureRange" on page 118,     added "BLDCFG_MEMORY_EXTENDED_TEMPERATURE_RANGE" on page 204.               |

|                 |          | DCR 463315: Add build options for JEDEC DDR3/4 SPD MAC  • added "DramMacDefault" on page 118,  • added "BLDCFG_MEMORY_ALTERNATIVE_MAX_ACTIVATE_COUNT" on page 203.                                 |

|                 |          | DCR462687: Support for custom VDDIO  • added "CustomVddioSupport" on page 267,  • added "BLDCFG_CUSTOM_VDDIO_VOLTAGE" on page 270                                                                  |

|                 |          | DCR462761: Add Memory Fatal Error Code MEM_ERROR_VDDPVDDR_UNSUPPORTED  • updated "AGESA_ERROR Class" on page 290                                                                                   |

| T |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | DCR439310: New Agesa call out functions  added "AllAPs" on page 162,  added "AgesaRunFcnOnAllAps" on page 161,  added "AgesaWaitForAllApsFinished" on page 166,  added "AgesaIdleAnAp" on page 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | DCR450871: Add - BLDCFG_MEMORY_ENABLE_BANK_SWAP_ONLY  • added "EnableBankSwapOnly" on page 267,  • added "BLDCFG_MEMORY_ENABLE_BANK_SWAP_ONLY" on page 268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | DCR462007 AGESA GNB interface changes  added "PkgPwrLimitAC" on page 265,  added "BLDCFG_PPT_LIMIT_AC" on page 271,  added "BLDCFG_PPT_LIMIT_DC" on page 272,  added "BLDCFG_PPT_LIMIT_DC" on page 272  added "BLDCFG_VRM_GFX_CURRENT_LIMIT" on page 187,  added "BLDCFG_VRM_GFX_CURRENT_LIMIT" on page 187,  added "BLDCFG_VRM_GFX_LOW_POWER_THRESHOLD" on page 188,  added "BLDCFG_VRM_GFX_SLEW_RATE" on page 188,  added "BLDCFG_VRM_GFX_HIGH_SPEED_ENABLE" on page 188,  added "BLDCFG_VRM_GFX_SVI_OCP_LEVEL" on page 189,  updated "BLDCFG_STAPM_GFX_SVI_OCP_LEVEL" on page 272,  added "BLDCFG_STAPM_SCALAR" on page 272,  added "BLDCFG_STAPM_TIME_CONSTANT" on page 273,  updated "BLDCFG_STAPM_TIME_CONSTANT" on page 273,  added "BLDCFG_SYSTEM_CONFIGURATION" on page 273,  Added "Dynamic Power and Thermal Configuration Interface  - Function C" on page 364,  updated "PCle® Port Descriptor List" on page 351,  added "BLDCFG_DP_FIXED_VOLT_SWING" on page 275  Moved controls to family specific appendix:  *BLDCFG_DD_C_DCKED  *BLDCFG_TDP_AC_DOCKED  *BLDCFG_TDP_AC_DOCKED  *BLDCFG_TDP_AC_UNDOCKED  *BLDCFG_STAPM_EN_AC_DOCKED  *BLDCFG_STAPM_EN_AC_UNDOCKED  *BLDCFG_STAPM_POWER_AC_UNDOCKED  *BLDCFG_STAPM_SOME_CUNDOCKED  *BLDCFG_STAPM_SOME_CUNDOCKED  *BLDCFG_STAPM_SOME_CUNDOCKED  *BLDCFG_STAPM_SOME_CUNDOCKED  *BLDCFG_STAPM_SOME_CUNDOCKED  *BLDCFG_STAPM_SOME_CUNDOCKED  *BLDCFG_STAPM_SOME_CUNDOCKED  *BLDC |

|   | •BLDCFG_NUM_GFX_CORES_ENABLED •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           |       | DCR460803 Add BLDCFG_GNB_AZ_SSID DCR457447 Add BLDCFG_CODEC_VERB_TABLE  • added parameters to "} PLATFORM_CONFIGURATION;" on page 105,  • added "BLDCFG_CODEC_VERB_TABLE" on page 273,  • added "BLDCFG_GNB_AZ_SSID" on page 275                                                                                                                                                    |

|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |       | R453240: Add BLDCFG_THERMCTL_LIMIT and drop BLDCFG_HTC_TEMPERATURE_LIMIT  • added "BLDCFG_THERMCTL_LIMIT" on page 271  • "ThermCtlLimit" on page 264  • Moved HTC & LHTC controls to family specific appendix: • "BLDCFG_HTC_TEMPERATURE_LIMIT" on page 279  • "BLDCFG_LHTC_TEMPERATURE_LIMIT" on page 279                                                                          |

|           |       | DCR444573: Arch2008: Add interface option for users to specific Memory Power Policy  • Added "MemoryPowerPolicy" on page 264  • "BLDCFG_MEMORY_POWER_POLICY_MODE" on page 268                                                                                                                                                                                                       |

|           |       | DCR435568 Deprecate BLDCFG_BATTERY_BOOST_EN  • Moved option to Family specific appendix:  "BLDCFG_BATTERY_BOOST_EN" on page 278                                                                                                                                                                                                                                                     |

|           |       | DCR452365: [Arch2008] DCR for AmdMemoryInfoHob  • Added "AmdMemoryInfoHob" on page 61                                                                                                                                                                                                                                                                                               |

|           |       | DCR447127: New BLDCFG definitions for LVDS Miscellaneous controls  • Modified "LvdsMiscControl" on page 130  • Added "BLDCFG_LVDS_BIT_DEPTH" on page 215 and  "BLDCFG_LVDS_PARAM_OVERWRITE_EN" on page 215                                                                                                                                                                          |

|           |       | <ul> <li>DCR446310 - Build options for AGESA_TESTPOINT controls.</li> <li>Added "IDS_DEBUG_PORT_SIZE_IN_BYTES - sets the size of the IO cycle write for the testpoint. Options are:" on page 257,</li> <li>"IDS_DEBUG_TP_PERFIX - Sets the value of a prefix set of bytes to be used in the upper bytes of the IO write to identify the source of the code." on page 257</li> </ul> |

|           |       | Updated the Related Documents section Removed text previously marked as deprecated.                                                                                                                                                                                                                                                                                                 |

| July 2014 | v3.00 | Initial public release. Updated for the Family 16h Model 30-3Fh processor and Family 15h Model 30-3Fh processor.                                                                                                                                                                                                                                                                    |

|           |       |                                                                                                                                                                                                                                                                                                                                                                                     |

# **Section I - AGESA<sup>TM</sup> Software Fundamentals**

# **Chapter 1** Introduction

The AMD Generic Encapsulated Software Architecture (AGESA<sup>TM</sup>) software is a BIOS procedure library designed to aid AMD customers to quickly implement AMD technology into their products.

This document covers the interface definition for the procedure library and provides some guidelines on how to use the library in the customer's environment. The library is designed to support multiple AMD products. This chapter explains the goals of the AGESA<sup>TM</sup> software.

#### 1.1 Goals

The goal of this document is to provide a user-level description of the procedures and abilities of the AGESA<sup>TM</sup> software library.

#### 1.2 Audience

This document is directed to the host environment wrapper implementer. It defines procedure call interfaces, specifies a recommended wrapper implementation and describes options that the wrapper implementer may choose to use. Some knowledge of BIOS programming practices is required.

## 1.3 Related Documents

Following is a list of related AMD documents:

- BIOS and Kernel Developer's Guides (BKDG)

- BIOS and Kernel Developer's Guide for AMD Family 14h Models 00h-0Fh Processors, order# 43170

- BIOS and Kernel Developer's Guide for AMD Family 15h Models 10h-1Fh Processors, order# 42300

- BIOS and Kernel Developer's Guide for AMD Family 16h Models 00h-0Fh Processors, order# 48751

- BIOS and Kernel Developer's Guide for AMD Family 16h Models 30h-3Fh Processors, order# 52740

- BIOS and Kernel Developer's Guide for AMD Family 15h Models 30h-3Fh Processors, order# 49125

- BIOS and Kernel Developer's Guide for AMD Family 15h Models 60h-6Fh Processors, order# 50742

- Revision Guides

- Revision Guide for AMD Family 14h Models 00h-0Fh Processors, order# 47534

- Revision Guide for AMD Family 15h Models 10h-1Fh Processors, order# 48931

- Revision Guide for AMD Family 16h Models 00h-0Fh Processors, order# 51810

- Revision Guide for AMD Family 16h Models 30h-3Fh Processors, order# 53072

- Revision Guide for AMD Family 15h Models 30h-3Fh Processors, order# 51603

- Revision Guide for AMD Family 15h Models 60h-6Fh Processors, order# 53564

- CPUID Specification, order# 25481

- Processor Design Guides

- Processor Functional Data Sheet

Related industry standards documents:

- DDR3 SDRAM Standard (JESD79-3F), July 2012.

- Advanced Configuration and Power Interface Specification, (ACPI) revision 5.0

- System Management BIOS (SMBIOS) Reference Specification, DMTF DSP0134, Version 2.8.0

- MultiProcessor Specification (MP Spec), Intel corp., version 1.4

- C Coding Standards Specification, UEFI consortium, USWG, v0.3

# 1.4 Terminology

The following definitions, acronyms and terms are used in this specification:

| TT . TO .                 | CC1          | C 1               | '1 1 C            | •           |

|---------------------------|--------------|-------------------|-------------------|-------------|

| Host Environment          | The main hod | y of code respons | ible for power-up | seallencing |

| 1105t Ellivii ollillellit | The main oou | y of code respons | IDIC IDI POWCI UP | bequenting  |

and initialization of the platform. This can be one of many code

bases in today's technical markets.

Link A HyperTransport<sup>TM</sup> technology connection between two

devices.

MCT Name used to refer to the memory controller and the memory

controller initialization code.

Node Refers to a processor or other device actively participating in

the HyperTransport link coherent fabric.

Socket Physical connector on the motherboard into which a processor

can be installed. Sockets are numbered relative to the system or motherboard and are software-identified by the SA[2:0] pins.

Processor AMD silicon product which fits into a socket and may contain

one or more die.

Die With the advent of Multi-Chip-Modules (MCM), a single

processor may contain more than one silicon wafer die. Each die may contain one or more cores. Die are numbered relative to

the processor.

Core A term used to refer to the portion of a central processing unit

which executes computational programs. Software sees each core as a separate entity even though two or more cores may physically reside in the same processor, or in the same die. Cores are numbered relative to the processor regardless of the

die on which they may be physically located.

System address Physical 40-bit address (without translations).

Wrapper The layer of code used to isolate the AGESA<sup>TM</sup> software code

from the host architecture code.

MP - Multi-Processor This refers to a programming environment in which multiple or Multi-Processing processor cores are executing code simultaneously. In such as

processor cores are executing code simultaneously. In such an environment, special programming practices must be used to communicate between processor cores and to synchronize their

operations.

BSP - Boot Strap Processor In an MP environment this is the master processor core. This

core controls what operations are allocated to the other cores.

AP - Application Processor In an MP environment this is a slave processor core that

performs operations as directed by the BSP. Once the operation is complete, the core stops execution and waits for its next

instructions from the BSP.

<Plat>Options This is a general term convention to indicate an item that is

specific to a Platform Solution. For example, when applied to a file, "<Plat>Options.c" would be interpreted as a file having the

name "MaranelloOptions.c"

BKDG A short hand reference to the BIOS and Kernel Developer's

Guides (BKDG)

# **Chapter 2** Logistical Matters

## 2.1 Version Numbering

The AGESA<sup>TM</sup> software uses a three-level version numbering scheme: X.Y.Z. This interface specification is updated along with the code and the specification version tracks with the code version except that the specification only uses a two-level version numbering scheme, X.Y, where:

| <b>X</b> - Major version number | A major version number of 0 indicates a prototype status. The   |

|---------------------------------|-----------------------------------------------------------------|

|                                 | first production ready version has a major version number of 1, |

|                                 | then increments for further changes. This number increments     |

|                                 | when a major new feature or feature set is added.               |

| Y - Minor version number        | This number is incremented when a minor change occurs in the    |

|                                 | interface specification. Example of a minor change is the       |

|                                 | addition of a new function or feature.                          |

| <b>Z</b> - Code update number   | This number is incremented for each software release. Changes   |

|                                 | at this level indicate no change has occurred in the interface. |

|                                 | Code changes are bug fixes only. Note that this number may be   |

|                                 | more than one digit long.                                       |

|                                 |                                                                 |

Incrementing a version sub-number causes all lower-level sub-numbers to revert to 0. The product name is not part of the version numbering, but it can be used to designate the full title. Take "AGESA MarG34PI V1.2.3" for example: the "AGESA MarG34PI" is the product title and the "V1.2.3" is the version number.

The version string is embedded into the code image and can be discovered by a program. The program searches the ROM image for the signature in the following structure. Once found, the program can start at the 3rd byte and use the rest of the structure as a null terminated ASCII string.

```

// AMD CODE HEADER Signatures.

#define AGESA_CODE_SIGNATURE { '!', '!', 'A', 'G', 'E', 'S', 'A', ' '}

#define CIMXNB_CODE_SIGNATURE { '!', '!', 'C', 'I', 'M', 'X', 'N', 'B' }

#define CIMXSB CODE SIGNATURE { '!', '!', 'C', 'I', 'M', 'X', 'S', 'B'}

/// AGESA_CODE_SIGNATURE

typedef struct {

CHAR8 Signature[8];  // code header Signature

TN

IN

CHAR8 ComponentName[8]; // 8 character name of the code module

ΤN

CHAR8 Version[12]; // 12 character version string

CHAR8 TerminatorNull; // = 0x00, null terminated string

CHAR8 VerReserved[7];  // reserved space

TN

} AMD CODE HEADER;

```

## 2.2 Release Package

The release package given to customers includes the following:

AGESA<sup>TM</sup> software technology core files

Binary block interfacing files

Binary compilations (all options set 'on')

Examples of user-generated files (wrapper)

Documentation (release notes)

UEFI interfacing files

Build control files

Specialized build tools

The files contained in the distribution are organized into a directory hierarchy similar to the one as shown in Figure 2.1below:

Figure 2.1: Package Directory Structure

# 2.3 File Naming Convention

The AGESA<sup>TM</sup> software complies with the *C Coding Standards Specification, UEFI consortium, USWG, v0.3* which states the core "C" code files use the long file name format. This removes any need for a cryptic naming convention, the file names are descriptive.

#### 2.4 File headers

Every source file contains a comment header describing the file function and purpose, as defined in the *C Coding Standards Specification*, *UEFI consortium*, *USWG*, *v0.3*. The following is an example comment header as used in the AGESA<sup>TM</sup> software files:

```

/**

* @file

*

* Text Title of file.

*

* Purpose of File Content.

*

* @xrefitem bom "File Content Label" "Release Content"

* @e project: AGESA

* @e sub-project: Library

* @e version: $Revision$     @e date: $Date$

*

```

This is immediately followed by the AMD copyright notice, which is not shown here. The revision number in the last line is the revision number of the individual file as recorded in the AMD source control system. This number has no relationship to the code block version number.

# 2.5 Procedure Naming Convention

All public procedures use a name prefix to assist the programmer in understanding his or her place and purpose. All call-in entry points to the AGESA<sup>TM</sup> software use a prefix: "Amd" (for example, AmdInitReset). All call-out procedures used to gather data or provide customizing opportunities use a prefix: "Agesa" (for example, AgesaReadSpd).

#### 2.6 Internal Documentation

This document describes the user interface to which the implemented code must conform. For more detailed information about the internal design or how the sub-systems work, there is internal documentation shipped with the sources in the delivery package. This internal documentation is generated from the source files using the open source tools 'Doxygen' and 'Dot'. The HTML output is quite impressive and includes linked function and structure definitions, include dependency trees, call trees and where used lists.

#### 2.6.1 Installing the Doxygen and Dot Tools

Doxygen is an open source, source code documentation generator tool. Documentation, user guides and downloads can be found at:

#### http://www.stack.nl/~dimitri/doxygen/index.html

Doxygen uses the Dot graphics generation tool to make visual diagrams and graphs of the dependency and call trees. Documentation and downloads can be found at:

http://www.graphviz.org/

#### 2.6.2 Building the HTML files

The AGESA<sup>TM</sup> software includes a Microsoft® Visual Studio SLN control file used for building the HTML internal documentation files. The build control file for the processor documentation can be found at \Proc\AgesaDoc.sln within the release package.

The documentation build can be run from the command line (see the inputs for the Legacy.Bat file) or it can be run interactively by opening MS Visual Studio with the proper environment variables established (same as needed for the code build), loading the AgesaDoc.sln file, then selecting the project 'rebuild' command. The HTML files will be placed in an Html sub-directory under the platform tip directory. An internet browser may be used to open mainpage.html in that folder.

For convenience, a single help file called *arch2008.chm* is placed at the same level as the html folder. This is the complete help output and may be used in place of the html folder content. A copy is provided within the release package.

# **Chapter 3** Design Concepts

## 3.1 Interface Design Theory

The goal for the interface is to remain a constant for several generations of processors. To accomplish this goal, the number of call entry points and the content of the interface are reduced as much as possible. The call entry points are based on the boot time line and represent time points in the boot process instead of specific technical functions. See "4.1 AGESA<sup>TM</sup> Core Software" on page 38 for more details.

#### 3.1.1 Required versus Optional Parameters

The AGESA<sup>TM</sup> software vigorously seeks to automatically determine configuration parameters for the host system. However, there are limits of technology and practicality, which means that there are still some required parameters that the host environment must provide. These parameters are identified in the call definitions. Many other parameters are available to the host environment for tailoring the configuration, but these are optional and the host environment may modify those it chooses. If not modified, the default values determined by the AGESA<sup>TM</sup> software are used. The default settings are identified in the interface definitions.

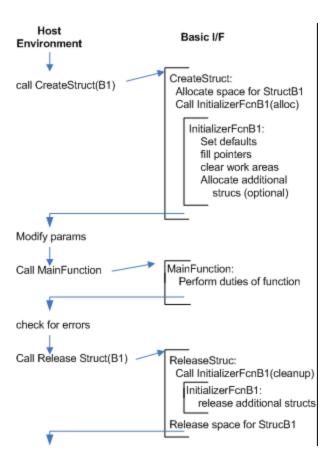

#### 3.1.2 Call Mechanics

To greatly simplify the host environment implementation of an AGESA™ software interface call, this architecture uses the concept of an "initializer" function. See Figure 3.2 on page 28. The initializer allocates space for the interface data structure and pre-fills the structure with default parameter settings. The host environment must then fill in any required parameters and may modify any additional parameters of interest. After the main function is called, the host environment checks error status, then releases the interface data structure.

Figure 3.2: Interface Call Flow

A code example for this process is as follows:

```

VOID

OemMyProcedure (UINT8 MyParam) {

AGESA_STATUS

MyStatus;

CREATE_STRUCT_PARAMS

LclConfigBlk;

AMD EARLY PARAMS

*MyPtr;

/* Fill the local Config Block */

LclConfigBlk.StdHeader.Func

= AMD_CREATE_STRUC

LclConfigBlk.StdHeader.ImageBase

= 0xFFFE0000;

LclConfigBlk.StdHeader.AltImageBase = 0x00000000;

LclConfigBlk.StdHeader.PcieBasePtr

= 0 \times 000000000i

LclConfiqBlk.StdHeader.CallBackPtr = &OemMyCbDispatcher;

LclConfigBlk.ParamStructName

= AMD EARLYINIT PARAMS;

LclConfigBlk.AllocMethod

= PREMEM_HEAP;

/* Call the AMD Initializer function */

MyStatus = AmdBridge32(&LclConfigBlk);

MyPtr = (AMD_EARLY_PARAMS *)LclConfigBlk.NewStruc;

```

```

/* OEM has chance to change parameter struct content */

MyPtr->EarlyParams.RandomParameter = MY OEM VALUE;

/* Call the AGESA main entry point */

MyPtr->StdHeader.Func = AMD EARLY INIT;

MyStatus = AmdBridge32(MyPtr);

/* Check return status */

switch (MyStatus) {

case AGESA_WARNING:

printf("Warning msg");

break;

case AGESA ERROR:

/* handle error */

/* Call to release the data structure */

LclConfigBlk.StdHeader.Func= AMD RELEASE STRUC

MyStatus = AmdBridge32(&LclConfigBlk);

};

```

All interface structure definitions are provided in an include file.

#### 3.1.3 Error Reporting

Two methods of error reporting are provided: return codes and error logs. The return codes are described in "4.3.1 Returned Status Codes" on page 41 and provide enough detail for most host environments. For more detailed error reporting, the error log system is provided (see section "4.3.2 Error Logging" on page 42 for more details).

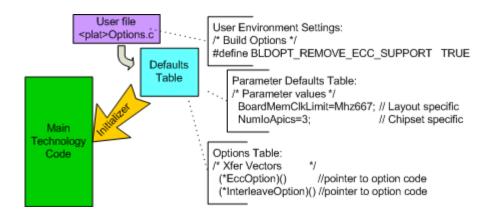

## 3.2 Build Design Theory

All pertinent data needed to select build options and to describe the target platform is contained in one user file named "<Plat>Options.c". See Figure 3.3 on page 30. This file contains a list of #define entries that are used to conditionally compile the AGESA<sup>TM</sup> software defaults tables. It is these defaults tables that are used by the "initializer" functions to pre-fill the procedure parameter data structures prior to the call to the main function as described in "3.1.2 Call Mechanics" on page 27.

Figure 3.3: Build Design Diagram

The main technology code is compiled, without #defines and without the <Plat>Options.c file. The main technology code then becomes a code library for the platform build.

The defaults tables file is compiled separately, referencing the <Plat>Options.c file. It extensively evaluates and cross checks the user options listed and outputs a data object file containing parameter data default values and reference pointers to selected option procedures. When linked with the main technology code library, the reference points cause only the desired option procedures to be included into the build. The location of this output object file must be specified to the AGESA<sup>TM</sup> module build control files.

The <Plat>Options.c file is located in a platform-specific directory according to the host environment needs. The defaults tables output file is located in the same platform-specific directory. The host environment may choose to reference it from that location or may choose to copy or move it to another directory location.

#### 3.2.1 Control Files

The AGESA<sup>TM</sup> software contains the ability to generate build control files for several code bases, including generic .mak files, UEFI descriptor files and some IBV specific files.

The control files are nested or layered to allow modular construction. The directories have a top-level control file that invokes control files from the other directories to assemble components needed for their interface.

#### 3.2.2 Build Styles

Some of the control files are designed to create binary images that can be built separately from the host environment code and merged into the final ROM image. This creates the ability to have multiple build styles:

- **Direct to module dispatcher** This style uses the separated binary image build, using a direct call to the module dispatcher entry point. The host environment must parse the binary header described in the next section to locate the module dispatcher entry point.