#### **Specification Agreement**

This Specification Agreement (this "Agreement") is a legal agreement between Advanced Micro Devices, Inc. ("AMD") and "You" as the recipient of the attached AMD Specification (the "Specification"). If you are accessing the Specification as part of your performance of work for another party, you acknowledge that you have authority to bind such party to the terms and conditions of this Agreement. If you accessed the Specification by any means or otherwise use or provide Feedback (defined below) on the Specification, You agree to the terms and conditions set forth in this Agreement. If You do not agree to the terms and conditions set forth in this Agreement. If You accessed to use the Specification; do not use, access or provide Feedback about the Specification.

In consideration of Your use or access of the Specification (in whole or in part), the receipt and sufficiency of which are acknowledged, You agree as follows:

1. You may review the Specification only (a) as a reference to assist You in planning and designing Your product, service or technology ("Product") to interface with an AMD product in compliance with the requirements as set forth in the Specification and (b) to provide Feedback about the information disclosed in the Specification to AMD.

2. Except as expressly set forth in Paragraph 1, all rights in and to the Specification are retained by AMD. This Agreement does not give You any rights under any AMD patents, copyrights, trademarks or other intellectual property rights. You may not (i) duplicate any part of the Specification; (ii) remove this Agreement or any notices from the Specification, or (iii) give any part of the Specification, or assign or otherwise provide Your rights under this Agreement, to anyone else.

3. The Specification may contain preliminary information, errors, or inaccuracies, or may not include certain necessary information. Additionally, AMD reserves the right to discontinue or make changes to the Specification and its products at any time without notice. The Specification is provided entirely "AS IS." AMD MAKES NO WARRANTY OF ANY KIND AND DISCLAIMS ALL EXPRESS, IMPLIED AND STATUTORY WARRANTIES, INCLUDING BUT NOT LIMITED TO IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, NON-INFRINGEMENT, TITLE OR THOSE WARRANTIES ARISING AS A COURSE OF DEALING OR CUSTOM OF TRADE. AMD SHALL NOT BE LIABLE FOR DIRECT, INDIRECT, CONSE-QUENTIAL, SPECIAL, INCIDENTAL, PUNITIVE OR EXEMPLARY DAMAGES OF ANY KIND (INCLUDING LOSS OF BUSINESS, LOSS OF INFORMATION OR DATA, LOST PROF-ITS, LOSS OF CAPITAL, LOSS OF GOODWILL) REGARDLESS OF THE FORM OF ACTION WHETHER IN CONTRACT, TORT (INCLUDING NEGLIGENCE) AND STRICT PRODUCT LIABILITY OR OTHERWISE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAM-AGES.

4. Furthermore, AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur.

5. You have no obligation to give AMD any suggestions, comments or feedback ("Feedback") relating to the Specification. However, any Feedback You voluntarily provide may be used by AMD without restriction, fee or obligation of confidentiality. Accordingly, if You do give AMD Feedback on

any version of the Specification, You agree AMD may freely use, reproduce, license, distribute, and otherwise commercialize Your Feedback in any product, as well as has the right to sublicense third parties to do the same. Further, You will not give AMD any Feedback that You may have reason to believe is (i) subject to any patent, copyright or other intellectual property claim or right of any third party; or (ii) subject to license terms which seek to require any product or intellectual property incorporating or derived from Feedback or any Product or other AMD intellectual property to be licensed to or otherwise provided to any third party.

6. You shall adhere to all applicable U.S., European, and other export laws, including but not limited to the U.S. Export Administration Regulations ("EAR"), (15 C.F.R. Sections 730 through 774), and E.U. Council Regulation (EC) No 428/2009 of 5 May 2009. Further, pursuant to Section 740.6 of the EAR, You hereby certifies that, except pursuant to a license granted by the United States Department of Commerce Bureau of Industry and Security or as otherwise permitted pursuant to a License Exception under the U.S. Export Administration Regulations ("EAR"), You will not (1) export, re-export or release to a national of a country in Country Groups D:1, E:1 or E:2 any restricted technology, software, or source code You receive hereunder, or (2) export to Country Groups D:1, E:1 or E:2 the direct product of such technology or software, if such foreign produced direct product is subject to national security controls as identified on the Commerce Control List (currently found in Supplement 1 to Part 774 of EAR). For the most current Country Group listings, or for additional information about the EAR or Your obligations under those regulations, please refer to the U.S. Bureau of Industry and Security's website at <a href="http://www.bis.doc.gov/">http://www.bis.doc.gov/</a>.

7. If You are a part of the U.S. Government, then the Specification is provided with "RESTRICTED RIGHTS" as set forth in subparagraphs (c) (1) and (2) of the Commercial Computer Software-Restricted Rights clause at FAR 52.227-14 or subparagraph (c) (1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.277-7013, as applicable.

8. This Agreement is governed by the laws of the State of California without regard to its choice of law principles. Any dispute involving it must be brought in a court having jurisdiction of such dispute in Santa Clara County, California, and You waive any defenses and rights allowing the dispute to be litigated elsewhere. If any part of this agreement is unenforceable, it will be considered modified to the extent necessary to make it enforceable, and the remainder shall continue in effect. The failure of AMD to enforce any rights granted hereunder or to take action against You in the event of any breach hereunder shall not be deemed a waiver by AMD as to subsequent enforcement of rights or subsequent actions in the event of future breaches. This Agreement is the entire agreement between You and AMD concerning the Specification; it may be changed only by a written document signed by both You and an authorized representative of AMD.

#

# AMD I/O Virtualization Technology (IOMMU) Specification

Publication # 48882-PUBRevision: 3.10Issue Date:February 2025

#### © 2011 – 2025 Advanced Micro Devices Inc. All rights reserved.

The information contained herein is for informational purposes only, and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.

Any unauthorized copying, alteration, distribution, transmission, performance, display or other use of this material is prohibited.

#### Trademarks

AMD, the AMD Arrow logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies. HyperTransport is a licensed trademark of the HyperTransport Technology Consortium

PCI Express, PCIe and PCI-X are registered trademarks of PCI-Special Interest Group (PCI-SIG).

Reverse engineering or disassembly is prohibited.

USE OF THIS PRODUCT IN ANY MANNER THAT COMPLIES WITH THE MPEG ACTUAL OR DE FACTO VIDEO AND/OR AUDIO STANDARDS IS EXPRESSLY PROHIBITED WITHOUT ALL NECESSARY LICENSES UNDER APPLICABLE PATENTS. SUCH LICENSES MAY BE ACQUIRED FROM VARIOUS THIRD PARTIES INCLUDING, BUT NOT LIMITED TO, IN THE MPEG PATENT PORTFOLIO, WHICH LICENSE IS AVAILABLE FROM MPEG LA, L.L.C., 6312 S. FIDDLERS GREEN CIRCLE, SUITE 400E, GREENWOOD VILLAGE, COLORADO 80111.

## Contents

|   | Cont | ents     |                                                                          | 5  |

|---|------|----------|--------------------------------------------------------------------------|----|

|   | Figu | res      |                                                                          | 9  |

|   | Tabl | es       |                                                                          | 13 |

|   | Revi | sion His | tory                                                                     | 17 |

|   |      |          | -                                                                        |    |

| 1 |      |          | erview                                                                   |    |

| 1 | 1.1  |          | ary of IOMMU Capabilities                                                |    |

|   | 1.2  |          | Models                                                                   |    |

|   | 1.2  | 1.2.1    | Replacing the GART                                                       |    |

|   |      | 1.2.1    | Replacing the Device Exclusion Vector Mechanism.                         |    |

|   |      | 1.2.3    | 32-bit to 64-bit Legacy I/O Device Mapping                               |    |

|   |      | 1.2.3    | User Mode Device Accesses                                                |    |

|   |      | 1.2.5    | Virtual Machine Guest Access to Devices.                                 |    |

|   |      | 1.2.6    | Virtualizing the IOMMU                                                   |    |

|   |      | 1.2.7    | Virtualized User Mode Device Accesses.                                   |    |

|   | 1.3  |          | U Optional Features.                                                     |    |

|   | 1.5  | 1.3.1    | Two-level Translation for Guest and Host Address Spaces                  |    |

|   |      | 1.3.2    | Enhanced Processor Page Table Compatibility                              |    |

|   |      | 1.3.3    | Performance Features.                                                    |    |

|   |      | 1.3.4    | Address Translation Services for Guest Virtual Addresses                 |    |

|   |      | 1.3.5    | Peripheral Page Request Support Compatible with PCI-SIG PRI.             |    |

|   |      | 1.3.6    | Selecting Translation Tables in a Memory Transaction                     |    |

|   |      | 1.3.7    | AMD64 Interrupt Virtualization (Guest Virtual APIC Interrupt Controller) |    |

|   |      | 1.3.8    | Enhanced Support for Access and Dirty Bits                               |    |

|   |      | 1.3.9    | Guest I/O Protection                                                     |    |

|   |      | 1.3.10   | SMI Filter                                                               |    |

|   |      | 1.3.11   | Hardware Error Registers                                                 |    |

|   |      | 1.3.12   | Hardware Accelerated Virtualized IOMMU (vIOMMU)                          |    |

|   |      | 1.3.12   | Secure Nested Paging (SEV-SNP).                                          |    |

|   |      |          |                                                                          |    |

| 2 |      |          |                                                                          |    |

|   | 2.1  |          | or                                                                       |    |

|   |      |          | Normal Operation                                                         | 51 |

|   |      | 2.1.2    | IOMMU Logical Topology                                                   |    |

|   |      | 2.1.3    | IOMMU Event Reporting                                                    |    |

|   |      | 2.1.4    | Special Conditions                                                       |    |

|   |      | 2.1.5    | System Management Interrupt (SMI) Controls                               |    |

|   | 2.2  | Data St  | tructures                                                                | 60 |

|   |      | 2.2.1    | Updating Shared Tables                                                   |    |

|   |      | 2.2.2    | Device Table                                                             |    |

|   |      | 2.2.3    | I/O Page Tables for Host Translations                                    |    |

|   |      | 2.2.4    | Sharing AMD64 Processor and IOMMU Page Tables—GPA-to-SPA                 |    |

|   |      | 2.2.5    | Interrupt Remapping Tables                                               | 89 |

|     | 2.2.6            | I/O Page Tables for Guest Translations                     | 99  |

|-----|------------------|------------------------------------------------------------|-----|

|     | 2.2.7            | Guest and Nested Address Translation                       | 114 |

|     | 2.2.8            | Guest Virtual APIC Table for Interrupt Virtualization      | 119 |

|     | 2.2.9            | Guest I/O Protection                                       | 120 |

| 2.3 | Startin          | g the IOMMU                                                | 120 |

|     | 2.3.1            | Data Structure Initialization                              | 120 |

|     | 2.3.2            | Making Guest Interrupt Virtualization Changes              | 121 |

| 2.4 | Comm             | ands                                                       | 122 |

|     | 2.4.1            | COMPLETION_WAIT                                            |     |

|     | 2.4.2            | INVALIDATE_DEVTAB_ENTRY                                    |     |

|     | 2.4.3            | INVALIDATE_IOMMU_PAGES                                     |     |

|     | 2.4.4            | INVALIDATE_IOTLB_PAGES                                     |     |

|     | 2.4.5            | INVALIDATE_INTERRUPT_TABLE                                 | 131 |

|     | 2.4.6            | PREFETCH_IOMMU_PAGES                                       | 131 |

|     | 2.4.7            |                                                            |     |

|     | 2.4.8            | INVALIDATE_IOMMU_ALL                                       |     |

|     | 2.4.9            | INSERT_GUEST_EVENT Command                                 |     |

|     | 2.4.10           | RESET_VMMIO Command                                        |     |

| ~ - | 2.4.11           | IOMMU Ordering Rules                                       |     |

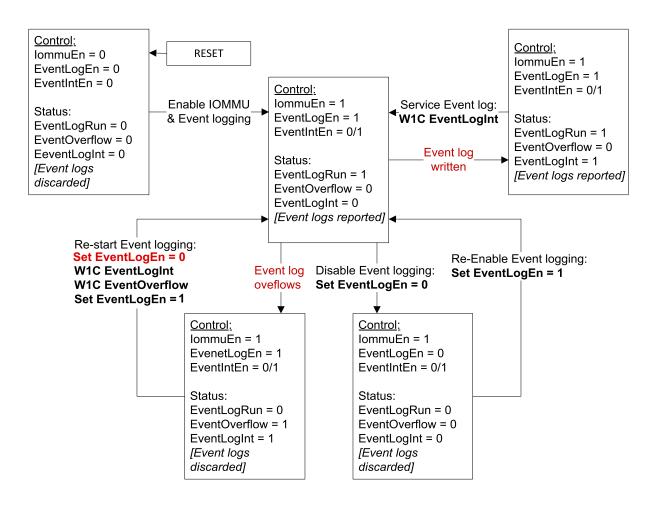

| 2.5 |                  | Logging.                                                   | 139 |

|     | 2.5.1            | Event Log Restart Procedure                                | 141 |

|     | 2.5.2            | ILLEGAL_DEV_TABLE_ENTRY Event                              |     |

|     | 2.5.3            | IO_PAGE_FAULT Event                                        | 152 |

|     | 2.5.4            | DEV_TAB_HARDWARE_ERROR Event.                              |     |

|     | 2.5.5            | PAGE_TAB_HARDWARE_ERROR Event                              |     |

|     | 2.5.6            | ILLEGAL_COMMAND_ERROR Event                                | 158 |

|     | 2.5.7            | COMMAND_HARDWARE_ERROR Event                               |     |

|     | 2.5.8<br>2.5.9   | IOTLB_INV_TIMEOUT Event                                    |     |

|     |                  | INVALID_DEVICE_REQUEST Event                               | 161 |

|     | 2.5.10           | INVALID_PPR_REQUEST Event         EVENT COUNTER ZERO Event |     |

|     | 2.5.11<br>2.5.12 | GUEST_EVENT_FAULT Event                                    |     |

|     | 2.5.12           | VIOMMU_HARDWARE_ERROR Event                                |     |

|     |                  | RMP       PAGE       FAULT Event       FAULT Event         |     |

|     |                  | RMP_FAGE_FAGE1 Event         RMP_HARDWARE_ERROR Event      |     |

|     |                  | IOMMU Event Reporting                                      | 170 |

|     |                  | Event Log Dual Buffering                                   | 172 |

| 2.6 |                  | eral Page Request (PPR) Logging                            | 174 |

| 2.0 | 2.6.1            | PPR Log Dual Buffering                                     | 177 |

|     | 2.6.2            | Peripheral Page Request Log Restart Procedure              | 178 |

|     | 2.6.3            | Peripheral Page Request Entry.                             | 179 |

|     | 2.6.4            | PPR Log Overflow Protection                                | 181 |

| 2.7 |                  | Virtual APIC (GA) Logging.                                 | 183 |

| 2.1 | 2.7.1            | Guest vAPIC Virtual Interrupt Request Log                  | 184 |

|     | 2.7.2            | Guest Virtual APIC Log Entry (Generic)                     | 187 |

|     | 2.7.3            | Guest Virtual APIC Request Entry (GA_GUEST_NR)             | 187 |

|     | 2.7.4            | Guest Virtual APIC Log Restart Procedure.                  | 188 |

|     |                  |                                                            | 100 |

|   | 2.8         | IOMMU Interrupt Support                                       | 188 |

|---|-------------|---------------------------------------------------------------|-----|

|   | 2.9         | Memory Address Routing and Control (MARC)                     | 189 |

|   | 2.10        | vIOMMU                                                        | 190 |

|   |             | 2.10.1 vIOMMU Private Address Space                           |     |

|   |             | 2.10.2 vIOMMU MMIO Resources                                  | 192 |

|   |             | 2.10.3 vIOMMU Event Logging                                   | 193 |

|   |             | 2.10.4 vIOMMU Extended Interrupt Remapping.                   | 193 |

|   |             | 2.10.5 vIOMMU and EOI Bus Cycle                               | 195 |

|   | 2.11        | Secure ATS Support                                            | 195 |

|   | 2.12        | IOMMU Secure Nested Paging (SEV-SNP) Support.                 | 195 |

|   |             | 2.12.1 SEV-SNP RMP Access Checks.                             | 196 |

|   |             | 2.12.2 SEV-SNP Restrictions                                   | 196 |

|   |             | 2.12.3 SEV-SNP Guest Virtual APIC Support                     | 197 |

| 3 | Regis       | sters                                                         | 199 |

| - | 3.1         | PCI Resources                                                 |     |

|   |             | 3.1.1 Accessing MSI Capability Block Registers                |     |

|   | 3.2         | IOMMU Base Capability Block Registers                         |     |

|   | 3.3         | IOMMU Vendor Specific Capability Block Registers              |     |

|   | 3.4         | IOMMU MMIO Registers                                          |     |

|   |             | 3.4.1 Control and Status Registers                            |     |

|   |             | 3.4.2 PPR Log Registers                                       |     |

|   |             | 3.4.3 SMI Filter                                              |     |

|   |             | 3.4.4 Guest Virtual APIC Log Registers                        |     |

|   |             | 3.4.5 Alternate PPR and Event Log Base Registers              |     |

|   |             | 3.4.6 Device Table Segment [1–7] Base Address Registers.      |     |

|   |             | 3.4.7 Device-Specific Feature Registers                       |     |

|   |             | 3.4.8 MMIO Access to MSI Capability Block Registers           |     |

|   |             | 3.4.9 Performance Optimization Control Register               |     |

|   |             | 3.4.10 IOMMU x2APIC Control Register                          |     |

|   |             | 3.4.11 vIOMMU Status Register                                 |     |

|   |             | 3.4.12 Memory Access and Routing (MARC) Registers             |     |

|   |             | 3.4.13 Extended Feature 2 Register                            |     |

|   |             | 3.4.14 Reserved Register                                      | 245 |

|   |             | 3.4.15 Command and Event Log Pointer Registers                | 245 |

|   |             |                                                               | 248 |

|   |             |                                                               | 251 |

|   |             | 3.4.18 Guest Virtual APIC Log Head and Tail Pointer Registers | 252 |

|   |             | 3.4.19 PPR Log B Head and Tail Pointer Registers              | 253 |

|   |             | 3.4.20 Event Log B Head and Tail Pointer Registers            | 254 |

|   |             | 3.4.21 PPR Log Overflow Protection Registers                  | 255 |

|   |             | 3.4.22 IOMMU Event Counter Registers                          | 257 |

|   | 3.5         | IOMMU Virtual Function Controls MMIO Registers                | 268 |

|   | 3.6         | IOMMU Virtual Function MMIO Registers.                        | 273 |

| 4 | Impl        | ementation Considerations                                     | 277 |

| - | <b>4</b> .1 |                                                               | 277 |

|   | 4.2         | • •                                                           | 278 |

|   | 4.3         |                                                               | 280 |

|   |             |                                                               |     |

|   | 4.4        | Chipset Specific Implementation Issues               | 281 |

|---|------------|------------------------------------------------------|-----|

|   | 4.5        | Software and Platform Firmware Implementation Issues | 281 |

| 5 | <b>I/O</b> | Virtualization ACPI Table                            | 283 |

|   | 5.1        | IOMMU Control Flow                                   | 284 |

|   | 5.2        | I/O Virtualization Reporting Structure (IVRS)        | 284 |

|   |            | 5.2.1 IVRS Header Fields                             | 286 |

|   |            | 5.2.2 I/O Virtualization Definition Blocks           | 287 |

|   | 5.3        | I/O Virtualization Device Tree                       | 304 |

|   |            | 5.3.1 I/O Virtualization Device Tree Data Structure  | 304 |

|   | Inde       | ex to Registers                                      | 307 |

# Figures

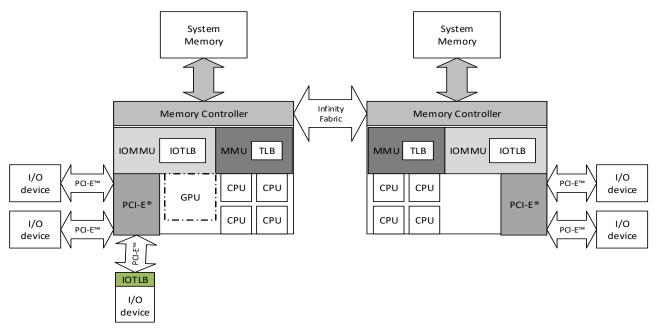

| Figure 1:  | Example Platform Architecture                                        | .35 |

|------------|----------------------------------------------------------------------|-----|

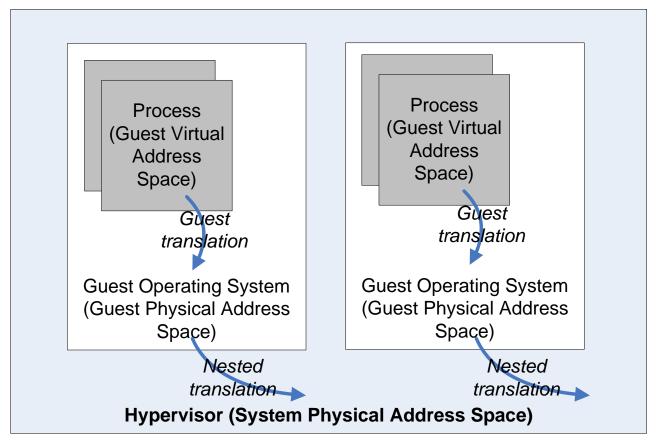

| Figure 2:  | Nested Address Spaces                                                | .44 |

| Figure 3:  | System Management Interrupt Address Format                           | .58 |

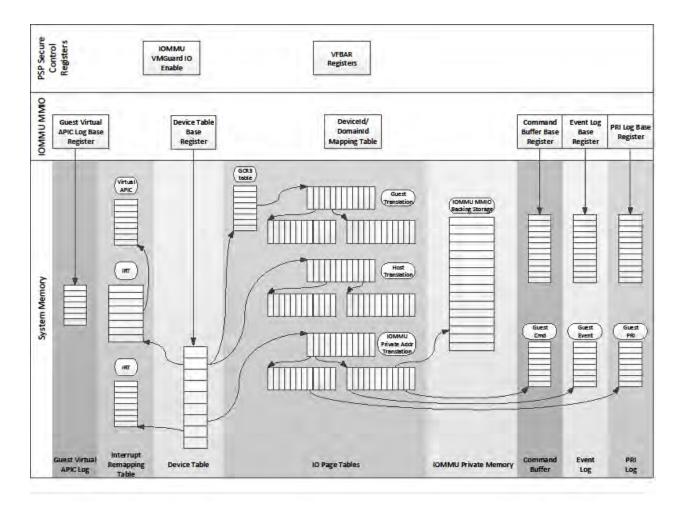

| Figure 4:  | IOMMU Data Structures                                                | .61 |

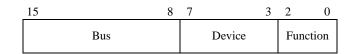

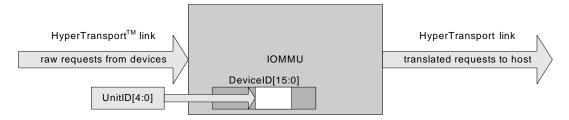

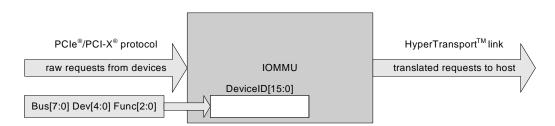

| Figure 5:  | Example DeviceID Derived from Peripheral RequesterID                 | .62 |

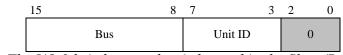

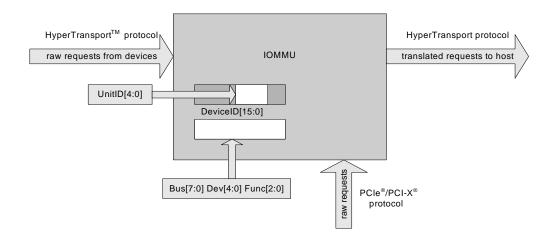

| Figure 6:  | DeviceID Derived from Peripheral UnitID                              | .63 |

| Figure 7:  | Device Table Entry (DTE) Fields                                      | .65 |

| Figure 8:  | I/O Page Table Entry Not Present (any level)                         | .82 |

| Figure 9:  | I/O Page Translation Entry (PTE), PR=1                               | .82 |

| Figure 10: | I/O Page Directory Entry (PDE), PR=1                                 | .84 |

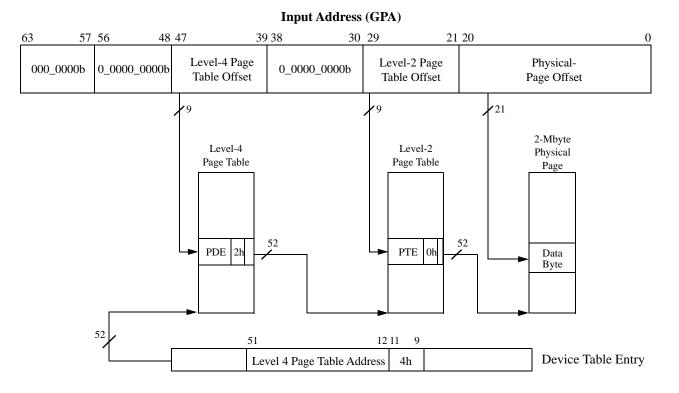

| Figure 11: | Address Translation Example with Skipped Level and 2-Mbyte Page      | .86 |

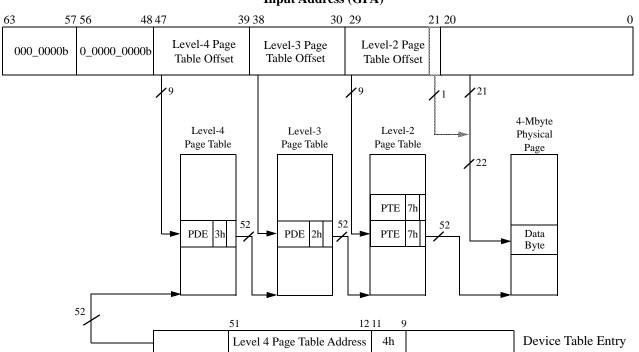

| Figure 12: | Address Translation Example with Page Size Larger than Default Size  | .87 |

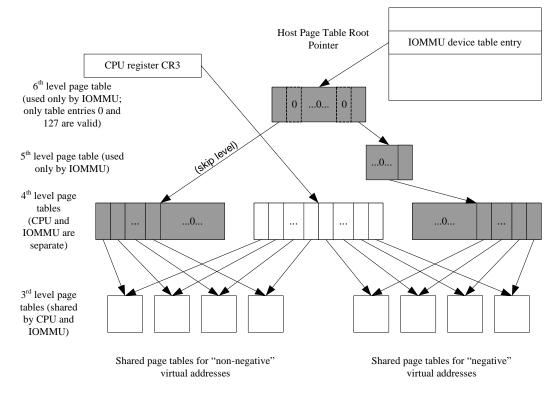

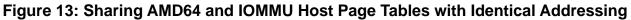

| Figure 13: | Sharing AMD64 and IOMMU Host Page Tables with Identical Addressing   | .89 |

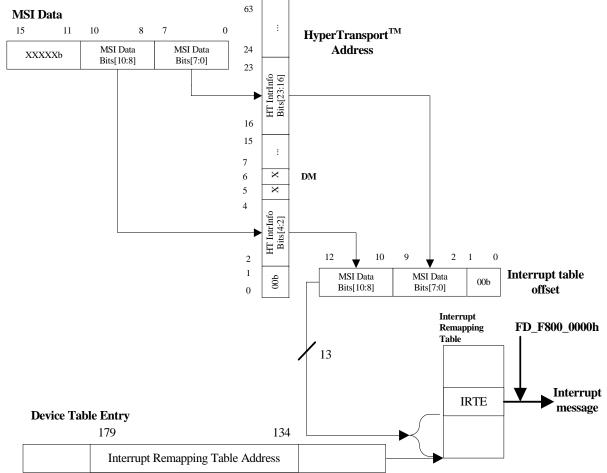

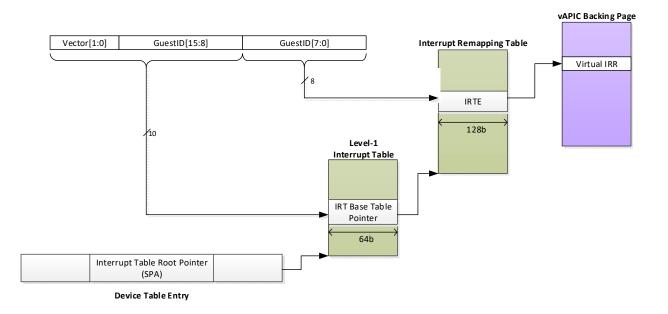

| Figure 14: | Interrupt Remapping Table Lookup for Fixed and Arbitrated Interrupts | .91 |

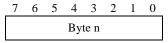

| Figure 15: | Interrupt Remapping Table Entry - Basic Format                       | .91 |

| Figure 16: | Bit Numbering of Virtual IRR in the Virtual APIC Backing Page        | .95 |

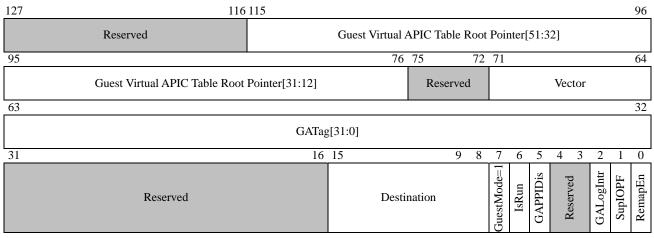

| Figure 17: | IRTE Fields with Guest Virtual APIC, IRTE[GuestMode]=0               | .95 |

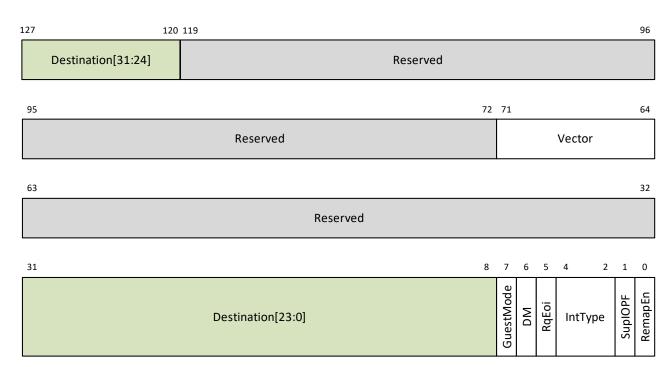

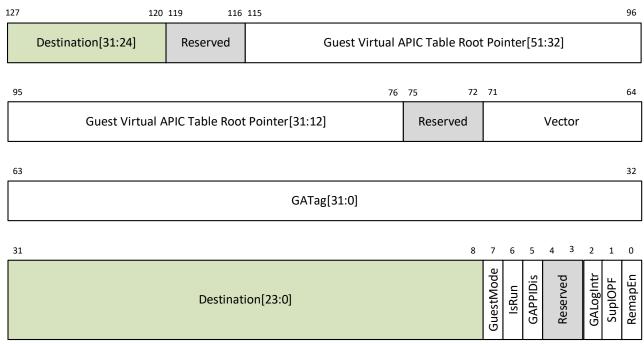

| Figure 18: | IRTE Fields with Guest Virtual APIC, IRTE[GuestMode]=1               | .96 |

| Figure 19: | IRTE Fields with Guest Virtual APIC, IRTE[GuestMode]=0               | .98 |

| Figure 20: | IRTE Fields with Guest Virtual APIC, IRTE[GuestMode]=1               | .98 |

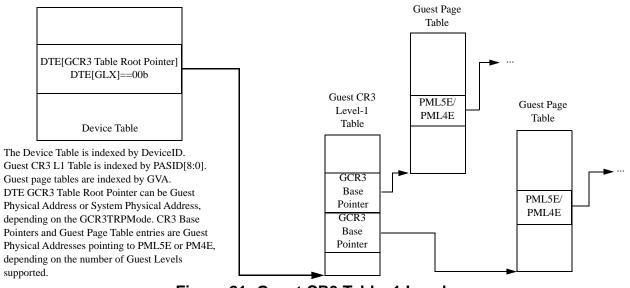

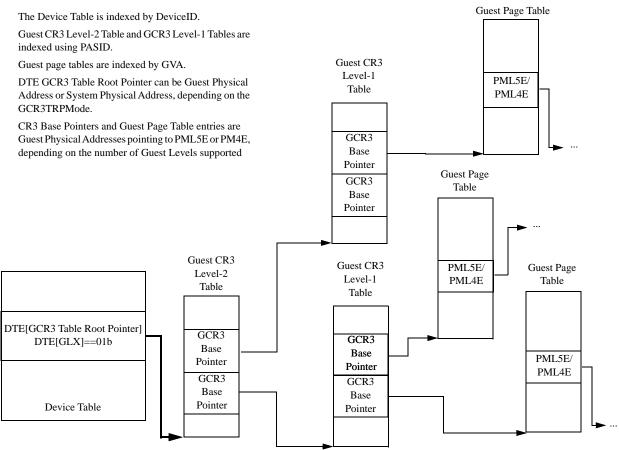

| Figure 21: | Guest CR3 Table, 1 Level.                                            | 101 |

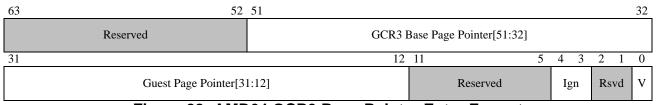

| Figure 22: | AMD64 GCR3 Base Pointer Entry Format                                 | 102 |

| Figure 23: | Guest CR3 Table, 2 Level.                                            | 103 |

| Figure 24: | Guest CR3 Level-2 Base Table Pointer Format                          | 104 |

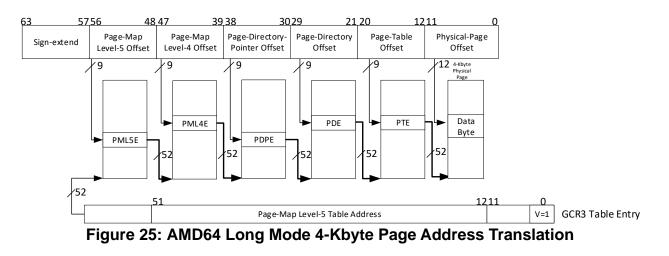

| Figure 25: | AMD64 Long Mode 4-Kbyte Page Address Translation                     | 105 |

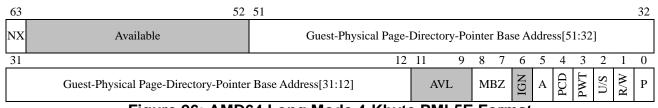

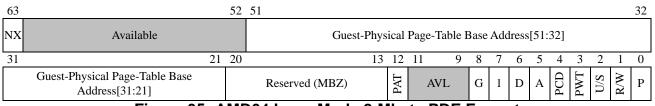

| Figure 26: | AMD64 Long Mode 4-Kbyte PML5E Format                                 | 105 |

| Figure 27: | AMD64 Long Mode 4-Kbyte PML4E Format                                 | 106 |

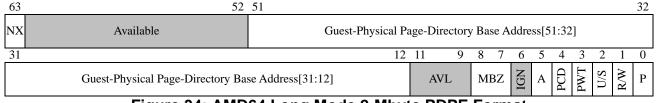

| Figure 28: | AMD64 Long Mode 4-Kbyte PDPE Format                                  | 106 |

| Figure 29: | AMD64 Long Mode 4-Kbyte PDE Format                                   | 106 |

| Figure 30: | AMD64 Long Mode 4-Kbyte PTE Format.                                  | 106 |

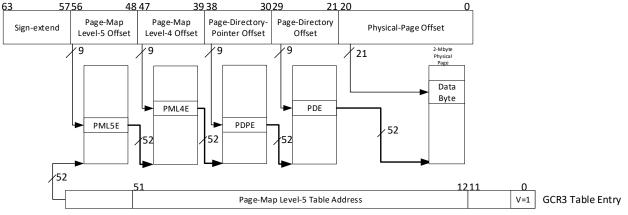

| Figure 31: | AMD64 Long Mode 2-Mbyte Page Address Translation                     | 108 |

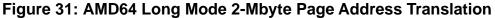

| Figure 32: | AMD64 Long Mode 2-Mbyte PML5E Format                                 | 108 |

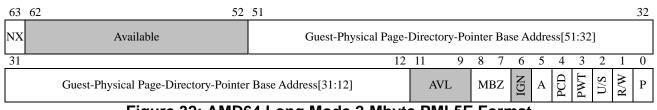

| Figure 33: | AMD64 Long Mode 2-Mbyte PML4E Format108                   |

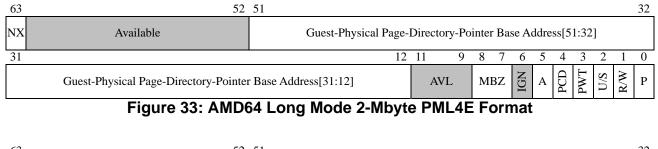

|------------|-----------------------------------------------------------|

| Figure 34: | AMD64 Long Mode 2-Mbyte PDPE Format                       |

| Figure 35: | AMD64 Long Mode 2-Mbyte PDE Format                        |

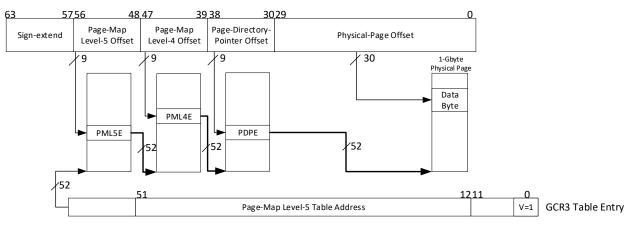

| Figure 36: | AMD64 Long Mode 1-Gbyte Page Address Translation          |

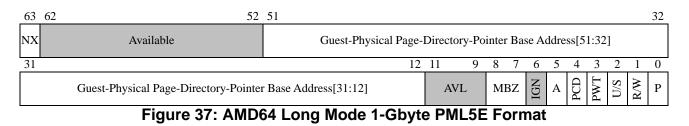

| Figure 37: | AMD64 Long Mode 1-Gbyte PML5E Format110                   |

| Figure 38: | AMD64 Long Mode 1-Gbyte PML4E Format                      |

| Figure 39: | AMD64 Long Mode 1-Gbyte PDPE Format111                    |

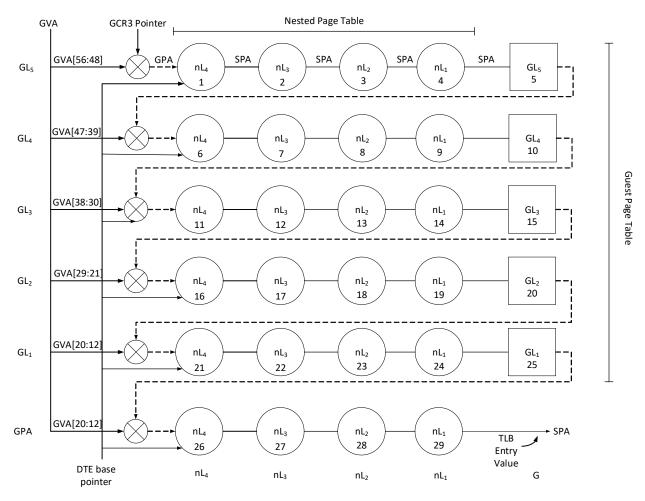

| Figure 40: | Complete GVA-to-SPA Address Translation113                |

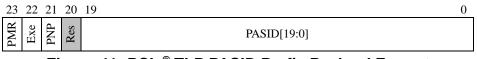

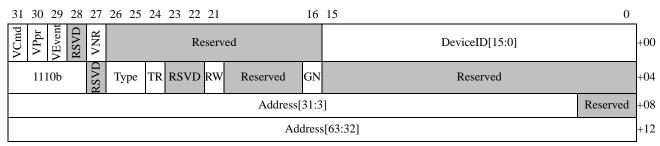

| Figure 41: | PCIe <sup>®</sup> TLP PASID Prefix Payload Format118      |

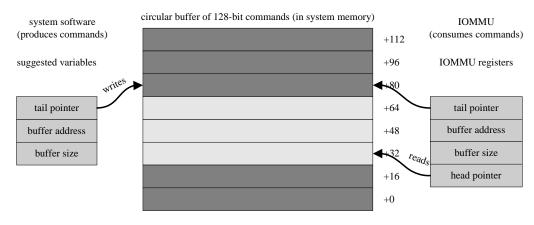

| Figure 42: | Command Buffer in System Memory122                        |

| Figure 43: | Generic Command Buffer Entry Format                       |

| Figure 44: | COMPLETION_WAIT Command Format124                         |

| Figure 45: | INVALIDATE_DEVTAB_ENTRY Command Format125                 |

| Figure 46: | INVALIDATE_IOMMU_PAGES Command Format127                  |

| Figure 47: | INVALIDATE_IOTLB_PAGES Command Format128                  |

| Figure 48: | INVALIDATE_INTERRUPT_TABLE Command Format131              |

| Figure 49: | PREFETCH_IOMMU_PAGES Command Format132                    |

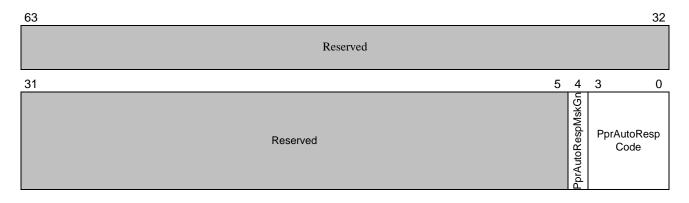

| Figure 50: | COMPLETE_PPR_REQUEST Command Format135                    |

| Figure 51: | INVALIDATE_IOMMU_ALL Command Format136                    |

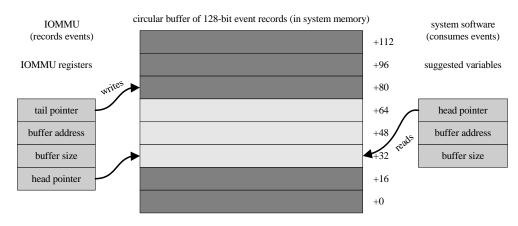

| Figure 52: | Event Log in System Memory140                             |

| Figure 53: | Event Log State Diagram                                   |

| Figure 54: | Generic Event Log Buffer Entry142                         |

| Figure 55: | ILLEGAL_DEV_TABLE_ENTRY Event Log Buffer Entry Format150  |

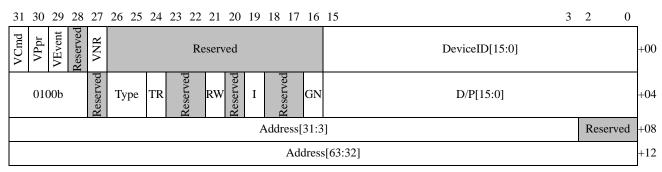

| Figure 56: | IO_PAGE_FAULT Event Log Buffer Entry Format               |

| Figure 57: | DEV_TAB_HARDWARE_ERROR Event Log Buffer Entry Format155   |

| Figure 58: | PAGE_TAB_HARDWARE_ERROR Event Log Buffer Entry Format157  |

| Figure 59: | ILLEGAL_COMMAND_ERROR Event Log Buffer Entry Format159    |

| Figure 60: | COMMAND_HARDWARE_ERROR Event Log Buffer Entry Format159   |

| Figure 61: | IOTLB_INV_TIMEOUT Event Log Buffer Entry Format160        |

| Figure 62: | INVALID_DEVICE_REQUEST Event Log Buffer Entry Format      |

| Figure 63: | INVALID_PPR_REQUEST Event Log Buffer Entry Format, RX = 0 |

| Figure 64: | INVALID_PPR_REQUEST Event Log Buffer Entry Format, RX = 1 |

| Figure 65: | EVENT_COUNTER_ZERO Event Log Buffer Entry Format          |

| Figure 66: | GUEST_EVENT_FAULT Event Buffer Entry Format               |

| Figure 67: | VIOMMU_HARDWARE_ERROR Event Entry Format167                             |

|------------|-------------------------------------------------------------------------|

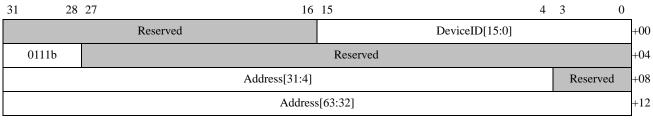

| Figure 68: | RMP_PAGE_FAULT Event Log Buffer Entry Format    169                     |

| Figure 69: | RMP_HARDWARE_ERROR Event Log Buffer Entry Format    171                 |

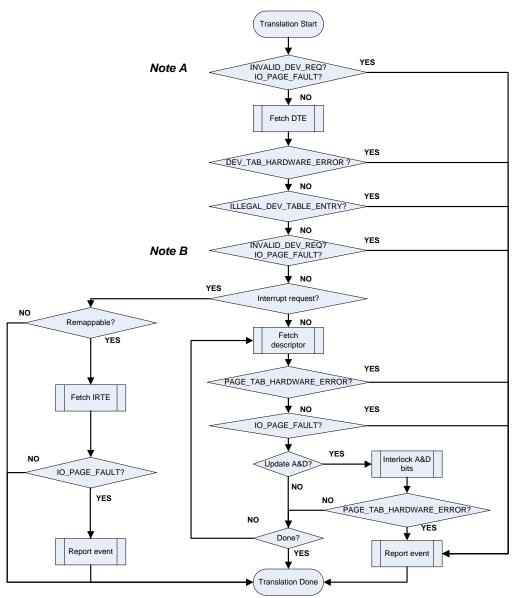

| Figure 70: | Translation and Remapping Validation Sequence                           |

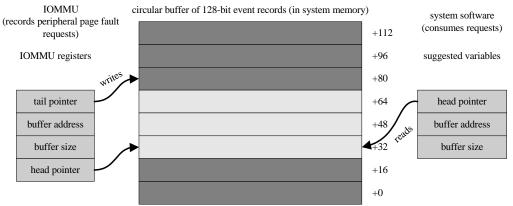

| Figure 71: | Peripheral Page Request Log in System Memory176                         |

| Figure 72: | PPR Log State Diagram                                                   |

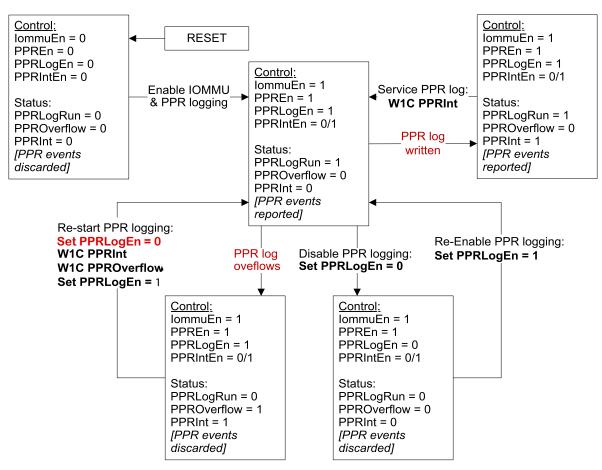

| Figure 73: | Generic Peripheral Page Request Log Buffer Entry Format                 |

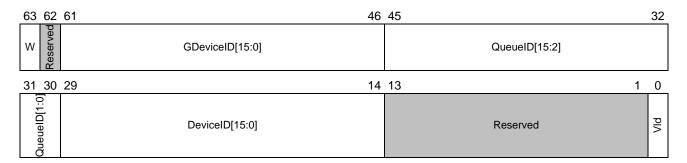

| Figure 74: | PAGE_SERVICE_REQUEST PPR Log Buffer Entry Format                        |

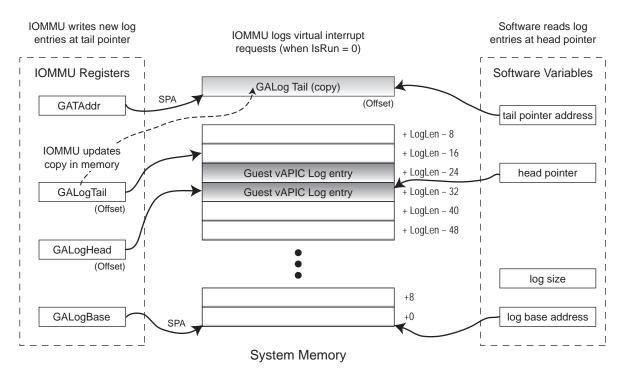

| Figure 75: | Guest vAPIC Log in System Memory                                        |

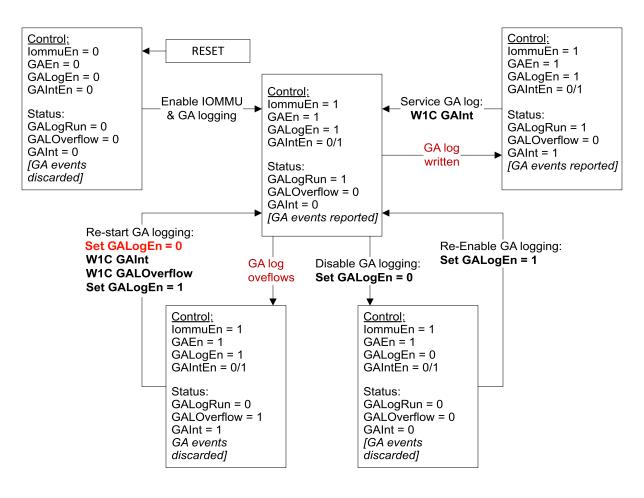

| Figure 76: | Guest Virtual APIC Log State Diagram                                    |

| Figure 77: | Generic Guest Virtual APIC Log Buffer Entry Format                      |

| Figure 78: | GA_GUEST_NR Log Buffer Entry Format187                                  |

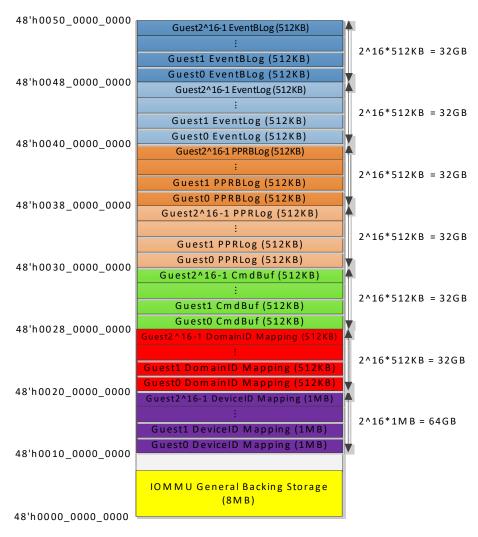

| Figure 79: | IOMMU Private Address Map191                                            |

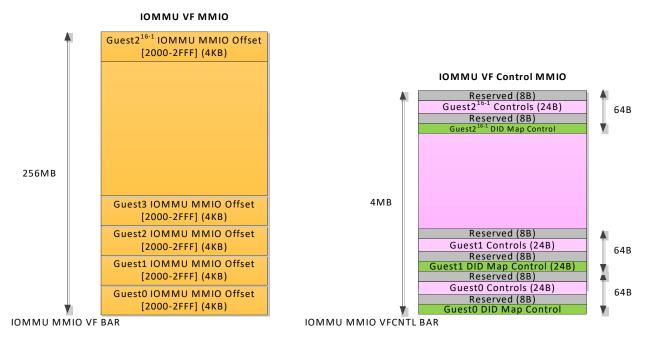

| Figure 80: | IOMMU Virtual Function Control MMIO and IOMMU Virtual Function MMIO 193 |

| Figure 81: | Extended Interrupt Remapping Table194                                   |

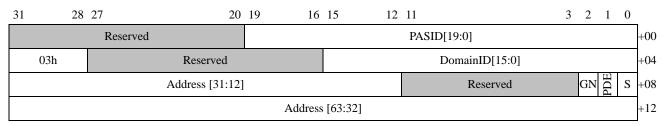

| Figure 82: | Level-1 Interrupt Table Entry Format194                                 |

| Figure 83: | IOMMU Counter Register Address Decode                                   |

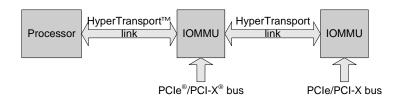

| Figure 84: | IOMMU in a Tunnel                                                       |

| Figure 85: | IOMMU in a Peripheral Bus Bridge                                        |

| Figure 86: | Hybrid IOMMU                                                            |

| Figure 87: | Chained Hybrid IOMMU in a Large System                                  |

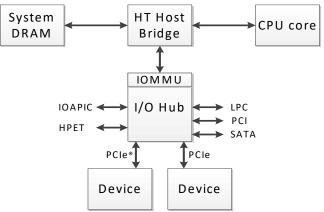

| Figure 88: | Example Platform Architecture                                           |

| Figure 89: | IVHD Type 10h IOMMU Feature Reporting Field Format                      |

48882-PUB-Rev 3.10-Feb 2025

## **Tables**

| Table 1:  | Bit Attribute Definitions                                                         |

|-----------|-----------------------------------------------------------------------------------|

| Table 2:  | Software-Visible Features                                                         |

| Table 3:  | Special Address Controls (GPA) when MMIO Offset 01A0h[HTRangeIgnore]=053          |

| Table 4:  | System Management Interrupt Address Fields                                        |

| Table 5:  | Feature Enablement for Address Translation                                        |

| Table 6:  | Feature Enablement for Interrupt Remapping and Virtualization                     |

| Table 7:  | Device Table Entry (DTE) Field Definitions                                        |

| Table 8:  | V, TV, and GV Fields in Device Table Entry74                                      |

| Table 9:  | IV and IntCtl Fields in Device Table Entry for Fixed and Arbitrated Interrupts74  |

| Table 10: | IV and Pass Fields in Device Table Entry for Selected Interrupts                  |

| Table 11: | GLX and Maximum Translatable PASID size                                           |

| Table 12: | Cache bit and U bit for ATS requests                                              |

| Table 13: | Registers Utilized to Allocate Device Table Segments                              |

| Table 14: | Example Page Size Encodings                                                       |

| Table 15: | Page Table Level Parameters                                                       |

| Table 16: | I/O Page Table Entry Not Present Fields, PR=0                                     |

| Table 17: | I/O Page Translation Entry (PTE) Fields, PR=1                                     |

| Table 18: | I/O Page Directory Entry (PDE) Fields, PR=1                                       |

| Table 19: | IOMMU Controls and Actions for Upstream Interrupts                                |

| Table 20: | Interrupt Remapping Table Fields - Basic Format                                   |

| Table 21: | Interrupt Virtualization Controls for Upstream Interrupts                         |

| Table 22: | IRTE Field Descriptions with Guest Virtual APIC, IRTE[GuestMode]=095              |

| Table 23: | IRTE Field Descriptions with Guest Virtual APIC, IRTE[GuestMode]=196              |

| Table 24: | Guest Address Translation Controls                                                |

| Table 25: | AMD64 Guest CR3 Level-1 Table Format102                                           |

| Table 26: | AMD64 GCR3 Base Pointer Entry Fields102                                           |

| Table 27: | Guest CR3 Level-2 Table Format                                                    |

| Table 28: | Guest CR3 Level-2 Base Table Pointer Fields104                                    |

| Table 29: | IOMMU Interpretation of AMD64 Page Table Fields for 4-Kbyte Page Translation .106 |

| Table 30: | IOMMU Interpretation of AMD64 Page Table Fields for 2-Mbyte Page Translation.109  |

| Table 31: | IOMMU Interpretation of AMD64 Long Mode 1-Gbyte Page Table Fields111              |

| Table 32: | AMD64 Access Privilege Conversion Table for ATS Request117                        |

| Table 33: | PCIe <sup>®</sup> TLP Prefix Payload Fields              |     |

|-----------|----------------------------------------------------------|-----|

| Table 34: | COMPLETION_WAIT Fields                                   |     |

| Table 35: | INVALIDATE_DEV_TAB_ENTRY Fields                          |     |

| Table 36: | INVALIDATE_IOMMU_PAGES Fields                            |     |

| Table 37: | INVALIDATE_IOTLB_PAGES Fields                            |     |

| Table 38: | INVALIDATE_INTERRUPT_TABLE command Fields                | 131 |

| Table 39: | PREFETCH_IOMMU_PAGES Fields                              |     |

| Table 40: | COMPLETE_PPR_REQUEST Fields                              | 135 |

| Table 41: | INVALIDATE_IOMMU_ALL Fields                              | 137 |

| Table 42: | Event Type Summary                                       |     |

| Table 43: | ILLEGAL_DEV_TABLE_ENTRY Event Types                      |     |

| Table 44: | IO_PAGE_FAULT Event Types                                | 144 |

| Table 45: | DEV_TAB_HARDWARE_ERROR Event Types                       | 146 |

| Table 46: | PAGE_TAB_HARDWARE_ERROR Event Types                      | 146 |

| Table 47: | COMMAND_HARDWARE_ERROR Event Types                       | 146 |

| Table 48: | ILLEGAL_COMMAND_ERROR Event Types                        | 147 |

| Table 49: | IOTLB_INV_TIMEOUT Event Types                            | 147 |

| Table 50: | INVALID_DEVICE_REQUEST Event Types (Access)              | 148 |

| Table 51: | INVALID_DEVICE_REQUEST Event Types (Translation Request) |     |

| Table 52: | INVALID_PPR_REQUEST Event Summary                        |     |

| Table 53: | EVENT_COUNTER_ZERO Event Types                           |     |

| Table 54: | RMP_PAGE_FAULT Event Types                               | 150 |

| Table 55: | RMP_HARDWARE_ERROR Event Types                           | 150 |

| Table 56: | ILLEGAL_DEV_TABLE_ENTRY Event Log Buffer Entry Fields    | 150 |

| Table 57: | IO_PAGE_FAULT Event Log Buffer Entry Fields              |     |

| Table 58: | Event Log Type Field Encodings                           | 154 |

| Table 59: | DEV_TAB_HARDWARE_ERROR Event Log Buffer Entry Fields     | 155 |

| Table 60: | PAGE_TAB_HARDWARE_ERROR Event Log Buffer Entry Fields    | 157 |

| Table 61: | ILLEGAL_COMMAND_ERROR Event Log Buffer Entry Fields      | 159 |

| Table 62: | COMMAND_HARDWARE_ERROR Event Log Buffer Entry Fields     | 160 |

| Table 63: | IOTLB_INV_TIMEOUT Event Log Buffer Entry Fields          |     |

| Table 64: | INVALID_DEVICE_REQUEST Type Field Encodings              | 161 |

| Table 65: | INVALID_DEVICE_REQUEST Event Log Buffer Entry Fields     |     |

| Table 66: | INVALID_PPR_REQUEST Event Log Buffer Entry Fields        | 164 |

| Table 67:  | EVENT_COUNTER_ZERO Event Log Buffer Entry Fields                              | б |

|------------|-------------------------------------------------------------------------------|---|

| Table 68:  | Guest_Event_Fault Event Log Buffer Entry Fields                               | б |

| Table 69:  | VIOMMU_HARDWARE_ERROR Event Entry Fields                                      | 7 |

| Table 70:  | RMP_PAGE_FAULT Event Log Buffer Entry Fields169                               | 9 |

| Table 71:  | RMP_HARDWARE_ERROR Event Log Buffer Entry Fields                              | 1 |

| Table 72:  | DualEventLogSup Field Capability Levels                                       | 4 |

| Table 73:  | DualEventLogEn Field Operation Levels17:                                      | 5 |

| Table 74:  | PAGE_SERVICE_REQUEST PPR Log Buffer Entry Fields                              | 0 |

| Table 75:  | GA_GUEST_NR Log Buffer Entry Fields                                           | 8 |

| Table 76:  | Pinned Memory Buffer Regions                                                  | 2 |

| Table 77:  | Level-1 Interrupt Table Entry Format                                          | 5 |

| Table 78:  | SMI Filter Register MMIO Offset Assignments                                   | б |

| Table 79:  | Device Table Segment Base Address Registers; Offsets and Maximum Size Value23 | 1 |

| Table 80:  | MARC Aperture Register Offsets (hexadecimal)                                  | 2 |

| Table 81:  | Counter Bank Addressing (MMIO)                                                | 0 |

| Table 82:  | Architectural Counter Input Group, CAC = 0b                                   | 3 |

| Table 83:  | I/O Virtualization Reporting Structure (IVRS)                                 | 5 |

| Table 84:  | IVRS Fields                                                                   | б |

| Table 85:  | IVRS Revision Field                                                           | б |

| Table 86:  | IVRS IVinfo Field                                                             | 7 |

| Table 87:  | I/O Virtualization Hardware Definition (IVHD) Block Generic Format            | 8 |

| Table 88:  | I/O Virtualization Hardware Definition (IVHD) Type 10h                        | 0 |

| Table 89:  | IVHD Type 10h Field Definitions                                               | 0 |

| Table 90:  | IVHD Flags Field                                                              | 1 |

| Table 91:  | IVHD IOMMU Info Field                                                         | 1 |

| Table 92:  | IVHD IOMMU Feature Reporting Field                                            | 1 |

| Table 93:  | I/O Virtualization Hardware Definition (IVHD) Type 11h                        | 3 |

| Table 94:  | IVHD Type 11h Field Definitions                                               | 3 |

| Table 95:  | IVHD Flags Field                                                              | 4 |

| Table 96:  | IVHD Type 11h IOMMU Attributes                                                | 4 |

| Table 97:  | I/O Virtualization Hardware Definition (IVHD) Type 40h Fields                 | 5 |

| Table 98:  | IVHD Type 40h Field Definitions                                               | 5 |

| Table 99:  | IVHD Type 40 Flags Field                                                      | б |

| Table 100: | IVHD Type 40h IOMMU Attributes                                                | 7 |

| Table 101: | IVHD Device Entry Length Based on Type       | 297 |

|------------|----------------------------------------------|-----|

| Table 102: | IVHD Device Entry Fields (4-byte)            | 298 |

| Table 103: | IVHD Device Entry Type Codes (4-byte)        | 298 |

| Table 104: | IVHD Device Table Entry DTE Setting          | 298 |

| Table 105: | IVHD Device Entry Type Codes (8-byte)        | 299 |

| Table 106: | IVHD Device Entry Extended DTE Setting Field | 300 |

| Table 107: | IVHD Special Device Entry Variety Field      | 301 |

| Table 108: | Device Entry Type F0h Fields                 | 301 |

| Table 109: | IVMD Types 20h–22h Format                    | 303 |

| Table 110: | IVMD Types 20h–22h Fields                    | 303 |

| Table 111: | IVMD Flags Definitions                       | 304 |

|            |                                              |     |

## **Revision History**

| Date                         | Revision     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2025                | 3.10         | <ul> <li>Updated "Related Documents" on page 30.</li> <li>Added features to Table 2, "Software-Visible Features" on page 41.</li> <li>Section 2:</li> <li>Updated Section 2.1.2 [IOMMU Logical Topology].</li> <li>Added note to Section 2.2.2 [Device Table].</li> <li>Updated Section 2.2.5 [Interrupt Remapping Tables], including Table 19, "IOMMU Controls and Actions for Upstream Interrupts" on page 90 and a correction in Table 23, "IRTE Field Descriptions with Guest Virtual APIC, IRTE[GuestMode]=1" on page 96.</li> <li>Updated Section 2.2.5.2 [Interrupt Virtualization Tables with Guest Virtual APIC Enabled].</li> <li>Updated bit 21 in Figure 41, "PCIe<sup>®</sup> TLP PASID Prefix Payload Format" on page 118.</li> <li>Updated bit 21 in Table 77, "Level-1 Interrupt Table Entry Format" on page 195.</li> <li>Section 3:</li> <li>In "IOMMU Control Register" on page 211, updated Bits 63:61, 45, and 44:43.</li> <li>Updated "Guest Miscellaneous Control Register" on page 269.</li> <li>Section 5:</li> <li>Updated bit 0 in Table 96, "IVHD Type 11h IOMMU Attributes" on page 294.</li> <li>Updated bit 0 in Table 100, "IVHD Type 40h IOMMU Attributes" on page 297.</li> <li>Updated bit 3 in Table 104, "IVHD Device Table Entry DTE Setting" on page 298.</li> </ul> |

| October 2023<br>October 2023 | 3.09<br>3.08 | <ul> <li>Updated note in Section 2.4.2 [INVALIDATE_DEVTAB_ENTRY].</li> <li>Added to "Related Documents" on page 30.</li> <li>Section 1: <ul> <li>Added "AMD Tiered Memory Page Migration" to Table 2.</li> </ul> </li> <li>Section 2: <ul> <li>Updated bits 58:52 in Table 17, "I/O Page Translation Entry (PTE) Fields, PR=1" on page 83 for Page Migration State.</li> <li>Updated Section 2.2.5.2 [Interrupt Virtualization Tables with Guest Virtual APIC Enabled].</li> <li>Updated Section 2.3.2 [Making Guest Interrupt Virtualization Changes].</li> <li>Updated Section 2.4.2 [INVALIDATE_DEVTAB_ENTRY] with a new requirement.</li> <li>Corrected notes in Table 76, "Pinned Memory Buffer Regions" on page 192 for mapping table references.</li> </ul> </li> <li>Section 3: <ul> <li>In MMIO Offset 0018h, updated Bit 56.</li> <li>In MMIO Offset 01A0h, updated Bit 2.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                 |

| Date         | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| October 2022 | 3.07     | <ul> <li>Updated "Related Documents" on page 30.</li> <li>Section 1:</li> <li>Added features to Table 2.</li> <li>Section 2:</li> <li>Updated Figure 7, "Device Table Entry (DTE) Fields" on page 65.</li> <li>Updated Table 7, "Device Table Entry (DTE) Field Definitions" on page 66.</li> <li>Updated bit 5 in Figure 18, "IRTE Fields with Guest Virtual APIC,<br/>IRTE[GuestMode]=1" on page 96 and Table 23, "IRTE Field Descriptions with Guest Virtual APIC, IRTE[GuestMode]=1" on page 96.</li> <li>Updated bit 5 in Figure 20, "IRTE Fields with Guest Virtual APIC,<br/>IRTE[GuestMode]=1" on page 98.</li> <li>Added Section 2.2.5.4, "Guest APIC Physical Processor Interrupt" on page 99.</li> <li>Updated Section 2.2.6.3, "Guest CR3 Table" on page 100, including Figure 21,<br/>Figure 23.</li> <li>Added Section 2.2.6.4, "Support for AMD64 Level 5 (PML5E) Page Table" on<br/>page 105.</li> <li>Updated Section 2.2.6.5, "AMD64 4-Kbyte Page Translation" on page 105 for PML5E,<br/>including Figure 25, added Figure 26, and Table 29.</li> <li>Updated Section 2.2.6.6, "AMD64 2-Mbyte Page Translation" on page 107 for PML5E,<br/>including Figure 31, added Figure 32, and Table 30.</li> <li>Updated Section 2.2.6.7, "AMD64 1-Gbyte Page Translation" on page 110 for PML5E,<br/>including Figure 40, "Complete GVA-to-SPA Address Translation" on page 113.</li> <li>Updated Section 2.10.1.1, "vIOMMU Backing Storage Memory" on page 191.</li> <li>Updated Section 2.12.2.4, "SEV-SNP Page Mode Restrictions" on page 197.</li> </ul> |

| October 2022 | 3.07     | <ul> <li>(continued)</li> <li>Section 3:</li> <li>In Capability Offset 10h, updated bit description for Bits 7:5.</li> <li>In MMIO Offset 0018h, updated Bits 60, 58, and 55.</li> <li>In MMIO Offset 0030h, updated Bits 13:12 and 5.</li> <li>Updated MMIO Offset 01A0h.</li> <li>Added VFCntlMMIO Offset {16'b[GuestID], 6'b01_1000}.</li> <li>Updated VFCntlMMIO Offset {16'b[GuestID], 6'b10_0000}.</li> <li>Updated VFCntlMMIO Offset {16'b[GuestID], 6'b10_1000}.</li> <li>Updated VFCntlMMIO Offset {16'b[GuestID], 6'b11_0000}.</li> <li>Updated Table 109, "IVMD Types 20h-22h Format" on page 303.</li> <li>Updated Table 110, "IVMD Types 20h-22h Fields" on page 303.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Date       | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March 2021 | 3.06     | Added terms in "Definitions" on page 24.<br>Added items to "Related Documents" on page 30.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            |          | <ul> <li>Section 1:</li> <li>Updated Figure 1, "Example Platform Architecture" on page 35.</li> <li>Updated Section 1.3, "IOMMU Optional Features" on page 39.</li> <li>Added rows to Table 2, "Software-Visible Features" on page 41 and a new column to indicate specification rev level (replacing Table 2, "Feature Support by Specification Rev Level."</li> <li>Added Section 1.3.12, "Hardware Accelerated Virtualized IOMMU (vIOMMU)" on page 49.</li> <li>Added Section 1.3.13, "Secure Nested Paging (SEV-SNP)" on page 50.</li> <li>Section 2:</li> <li>Updated Figure 4, "IOMMU Data Structures" on page 61.</li> <li>Updated Figure 7, "Device Table Entry (DTE) Fields" on page 65.</li> <li>Updated Table 7, "Device Table Entry (DTE) Field Definitions" on page 66.</li> <li>Updated Figure 18, "IRTE Field Descriptions with Guest Virtual APIC, IRTE[GuestMode]=1" on page 96.</li> <li>Updated Section 2.4.8, "INVALIDATE_IOMMU_ALL" on page 136.</li> <li>Added Section 2.4.9, "RESET_VMMIO Command" on page 137.</li> <li>Added Section 2.4.9, "RESET_VMMIO Command" on page 137.</li> <li>Added Table 54, "RMP_PAGE_FAULT Event Types" on page 150.</li> <li>Updated Figure 55, "ILLEGAL_DEV_TABLE_ENTRY Event Log Buffer Entry Format" on page 150.</li> <li>Updated Table 56, "ILLEGAL_DEV_TABLE_ENTRY Event Log Buffer Entry Fields" on page 150.</li> </ul> |

|            |          | (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Date       | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March 2021 | 3.06     | (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |          | Section 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            |          | <ul> <li>(continued)</li> <li>Section 2:</li> <li>Updated Figure 56, "IO_PAGE_FAULT Event Log Buffer Entry Format" on page 152.</li> <li>Updated Table 57, "IO_PAGE_FAULT Event Log Buffer Entry Fields" on page 152.</li> <li>Updated Table 58, "Event Log Type Field Encodings" on page 154.</li> <li>Added Figure 57, "DEV_TAB_HARDWARE_ERROR Event Log Buffer Entry Format" on page 155.</li> <li>Updated Table 59, "DEV_TAB_HARDWARE_ERROR Event Log Buffer Entry Fields" on page 155.</li> <li>Updated Figure 58, "PAGE_TAB_HARDWARE_ERROR Event Log Buffer Entry Format" on page 157.</li> <li>Updated Table 60, "PAGE_TAB_HARDWARE_ERROR Event Log Buffer Entry Format" on page 157.</li> <li>Updated Table 60, "PAGE_TAB_HARDWARE_ERROR Event Log Buffer Entry Fields" on page 157.</li> <li>Added Section 2.5.13, "VIOMMU_HARDWARE_ERROR Event" on page 167.</li> <li>Added Section 2.5.14, "RMP_PAGE_FAULT Event" on page 168.</li> <li>Added Section 2.5.14, "RMP_HARDWARE_ERROR Event" on page 170.</li> <li>Added Section 2.10, "vIOMMU" on page 190.</li> <li>Added Section 2.11, "Secure ATS Support" on page 195.</li> <li>Updated Figure 7, "Device Table Entry (DTE) Fields" on page 65.</li> <li>Updated Figure 7, "Device Table Entry (DTE) Fields" on page 66.</li> <li>Updated Table 7, "Device Table Entry (DTE) Field Definitions" on page 66.</li> <li>Updated Table 7, "ITTE Field Descriptions with Guest Virtual APIC, IRTE[GuestMode]=1" on page 96.</li> <li>Updated Section 2.4.8, "INVALIDATE_IOMMU_ALL" on page 136.</li> <li>Added Section 2.4.9, "INSERT_GUEST_EVENT Command" on page 137.</li> <li>Added Section 2.4.9, "RESET_VMMIO Command" on page 137.</li> </ul> |

|            |          | <ul> <li>Added Table 54, "RMP_PAGE_FAULT Event Types" on page 150.</li> <li>Added Table 55, "RMP_HARDWARE_ERROR Event Types" on page 150.</li> <li>Updated Figure 55, "ILLEGAL_DEV_TABLE_ENTRY Event Log Buffer Entry</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            |          | <ul> <li>Format" on page 150.</li> <li>Updated Table 56, "ILLEGAL_DEV_TABLE_ENTRY Event Log Buffer Entry Fields" on page 150.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            |          | <ul> <li>Updated Figure 56, "IO_PAGE_FAULT Event Log Buffer Entry Format" on page 152.</li> <li>Updated Table 57, "IO_PAGE_FAULT Event Log Buffer Entry Fields" on page 152.</li> <li>Updated Table 58, "Event Log Type Field Encodings" on page 154.</li> <li>Added Figure 57, "DEV_TAB_HARDWARE_ERROR Event Log Buffer Entry Format" on page 155.</li> <li>Updated Table 59, "DEV_TAB_HARDWARE_ERROR Event Log Buffer Entry Fields"</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            |          | <ul> <li>on page 155.</li> <li>Updated Figure 58, "PAGE_TAB_HARDWARE_ERROR Event Log Buffer Entry Format" on page 157.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |          | (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |