### SOLUTION BRIEF

# AUTOMOTIVE NIGHT VISION CAMERAS WITH AMD ARTIX™ ULTRASCALE+™ XA AU7P FPGA

Supports night vision cameras with real-time image processing, flexible logic for proprietary sensor interfaces, MIPI data streams, and high-speed transceivers for seamless vehicle-wide data transmission.

#

The AMD Artix<sup>™</sup> UltraScale+<sup>™</sup> XA AU7P FPGA offers a compact, power-efficient, and cost-optimized solution for night vision cameras in ADAS and autonomous vehicles. Its innovative architecture and advanced peripherals deliver exceptional performance per watt to support long-wave infrared (LWIR) cameras, vital for enhancing Automatic Emergency Braking (AEB) and pedestrian detection.

LWIR cameras detect heat signatures of pedestrians, animals, and objects in low visibility. A 2024 U.S. Department of Transportation mandate requires AEB systems with night functionality in all new vehicles by 2029, propelling the adoption of advanced sensing technologies. The expected rise of L4 vehicles and robotaxis in the 2030s will further boost demand for automotive LWIR cameras.

The 9x9 mm Artix UltraScale+ XA AU7P FPGA meets stringent automotive LWIR requirements with an automotive-grade package, AEC-Q00 qualification, and ISO 26262 ASIL-B certification. Leveraging the AMD LUT6 architecture and superior thermal resistance, it delivers exceptional efficiency, making the XA AU7P FPGA the premier choice for advanced night vision cameras.

# HIGHLIGHTS

### ADVANCED DSP COMPUTE FOR IMAGE SENSOR PROCESSING

- 216 DSP slices support real-time pixel correction and image enhancement for LWIR sensor data.

- Optimized for fixed- and floating-point computation.

# HIGH I/O BANDWIDTH AND COMPUTE FOR VEHICLE-WIDE COMMUNICATION

- AMD Artix UltraScale+ FPGAs offer up to 1.8X higher F<sub>MAX</sub> compared to Lattice 16 nm solutions, enabling faster real-time image processing.<sup>1</sup>

- 2.5 Gb/s MIPI performance supports the latest sensor technologies.

- The 16 Gb/s line rate enables high-speed data transfer from LWIR sensors to ADAS systems with optimal signal integrity.

## **KEY BENEFITS**

### HIGH COMPUTE TO OPTIMAL COST & POWER

ARTIX

Optimized performance per watt, delivering exceptional compute density in a cost-effective package.

#### FLEXIBILITY

Seamless integration with diverse sensor interfaces, ISP pipelines, and ADAS data types.

### STATE OF THE ART FUNCTIONAL SAFETY

Certified to ISO 26262 ASIL-B standards, ensuring reliable operation in critical automotive systems.

#### SECURITY

Features multi-level protection with RSA-2048 authentication, NIST-certified AES-GCM decryption, and anti-tamper capabilities. Other features include CNSA 2.0 PQC & certified secure boot.

#### AUTOMOTIVE-GRADE CHIPSCALE PACKAGE FOR SPACE-CONSTRAINED CAMERAS

- Ultra-compact 9x9 mm form factor fits into space-limited camera housings.

- Chipscale packaging enhances signal density, reliability, and electrical performance for edge sensors.

### LOW-POWER FOR ACCURATE THERMAL SENSING

- AMD UltraScale+ devices offer up to 46% lower total power compared to Lattice Nexus.<sup>2</sup>

- AMD packages offer up to 34% lower junction-to-ambient thermal dissipation compared to equivalent Lattice device packages,<sup>3</sup> allowing simplified thermal management in LWIR camera housings.

- AMD Artix UltraScale+ low-voltage, low-speed grade devices enable reduction in static and dynamic power.

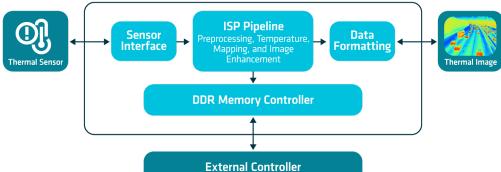

## **BLOCK DIAGRAM**

#### AMD Artix UltraScale+ XA AU7P FPGA

### FEATURES

#### AMD ARTIX ULTRASCALE+ XA FPGA HIGHLIGHTS

| ENHANCED & OPTIMIZED PROGRAMMABLE LOGIC<br>Architecture | <ul> <li>Up to 40% lower utilization with LUT6 architecture over LUT4<sup>4</sup></li> <li>Voltage scaling to tune power and performance on the same device</li> <li>Enhanced CLB/LUTs, routing, and ASIC-class clocking for high utilization</li> </ul>                                                                    |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HIGH-PERFORMANCE TRANSCEIVERS                           | <ul> <li>Minimum of 12 Gb/s and up to 16 Gb/s transceiver line rates</li> <li>Power-optimized architecture vs. Artix 7 FPGAs</li> <li>Single oscillator for fabric and SerDes eliminates extra clocking components</li> </ul>                                                                                               |

| EXCEPTIONAL DSP COMPUTE                                 | <ul> <li>Highest performance in a cost-optimized AMD FPGA</li> <li>Up to 1,860 GOP/s, 620 GFLOPs (FP32) in the largest device</li> </ul>                                                                                                                                                                                    |

| SAFETY AND MULTI-LEVEL SECURITY FEATURES                | <ul> <li>RSA-4096 authentication to verify design source</li> <li>NIST AES-CGM decryption approved, for faster configuration</li> <li>Permanent tamper penalty to prevent adversaries from accessing security features</li> <li>Security monitoring IP to adapt to security threats across the product lifecycle</li> </ul> |

| OUTSTANDING MIPI AND LVDS<br>Performance                | <ul> <li>Up to 2500 Mb/s MIPI and LVDS performance</li> <li>Support for advanced vision sensors (MIPI, SLVS-EC)</li> </ul>                                                                                                                                                                                                  |

| ANALOG MIXED-SIGNAL<br>Monitoring Block                 | <ul> <li>Voltage, current, and temperature tracking for safe, secure, and reliable operation</li> <li>Helps meet requirements for key standards: FIPS 140-2, IEC 61508, and ISO26262</li> <li>Allows for integration of low-amplitude sensors</li> </ul>                                                                    |

| ROBUST AUTOMOTIVE IP PORTFOLIO                          | <ul> <li>SEM-IP</li> <li>CAN/CAN-FD</li> <li>MIPI Controller</li> <li>Ethernet IP</li> <li>Video Processing IP: scalers, frame capture, color space converters, ISP, etc.</li> <li>DSP IP: FFT and assorted functions</li> </ul>                                                                                            |

## **NEXT STEPS**

- Explore a full list of <u>Automotive IP</u> offered through AMD & partners

- Learn more about the automotive-grade AMD Artix<sup>™</sup> UltraScale+<sup>™</sup> portfolio

- Learn more about <u>AMD competitive advantages</u> over other offerings in the market

#### ENDNOTES

- Based on AMD analysis in July 2024, calculating F<sub>MM</sub>, ratios averaged over 30 open-core designs for (16 nm) AMD Artix UltraScale+ AU7P FPGA, compared to the (16 nm) Lattice Avant E70 FPGA, at the respective highest speed grades. Results will vary based on architecture, device, speed grade, package size, design, configuration, and other factors. (AUS-010)

- Based on AMD testing in July 2024, performed in AMD Power Estimation Tools (XPE\_2019\_1\_2 for 28 nm node size and PDM\_2024.1 for 16 nm node size), and Lattice Radiant Power Estimation Tool 2024.1, to measure the power consumption of the AMD Spartan UltraScale+ FPGAs versus the Lattice Nexus platform. Total Power results include fabric power and HDIO only. Stated results assume a normalized max ambient temperature of 100°C. Actual performance, power consumption, and/or power savings will vary based on device, customer design specifications, system configuration, and other factors. (SUS-014)

- 3. Based on July 2024 AMD analysis of published data sheets using standard JESD51 definition for θJa versus equivalent Lattice packages. Stated results are provisional and will vary based on architecture, package size, speed grade, device, design, configuration, and other factors. (COP-002)

- 4. Based on AMD testing in July 2024, measuring the utilization scores of the LUT6 architecture-based AMD Artix 7 A100T (28 nm) and Artix UltraScale+ AU7P (16 nm) versus the LUT4 architecture-based Lattice Nexus MachXO5 25 (28 nm) and Lattice Avant E70 (16 nm) devices, measured on AMD Vivado 2024.1 and Lattice Radiant 2024.1, respectively, at various speed grades, averaged over 30 open-core designs. Results will vary based on architecture, device, speed grade, package size, design, configuration, and other factors. (COP-001)

#### DISCLAIMERS

The information contained herein is for informational purposes only and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and ssumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale. GD-18u

#### **COPYRIGHT NOTICE**

© 2025 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, Artix, UltraScale+, and combinations thereof are trademarks of Advanced Micro Devices. Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective owners. Certain AMD technologies may require third-party enablement or activation. Supported features may vary by operating system. Please confirm with the system manufacturer for specific features. No technology or product can be completely secure. PID3412950