AMD のコスト重視デバイスで実現する 産業オートメーションのフィールド機器 AMD ひ together we advance\_

### 概要

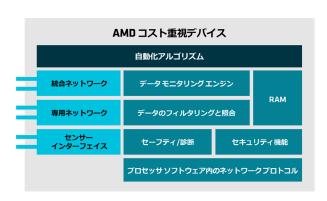

工場の生産性を高めるには、産業プロセスの自動化が不可欠です。特定のプロセスに関する 経験も重要ですが、自動化の進化を左右するのは基盤となる技術です。自動化による生産性の 最大化に必要な要素は次のとおりです。

- **コネクティビティ**:複数ネットワークへの接続により、即時情報と蓄積情報を最大限に活用 可能

- **メモリ**: ストリーミング データをローカル メモリに格納可能

- **リアルタイムのデータ監視、フィルタリング、照合:** デバイス内部のデータ処理エンジンで 実行

- 機能安全: 内蔵モニターとカスタム ロジックによる診断カバレッジを提供。認証済みの機能 安全対応の開発インフラ。

- **セキュリティ機能**: 改ざん防止、情報保護、サプライチェーン保証を提供し、フィールドの 自動化システムを攻撃から守る

AMDのコスト重視デバイスは、すべての機能を統合したプラットフォームを提供します。プログラム可能な構造により、ハードウェアを変更することなく、自動化アルゴリズムをライフサイクル全体にわたって継続的に最適化できます。

# 特長

#### AMD のコスト重視デバイスは、競合製品に比べて明確な優位性がある

- LUT6 アーキテクチャは、競合製品の LUT4 アーキテクチャと比較して最大 40% 優れた リソース利用効率を実現!

- 同じ 16 nm プロセス ノードで最高スピード グレードの場合、平均 1.8 倍の  $F_{\text{MAX}}$  を実現 $^2$

- LUT6 アーキテクチャと先進パッケージ技術の採用により、競合の LUT4 アーキテクチャと 比較して、総消費電力を最大 46% 削減<sup>3</sup>

- 認証された安全設計フロー

- AMD LogiCORE™ IP カタログ

## 主な利点

#### 拡張性

- 多様なロジック密度

- ・ 拡張可能な内蔵メモリ

- 豊富なプログラマブル I/O

- FPGA から SoC へ移行可能

### 安全認証

- ・ 設計フローの年次監査

- 認証済みの機能安全対応の開発インフラ

- 故障率解析ツール

#### セキュリティ機能

- ・ 認証と暗号化

- ・ システム モニター

- ・ セキュア プロビジョニング

- ポスト量子暗号 (PQC)

#### 長い製品ライフサイクル

- ・ 15 年以上の供給保証

- フィールド アップデートが可能

- 製品ファミリ間の移行が簡単

インテリジェントなフィールド機器

## 差別化要因

| アダプティブ テクノロジの特長    |                                                                                                           |  |

|--------------------|-----------------------------------------------------------------------------------------------------------|--|

| 拡張可能なデータ取得         | <ul><li>プログラム可能な I/O</li><li>イーサネット、産業用ネットワーキング、TSN*</li><li>高速トランシーバー</li></ul>                          |  |

| 既設システムへの柔軟な対応      | ・新旧いずれの産業機器にも接続可能<br>・3.3V 対応 I/O を多数搭載 (Spartan™ UltraScale+™ FPGA)                                      |  |

| 次世代セキュリティ規格に<br>対応 | <ul> <li>セキュア ブートのためのポスト量子暗号化 (PQC)</li> <li>ユーザー制御可能なセキュリティ機能</li> <li>TRNG および PUF</li> </ul>           |  |

| 高い演算性能             | AMD MicroBlaze™ V (RISC-V ソフト コア) プロセッサによるスケーラブルな演算性能     LPDDR4 および LPDDR3* に対応するメモリ コントローラーとインターフェイスを内蔵 |  |

# ターゲット アプリケーション

#### スマート センサー

- フィールドバス、産業用イーサネット、イメージ センサー インターフェイス、SPI、I<sup>2</sup>C、A/D コンバーターなどを介して、あらゆる タイプのセンシング機器と柔軟に接続可能

- センサーから送られる周期的なデータをリアルタイムに処理

- プログラマブル ロジック内のアルゴリズムを使用して受信データを処理

- イーサネット接続で上位システムの IP ネットワークと連携

- AMD ツールを使用する共通の設計フローで、各構成要素を統合

### アクチュエーターを高性能かつ安全に制御

- インバーター制御用の決定論的な制御ループを高速なプログラマブルロジックで実行し、従来比 1.8 倍のクロック周波数で処理可能<sup>2</sup>

- 接続されるアクチュエーター数に応じて拡張可能

- AMD Isolation Design Flow (IDF) による分離監視で、診断カバレッジを向上

- AMD のウェブサイトにあるセーフティ ラウンジで、包括的なユーザー ガイド、ツール、およびセーフティ マニュアルを提供 (アクセスには機能安全パッケージの購入が必要)

- AMD の機能安全認証済み設計フローでタイム トゥ マーケットを加速

### インダストリアル IoT におけるデータ収集と転送

- ブロック RAM、UltraRAM、分散 RAM など、容量の異なるオンチップ RAM を搭載

- RISC-V ISA 準拠の MicroBlaze V コントローラーおよびアプリケーション プロセッサ

- AMD TSN (Time Sensitive Networking) サブシステムを搭載した Artix™ UltraScale+ FPGA

- プログラミング ファイルの真正性を検証し、IP を保護するセキュリティ機能

- 複雑な処理タスクでも、Vivado™ 統合開発環境ですばやく簡単にタイミング クロージャを達成できる⁴

<sup>\*</sup>一部のデバイスでのみ対応

### IP

| 主な IP                        |                                                                                                                              | 提供元     |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------|

| TSN エンドポイント サブシステム           | ・AMD の Time Sensitive Networking (TSN) LogiCORE IP により、AMD SoC のプロセッサ システムを<br>TSN インフラに直接接続可能                               | AMD     |

| マネージド/アンマネージド<br>イーサネット スイッチ | ・このスイッチ IP を使用することで、ポート数を柔軟に構成できるイーサネット インフラを構築可能。<br>最大 10 Gb/s のインターフェイス速度に対応                                              | SOC-E   |

| 産業用ネットワーキング                  | <ul> <li>Profinet や EtherNet/IP に対応し、FPGA に組み込まれた MicroBlaze プロセッサを活用することで、<br/>リアルタイム性が確保された産業用ネットワーク ソリューションを実現</li> </ul> | SOFTING |

### 機能

| プラットフォームの特長              |                                                                                                                                                                          |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPARTAN ULTRASCALE+ FPGA | <ul> <li>3.3V 対応ボートを多数備え、業界最高クラスの I/O 対ロジックセル比率<sup>5</sup></li> <li>DDR メモリ コントローラーを内蔵*</li> <li>PCle® Gen4 対応*</li> <li>省電力向けの低密度デバイス</li> </ul>                       |

| ARTIX ULTRASCALE+ FPGA   | <ul> <li>最大 16 Gb/s のトランシーバーを搭載</li> <li>超小型の InFO および CSP パッケージに対応</li> <li>最大 1.8 TeraMAC の大容量 DSP 帯域幅を実現</li> <li>AMD の TSN (Time Sensitive Networking) IP</li> </ul> |

<sup>\*</sup> 一部のデバイスでのみ対応

# 次のステップ

- AMD およびパートナーが提供する産業用 IP を確認する

- AMD Spartan UltraScale+ FPGA の詳細を確認する

- AMD Artix UltraScale+ FPGA の詳細を確認する

- ・ 競合製品と比較した AMD 製品の優位性について理解する

#### 脚注

- 1. 2024年7月にAMD が実施したテスト結果に基づいています。LUT6 アーキテクチャベースの AMD Artix 7 A100T (28 nm) および Artix UltraScale+ AU7P (16 nm) と、LUT4 アーキテクチャベースの Lattice Nexus MachX05 25 (28 nm) および Lattice Avant E70 (16 nm) デバイスのリソース使用率を比較しました。AMD Vivado 2024.1 と Lattice Radiant 2024.1 をそれぞれ使用して、さまざまなスピード グレードで実施し、30 種類のオープンコア デザインを基に平均を算出しました。実際の結果は、アーキテクチャ、デバイス、スピード グレード、バッケージ サイズ、設計、構成、およびその他の要因によって変動する可能性があります。(COP-001)

- 2. 2024 年 7 月に AMD が実施した分析結果に基づいています。30 種類のオープンコアデザインを対象に、AMD Artix UltraScale+ AU7P FPGA (16 nm) と Lattice Avant E70 FPGA (16 nm) の F<sub>MAX</sub> 比率を平均化し、それぞれの最高スピード グレードで比較しました。実際の結果は、アーキテクチャ、デバイス、スピード グレード、パッケージ サイズ、設計、構成、およびその他の要因によって変動する可能性があります。 (AUS-010)

- 3. 2024年7月にAMD が実施した評価に基づいています。28 nm 向けの AMD Power Estimation Tool (XPE\_2019\_1\_2)、16 nm 向けの PDM\_2024.1、および Lattice Radiant Power Estimation Tool 2024.1 を使用し、Spartan UltraScale+35P、50P、100P FPGA と、Lattice MachXO5-NX 25、CertusPro-NX 50、および MachXO5-NX 100T FPGA の消費電力を比較しました。すべて HP (High Performance) スピード グレードで評価されています。合計電力の測定には、ファブリックおよび HDIO の電力のみが含まれています。結果は、最大周囲温度を100°Cとして測定したもので、比較対象のデバイスを選ぶ際には LUT6 アーキテクチャの利用効率が 40% 優れていることを考慮しています。測定結果は、製品の市場投入後に変更される可能性があります。また、アーキテクチャ、バッケージ サイズ、スピード グレード、デバイス、設計、構成、およびその他の要因によって変動する可能性があります。(SUS-014)

- 4. 2024 年 9 月に実施した AMD 配置配線テストに基づいています。 Vivado 2024.1 および Lattice Radiant Software 2024.1 のデフォルト モードでコンパイルした 26 のオープンコア デザインを対象に、Artix UltraScale+ AU10P と Lattice Mach LFMX05 (F<sub>MAX</sub> 目標 150 MHz)、および Kintex UltraScale+ KU5P と Lattice Avant E70 (F<sub>MAX</sub> 目標 200 MHz) を比較しました。 PGR の性能は、使用するデバイス、設計、構成、およびその他の要因により変動します。 (VIV-011)

- 5. I/O あたりのロジックセル比が最も高いという結果は、AMD Spartan UltraScale+ SU10P FPGA の製品データシートと、Efinix、Intel、Lattice、Microchip の 28 nm またはそれ以下のノードサイズを採用した競合 FPGA の公開製品データシートを比較した、AMD 社内分析に基づいています。I/O あたりのコスト削減は、200 以上の GPIO を必要とする設計において、2024 年 2 月時点の AMD のリスト価格に基づき、Spartan UltraScale+ SU10P と Spartan 7 7550 を比較したものです。(SUS-011)

### 免責条項

ここに記載されている情報は、情報提供のみを目的としており、事前通知なしで変更される場合があります。この資料の作成時には確認を重ねているものの、技術的な誤りや欠落、誤記などが含まれる可能性があり、AMD は 当該情報の更新または修正の義務を負いません。Advanced Micro Devices, Inc. は、この資料の内容の正確性または完全性に関していかなる表明または保証も行わず、ここに記載される AMD ハードウェア、ソフトウェア、 その他の製品の操作または使用に関して、非侵害、商品性、特定の目的への適合性の黙示的な保証を含め、いかなる種類の責任も一切負わないものとします。この資料は、黙示的あるいは禁反言で生じるものを含め、いかなる知的財産権へのライセンス付与を行うものではありません。AMD 製品の購入または使用に適用される条件および制限は、当事者間で締結された契約または AMD 標準売買条件に規定されているとおりです。GD-18u。

### 商標情報

© 2025 Advanced Micro Devices, Inc. All rights reserved. AMD、AMD Arrow ロゴ、Artix、Kintex、LogiCORE、MicroBlaze、Spartan、UltraScale+、Vivado、およびそれらの組み合わせは、Advanced Micro Devices, Inc. の商標です。PCle は、PCl-SIC Corporation の登録商標です。本ドキュメントに使用されるその他の商品名は情報提供のみを目的としており、各所有者の商標である可能性があります。一部の AMD テクノロジでは、サードパーティによる有効化またはアクティブ化が必要になる場合があります。サポートされる機能はオペレーティングシステムによって異なる場合があります。具体的な機能については、システム メーカーにお問い合わせください。完全に安全なテクノロジや製品はありません。PID3510500