##

# HOW TO PROGRAM AMD VERSAL<sup>™</sup> AI ENGINES IN SIX STEPS

### A quick guide for FPGA architects and engineers

AMD Versal<sup>™</sup> AI Engines are programmable arrays of vector processors that are ideal for compute-intensive workloads. Programming AI Engines requires a different methodology than traditional FPGAs, but the AMD Vitis<sup>™</sup> development platform makes programming easy.

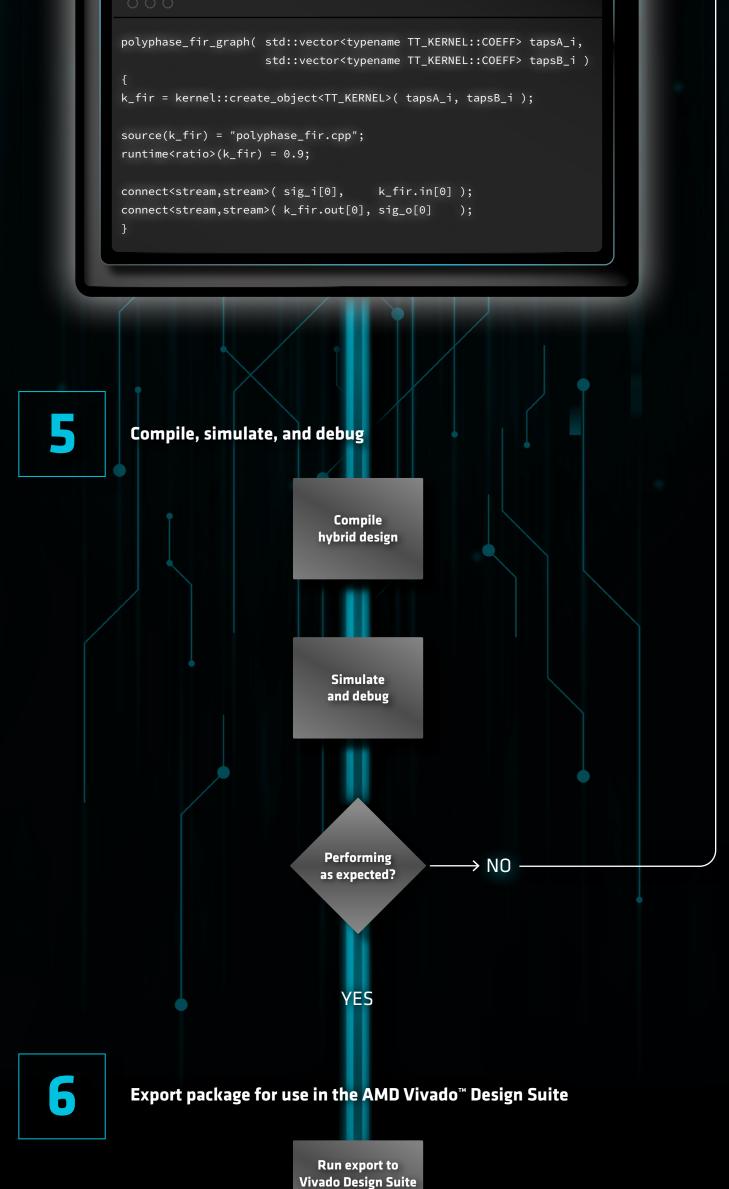

When the AI Engine design is completed within the Vitis platform, the design can be exported and integrated into a larger system using AMD Vivado<sup>™</sup> design tools.

Let's see how it works by exploring how to program a polyphase channelizer.

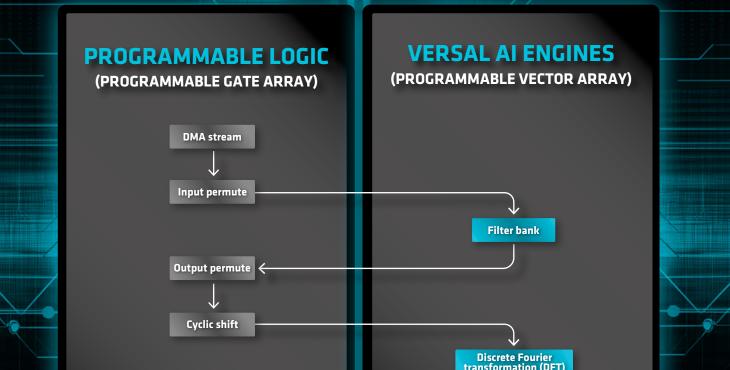

#### Map workloads and functions to programmable logic and Versal AI Engines

Functions that move and reorder data run efficiently in programmable logic.

Filtering and Fourier transformations have inherent parallelism that can be vectorized, so they map efficiently to the Versal AI Engines.

transformation (DFT) DMA stream Develop and simulate in the Vitis platform < Implement and instantiate Versal AI Engine kernels **Build with Vitis** C/C++ libraries, APIs, and intrinsics //call filter bank function polyphase\_fir(TT\_COEFF (&taps0\_i)[NUM\_POLY\*TAPS\_PER\_PHASE], TT\_COEFF (&taps1\_i)[NUM\_POLY\*TAPS\_PER\_PHASE] ); //implement discrete fourier transform template<class TT\_DATA,class TT\_COEFF,class TT\_ACC,unsigned NSAMP> dft\_1xN\_input<TT\_DATA,TT\_COEFF,TT\_ACC,NSAMP>::dft\_1xN\_input( TT\_COEFF (&coeff0\_i)[8], TT\_COEFF (&coeff1\_i)[8] ) : coeff0( coeff0\_i ), coeff1( coeff1\_i ) aie::set\_rounding(aie::rounding\_mode::positive\_inf); aie::set\_saturation(aie::saturation\_mode::saturate);

Integrate and interconnect via Graph C code

e ...

Vitis platform

# EVALUATE AI ENGINES IN AMD VERSAL ADAPTIVE SoCs AMD VERSAL

Versal AI Engines are available as options in several Versal adaptive SoCs:

Versal<sup>™</sup> AI Core Series | Versal<sup>™</sup> AI Edge Series | Versal<sup>™</sup> Premium Series

### **START DESIGNING**

Learn more about programming Versal adaptive SoCs, then experiment with shifting DSP algorithms and functions to Versal AI Engines for acceleration of your high-performance signal processing system.

**Dive Deeper**

© 2025 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, Versal, Vitis, Vivado, and combinations thereof are trademarks of Advanced Micro Devices, Inc. in the United States and other countries. Other product names used in this publication are for identification purposes only and may be trademarks of their respective owners.