# Designing With The AMD MicroBlaze™ V Processor for The AMD Spartan™ Ultrascale+™ FPGA

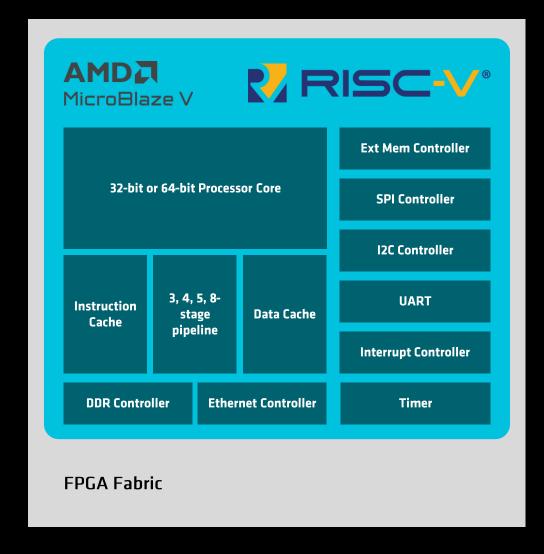

# **AMD MicroBlaze™ V Soft Processor**

#### **AXI Interconnect**

- Plug-and-play design integration

- Extensive soft IP peripherals

#### **RISC-V Extension Support**

Support for extensions: M, A, F, D, C, Zb[abcs], Zicsr, Zifencei, Zicbom

#### Area & Performance Tuning

- Configurable pipeline length

- Optional instruction and data caches

#### **Lockstep Capable**

- Tamper resistance

- Fault protection

# Triple Modular Redundant (TMR) Capable

- Single event upset (SEU) mitigation

- Voter circuit

#### **Predefined Configurations**

- Microcontroller: Area optimal

- Real-Time: RTOS support with soft DDR controller and cache

AMD together we advance\_

### **Additional Resources**

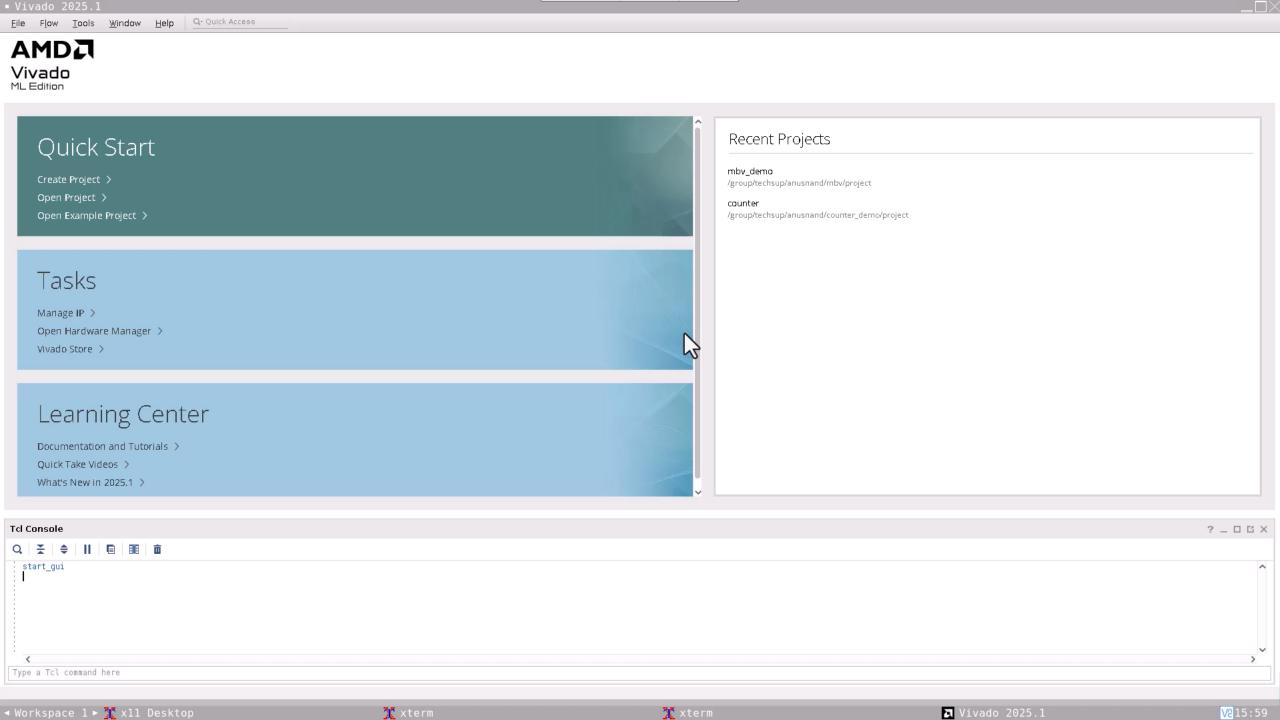

Programming an

Embedded MicroBlaze™

Processor Tutorial

#### UG1629:

MicroBlaze V Processor Reference Guide

#### PG428::

MicroBlaze Debug Module V LogiCORE™ IP Product Guide

#### WP469:

<u>Using MicroBlaze to Accelerate</u> <u>Cost-Sensitive Embedded</u> <u>System Development</u>

#### **UG1711:**

MicroBlaze V Processor Embedded Design User Guide

#### **PG112:**

LMB BRAM Interface Controller LogiCORE IP Product Guide

#### GitHub:

<u>Vivado-Design-</u> <u>Tutorials/Designing in IPI</u>

#### XMP507:

MicroBlaze V Processor Quick Start Guide for Vitis™ Unified 2024.1

#### PG268:

<u>Triple Modular Redundancy</u> (TMR) <u>LogiCORE IP Product</u> Guide

#### GitHub:

Embedded-Design-Tutorials/Programming an Embedded MicroBlaze V Processor

# **General Disclaimer and Attribution Statement**

The information contained herein is for informational purposes only and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale. GD-18u.

© 2025 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, Vivado, MicroBlaze and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective owners. Certain AMD technologies may require third-party enablement or activation. Supported features may vary by operating system. Please confirm with the system manufacturer for specific features. No technology or product can be completely secure.

#