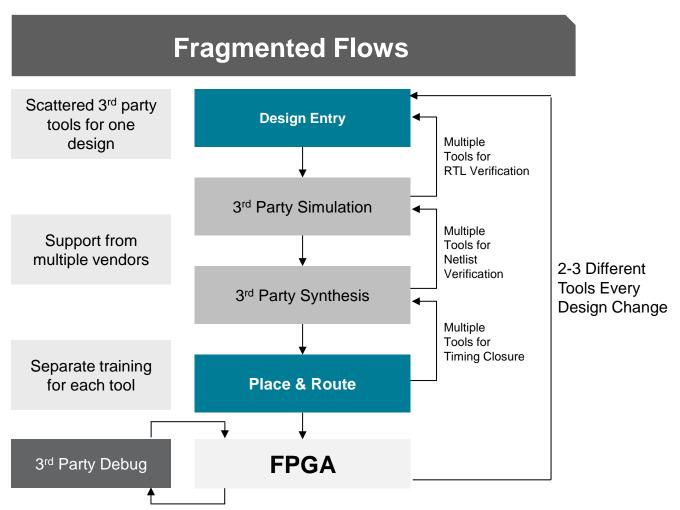

#### INDUSTRY CHALLENGES WITH FRAGMENTED TOOL FLOWS

#### **Time to Design Closure**

- Meeting F<sub>MAX</sub> target can be unpredictable

- Varying levels of tool optimization features

- Implementation flows spanning multiple tools can cause delays

#### **Developer Efficiency**

- Fragmented flow left for user to maintain

- Limited automation across entire flow

#### **Learning Curve**

- New training per tool

- Varying levels of learning resources

- Multiple sources of technical support

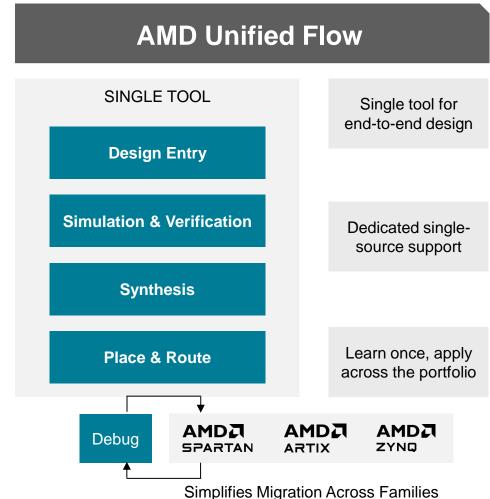

# AMD VIVADO™ DESIGN SUITE FOR STREAMLINED DESIGN CYCLES

#### **Design Entry**

- Import RTL and/or GUI-based IP Integration

- High-level design w/structured C++ or MATLAB®

#### Simulation & Verification

- Behavioral (RTL) or gate-level (post-synthesis)

- AMD Vivado<sup>™</sup> simulator (no-cost) & 3rd party simulator support

#### **Implementation**

- Native RTL synthesis integrated with P&R

- Guided flows and ML-based algorithms for QoR

#### **Debug**

- Integrated Logic Analyzer (ILA) IP (ChipScope)

- Integrated with P&R for fast iterations

**Free Standard Edition**

AMD together we advance\_

#### BENEFITS OF A UNIFIED VS. FRAGMENTED FLOW

# AMD VIVADO™ ADVANCED FEATURES TO ACCELERATE PRODUCTIVITY

#### **Integrated Flow Across Cost-Optimized Portfolio**

- Tool recommendations for timing closure

- ML-based implementation algorithms

#### **Fast Design Iterations**

- Incremental compile flows

- Ease-of-use features at every stage of the flow

#### **Accurate Power Estimation**

- Holistic system-level power budgeting & thermal design

- Informed device selection

#### STARTS WITH DESIGN ENTRY

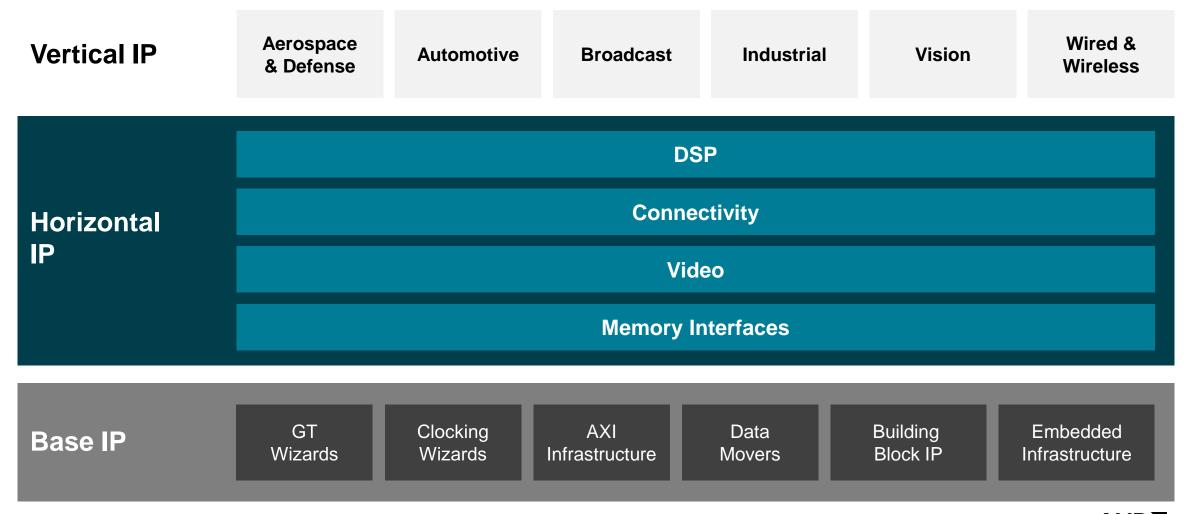

#### LARGE IP CATALOG TO ACCELERATE THE DESIGN PHASE

#### **OVER 500 CORES**

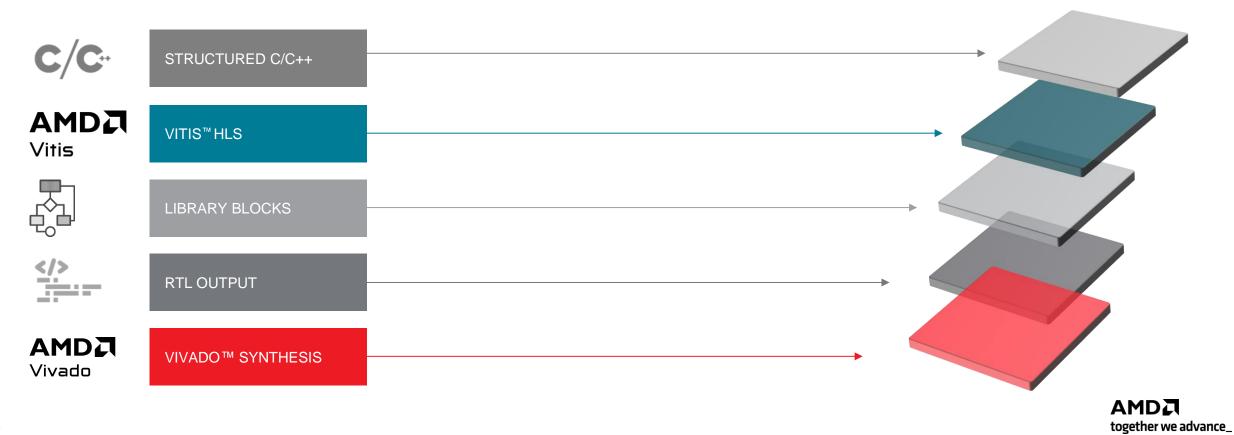

# HIGH-LEVEL SYNTHESIS WITH C/C++ FOR HIGHER LEVELS OF ABSTRACTION

- Design in structured C/C++ → synthesizable libraries → RTL for implementation in hardware

- AMD Vivado<sup>™</sup> RTL synthesis under the hood

- Ideal for algorithmic development or production IP with moderate QoR requirements

#### DESIGNING WITH MATHWORKS MATLAB OR SIMULINK

- Design with MATLAB® or Simulink® → synthesizable libraries → RTL for implementation in hardware

- AMD Vivado™ RTL synthesis under the hood

- Ideal for fast Proof of Concepts for algorithms

## MEET TARGET F<sub>MAX</sub>

# DESIGN ANALYSIS & STRATEGY RECOMMENDATIONS TO MEET TARGET $F_{M\Delta x}$

#### **RQA**

#### **Report QoR Assessment**

- Scores the design, predicts likelihood of meeting F<sub>MAX</sub>

- Flags issues that impact performance

- Done post-synthesis or at any stage of implementation flow

# Reports Window Layout View Report IP Status Compare Block Designs... IO Timing Report Methodology... Report DRC... Report Design Analysis... Report QoR Suggestion... Report QoR Assessment...

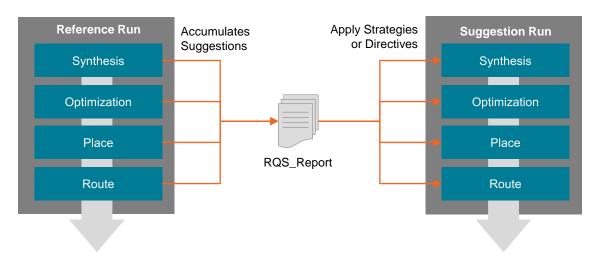

#### RQS

#### **Report QoR Suggestions**

- Suggests compile strategies or directives to improve F<sub>MAX</sub>

- Analyzes design at different stages of implementation flow

- RQS improves RQA score

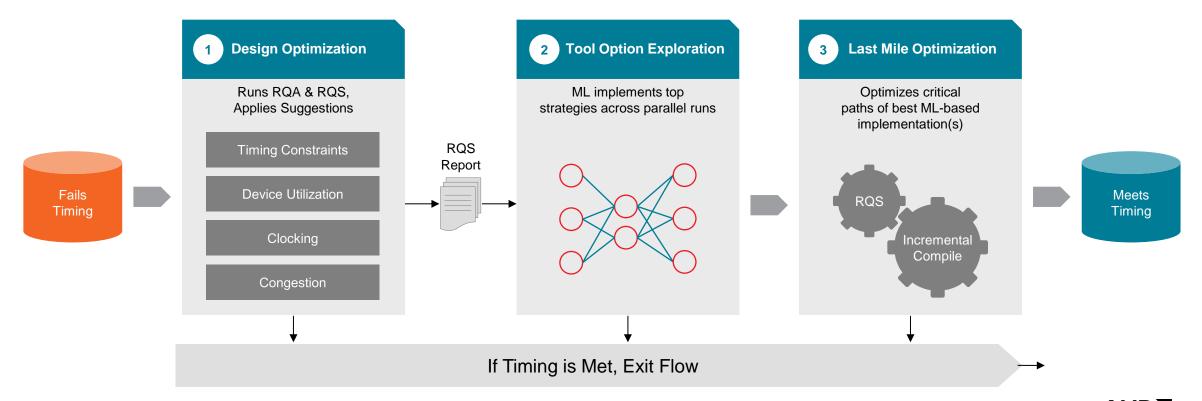

# INTELLIGENT DESIGN RUNS: ML-BASED IMPLEMENTATION ALGORITHMS

- The Intelligent Design Run (IDR) flow provides automated timing closure, leveraging RQA and RQS

- Uses machine learning to estimate delays & congestion, then recommends constraints to improve timing

- ML strategies implement tool options and directives across multiple runs

#### **FAST DESIGN ITERATION**

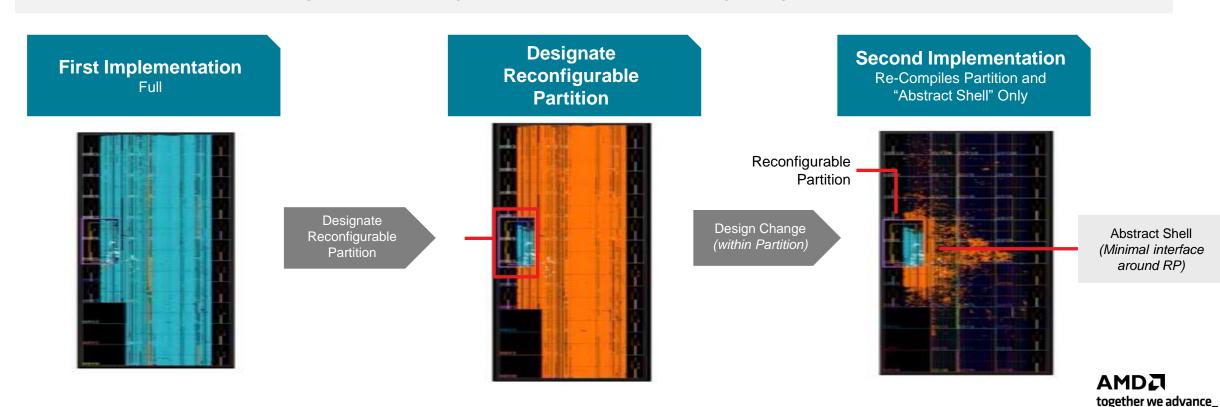

#### ABSTRACT SHELL FOR OPTIMAL COMPILE TIME

- Fast place-and-route compile times on incremental design changes

- Leverages Dynamic Function eXchange ('partial reconfiguration') technology

- User designates portion of design ("Reconfigurable Partition") to be modified, e.g., frequently updated IP

- AMD Vivado™ tools will only recompile the module and minimal boundary interface → Abstract Shell

- Ideal for team-based design, the need (e.g., distribute partitions among designers)

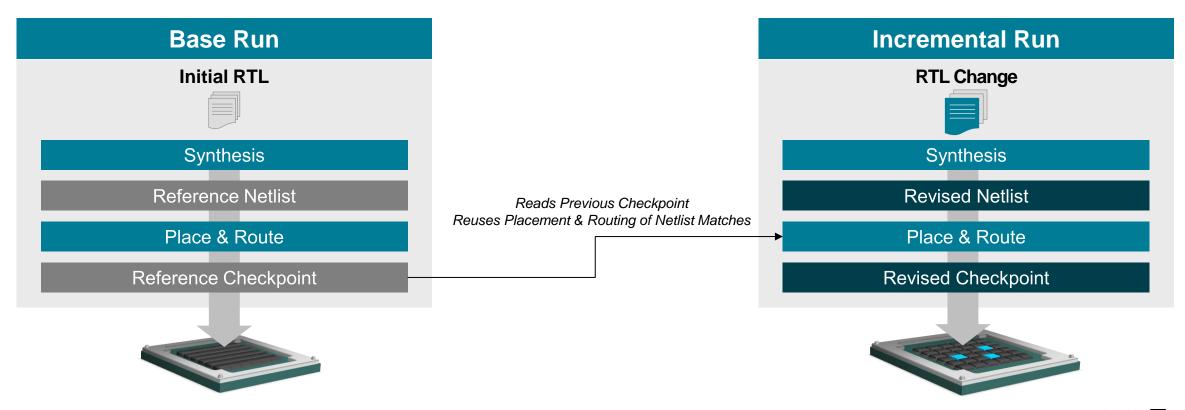

#### **INCREMENTAL COMPILE**

- Speeds up compile time by reusing synthesis and P&R data from base run

- Good for small changes, e.g., < 5% of design (e.g., minor updates, RTL bug fixes, adding debug cores)</li>

- Helps ensure timing closure of previous run is maintained

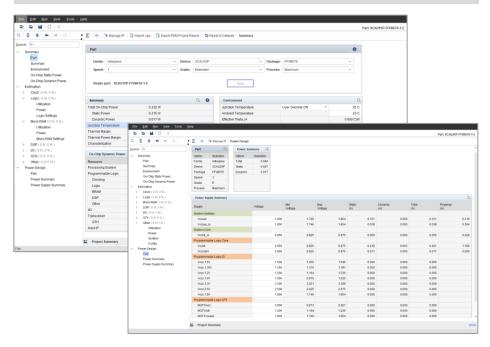

#### **ACCURATE POWER ESTIMATES**

#### **POWER DESIGN MANAGER**

#### **Early Power Estimates**

- Allows for optimal device selection to meet thermal & power req's

- Estimates power, explore tradeoffs before design and implementation

#### **Accurate Power Estimates**

- Up-to-date power characterization models

- IP wizards for granular, accurate power for hard and soft IP

#### **Explore Power Management Techniques**

- Clock Gating, Logic Gating

- Frequency Scaling

#### **XPE (Xilinx Power Estimator) vs. PDM Support**

- 7 Series devices supported by XPE only (no PDM)

- XPE still supported for AMD Artix UltraScale+ for Zynq UltraScale+

- PDM Supports AMD UltraScale+ devices or later

Stand-Alone Tool, License-Free does not require any other software

#### **GETTING STARTED AND KEY TAKE-AWAYS**

#### AVAILABLE AMD VIVADO™ RESOURCES

#### **Collateral & Docs**

- UltraFast™ Methodology Guide

- UltraFast Quick Reference Guide

- Timing Closure Quick Reference Guide

- Intelligent Design Runs White Paper

- **Abstract Shell White Paper**

- Abstract Shell Case Study

- And more . . .

#### **Videos & Tutorials**

- Design Flow Tutorial (UG888)

- Logic Simulation Tutorial (UG937)

- UltraFast Methodology Checklist

- Vivado IP Flow

- Designing with IP Integrator

- Introduction to Clock Constraints

- **Abstract Shell**

- Logic Debug in Vivado

- Intro to Power Design Manager

- And more ...

#### **On-Demand Courses**

- Designing with Vivado Part 1

- Designing with Vivado Part 2

- Designing with Vivado Part 3

- Designing with Vivado Part 4

- **Design Closure Techniques**

- Designing with IP Integrator

- Dynamic Function Exchange

#### **Support Forums**

- Installation & Licensing

- Design Entry & IP Flows

- Simulation & Verification

- Synthesis

- **Implementation**

- Timing & Constraints

- Debug & Tools

- **Advanced Flows**

#### **From Partners**

designlinx\*

Coaching

**Live Training**

SYSELLENT

इवार्वेट्ट्राप्ट्रिकारे

Download Vivado<sup>™</sup> Design Suite at <u>www.amd.com/vivado</u>

#### **Faster Development and Trusted Results**

#### **Integrated Tool Flow Across Cost-Optimized Portfolio**

#### AMD T

#### **Trusted QoR Results**

- Meet F<sub>MAX</sub> quickly with advanced flows

- Fast iterations for timing closure

- ML algorithms for advanced techniques

#### AMD ARTIX

#### **Developer Efficiency**

- 100+ Soft IPs to jumpstart design

- High-levels of abstraction

- Fast compile times and iterations

- Accurate and early power estimation

### AMD ZYNQ

#### **Rapid Learning Curve**

- Library of collateral, videos, & courses

- Example designs and trainings

- Single source for technical support

#### DISCLAIMER AND ATTRIBUTIONS

#### **DISCLAIMER**

Timelines, roadmaps, and/or product release dates shown in these slides are plans only and subject to change.

The information contained herein is for informational purposes only, and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale. GD-18

©2024 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, Artix, Spartan, Vitis, Vivado, Zynq, and combinations thereof are trademarks of Advanced Micro Devices, Inc. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# AMDI