# **AMD** Vitis<sup>™</sup> Functional Simulation

# **Agenda**

- What is Functional Simulation?

- Introduction to AMD Vitis™ Functional Simulation (VFS)

- Vitis Array (varray)

- VFS in MATLAB® / Python™ Environment

#### What is Functional Simulation?

#### **Functional Simulation**

#### Test and verify the functional correctness of the design

- Generate test vectors and simulate the behavior

- Bit-accurate simulation

- Use x86 simulator for AI Engine component

- Use C-Sim for HLS (PL) component

- · Custom testbench is required

# Programmable Logic (PL)

FPGA Logic

Simulated using C-Sim (if written in Vitis HLS)

#### AMD Versal™ Al Engine Array

**AIE Function**

Simulated using x86 simulator

AMD Together we advance\_

#### Simulation in High-Level Languages

Why?

Simulation of the algorithmic part of a design in high-level languages is critical in shortening development time and accelerating time to market.

What?

AMD Versal<sup>™</sup> devices introduce Al Engines in addition to programmable logic and a simulation solution should seamlessly incorporate both compute domains.

The simulation should be done in the customer's preferred language.

# **Challenges**

Customers cannot functionally simulate an Al Engine graph or the HLS component in MATLAB® and Python™ frameworks.

Customers cannot functionally simulate a heterogeneous design in MATLAB and Python frameworks.

Solution

AMD Vitis<sup>™</sup> functional simulation allows customers to functionally simulate using the MATLAB or Python frameworks.

# **Agenda**

- What is Functional Simulation?

- Introduction to AMD Vitis™ Functional Simulation (VFS)

- Vitis Array (varray)

- VFS in MATLAB<sup>®</sup> / Python<sup>™</sup> Environment

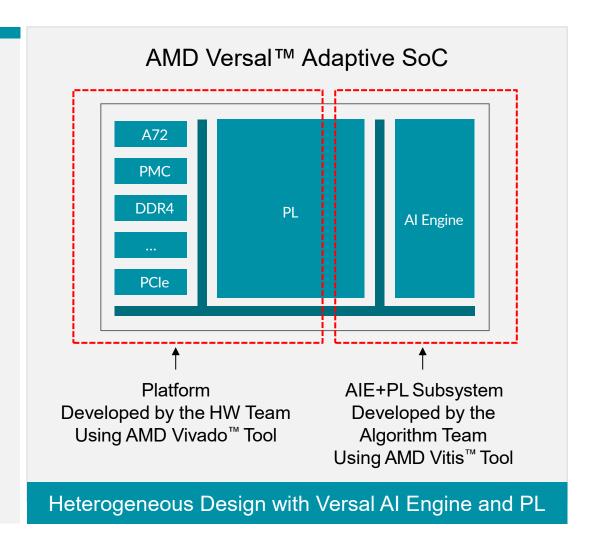

### Introduction to AMD Vitis™ Functional Simulation (VFS)

Heterogeneous design with AMD Versal™ AI Engine and HLS (targeting the PL)

#### Enables functional verification of:

- Al Engine graph natively in the MATLAB® or Python™ framework

- HLS kernel natively in the MATLAB or Python framework

- AIE-PL (HLS) subsystem natively in the MATLAB or Python framework

Maintain original environment – minimizes changes during verification

Support heterogeneous systems

Bit-accurate functional simulation

Al Engine (AMD IP or Custom IP)

Programmable Logic (HDL, HLS) (AMD IP or Custom IP)

Functionally simulate each component or co-simulate

AMD Vitis™ Functional Simulation

(MATLAB, Python)

Cycle accurate simulation of each component

AIE Simulation/HLS RTL cosim

#### Benefits of AMD Vitis™ Functional Simulation

AMD VFS automatically compiles

Al Engine graphs or HLS kernels

if required

Simulate and debug when building up the design – high level of design visibility

Provides choice of frameworks to match needs (MATLAB® or Python™ environments)

Fast simulation speed – run millions of vectors and analyze system metrics (SNR, BER, etc.) in a closedloop environment

Flexible options to instantiate the components and simulate: Use a config file or key-value pairs

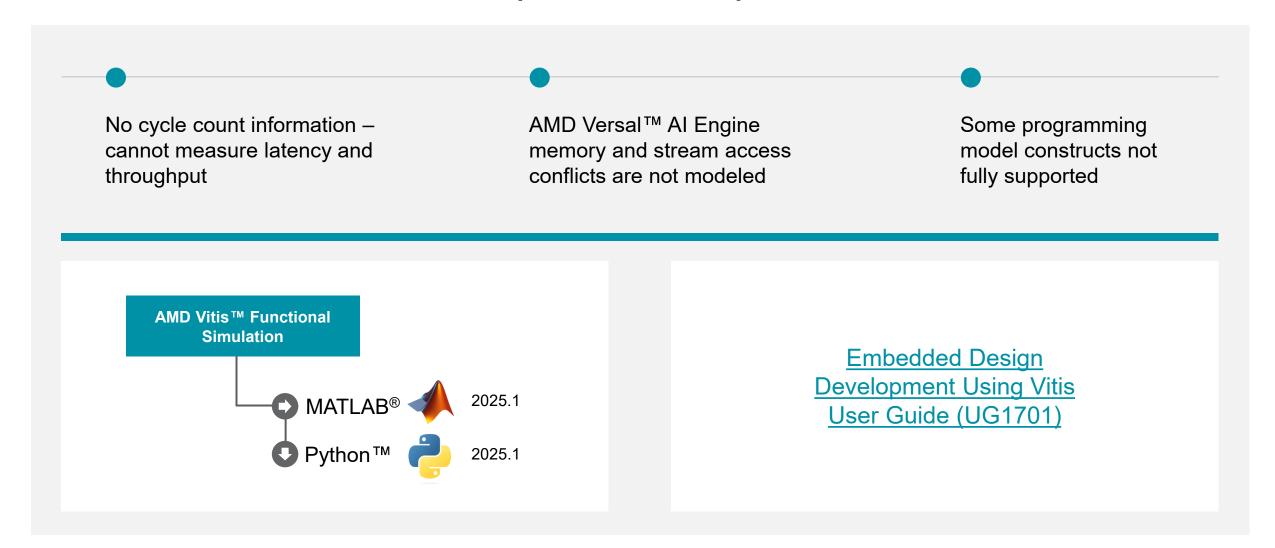

## **Current Tool Constraints (as of 2025.1)**

# **Agenda**

- What is Functional Simulation?

- Introduction to AMD Vitis<sup>™</sup> Functional Simulation (VFS)

- Vitis Array (varray)

- VFS in MATLAB® / Python Environment™

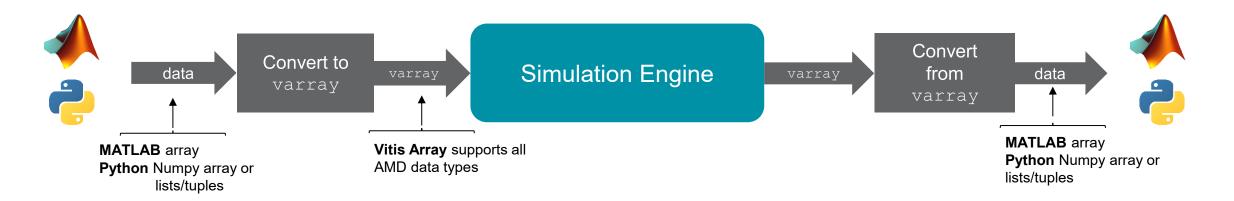

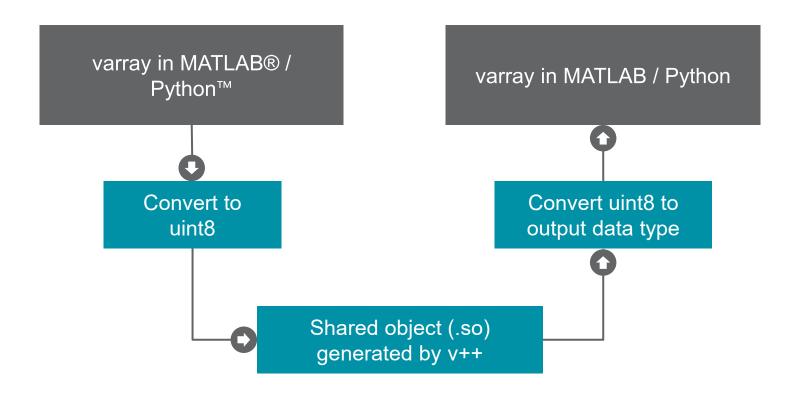

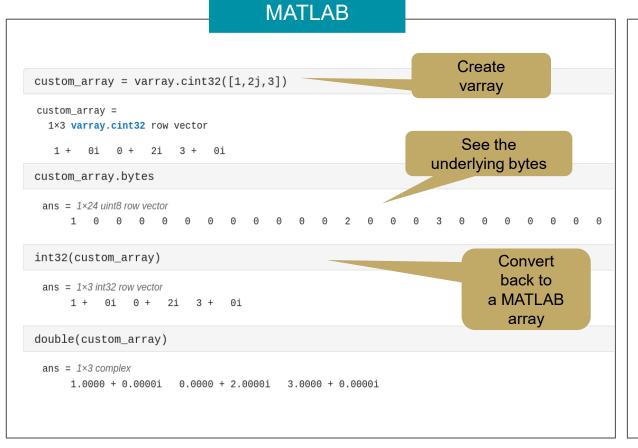

### AMD VFS and AMD Vitis™ Array (varray)

AMD Vitis™ Array (varray)

- A module to support all data types for AMD devices in MATLAB<sup>®</sup> / Python™

- Allows conversion and casting between the data types

The simulation engine needs to support all data types supported by AMD devices

Not all AMD supported data types are natively supported in MATLAB / Python

### Varray and Supported Data Types

| int8, uint8, cint8, cuint8                 |

|--------------------------------------------|

| int16, uint16, cint16, cuint16             |

| int64, uint64, cint64, cuint64             |

| float, cfloat                              |

| double, cdouble                            |

| float8, bfloat8 (2025.2)                   |

| float16 (AIE-ML v2)                        |

| Bfloat16, cbfloat16 (AIE-ML)               |

| mx9,mx6,mx4 (AIE-ML v2) <sup>1</sup>       |

| uint4,int4 (AIE-ML v2)                     |

| fi(sign, width, fractional) <sup>2,3</sup> |

|                                            |

- 1 You can specify a rounding mode for mx data types.

- 2 For fi, Overflow mode: Saturate, Rounding mode: Nearest

- 3 In HLS, we specify the bit width and the integer bits ap\_fixed<16,16> is equivalent to fi(1,16,0)

# Varray in MATLAB® / Python™ Environment

```

PYTHON

import numpy as np

import varray as va

Create varray

# Create a numpy array

in data = np.array([1.0, 2.0], 3.0])

# Initialize a custom varray with a specific data type

custom array = va.array(in data, va.cint32)

See the

print(custom array)

underlying bytes

print(custom array.bytes)

13 numpy array = np.array(custom array)

✓ 0.0s

Convert back

varray.cint32(dtype=varray.cint32)

to numpy

[1.+0.j \ 0.+2.j \ 3.+0.j]

```

## **Agenda**

- What is Functional Simulation?

- Introduction to AMD Vitis™ Functional Simulation (VFS)

- Vitis Array (varray)

- VFS in MATLAB® / Python™ Environment

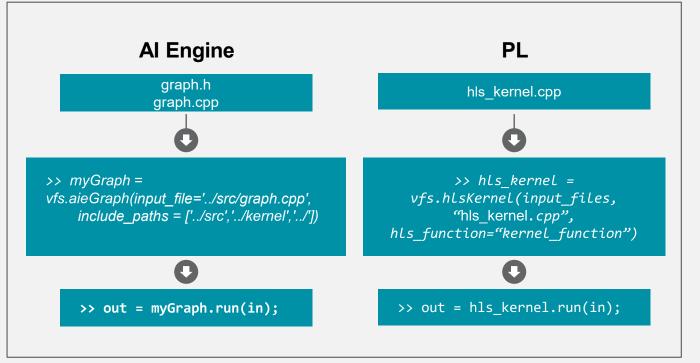

#### **AMD VFS Initialization Methods**

#### **Using a Configuration File**

- Specify a .cfg file with build details

- VFS checks for availability of build; updates

```

aie_graph =

vfs.aieGraph(config_file='<path_to_cfg_file>')

hls_kernel =

vfs.hlsKernel(config_file='<path_to_cfg_file>')

```

#### **Using Key-Value Pairs**

- Specify simulation parameters as key-value pairs

- VFS generates .cfg file and checks for build

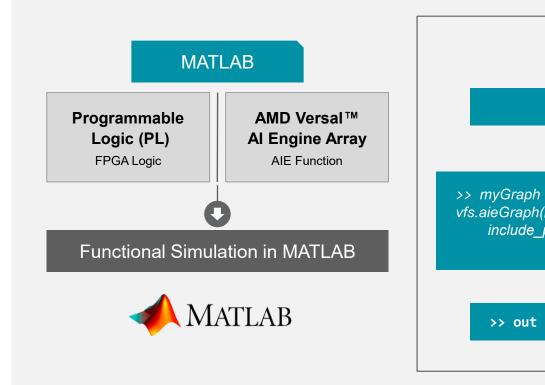

#### AMD Vitis™ Functional Simulation – MATLAB Environment

MATLAB® tool is the DSP environment of choice

Allows calling AIE graphs and PL (HLS) kernels directly from m-code

Generate data and simulate and verify functionality in the MATLAB environment

#### **AMD VFS with MATLAB Tool – Example**

#### FIR – Al Engine Graph

```

class FIR_Asymmetric_62a73e96 : public adf::graph {

public:

static constexpr unsigned int TP SSR = 1;

template <typename dir>

using ssr_port_array = std::array<adf::port<dir>, TP_SSR>;

ssr_port_array<input> in;

// No dual input

//No coeff port

ssr port array(output) out;

// No dual output

std::vector<cint16> taps = {{-13, 0}, {569, 0}, {95, 0},

xf::dsp::aie::fir::sr_asym::fir_sr_asym_graph<

cint16, //TT_DATA

cint16, //TT COEFF

32, //TP_FIR_LEN

16, //TP SHIFT

0, //TP_RND

256, //TP_INPUT_WINDOW_VSIZE

6, //TP CASC LEN

0, //TP USE COEFF RELOAD

1, //TP_NUM_OUTPUTS

0, //TP_DUAL_IP

0, //TP API

1, //TP_SSR

0 //TP_SAT

> filter;

FIR_Asymmetric_62a73e96() : filter(taps) {

adf::kernel *filter_kernels = filter.getKernels();

for (int i=0; i < 1; i++) {

adf::runtime<ratio>(filter_kernels[i]) = 0.9;

for (int i=0; i < TP_SSR; i++) {</pre>

adf::connect<> net in(in[i], filter.in[i]);

// No dual input

//No coeff port

adf::connect<> net_out(filter.out[i], out[i]);

// No dual output

```

#### VFS Call within MATLAB® to Graph Code

```

taps = [-13, 569, 95, -427, -289, 504, 601, -495, -1052, 323, 1700, 169, -2777, -1562, 5883, 13536,

num taps = length(taps);

myfir = vfs.aieGraph(input file = "../src/AI Engine FIR.cpp",...

Providing the

part = 'xcvc1902-vsva2197-2MP-e-S',...

input files,

include_paths = {"../src",...

target part and

sprintf('%s/L2/include/aie/',getenv("DSPL

include paths

sprintf('%s/L1/include/aie/',getenv("DSPL

sprintf('%s/L1/src/aie/',getenv("DSPLIB ROOT"))});

zi = zeros(num taps - 1, 1);

for i = 1:1

in 16bit r = randi([-2^12, 2^12-1], [2^20, 1], 'int16');

in 16bit i = randi([-2^12, 2^12-1], [2^20, 1], 'int16');

in c16 = complex(in 16bit r, in 16bit i);

Vitis Software

Platform array

in array = varray.cint16(in c16);

Running the

out c16 = myfir.run(in array);

AIE graph

[out c16 r, zi] = filter(taps, 1.0, in c16, zi);

delta = real(out c16)-real(int16(out c16 r));

absDelta = abs(delta);

%convert detla to double from int16 for division with a double number

assert(all(double(absDelta)/(2^16) < 1.42));

end

```

Creates an Al Engine graph

/ HLS kernel object

AMD Vitis™ Software Platform array appears, behaves, and operates like MATLAB array

"run" takes Vitis Software

Platform array input, runs the

graph, and produces the

output

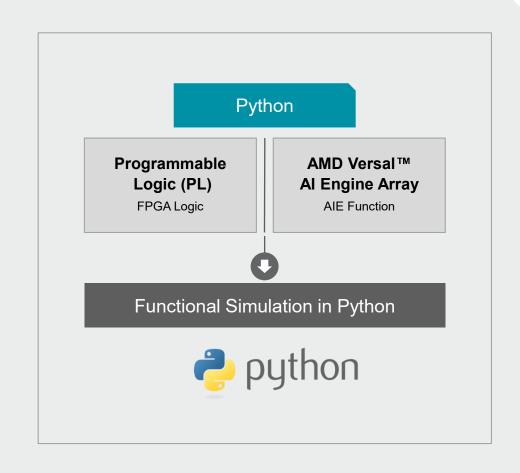

# AMD Vitis™ Functional Simulation – Python Scripting

Python™ scripting is a popular choice in machine learning applications

AMD VFS allows calling AI Engine graphs and PL (HLS) kernels directly from Python scripts

Users can take the design to the Python environment

– functionally simulate and verify

# AMD VFS with Python™ Scripting – Example

```

import vfs

import varray as va

import numpy as np

from scipy.signal import lfilter

import os

DSPLIB ROOT = os.environ["DSPLIB ROOT"]

taps = [-13, 569, 95, -427, -289, 504, 601, -495, -1052, 323, 1700, 169, -2777, -1562, 5883, 13536,

num taps = len(taps)

myfir = vfs.aieGraph(input file = "../src/AI Engine FIR.cpp",

part = 'xcvc1902-vsva2197-2MP-e-S',

Providing the input files,

include paths = ["../src",

DSPLIB ROOT + "/L2/include/aie/",

target part and include paths

DSPLIB ROOT + "/L1/include/aie/",

DSPLIB ROOT + "/L1/src/aie/"])

zi = np.zeros(num taps - 1)

for in range(1):

in 16bit r = np.random.randint(low=-2**12, high=2**12-1, size=(2**20,), dtype=np.int16)

in 16bit i = np.random.randint(low=-2**12, high=2**12-1, size=(2**20,), dtype=np.int16)

in c16 = in 16bit r+ 1j*in 16bit i

AMD Vitis™ Software

Platform array

in array = va.array(in c16, dtype = va.cint16)

out c16 = myfir.run(in array)

Running the AIE graph

out c16 r, zi = lfilter(taps, 1.0, in c16, zi = zi )

assert(np.all(abs(np.asarray(out c16)-out c16 r/2**16)<1.42))

```

## AMD VFS with MATLAB and Python – Example Comparison

Source: <path\_to\_tools>/settings64.(c)sh

##

#### Port Dump for Al Engine Graph

You can dump all the ports within the Al Engine graph into files:

```

myGraph = vfs.aieGraph(input_file = "../src/port_dump/vmc_model/code/ip/mySub/src/mySub.cpp", ..

part = 'xcvc1902-vsva2197-2MP-e-S',

Enable port dump

include paths = "../src/port dump/vmc model/");

myGraph.setPortDump()

in 32bit = va.array(np.random.randit(low=-2**30, high =2**30-1, size=(10**6,)), dtype = va.int32)

out32 bit = myGraph.run(int32 bit);

Run simulation

myGraph.writePortDump()

✓ aiePortDump / aieGraph / dump

≡ mygraph_mygraph_complex_in_out_in_0.txt

Dump files

≡ mygraph_mygraph_complex_in_out_out_0.txt

{} x86sim_simdata_index.json

x86sim_simdata_index.txt

```

### **Summary**

- AMD Vitis™ functional simulation (VFS) enables customers to develop subsystems in their own simulation frameworks

- Vitis Array supports all the datatypes available in AMD devices in both MATLAB® and Python™ environments and allows conversion and casting between the types

- VFS allows calling AI Engine graphs and HLS kernels directly from MATLAB or Python code

- O4 Subsystem simulation can be performed either through MATLAB or Python frameworks with VFS

- VFS can provide a high level of design visibility as it enables simulation and debug when build up a design

#### **General Disclaimer and Attribution Statement 2025**

The information contained herein is for informational purposes only and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale. GD-18u.

©2025 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, Versal, Vitis, Vivado, and combinations thereof are trademarks of Advanced Micro Devices, Inc. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. Python is a trademark of the Python Software Foundation. TensorFlow, the TensorFlow logo and any related marks are trademarks of Google Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective owners. Certain AMD technologies may require third-party enablement or activation. Supported features may vary by operating system. Please confirm with the system manufacturer for specific features. No technology or product can be completely secure.

# AMDI