AMD Spartan™ UltraScale+™ FPGAs Begin Production Shipments

Jun 17, 2025

High I/O, low power, and state-of-the-art security features for cost-sensitive edge applications

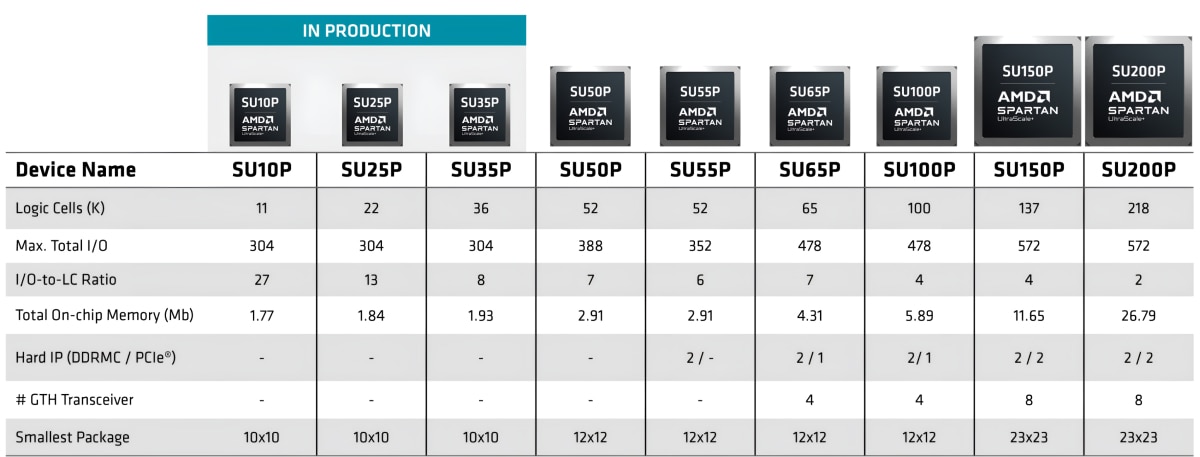

AMD is pleased to announce that the initial devices in the Spartan™ UltraScale+™ cost-optimized family are now in volume production! The three smallest devices, the SU10P, SU25P, and SU35P, are currently available for order with production device support in AMD Vivado™ Design Suite 2025.1.

Built for cost-sensitive edge applications requiring high I/O, low power, and state-of-the-art security features, this new offering in the AMD Cost-Optimized Portfolio brings modernized connectivity, post-quantum cryptography, and more to the proven UltraScale+™ portfolio of FPGAs and adaptive SoCs.

First production shipments of the three lowest-density devices mark a significant milestone in the availability of proven, small FPGA solutions for the low and mid-range markets.

A Proven Foundation for Fast Time to Market

Engineers looking for cost-optimized, compact FPGAs also want simplicity and a fast time to market. They need programmable logic, high I/O, robust security, and world-class reliability. They also need tools that deliver push-button timing closure and rapid debug capabilities. Above all, they need a low-risk path to market. Built by the industry leader1 using proven UltraScale+ technology, Spartan UltraScale+ FPGAs deliver exactly that.

With Spartan UltraScale+ FPGAs, AMD starts with a well-established UltraScale+ FPGA fabric, which provides an excellent balance of performance and low power—along with a long product lifecycle. For connectivity, Spartan UltraScale+ FPGAs combine high-density input/output (HDIO) for rich 3.3V I/O support, with new high-speed XP5IO and deliver the industry’s highest ratio of I/O to logic,2 powered by high-performance and low-power fabric. Designers can also expect fast design convergence and easy reuse across programs with the AMD Vivado Design Suite, offering support for more than 160 AMD FPGAs and adaptive SoCs. In applications such as board control and I/O expansion, where clock speeds rarely exceed 150 MHz, users can expect push-button timing closure for fast design iteration.3 For applications in machine vision, industrial, and medical requiring higher performance, Spartan UltraScale+ FPGAs deliver a two speed-grade advantage over the competition.4

New Capabilities for Cost-Sensitive Applications

Building on this proven foundation, Spartan UltraScale+ FPGAs also bring several new advances to the AMD Cost-Optimized Portfolio:

- State-of-the-art security with hard IP for post-quantum cryptography using NIST-approved algorithms. This enables both secure device configuration and user access to dedicated cryptographic resources, including a true random number generator (TRNG), physical unclonable function (PUF), secure hashing, and more.

- An integrated memory controller for LPDDR4X/5 supporting up to 4266 Mb/s on a 32-bit interface saves up to 15 kLC, allowing designers to move into a smaller device and further reduce power and cost.

- The new XP5IO class supports low-voltage differential signaling (LVDS) up to 1.8 Gb/s, 3.2 Gb/s MIPI D-PHY, and other high-speed differential interfaces.

- Compliant PCIe® Gen4 hard IP, supporting both endpoint and root port applications.

- Octal SPI interface support for faster configuration and data transfer rates from external flash memory.

Like other AMD cost-optimized devices, support for Spartan UltraScale+ FPGAs is included in the free AMD Vivado Design Suite Standard Edition, enabling everything from simulation to verification in a single tool. Download the Vivado Design Suite and get started today.

Footnotes:

- Revenue data, Omida Competitive Landscape Tool CTL Quarterly Semiconductor Market Share, November 2023. (SUS-012)

- Based on AMD internal analysis December 2023, comparing the total I/O-to-logic-cell ratio for AMD Spartan UltraScale+ FPGAs to previous generations of AMD cost-optimized FPGAs. (SUS-001)

- Based on AMD place-and-route testing in September 2024, using 26 open-core designs compiled with AMD Vivado 2024.1 and Lattice Radiant Software 2024.1 in default mode, with the Artix UltraScale+ AU10P device versus Lattice Mach LFMXO5 device @ 150 MHz FMAX target; and Kintex UltraScale+ KU5P device versus Lattice Avant E70 device @ 200 MHz FMAX target. P&R performance will vary based on device, design, configuration, and other factors. (VIV-011)

- Based on AMD analysis in July 2024, calculating the FMAX yields for all available speed grades for the (16 nm) AMD Artix UltraScale+ AU7P and the (16 nm) Lattice Avant E70. Actual results will vary based on architecture, device, speed grade, package size, design, configuration, and other factors. (AUS-009)

© 2025 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, Artix, Spartan, UltraScale+, Vivado, and combinations thereof are trademarks of Advanced Micro Devices, Inc. PCIe is a registered trademark of PCI-SIG Corporation. Other product names used in this publication are for identification purposes only and may be trademarks of their respective owners. Certain AMD technologies may require third-party enablement or activation. Supported features may vary by operating system. Please confirm with the system manufacturer for specific features. No technology or product can be completely secure.