Low Power

Spartan UltraScale+ FPGAs leverage a 16 nm architecture and offer up to a 30% reduction in total power compared to the previous 28 nm devices on lower densities.2 The larger density devices, which include hard DDR and PCIe interfacing IP, offer an improved power efficiency of up to 60% compared to the previous 28 nm devices,3 thereby enhancing overall system performance.

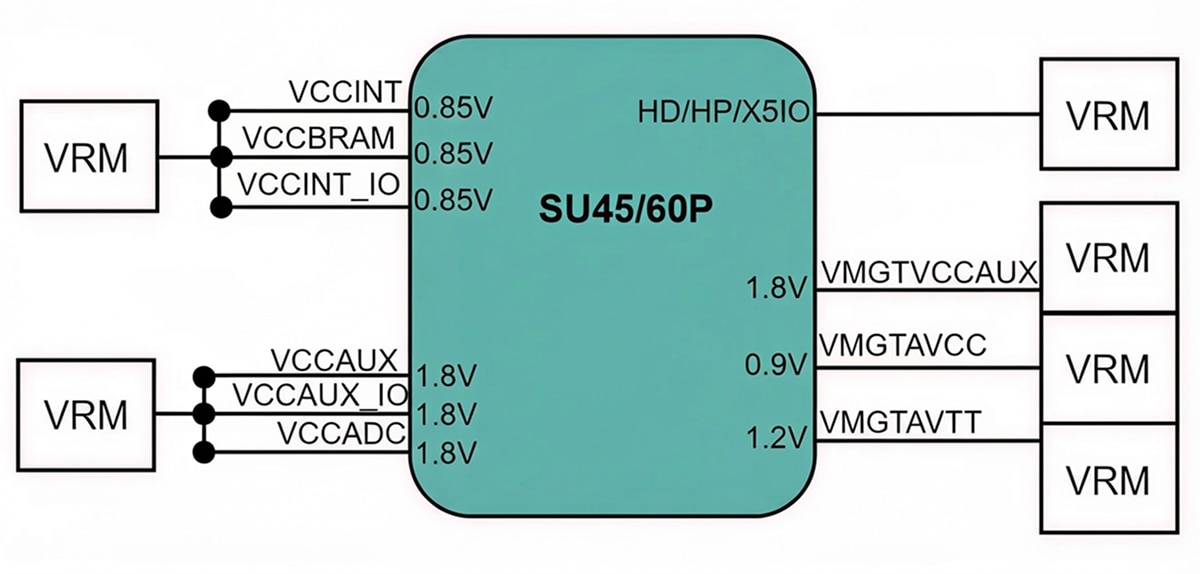

Power delivery for Spartan UltraScale+ FPGAs is simplified by combining power rails together, reducing the amount of voltage regulators required, thus reducing sequencing complexity and shrinking BOM. AMD has partnered with industry-leading power vendors to ensure flexible power solutions from discrete regulators and LDOs to sophisticated Power Management ICs (PMICs) with integrated power sequencing. Leveraging AMD AECG power reference designs can also accelerate time to market and help ensure your power solution meets your design needs.

Explore our Simplified Power Sequencing application note for techniques on reducing power sequencing complexity and leveraging partner sequencers. Visit the AMD Power Efficiency page for more information.