成熟可靠备受信赖持久耐用

AMD 器件的使用寿命一般超过 15 年,能够在您的设计的整个生命周期内可靠运行。AMD 7 系列 FPGA 和自适应 SoC 的使用寿命可持续到 2040 年,而 AMD UltraScale+™ FPGA 和自适应 SoC 的使用寿命可持续到 2045 年。

AMD Spartan™ UltraScale+™ 产品优势

随着越来越多的器件和传感器连接到边缘设备,市场对能够处理大量数据的安全器件的需求不断增加。AMD 全新推出的成本优化型 Spartan™ UltraScale+™ FPGA 凭借高 I/O、低成本、高能效和现代安全功能,可助力设计师快速应对这些挑战。

高 I/O、低功耗及先进的安全功能

- 采用 28nm 及以下制程工艺的卓越 FPGA,提供超高 I/O 逻辑单元比1

- 与上一代相比,采用 16nm FinFET 制程工艺的器件总功耗降低了 30%2

使用经验证的设计工具加快设计收敛

- 自 2012 年推出的强大、高品质 AMD Vivado™ Design Suite

- 涵盖从仿真到验证的各个环节,适用于各种类型的 FPGA

依托可信赖的供应商,确保设计一次性成功

- 深耕 FPGA 业务近 40 年,器件出货量达数十亿

- 超过 15 年的产品生命周期和现场可升级性,带来超长设计寿命

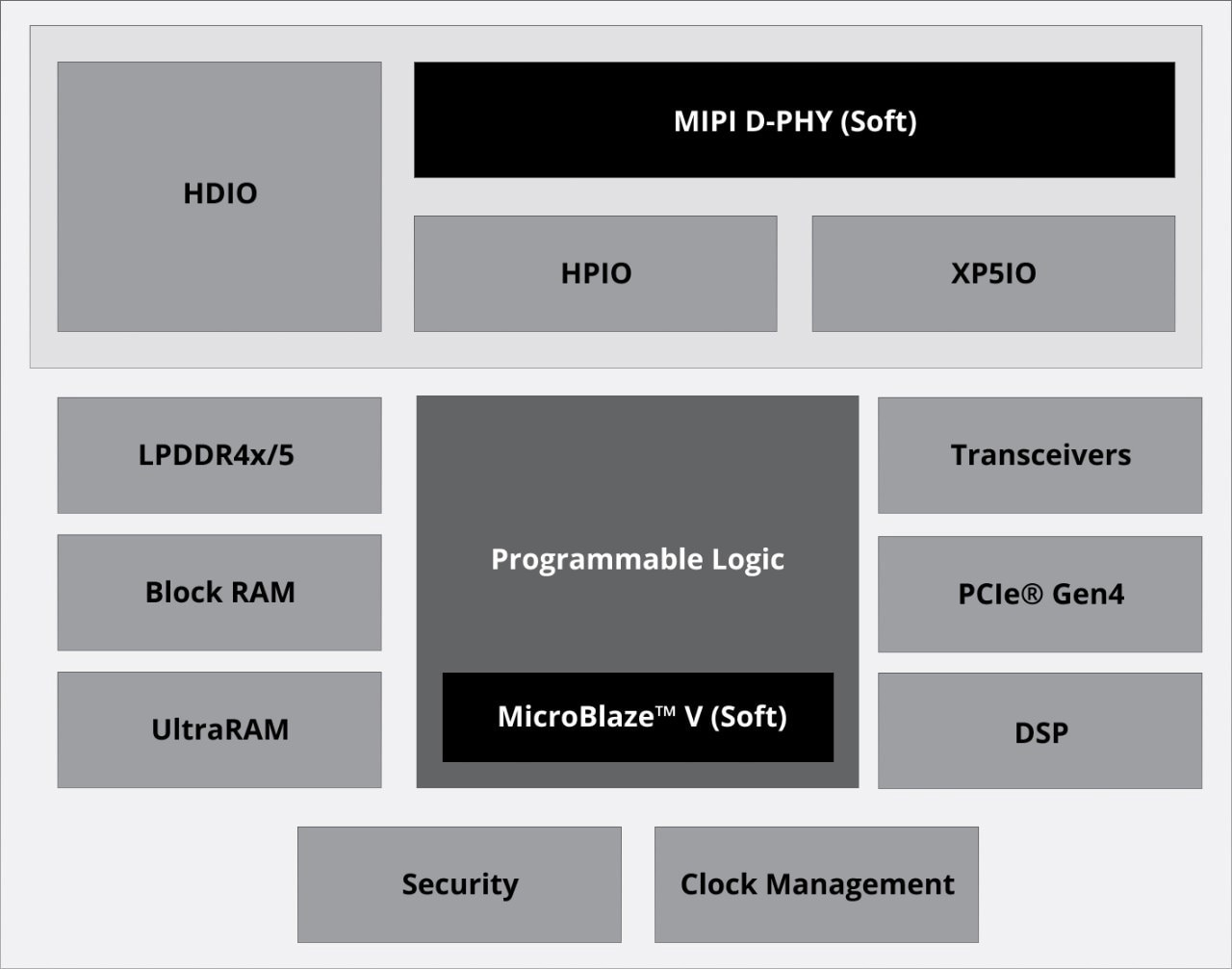

基本构建块

Spartan UltraScale+ FPGA 具有出色的 I/O 功能、低功耗以及先进的安全功能。该系列配备高速收发器、大量内置和外部存储器以及 PCIe® Gen4,为各种应用场景带来强大稳定的解决方案。

详细了解 Spartan UltraScale+ FPGA

AMD Spartan UltraScale+ FPGA 网络研讨会:带来高 I/O、低功耗及先进的安全功能

深入探索 Spartan UltraScale+ FPGA 的高 I/O、低功耗及先进的安全功能,并了解备受信赖的芯片供应商 AMD 如何凭借经验证的设计工具助您加快上市速度。

特性与优势

- 灵活的 I/O 接口

- 低功耗

- 先进的安全功能

- 集成型硬核存储器控制器

- MIPI 和 LVDS 性能

- 可扩展性

灵活的 I/O 接口

Spartan UltraScale+ FPGA 带来超多通用 I/O (GPIO),支持传统及新兴协议,并配备适用于网络、视频和视觉应用的 16.3Gb/s 收发器。此外,该系列器件还符合 PCIe® Gen4、10GE Vision、CoaXPress 2.1 和 12G-SDI 等行业标准,有助于加快产品上市进程。

低功耗

Spartan UltraScale+ FPGA 采用 16nm 架构,与之前较低密度的 28nm 器件相比,总功耗最多可降低 30%。2 高密度器件配备硬核 DDR 和 PCIe 接口 IP 等,与之前的 28nm 器件相比,能效提升最高可达 60%3,从而全面提高整体系统性能。

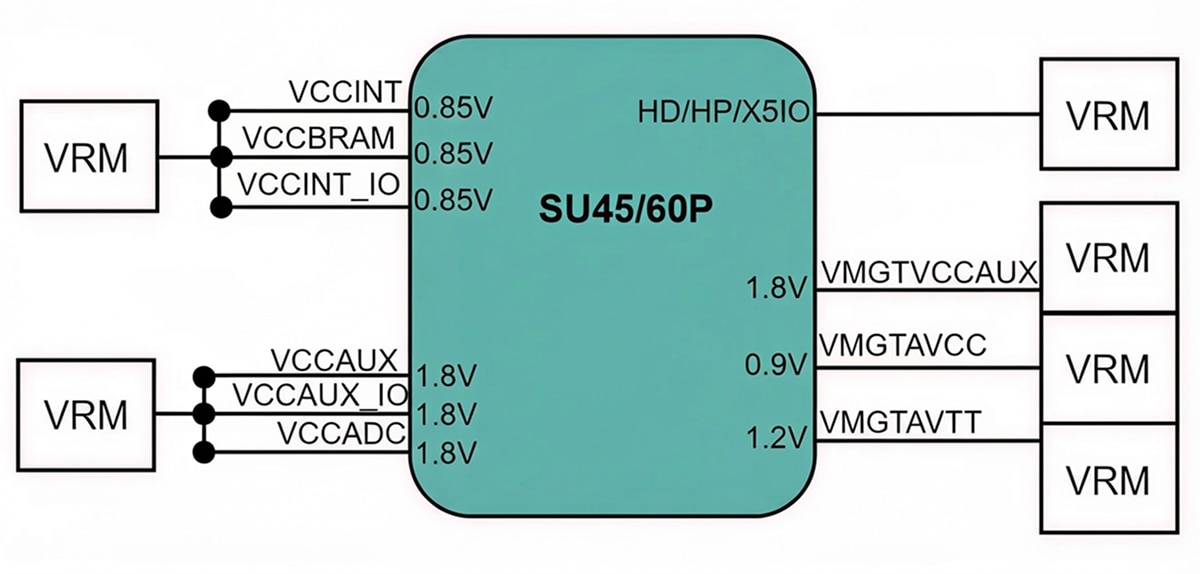

通过整合电源轨,Spartan UltraScale+ FPGA 的供电设计得以简化,减少了所需的电压调节器数量,进而降低了电源排序复杂度并缩减了物料清单 (BOM)。AMD 已与业界领先的电源供应商建立合作,确保提供灵活多样的电源解决方案,包括分立式电压调节器、低压差稳压器 (LDO) 以及集成电源排序功能的精密电源管理芯片 (PMIC)。借助 AMD AECG 电源参考设计,还可以加快产品上市速度,并确保电源解决方案满足您的设计需求。

请参阅我们的简化的电源排序应用指南,了解如何借助相关技术降低电源排序复杂度,以及如何利用合作伙伴定序器。有关更多信息,请访问 AMD 电源效率页面。

先进的安全功能

Spartan UltraScale+ FPGA 具有稳健的多层安全机制,其中包括经 NIST 批准的后量子加密、通过物理不可克隆功能实现的唯一设备标识、用于设备保护的永久性篡改惩罚、通过 DPA 反制机制实现的旁路攻击保护,以及高适应性 AES-GCM 解密以应对不断发展的安全威胁。

集成型硬核存储器控制器

在提高能效的同时,性能也通过硬 IP(例如特定器件中提供的集成型硬核存储器控制器 LPDDR4X/5)得到增强。这种硬核存储器控制器不仅支持高达 4.2 Gb/s 的直接、高吞吐量内存访问,而且还可降低高价值设计模块的 FPGA 架构资源消耗。

MIPI 和 LVDS 性能

Spartan UltraScale+ 系列成本优化型 FPGA 具有高达 3.2Gb/s 的 MIPI 性能,可为高级摄像头传感器的数据捕获与显示提供支持。完整的 MIPI IP 和参考设计解决方案可在此处深入了解。该系列 FPGA 还具有出色的 LVDS 性能,可支持包括 SLVS-EC(面向 CMOS 图像传感器)在内的众多协议。

可扩展性

经过量产验证的 UltraScale™ 架构采用台积电的 16nm 低功耗 FinFET 制程工艺,可扩展至其它 16nm 系列以及更广泛的产品系列。开发者可利用相同的 IP、工具流程和生态系统来保护设计投资,从而为各种产品系列提供可重复使用的平台。

应用

面向机器视觉的灵活 I/O

Spartan UltraScale+ FPGA 可提供低延迟连接和处理能力,符合工业和医疗领域各类传感器及机器视觉系统的连接标准。此外,该 FPGA 系列还与多种通信协议兼容,并提供紧凑型和低功耗产品。

多功能数据采集助力工业和医疗行业发展

Spartan UltraScale+ FPGA 提供高度灵活的 I/O、片上存储器以及高效的边缘处理能力,可充分满足市场对高级数据采集不断增长的需求。该系列 FPGA 具有低功耗、可扩展网络和高级安全功能,非常适合传感器聚合和护理点医疗系统等应用。

面向数据中心的低成本 I/O 扩展与主板管理控制器 (BMC)

在服务器制造商的主板设计变得日益复杂之际,Spartan UltraScale+ FPGA 可提供高效功耗管理、灵活 I/O 和参考设计(例如通用主板管理控制器),可充分满足数据中心服务器 I/O 市场的需求。Spartan UltraScale+ FPGA 系列器件可与各类服务器主机处理器主板和主板管理控制器卡实现同步扩展。

提升视频采集卡的广播效率

凭借强大的高级广播技术,Spartan UltraScale+ FPGA 带来非凡功能。通过 PCIe® Gen4 和硬核存储器控制器 LPDDR4x/5,视频采集卡可成功采集并传输高质量的基带视频。实时传输加上高效处理,不仅可简化视频采集过程,而且还能优化广播工作流程。

产品表

| SU10P | SU25P | SU35P | SU45P | SU60P | SU65P | SU100P | SU150P | SU200P | |

|---|---|---|---|---|---|---|---|---|---|

| 系统逻辑单元 (K) | 11 | 22 | 36 | 53 | 66 | 66 | 101 | 138 | 219 |

| CLB LUT (K) | 5 | 10 | 16 | 24 | 30 | 30 | 46 | 63 | 100 |

| DSP Slice | 24 | 36 | 48 | 96 | 144 | 144 | 144 | 384 | 384 |

| 总 RAM (Mb)* | 1.77 | 1.84 | 1.93 | 3.03 | 4.10 | 4.37 | 5.98 | 11.65 | 26.79 |

| 集成式内存控制器 LPDDR4X/5 | 0 | 0 | 0 | 0 | 0 | 2 | 2 | 2 | 2 |

| 收发器(16.375Gb/s 或 12.5Gb/s) | 0 | 0 | 0 | 4 | 4 | 4 | 4 | 8 | 8 |

| PCI Express® | 0 | 0 | 0 | 1x Gen4x4 | 1x Gen4x4 | 1x Gen4x4 | 1x Gen4x4 | 1x Gen4x8 或 2x Gen4x4 |

1x Gen4x8 或 2x Gen4x4 |

| 最大 I/O 引脚数 | 304 | 304 | 304 | 262 | 262 | 478 | 478 | 572 | 572 |

* 总 RAM = 最大分布式 RAM + 块 RAM 总计 + UltraRAM

根据器件数据手册或产品指南验证上表中的所有数据。

立即体验

利用面向量产芯片提供的经过验证的硬件、软件支持、工具、设计示例和文档,快速启动您的设计周期,并实现快速上市。欢迎利用以下资源,进一步了解 UltraScale™ 架构的设计工具和设计方法。

AMD SCU35 评估套件

SCU35 评估套件是采用 Spartan UltraScale+ SU35P FPGA 的高性价比开发平台,通过提供丰富多样的传感器和外设接口选项来满足不同应用需求。

查看 UltraScale 架构数据手册

查找完整 UltraScale 架构产品线的详细规格。

适用于 Spartan UltraScale+ 的 Vivado

详细了解 AMD Vivado™ Design Suite 如何凭借一键式时序收敛,减少迭代周期,加速 Spartan UltraScale+ 设计开发。

联系 AMD 销售人员

无论是咨询定价,还是申请抢先访问安全站点以体验预生产器件,亦或是需要特定支持,我们的销售团队都将随时提供协助,竭力满足您的需求。

其他支持和资源

联系销售人员

我们的销售团队将根据您的具体需求帮助您做出明智的技术决策。

附注

- “超高 I/O 逻辑单元比”这一结论基于 AMD 进行的内部分析。此次分析依据 AMD Spartan UltraScale+ SU10P FPGA 及同类产品的已发布产品数据手册,评估了 28nm 及更低制程 FPGA 的 I/O 逻辑单元比。根据截至 2024 年 2 月 AMD Spartan UltraScale+ SU10P 与 AMD Spartan 7 7550 的标价,并针对至少需要 200 通用 I/O (GPIO) 的用户设计,计算每个 I/O 组所节省的成本。(SUS-011)

- 预测基于 AMD 实验室 2024 年 1 月的内部分析,根据 AMD Artix UltraScale+ AU7P FPGA 的逻辑单元数量差异计算总功耗(静态及动态功耗),以使用 Xilinx Power Estimator (XPE) 工具(版本 2023.1.2)。预估的总功耗可能与最终产品上市后的实际总功耗有所不同,具体取决于配置、设计、使用情况和其他因素。(SUS-003)

- 预测基于 AMD 实验室 2024 年 1 月的内部分析,根据 AMD Artix UltraScale+ AU7P FPGA 的逻辑扩展数量计算总功耗(静态及动态功耗),以使用 Xilinx Power Estimator (XPE) 工具(版本 2023.1.2)估算 AMD Spartan UltraScale+ SU200P FPGA 与 AMD Artix 7 7A200T FPGA 的总功耗。实际总功耗在最终产品上市时可能会有所不同,具体取决于配置、设计、使用情况和其他因素。(SUS-006)

- “超高 I/O 逻辑单元比”这一结论基于 AMD 进行的内部分析。此次分析依据 AMD Spartan UltraScale+ SU10P FPGA 及同类产品的已发布产品数据手册,评估了 28nm 及更低制程 FPGA 的 I/O 逻辑单元比。根据截至 2024 年 2 月 AMD Spartan UltraScale+ SU10P 与 AMD Spartan 7 7550 的标价,并针对至少需要 200 通用 I/O (GPIO) 的用户设计,计算每个 I/O 组所节省的成本。(SUS-011)

- 预测基于 AMD 实验室 2024 年 1 月的内部分析,根据 AMD Artix UltraScale+ AU7P FPGA 的逻辑单元数量差异计算总功耗(静态及动态功耗),以使用 Xilinx Power Estimator (XPE) 工具(版本 2023.1.2)。预估的总功耗可能与最终产品上市后的实际总功耗有所不同,具体取决于配置、设计、使用情况和其他因素。(SUS-003)

- 预测基于 AMD 实验室 2024 年 1 月的内部分析,根据 AMD Artix UltraScale+ AU7P FPGA 的逻辑扩展数量计算总功耗(静态及动态功耗),以使用 Xilinx Power Estimator (XPE) 工具(版本 2023.1.2)估算 AMD Spartan UltraScale+ SU200P FPGA 与 AMD Artix 7 7A200T FPGA 的总功耗。实际总功耗在最终产品上市时可能会有所不同,具体取决于配置、设计、使用情况和其他因素。(SUS-006)