屢經考驗。深受信賴。歷久彌新。

有了至少 15 年起跳的典型使用壽命,您可以放心依靠 AMD 器件來維持您設計的生命週期:AMD 7 系列 FPGA 和自適應 SoC 的供貨期延長到 2040 年,AMD UltraScale+™ FPGA 和自適應 SoC 則延長到 2045 年。

AMD Spartan™ UltraScale+™ 產品優勢

由於邊緣端連接的器件和感測器越來越多,所以需要能處理大量資料的安全器件。全新的成本最佳化 AMD Spartan™ UltraScale+™ FPGA 系列,不僅具有高 I/O,亦透過提供實惠成本、出色能效和現代安全功能,協助設計人員迅速因應這些挑戰。

高 I/O、低功耗,具備最高水準的安全功能

- 採用 28 nm 與更小製程技術製造的 FPGA,有著業界最高的 I/O 對邏輯單元比1

- 相較於前一代,16 奈米 FinFET 製程最高可將總耗電量減少 30%2

使用歷經實證的設計工具加快設計收斂速度

- 自 2012 年至今,始終穩定投產且品質卓越的 AMD Vivado™ Design Suite

- 一項工具就能因應整個 FPGA 產品組合的模擬至驗證作業

值得信賴的供應商,一次設計抵用數年

- AMD 的 FPGA 事業已發展近 40 年,器件出貨量達到數十億

- 產品生命週期逾 15 年,現場可升級性有助於獲得最長的設計壽命

基礎建構模塊

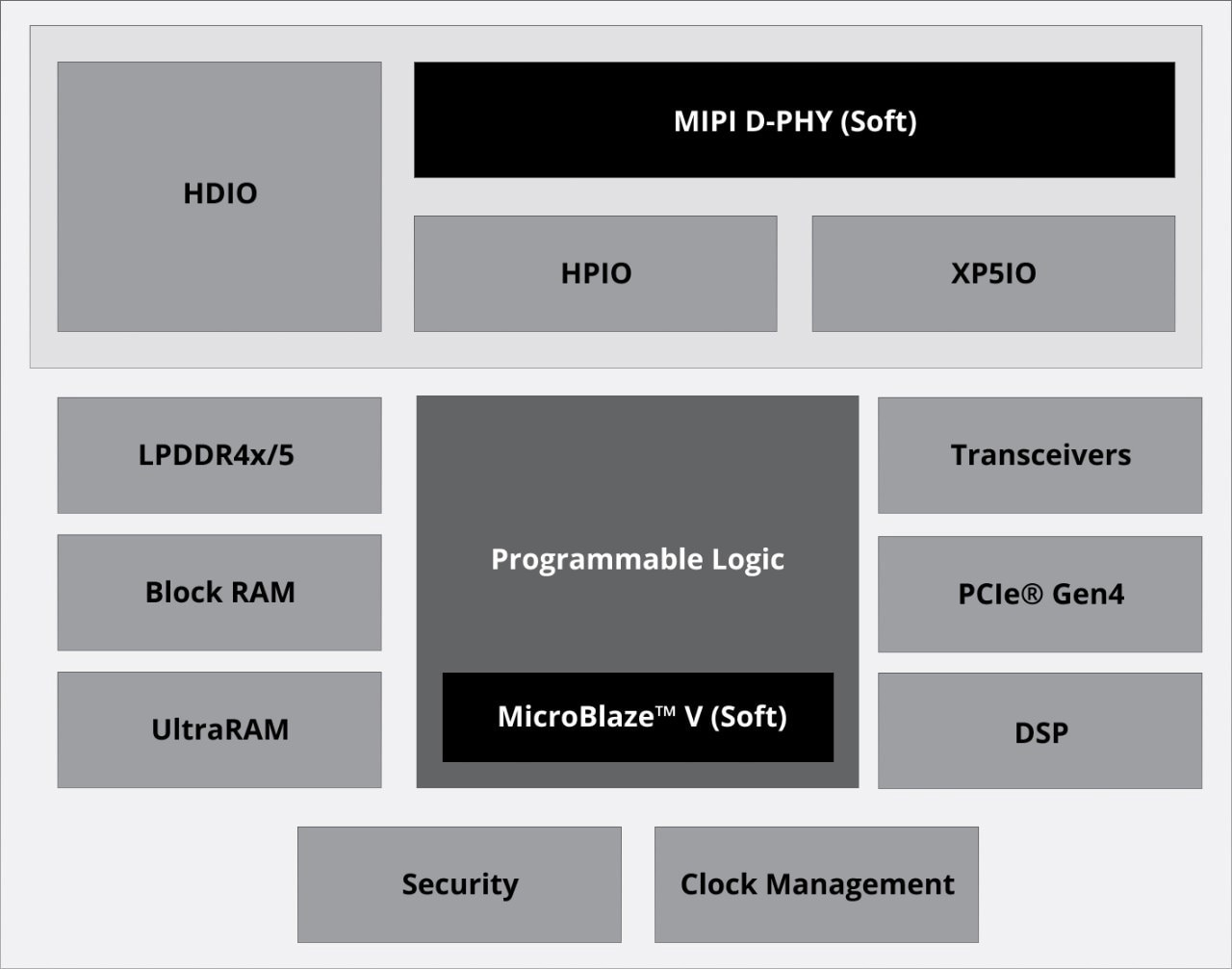

Spartan UltraScale+ FPGA 提供先進的 I/O 功能、低功耗和最高水準的安全功能。此系列搭載了高速收發器、強大的內建和外部記憶體及 PCIe® Gen4,可為各式各樣的應用提供穩健可靠的解決方案。

進一步瞭解 Spartan UltraScale+ FPGA

AMD Spartan UltraScale+ FPGA 網路研討會:提供高 I/O、低功耗,及最高水準的安全功能

深入探索 Spartan UltraScale+ FPGA 所具備的高 I/O、低功耗設計與先進安全功能,並瞭解如何透過 AMD 這個值得信賴的晶片供應商與其經實證的設計工具,縮短產品上市時間。

功能與優點

- 靈活的 I/O 介面

- 低功耗

- 最高水準的安全性

- 整合式硬式記憶體控制器

- MIPI 與 LVDS 效能

- 擴充性

靈活的 I/O 介面

Spartan UltraScale+ FPGA 提供高通用輸入輸出 (General Purpose Input Output, GPIO) 數、傳統和新興協定支援,以及用於網路、視訊和視覺應用的 16.3 Gb/s 收發器。這些器件亦符合業界標準,例如 PCIe® Gen4、10 GE Vision、CoaXPress 2.1 和 12G-SDI,有助於加快上市時間。

低功耗

Spartan UltraScale+ FPGA 採用 16 奈米架構,與先前密度較低的 28 奈米器件相比,總功耗最多降低達 30%2。密度較高的器件(包括硬式 DDR 和 PCIe 介面 IP),能效較先前的 28 奈米器件提升達 60%3,整體系統效能因而獲得大幅強化。

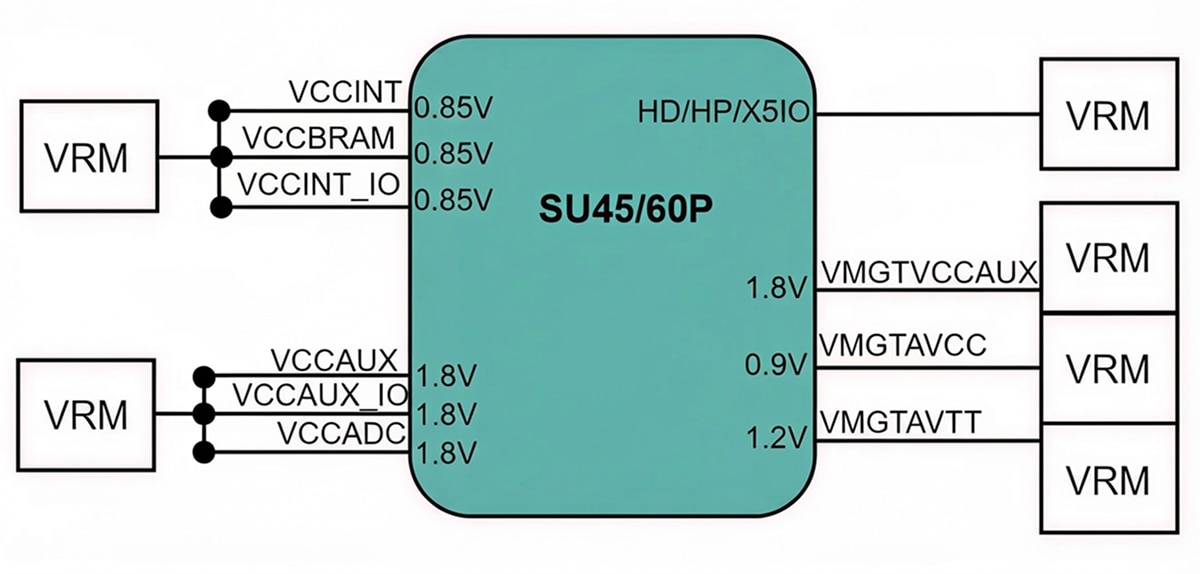

Spartan UltraScale+ FPGA 將電源軌結合在一起,減少所需要的電壓調節器數量,進而減少上電順序的複雜度並縮減 BOM,達到簡化供電的效果。AMD 持續與領先業界的電源廠商合作,確保各式電源解決方案的供應,從獨立調節器與 LDO,到具有整合式上電定序功能的精密電源管理 IC (PMIC),一系列方案供您彈性選擇。利用 AMD AECG 電源參考設計也能加速上市時間,並協助確保您的電源解決方案符合您的設計需求。

探索我們的簡化上電順序應用注意事項,瞭解降低上電順序複雜度和使用合作夥伴排序器的技術。如需更多資訊,請造訪 AMD 能源效率頁面。

最高水準的安全性

Spartan UltraScale+ FPGA 採取 NIST 核准的後量子密碼技術,提供穩健可靠的多層安全性,並透過物理不可複製函數,達成唯一裝置識別機制,同時還搭載永久防竄改功能可保護器件,並能利用 DPA 反制措施防範旁路攻擊,此外還有可自行調適的進階加密標準伽羅瓦計數器模式 (Advanced Encryption Standard Galois Counter Mode, AES-GCM) 解密技術,藉此因應瞬息萬變的威脅。

整合式硬式記憶體控制器

與其高能效表現相襯的是硬核 IP 帶來的強化效能,比方說特定器件型號就搭載了整合式硬式 LPDDR4X/5 記憶體控制器。這種硬式記憶體控制器,可直接以最高 4.2 Gb/s 的高輸送量存取記憶體,並降低高價值設計區塊的 FPGA 網狀架構資源使用率。

MIPI 與 LVDS 效能

Spartan UltraScale+ 系列具備成本最佳化 FPGA,可提供最高達 3.2 Gb/s 的 MIPI 效能,並支援先進的鏡頭感測器擷取及顯示。欲取得完整的 MIPI IP 和參考設計解決方案,也可參見此處。此系列的電壓差分訊號 (Low Voltage Differential Signaling, LVDS) 效能亦支援多種不同協定,包括 SLVS-EC(用於 CMOS 影像感測器)。

擴充性

經過投產實證的 UltraScale™ 架構,採用 TSMC 的 16 奈米低功耗 FinFET 製程打造而成,可進一步擴充至其他 16 奈米系列及其他系列產品。開發人員可以運用相同的 IP、工具流程和生態系統,使設計投資不至於浪費,進而打造出可重複利用於多款系列產品的統一平台。

應用程式

適用於機器視覺的靈活 I/O

Spartan UltraScale+ FPGA 為工業和醫療領域所用機器視覺系統的各種感測器和連線標準,提供低延遲的介面和處理能力。FPGA 系列亦與多種通訊協定相容,且器件能維持小巧外型和低功耗表現。

適合工業和醫療保健應用的多功能資料擷取

隨著市場對於先進資料擷取功能的需求不斷成長,Spartan UltraScale+ FPGA 為邊緣提供了相當靈活的 I/O、晶片上記憶體及高效率處理能力。具備低功耗、可擴充網路和進階安全性等特點,因此成為感測器彙總和照護點醫療系統等應用的理想首選。

經濟實惠的 I/O 擴充和基板管理控制器 (BMC),專為資料中心量身打造

由於伺服器製造商的主機板設計愈趨複雜,您需要 Spartan UltraScale+ FPGA 提供電源管理、彈性 I/O 和參考設計(例如通用主機板管理控制器),以便充分因應資料中心伺服器 I/O 市場的需求。Spartan UltraScale+ FPGA 器件系列的產品定位,便是要能配合各種伺服器主機處理器主機板和主機板管理控制卡進行擴充。

加速視訊擷取卡的廣播效率

Spartan UltraScale+ FPGA 運用先進廣播技術賦予的強大功能,帶來了與眾不同的革新功能。有了 PCIe® Gen4 和硬式記憶體控制器 LPDDR4x/5,這些擷取卡即可順利擷取和傳輸高畫質基頻視訊。即時傳輸和高效率處理能力,簡化了視訊擷取流程,也精簡了廣播工作流程。

產品表格

| SU10P | SU25P | SU35P | SU45P | SU60P | SU65P | SU100P | SU150P | SU200P | |

|---|---|---|---|---|---|---|---|---|---|

| 系統邏輯單元 (K) | 11 | 22 | 36 | 53 | 66 | 66 | 101 | 138 | 219 |

| CLB LUT (K) | 5 | 10 | 16 | 24 | 30 | 30 | 46 | 63 | 100 |

| DSP 配量 | 24 | 36 | 48 | 96 | 144 | 144 | 144 | 384 | 384 |

| RAM 總量 (Mb)* | 1.77 | 1.84 | 1.93 | 3.03 | 4.10 | 4.37 | 5.98 | 11.65 | 26.79 |

| 整合式記憶體控制器 LPDDR4X /5 | 0 | 0 | 0 | 0 | 0 | 2 | 2 | 2 | 2 |

| 收發器(16.375 Gb/s 或 12.5 Gb/s) | 0 | 0 | 0 | 4 | 4 | 4 | 4 | 8 | 8 |

| PCI Express® | 0 | 0 | 0 | 1x Gen4x4 | 1x Gen4x4 | 1x Gen4x4 | 1x Gen4x4 | 1x Gen4x8 或 2x Gen4x4 |

1x Gen4x8 或 2x Gen4x4 |

| 最大 I/O 腳位 | 304 | 304 | 304 | 262 | 262 | 478 | 478 | 572 | 572 |

* RAM 總量 = 最大分散式 RAM + 總區塊 RAM + 總 UltraRAM

請根據器件資料表或產品指南,核實上表所有資料。

開始

利用量產晶片所提供的經實證的硬體、軟體支援、工具、設計範例及文件,快速展開設計週期並快速上市。請利用以下資源,瞭解更多有關 UltraScale™ 架構的設計工具和設計方法。

AMD SCU35 評估套件

SCU35 評估套件採用 Spartan UltraScale+ SU35P FPGA,是一款經濟實惠的開發平台,可為多樣化的應用提供各式各樣的感測器與周邊設備介接選項。

查看 UltraScale 架構資料表

尋找完整 UltraScale 架構產品線的詳細規格。

適用於 Spartan UltraScale+ 的 Vivado

進一步瞭解 AMD Vivado™ Design Suite 如何以直觀易用的時序收斂與較少的迭代週期,加速 Spartan UltraScale+ 的設計開發。

聯絡 AMD 銷售人員

我們的銷售團隊隨時都可協助處理定價諮詢,為想搶先體驗預生產器件的用戶安排安全網站的存取權限,並且為您的特定需求提供支援。

其他支援與資源

聯絡銷售人員

我們的銷售團隊會根據您的特定需求,協助您做出最佳的技術決策。

尾註

- 最高每邏輯單元 I/O 是根據 AMD 內部分析,分析的資料根據為 AMD Spartan UltraScale+ SU10P FPGA 產品資料表,以及 Efinix、Intel、Lattice 和 Microchip 同級 FPGA 競品的已發佈產品資料表,競品的節點大小均在 28 nm 以下。每 I/O 成本降低是根據截至 2024 年 2 月的 AMD 清單價格,比較為了完成至少要 200 GPIO 的設計,AMD Spartan UltraScale+ SU10P 與 AMD Spartan 7 7550 各需多少成本。(SUS-011)

- 此推估是根據 2024 年 1 月的 AMD 實驗室內部分析,使用根據 AMD Artix UltraScale+ AU7P FPGA 邏輯單元計數差異的總功耗計算(靜態加動態功耗),去估算 16 nm AMD Spartan UltraScale+ SU35P FPGA 對比 28 nm AMD Artix 7 7A35T FPGA 的功耗,估算工具是 Xilinx Power Estimator (XPE) 工具 2023.1.2 版。總功耗估算和推估將在產品上市時,因設計、配置、使用情況和其他因素而有所不同。(SUS-003)

- 此預估是根據截至 2024 年 1 月的 AMD 內部分析,使用根據 AMD Artix UltraScale+ AU7P FPGA 邏輯規模計算的總功耗(靜態功耗與動態功耗),去估算 AMD Spartan UltraScale+ SU200P FPGA 對比 AMD Artix 7 7A200T FPGA 的總功耗。估算工具是 Xilinx Power Estimator (XPE) 工具 2023.1.2 版。總功耗介面結果將在產品上市時,因配置、設計、使用情況和其他因素而有所不同。(SUS-006)

- 最高每邏輯單元 I/O 是根據 AMD 內部分析,分析的資料根據為 AMD Spartan UltraScale+ SU10P FPGA 產品資料表,以及 Efinix、Intel、Lattice 和 Microchip 同級 FPGA 競品的已發佈產品資料表,競品的節點大小均在 28 nm 以下。每 I/O 成本降低是根據截至 2024 年 2 月的 AMD 清單價格,比較為了完成至少要 200 GPIO 的設計,AMD Spartan UltraScale+ SU10P 與 AMD Spartan 7 7550 各需多少成本。(SUS-011)

- 此推估是根據 2024 年 1 月的 AMD 實驗室內部分析,使用根據 AMD Artix UltraScale+ AU7P FPGA 邏輯單元計數差異的總功耗計算(靜態加動態功耗),去估算 16 nm AMD Spartan UltraScale+ SU35P FPGA 對比 28 nm AMD Artix 7 7A35T FPGA 的功耗,估算工具是 Xilinx Power Estimator (XPE) 工具 2023.1.2 版。總功耗估算和推估將在產品上市時,因設計、配置、使用情況和其他因素而有所不同。(SUS-003)

- 此預估是根據截至 2024 年 1 月的 AMD 內部分析,使用根據 AMD Artix UltraScale+ AU7P FPGA 邏輯規模計算的總功耗(靜態功耗與動態功耗),去估算 AMD Spartan UltraScale+ SU200P FPGA 對比 AMD Artix 7 7A200T FPGA 的總功耗。估算工具是 Xilinx Power Estimator (XPE) 工具 2023.1.2 版。總功耗介面結果將在產品上市時,因配置、設計、使用情況和其他因素而有所不同。(SUS-006)