Vitis 軟體平台開發環境

AMD Vitis™ 軟體平台是一套開發環境,適用於針對現場可程式化閘陣列 (Field Programmable Gate Array, FPGA) 網狀架構、Arm® 處理器和 AI 引擎的設計,可搭配 AMD Vivado™ Design Suite 運作以提供更高階的抽象化。

Vitis 軟體包括適用於使用 Arm 處理器進行 C/C++ 應用程式開發的 Vitis Embedded;AI 引擎編譯器和模擬器;用於 C/C++ 式 FPGA IP 的 Vitis HLS;用於 Simulink® 模型式設計的 Vitis 模型編輯器;以及適用於 FPGA 或 AI 引擎部署的效能最佳化程式庫,例如 DSP、視覺、求解器、超音波和 BLAS 程式庫。

設計和模擬流程

Adam Taylor 主筆:使用 Vitis 統一平台逐步進行系統設計

了解如何使用 Vitis 統一軟體平台異構系統流程建立嵌入式系統解決方案。

Vitis Embedded 軟體開發流程

(過往 FPGA 系列習慣稱之為嵌入式 SDK)

從 Vivado 將硬體匯出為平台檔案

開發應用程式碼

除錯和產生開機映像檔

為 AMD 自適應 SoC 中的 Arm® 嵌入式處理器子系統開發 C/C++ 程式碼的設計人員,通常會使用此流程。

- 硬體工程師設計出可程式化邏輯,並使用 AMD Vivado™ Design Suite 將硬體匯出為 Xilinx Support Archive (XSA) 檔案。

- 軟體工程師將這份硬體設計資訊整合進他們的目標平台,並使用 Vitis Embedded 軟體來開發應用程式碼。

開發人員可在 Vitis Embedded 軟體中執行所有系統層級驗證,並產生用來啟動應用程式的開機映像檔以。

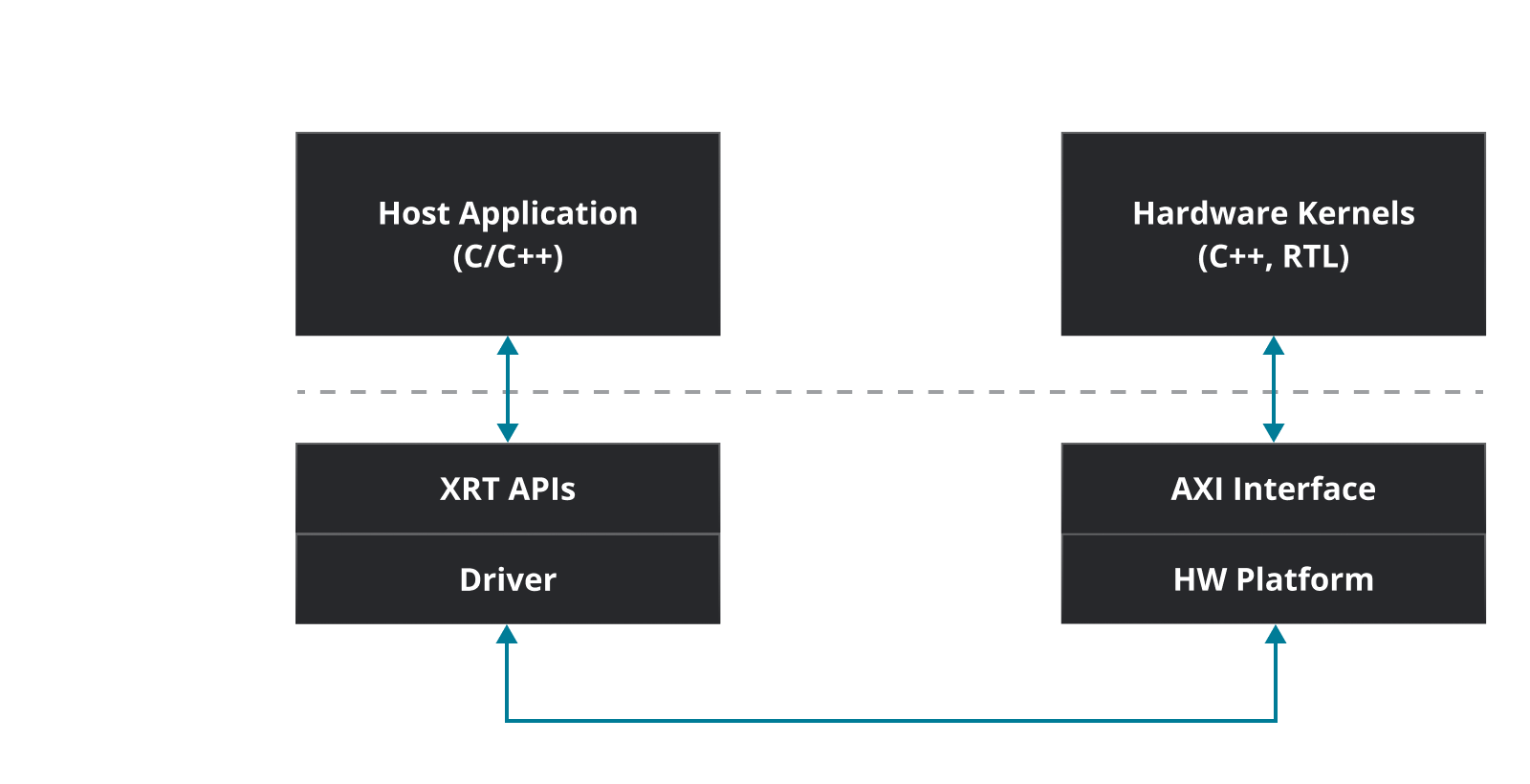

Vitis 系統設計流程

(硬體和軟體)

欲將其軟硬體設計部分整合至 AMD 自適應 SoC 中的系統設計人員,通常會使用此流程。

此流程用於異構嵌入式系統的設計開發,包括在 Arm® 嵌入式處理器上執行的軟體應用程式,以及在可程式化邏輯 (PL) 和/或 Versal™ AI 引擎陣列上執行的運算內核。

此流程包括:

- 以 C/C++ 編寫的軟體主應用程式,通常在嵌入式 Arm 處理器子系統上執行。它會用到 AMD Vitis 執行階段程式庫實作的原生 API,來與 AMD 器件內的硬體內核互動。

- 硬體內核,可使用 AMD Vitis™ HLS 工具以 C++ 產生,或使用 AMD Vivado™ Design Suite 直接以 RTL 描述。

AMD Alveo™ 資料中心加速器卡採用相同的系統設計流程,軟體程式在 x86 主機上執行,內核則在 PCIe® 介接加速器卡上的 FPGA 中執行。

Vitis 異構模擬流程

以您偏好的工具進行模擬

• 使用現有的 MATLAB®、Python™、C++ 或 HDL 測試平台

• 避免重寫測試平台或學習新的工作流程

• 加速演算法到硬體的迭代作業

統一 AI 引擎 + PL 模擬(Vitis 子系統)

• 同時模擬 AI 引擎和 PL

• 以一個一貫的方法取代零散的流程

• 及早偵測整合問題

硬體迴路 (HIL) 驗證

• 縮短系統層級的驗證時間

• 透過晶片串流實際 I/O,加快除錯作業

• 在最終硬體定案之前,先驗證端對端輸送量

工具和程式庫

2025.2 最新功能

增強 AMD Versal™ AI Engine 的設計流程

- AI 引擎 API 增強功能

- 新增並增強資料類型

- 程式設計模型更新與最佳化

- 全新強化的 DSP 程式庫函數

- 改善 AI 引擎對應工具與路由器

更簡易的 Versal AI Engine 設計驗證

- 更新 Vitis 功能模擬工作流程

- 提供採用 MATLAB® 與 Python™ 測試平台的硬體迴路測試法(搶先體驗)

- 瞭解更多關於 Versal AI Engine 的資訊

針對 AIE DSP 設計強化 Vitis 模型編輯器的功能

- 針對超取樣率 (SSR) 設計提供易用性更新

- 新增其他同時適用於 AI 引擎及 HDL 的區塊

- 瞭解更多關於 Vitis 模型編輯器的資訊

適用於嵌入式開發的 Vitis IDE 更新

- Vitis Embedded 現在可整合第三方 AI 程式碼助理

- 透過 Eclipse Theia 平台,引進對於 VS Code 編輯器的支援

- 支援 Zephyr (RTOS)

- 增強 PS Trace 的除錯功能

- 瞭解更多關於 Vitis IDE 的資訊