Vitis Embedded

Vitis Embedded

Vitis™ Embedded는 임베디드 Arm 프로세서에서 실행되는 호스트 애플리케이션 개발을 위한 독립형 임베디드 소프트웨어 개발 패키지입니다.

2025.2 릴리스 출시

AMD Vitis™ 소프트웨어 플랫폼은 FPGA 패브릭, Arm® 프로세서, AI 엔진을 대상으로 하는 설계를 위한 개발 환경으로, AMD Vivado™ Design Suite와 함께 작동하여 더 높은 수준의 추상화를 제공합니다.

Vitis 소프트웨어에는 Arm 프로세서에서 C/C++ 애플리케이션 개발을 위한 Vitis Embedded, AI 엔진 컴파일러 및 시뮬레이터, C/C++ 기반 FPGA IP용 Vitis HLS, Simulink®에서 모델 기반 설계를 위한 Vitis 모델 컴포저, FPGA 또는 AI 엔진 배포를 위한 DSP, Vision, Solver, Ultrasound, BLAS와 같은 성능 최적화 라이브러리가 포함됩니다.

Vitis 통합 이종 시스템 흐름을 사용하여 임베디드 시스템 솔루션을 생성하는 방법에 대해 알아보세요.

(기존에는 이전 FPGA 제품군에서 임베디드 SDK라고 함)

AMD 적응형 SoC에서 Arm® 임베디드 프로세서 하위 시스템용 C/C++ 코드를 개발하는 설계자가 일반적으로 이 흐름을 사용합니다.

개발자는 애플리케이션을 실행하기 위해 Vitis Embedded 소프트웨어 내에서 모든 시스템 수준 검증을 수행하고 부팅 이미지를 생성할 수 있습니다.

(하드웨어 및 소프트웨어)

AMD 적응형 SoC에 설계의 소프트웨어 및 하드웨어 부분을 통합하는 시스템 설계자가 일반적으로 이러한 흐름을 사용합니다.

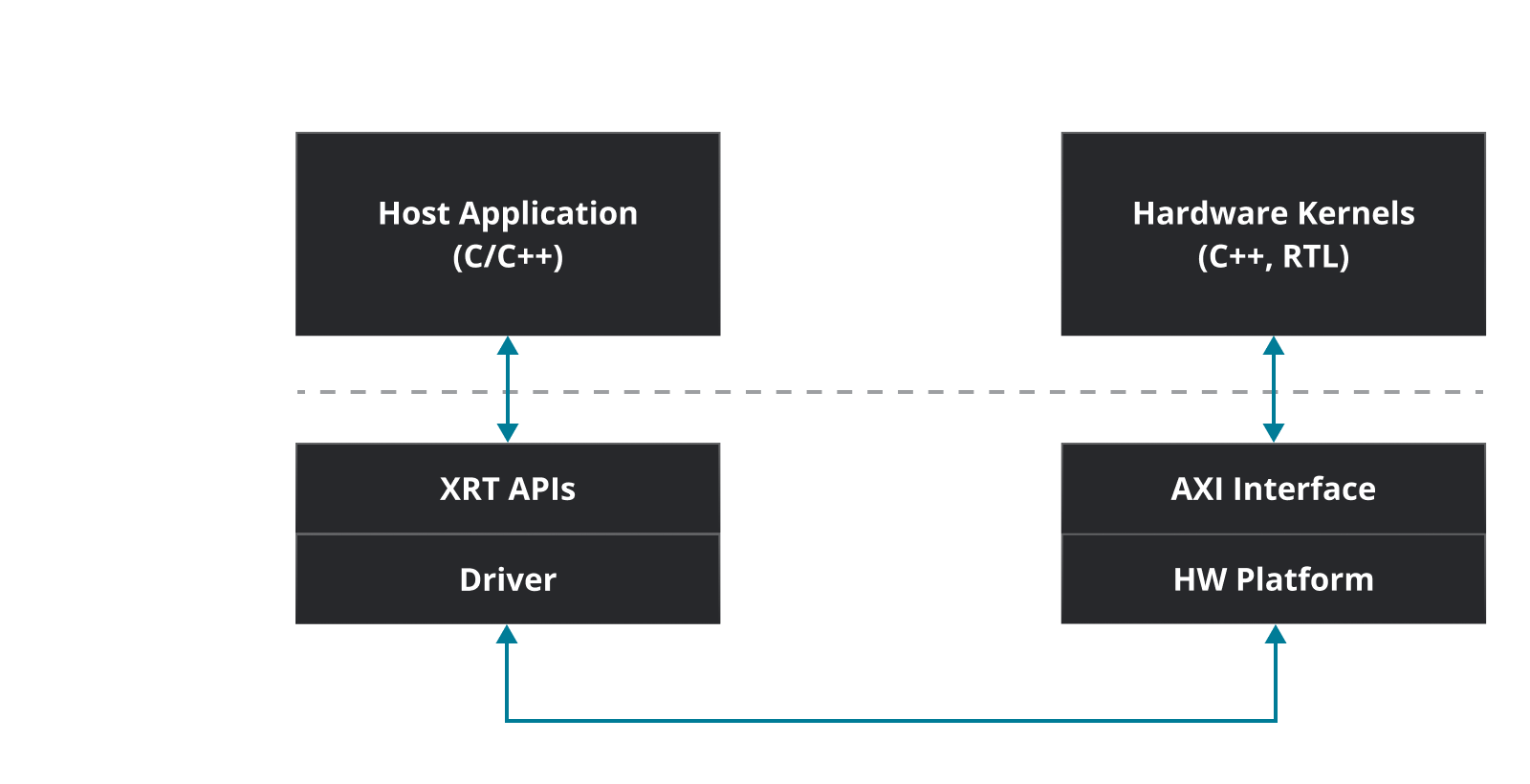

이 흐름은 Arm® 임베디드 프로세서에서 실행되는 소프트웨어 애플리케이션과 프로그래밍 가능 로직(PL) 및/또는 Versal™ AI 엔진 어레이에서 실행되는 컴퓨팅 커널로 구성된 이종 임베디드 시스템 설계를 개발하는 데 사용됩니다.

이 흐름은 다음과 같이 구성되어 있습니다.

AMD Alveo™ Data Center 가속기 카드는 동일한 시스템 설계 흐름을 사용합니다. 따라서 소프트웨어 프로그램은 x86 호스트에서 실행되고 커널은 PCIe® 연결 가속화 카드의 FPGA에서 실행됩니다.

선호하는 도구에서 시뮬레이션

• 기존 MATLAB®, Python™, C++ 또는 HDL 테스트 벤치 사용

• 테스트 벤치 재작성 또는 새로운 워크플로 학습 불필요

• 알고리즘-하드웨어 반복 가속화

통합 AI 엔진 + PL 시뮬레이션(Vitis 하위 시스템)

• AI 엔진과 PL을 함께 시뮬레이션

• 파편화된 흐름을 하나의 일관된 방법론으로 대체

• 통합 문제 조기 발견

HIL(하드웨어 인 더 루프) 검증

• 시스템 수준 검증 시간 단축

• 실제 I/O를 실리콘에 스트리밍하여 디버깅 속도 향상

• 최종 하드웨어 준비 전 엔드투엔드 처리율 검증