Vitis Embedded

Vitis Embedded

Vitis™ Embedded is a standalone embedded software development package for developing host applications running on embedded Arm processors.

2025.2 Release Now Available

The AMD Vitis™ software platform is a development environment for designs targeting FPGA fabric, Arm® processors, and AI Engines, working alongside the AMD Vivado™ Design Suite to provide a higher level of abstraction.

Vitis Software includes Vitis Embedded for C/C++ application development on Arm processors; AI Engine compilers and simulators; Vitis HLS for C/C++-based FPGA IP; Vitis Model Composer for model-based design in Simulink®; and performance-optimized libraries such as DSP, Vision, Solver, Ultrasound, and BLAS for FPGA or AI Engine deployment.

Learn to create an embedded system solution using the Vitis Unified heterogeneous system flow.

(Traditionally called Embedded SDK for previous FPGA families)

Designers who are developing C/C++ code for the Arm® embedded processor subsystem in AMD adaptive SoCs will typically use this flow.

Developers can perform all system-level verification within the Vitis Embedded software and generate boot images to launch the application.

Learn more in the Vitis Tools for Embedded Software Development section in UG1400 >

(Hardware and Software)

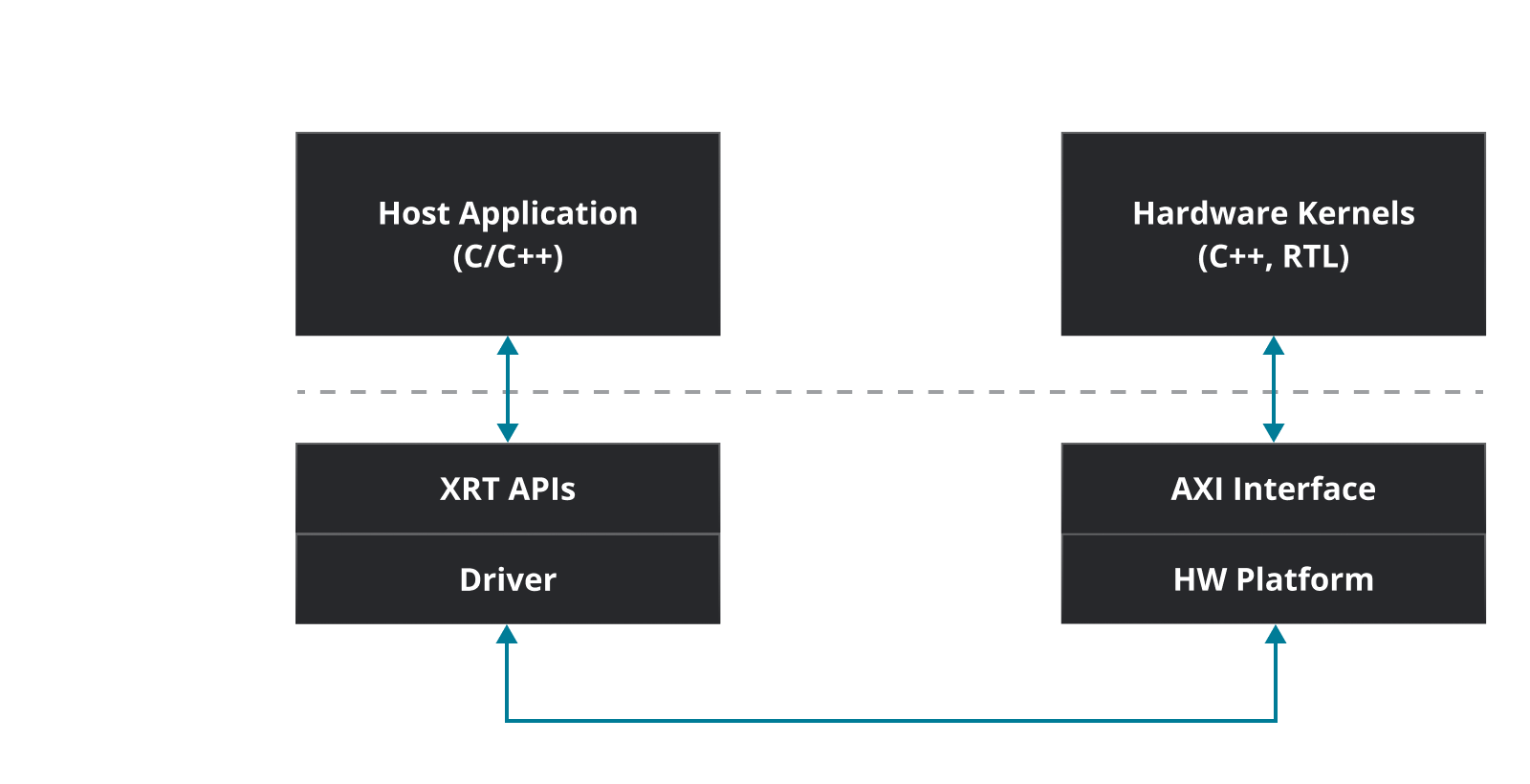

System designers who are integrating both the software and hardware portions of their design in AMD adaptive SoCs will typically use this flow.

This flow is used to develop heterogeneous embedded system designs comprising of software applications running on Arm® embedded processors and compute kernels running on programmable logic (PL) and/or Versal™ AI Engine arrays.

This flow comprises:

Learn more in the Vitis Tools for Heterogeneous System Design section in UG1393 >

AMD Alveo™ Data Center accelerator cards employ the same system design flow—the software program runs on an x86 host, and the kernels run in the FPGA on a PCIe®-attached acceleration card.

Learn more in Vitis tools for Data Center Acceleration section in UG1393 >

Simulate in Your Preferred Tools

• Use existing MATLAB®, Python™, C++, or HDL testbenches

• Avoid rewriting testbenches or learning new workflows

• Accelerate algorithm-to-hardware iteration

Unified AI Engine + PL Simulation (Vitis Subsystem)

• Simulate AI Engine and PL together

• Replace fragmented flows with one consistent methodology

• Detect integration issues early

Hardware-in-the-Loop (HIL) Validation

• Shorten system-level validation time

• Stream real I/O through silicon for faster debugging

• Verify end-to-end throughput before final hardware