Vitis Embedded

Vitis Embedded

O Vitis™ Embedded é um pacote autônomo de desenvolvimento de software incorporado para o desenvolvimento de aplicativos host executados em processadores Arm incorporados.

A versão 2025.2 já está disponível

A plataforma de software AMD Vitis™ é um ambiente de desenvolvimento para projetos direcionados a malha FPGA®, processadores Arm e mecanismos de IA, trabalhando em conjunto com o AMD Vivado™ Design Suite para oferecer um nível mais alto de abstração.

O software Vitis inclui o Vitis Embedded para desenvolvimento de aplicativos com C/C++ em processadores Arm; compiladores e simuladores de mecanismos de IA; Vitis HLS para IP FPGA com base em C/C++; Compositor de modelos do Vitis para projeto baseado em modelo no Simulink® e bibliotecas otimizadas para desempenho, como DSP, Vision, Solver, Ultrasound e BLAS para implantação de FPGA ou mecanismo de IA.

Aprenda a criar uma solução de sistema incorporada usando o fluxo de sistema heterogêneo unificado Vitis.

(Tradicionalmente chamado de SDK incorporado para famílias de FPGA anteriores)

Os projetistas que estão desenvolvendo código C/C++ para o subsistema de processador incorporado Arm® nos SoCs adaptativos da AMD normalmente usarão esse fluxo.

Os desenvolvedores podem realizar toda a verificação em nível de sistema no software Vitis Embedded e gerar imagens de inicialização para iniciar o aplicativo.

Saiba mais na seção Ferramentas do Vitis para desenvolvimento de software incorporado em UG1400 >

(Hardware e software)

Os projetistas de sistemas que estão integrando as partes de software e hardware de seu projeto nos SoCs adaptativos da AMD geralmente usam esse fluxo.

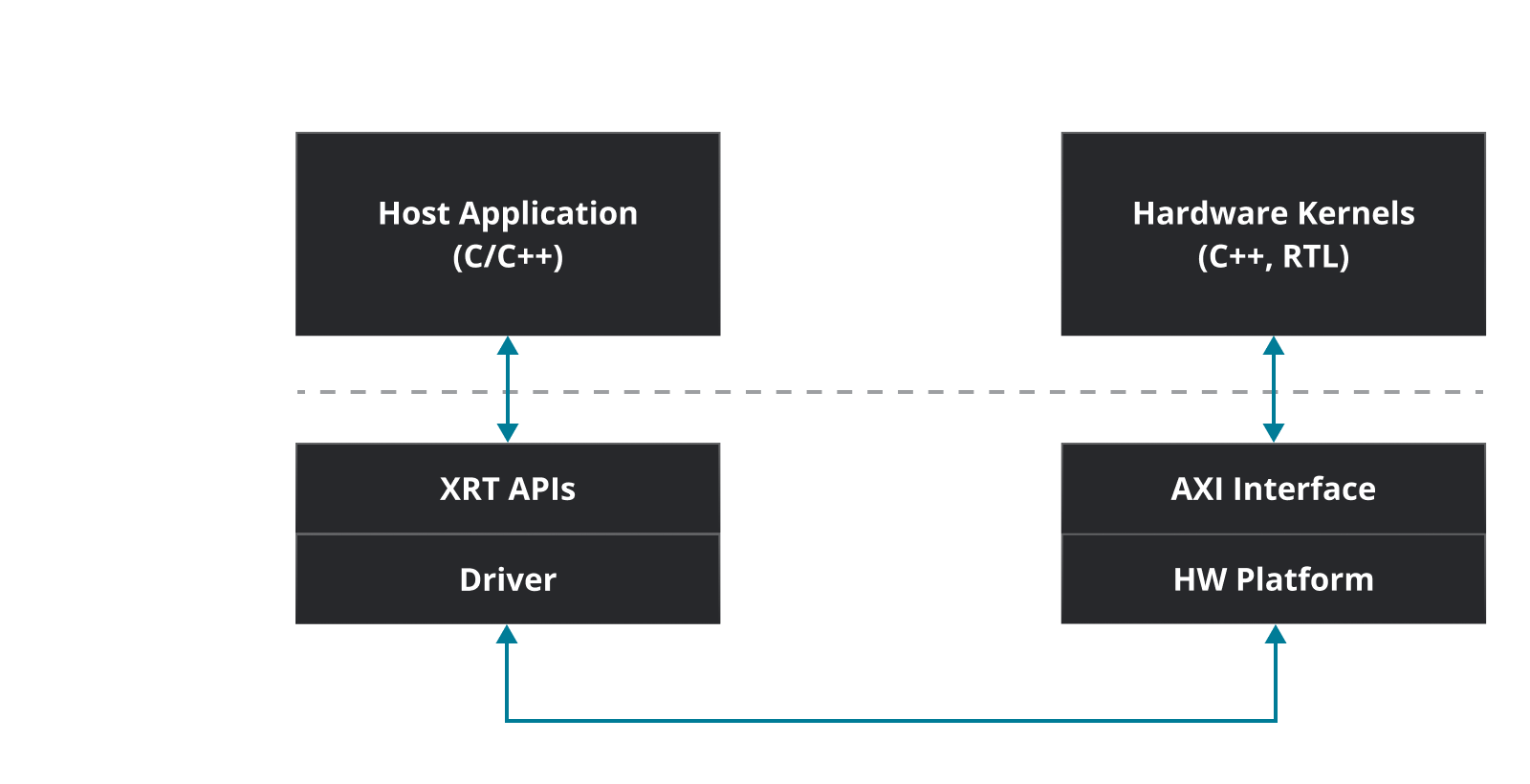

Esse fluxo é usado para desenvolver projetos de sistemas incorporados heterogêneos que incluem aplicativos de software executados em processadores incorporados Arm® e kernels de computação executados em lógica programável (PL, Programmable Logic) e/ou Matrizes do mecanismo de IA do Versal™.

Esse fluxo compreende:

Saiba mais na seção Ferramentas do Vitis para projeto de sistema heterogêneo em UG1393 >

As placas aceleradoras de data center AMD Alveo™ empregam o mesmo fluxo de projeto de sistema. O programa de software é executado em um host x86 e os kernels são executados na FPGA em uma placa de aceleração conectada ao PCIe®.

Saiba mais na seção Ferramentas do Vitis para aceleração de data center em UG1393 >

Simule em suas ferramentas preferidas

• Utilize test benches existentes em MATLAB®, Python™, C++ ou HDL

• Evite reescrever test benches ou aprender novos fluxos de trabalho

• Acelere a iteração do algoritmo para o hardware

Simulação unificada do mecanismo de IA e PL (subsistema Vitis)

• Simule o mecanismo de IA e PL em conjunto

• Substitua fluxos fragmentados por uma metodologia consistente

• Detecte problemas de integração no início

Validação de hardware-in-the-loop (HIL)

• Reduza o tempo de validação no nível do sistema

• Transmita E/S real por chip para depuração mais rápida

• Verifique a produtividade completa antes do hardware final