Visão geral

AMD Vitis™ HLS para produtividade e projetos intuitivos

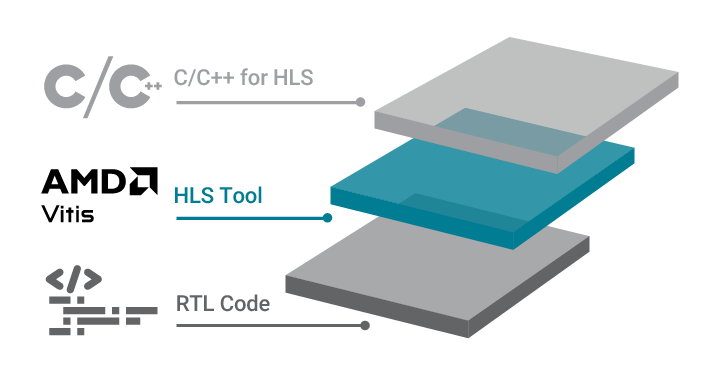

A ferramenta AMD Vitis™ HLS permite que os usuários criem facilmente algoritmos complexos de FPGA sintetizando uma função C/C++ em RTL. A ferramenta Vitis HLS está bem integrada com o Vivado™ Design Suite para síntese, local e rota e a plataforma de software unificada Vitis™ para projetos e aplicações de sistemas heterogêneos.

- Usando o fluxo do Vitis HLS, os usuários podem aplicar diretivas ao código C para criar o RTL específico para uma implementação desejada.

- É possível criar várias arquiteturas de projeto a partir do código-fonte C. Além disso, há um caminho para RTL correto por construção e de alta qualidade habilitado.

- A simulação em C pode ser usada para validar o projeto e permite iterações mais rápidas do que uma simulação baseada em RTL tradicional.

- A ferramenta Vitis HLS apresenta um rico conjunto de ferramentas de análise e depuração que facilitam a otimização do projeto.

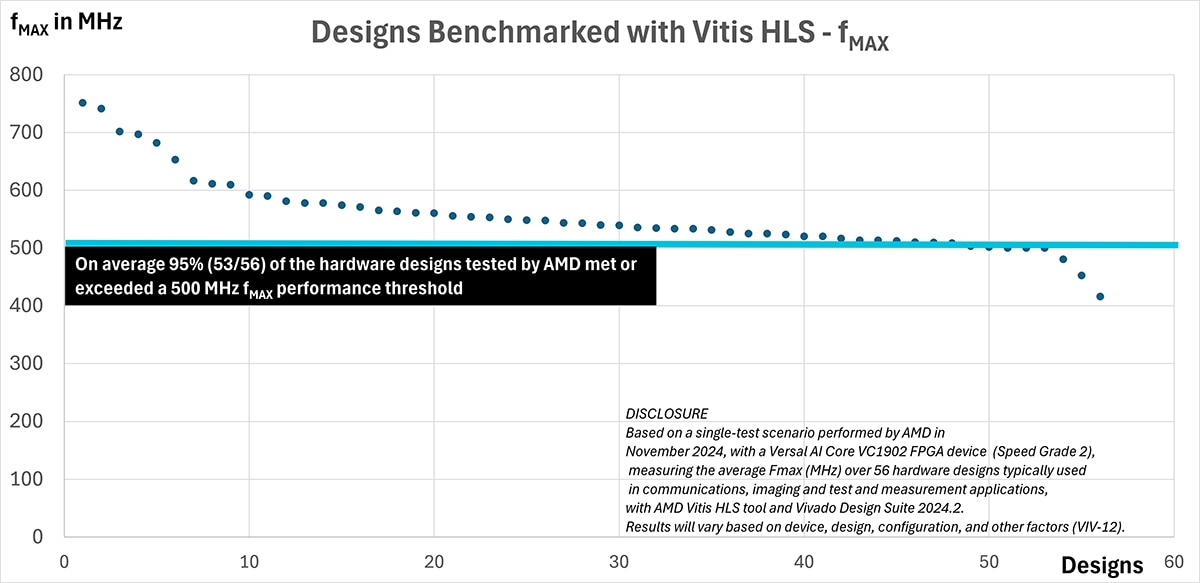

AMD Vitis™ HLS Performance Pragma

O AMD Vitis HLS tem um novo pragma com desempenho de nível superior que ajuda você a alcançar uma alta QoR. Consulte o módulo técnico para obter mais informações sobre como usar esse novo recurso.

Metodologia de projeto

Modelo de programação do Vitis HLS

O código C do Vitis HLS é desenvolvido para aproveitar os benefícios e as características oferecidos pela arquitetura de FPGAs e SoCs adaptativos da AMD.

A ferramenta Vitis HLS suporta construções de programação paralela para modelar uma implementação desejada. Essas construções incluem:

- Tarefas de HLS que permitem simultaneidade no nível do processo

- Vetores de HLS que permitem o paralelismo no nível de dados

- Fluxos de HLS que permitem a comunicação entre tarefas simultâneas

- Os pragmas de síntese podem ser usados para controlar os resultados. Esses pragmas incluem pipeline, unroll, particionamento de matriz e protocolos de interface.

- Para obter detalhes adicionais, consulte a seção "Guia de programadores de HLS" no Guia do usuário de síntese de alto nível do Vitis.

Geração de código C++ MATLAB para HLS

As funções desenvolvidas no MATLAB® podem ser sintetizadas em código C++ compatível com AMD Vitis™ HLS por meio dos recursos de geração de código do MathWorks HDL Coder, disponível no MATLAB R2025a.

Esse código C++ sintetizável e gerado pode servir como entrada para o Vitis™ HLS. Este fluxo de trabalho pode agilizar o processo de conversão de um projeto de algoritmo de alto nível (normalmente feito no MATLAB) para uma implementação de RTL de baixo nível.

Use o MATLAB e o HDL Coder para projetar e criar test benchs e, em seguida, use o recurso de geração de código do HDL Coder para inserir no Vitis HLS para simulação e síntese em FPGAs e SoCs adaptativos da AMD.

Para saber mais, visite a página do MathWorks HDL Coder.

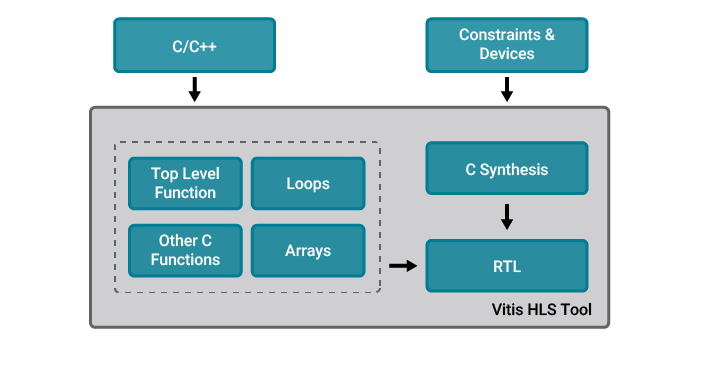

Conversão de C para RTL

A ferramenta Vitis HLS sintetiza diferentes partes do código C:

- Os argumentos de função de nível superior do código C/C++ são sintetizados nas portas de E/S de RTL e são automaticamente implementados com um protocolo de hardware de síntese de interface.

- Outras funções C são sintetizadas em blocos de RTL, mantendo a hierarquia do projeto.

- Os loops de função C são mantidos como rolled ou em pipeline para melhorar o desempenho.

- As matrizes no código C podem ser direcionadas a qualquer recurso de memória, como BRAM, LUTRAM e URAM.

- Métricas de desempenho, como latência, intervalo de iniciação, latência de iteração de loop e utilização de recursos, podem ser revisadas com relatórios de síntese.

- As diretivas de pragmas e otimização da ferramenta Vitis HLS permitem configurar os resultados da síntese para o código C/C++.

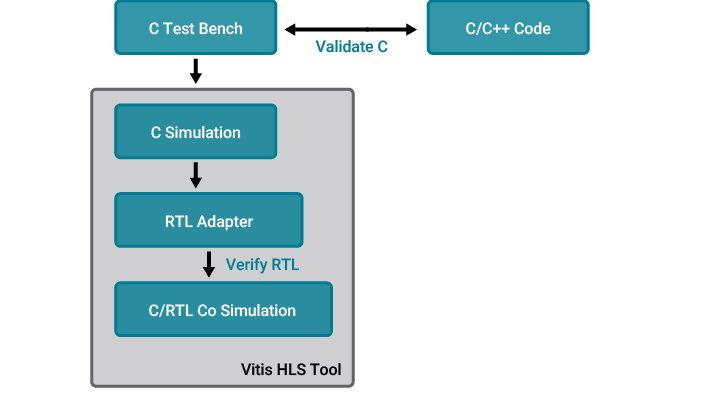

Simulação e verificação

A ferramenta Vitis HLS contém fluxos de simulação incorporados para possibilitar tempos de verificação mais rápidos:

- A simulação em C valida a funcionalidade do código C. Essa etapa é rápida e usa um testbench em C.

- A cossimulação de C/RTL reutiliza um testbench em C para realizar a validação no RTL gerado, verificando se o RTL é funcionalmente idêntico ao código-fonte C.

- O fluxo tem recursos integrados de análise, depuração e visualização de forma de onda, bem como suporte popular ao simulador.

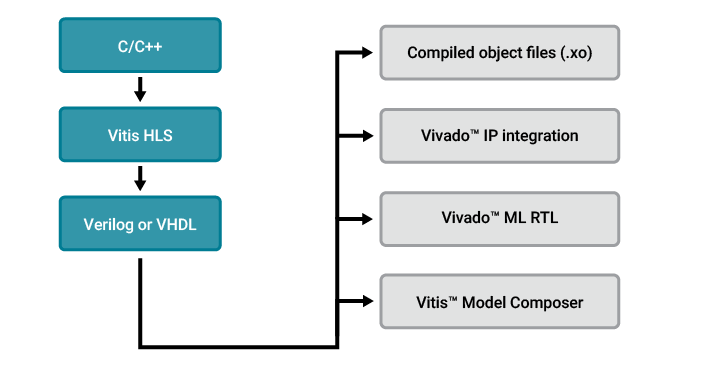

Exportação de IP

A saída da ferramenta Vitis HLS é uma implementação RTL que pode ser colocada em pacote para um arquivo de objeto compilado (.xo) ou exportada para um IP RTL:

- Os arquivos de objeto compilados (.xo) são usados para criar funções de aceleração de hardware para uso no fluxo de desenvolvimento do aplicativo Vitis.

- O IP RTL pode ser usado de três maneiras:

- Adicionado usando a ferramenta de integração de IP Vivado™

- Importado como um bloco RTL no Vivado IDE

- Usado como um único conjunto de blocos no Vitis Model Composer para aplicações de DSP

O que há de novo

- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

Destaques da versão 2025.2

- Melhorias no Pragma de desempenho

- O pragma de desempenho agora será otimizado com base na contagem de viagens calculada pelo CSIM

- As otimizações do pragma de desempenho podem ser convertidas em diretivas em um arquivo de configuração

- Controle condicional de pragmas, incluindo o pragma de desempenho

- Novo suporte de IP

- Taxa fracionária SSR para FIR e FFT, para FFT, a SSR em SPFP32 agora suporta até SSR=64.

- Suporte ECC para buffers de fluxo de dados implementados com RAM de bloco ou UltraRAM

- Recursos fáceis de usar

- Suporte à reinicialização automática no CSIM e no CoSim

- Cache multiporta para M-AXI

- Novas APIs para transmissões AXI com sinais de bandas laterais

Destaques da versão 2025.1

- Gere o código C++ compatível com Vitis HLS a partir de projetos MATLAB (.m) usando o HDL Coder e MATLAB R2025a

- Novos recursos de facilidade de uso do Vitis HLS

- Modelagem de entradas de fios e entradas AXI Lite que mudam durante a execução (E/S direta)

- Pragma de desempenho para o projeto HLS de nível superior (acesso antecipado aberto)

- Suporte para complex multiplier Versal por meio da biblioteca intrínseca dedicada

- Melhorias na GUI do Vitis HLS

- Suporte inicial C++17 via Clang 16

Destaques da versão 2024.2

O Vitis HLS versão 2024.2 inclui uma série de recursos que facilitam o desenvolvimento e a depuração de um projeto HLS; entre eles:

- Modelagem de entradas escalares/de fios que mudam durante a execução (E/S direta)

- Suporte para tipos de ponto flutuação de precisão arbitrária

- Mapeamento do código HLS para blocos de DSP

- Sequência determinada pelo usuário da execução do código

- Depurador HLS que mostra tipos de dados de maneira amigável (usando a tecnologia de prettyprint do depurador GNU)

Destaques da versão 2024.1

- Um novo pragma de estêncil simplifica o código HLS em C++ para imagens e vídeos

Novos assistentes de função de biblioteca aproveitam o repositório GitHub das bibliotecas do AMD Vitis

- Crie IPs "Solver" e "Vision" (compatível com OpenCV) para a ferramenta de projetos do AMD Vivado

- Execute os exemplos de biblioteca disponíveis

Agora, o pragma para interface de memória (ap_memory) pode agrupar portas para o AMD Vivado IP Integrator

A nova comparação de componentes HLS exibe métricas lado a lado para 2 ou mais componentes

Suporte para código RTL do provedor de usuário para substituir uma função do C++ (fluxo de black-box)

Agora, o analisador de código pode desagregar membros de estrutura em C++ para ajustar a análise de desempenho

Novo controle de usuário para codificação de FSM global de HLS e seleção de estado seguro

Acesso a limpadores de clang durante a simulação em C para realizar verificações de endereço e de inicialização

Destaques da versão 2023.2

- Novo Vitis™ Unified IDE para componentes HLS

- Novos requisitos de licença do Vitis HLS

- Novo recurso do analisador de código para obter estimativas de desempenho antes de executar a síntese em C

- Aprimoramentos na interface AXI:

- Aprimoramentos no suporte de canal lateral de transmissão AXI de HLS

- Suporte para cache principal AXI configurável pelo usuário

- Outros aprimoramentos:

- Novo relatório de complexidade de código para possibilitar a identificação de problemas de tamanho de projeto durante a síntese em C

- Aprimoramentos no tempo de compilação: Aprimoramento médio no tempo de compilação de 20% na versão 2023.2 em comparação com a versão 2023.11

Destaques da versão 2023.1

- Aprimoramentos de desempenho2: Aprimoramentos médios de latência de 5,2% na versão 2023.1 em comparação com a versão 2022.2

- Maneira fácil de baixar, visualizar e instanciar funções de bibliotecas de L1 na ferramenta Vitis HLS. Assista ao vídeo

- Suporte aprimorado para transações de AXI e relatórios de bursts na ferramenta Vitis HLS

Destaques da versão 2022.2

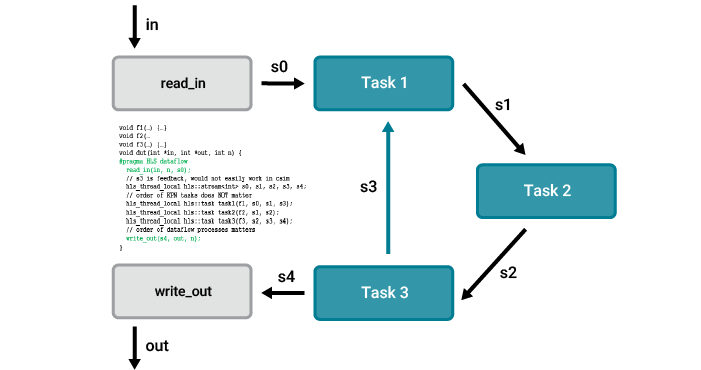

- Nova maneira de gravar código "paralelo no nível da tarefa" para aplicações de processamento de dados

- O usuário pode definir explicitamente o paralelismo no nível da tarefa usando a nova função hls::task

- Mais fácil de modelar para projetos puramente de streaming (por exemplo, comutação de pacotes)

- Aprimoramentos de temporização e desempenho

- A ferramenta infere automaticamente unroll, pipeline, partições de matriz e pragmas em linha para um melhor desempenho

- Aprimoramentos de análise e depuração

- Novo recurso para sintetizar instruções de impressão a partir da fonte C no código RTL gerado

- Quando o RTL é simulado, isso permite rastrear a execução de um bloco de código e o valor de uma variável

- Facilidade de uso

- A interface hls::stream agora é compatível para IPs FFT e FIR

Destaques da versão 2022.1

- Novo visualizador de rastreamento de linha de tempo

- Mostra o perfil de tempo de execução de todas as funções sobreviventes em seu projeto, ou seja, aquelas que são convertidas em módulos

- Especialmente útil para ver o comportamento das regiões de fluxo de dados após a cossimulação. Nativo para Vitis™ HLS — não é mais necessário iniciar o visualizador de forma de onda xsim

- Novo pragma de desempenho

- A HLS mostra qual é o seu destino de produtividade usando #pragma hls performance

- A HLS tentará atingir a meta, se possível, usando menos recursos

- A HLS indicará as transformações realizadas e, se não conseguir atingir o alvo, indicará o fator limitante

- Suporte à partição de matriz para o tipo fluxo de blocos

- Aprimoramento de hls::stream em que cada elemento é uma matriz

- Pode ser usado para dividir o processamento de matriz grande em partes menores e com pipeline

Destaques da versão 2021.2

- Inferência de burst controlada pelo usuário

- O usuário pode adotar a nova otimização manual de burst

- Uma nova classe "hls::burst_maxi" foi adicionada para oferecer suporte ao controle manual do comportamento de burst. Novas APIs de HLS são fornecidas para uso junto com a nova classe.

- Os usuários precisam entender o protocolo AXI AMBA e a modelagem em nível de transação de hardware no projeto de HLS

- Aprimoramentos de temporização e de Qualidade dos resultados

- Melhora a precisão da estimativa de temporização de HLS. Quando a HLS relata o encerramento de temporização, a síntese de RTL no Vivado™ também deve esperar cumprir a temporização

- Aprimoramentos de EoU

- Adicione o relatório de adaptadores de interface no relatório de síntese em C

- Os usuários precisam saber o impacto dos recursos que os adaptadores de interface têm em seu projeto

- Os adaptadores de interface têm propriedades variáveis que afetam a QoR do projeto

- Adicione uma nova seção ao relatório de síntese para mostrar a lista de pragmas e advertências sobre pragmas

- Aprimoramentos de análise e geração de relatórios

- Nova capacidade de aumentar e diminuir o zoom baseada em arrastar do mouse

- Novo recurso de visão geral que mostra o gráfico completo e permite que o usuário aumente o zoom em partes do gráfico geral

- Todas as funções e loops são mostrados junto com seus dados de simulação

- Um novo Timeline Trace Viewer agora está disponível após a simulação. Este visualizador mostra o perfil de tempo de execução do seu projeto e permite que o usuário permaneça na GUI do Vitis HLS

Destaques da versão 2021.1

- Novo "Navegador de fluxo" na GUI para acesso rápido às fases de fluxo e relatórios. As visualizações contextuais "síntese, análise, depuração" são mescladas em um contexto padrão geral

- Nova seção de relatório de síntese para as diretivas BIND_OP e BIND_STORAGE

- Um novo relatório de texto pós-síntese reflete as informações fornecidas no relatório de síntese da GUI

- Os widgets de execução exportação IP e de implementação do Vivado™ foram reprojetados com opções para passar arquivos de configurações e restrições para o Vivado

- Novo visualizador de grafo de chamada de função para visualizar funções e loops que podem ser destacados com uma área de destaque opcional para detectar pontos de acesso de utilização de II, latência ou DSP/BRAM

- Calibração de temporização do Versal™ e novos controles para operações nativas de ponto de flutuação de bloco de DSP (a opção de precisão para config_op)

- A opção alternativa de pipeline descarregável foi melhorada (pipeline de execução livre, também conhecida como "frp")

- No Vitis, a remodelação das interfaces m_axi deve ser feita por meio dos tipos de hls::vector

- Novas opções de personalização para armazenamento de dados s_axilite e m_axi que podem ser "auto, "uram", "bram" ou "lutram", permitindo que você ajuste a utilização da RAM no seu projeto

- No Vitis, apresentamos um novo modo de execução contínuo (também conhecido como "never-ending") para o kernel

- A opção de relógio secundário axi_lite foi reinstalada

Histórias de sucesso

Sucesso do cliente do Vitis HLS: Intuitive Surgical

A Intuitive Surgical, líder mundial em robôs cirúrgicos, usa FPGAs para implementar alguns de seus requisitos de geração de imagens de alto desempenho.

Uma função para a qual eles precisavam criar protótipos era uma função de distorção de imagem para resolução de 4K a 60 frames por segundo (FPS). O projeto tinha requisitos rigorosos de latência. Devido a restrições de tempo, eles decidiram implementar essa função usando o Vitis HLS. O código foi desenvolvido do zero com o suporte técnico da equipe AMD Vitis HLS. Todo o processo de projeto levou cerca de duas semanas e as metas de desempenho foram atingidas.

"A distorção de imagem é uma operação complexa em FPGAs e pode levar vários meses quando implementada usando RTL. A abordagem baseada no Vitis HLS nos permitiu implementar rapidamente o projeto. Embora o projeto não tenha sido totalmente otimizado, a velocidade com que alcançamos a prototipagem foi fenomenal, demonstrando os benefícios de HLS. Esse método facilitou iterações rápidas e, com o suporte da equipe de HLS da AMD e ajustes nos pragmas aplicados, conseguimos colocar o projeto em funcionamento com sucesso no SoC e FPGA em um prazo sem precedentes. Temos utilizado e pretendemos continuar utilizando a HLS para nossas funções de imagem."

- Azhar Sufi, Gerente Sênior, Firmware — Imagens, Intuitive Surgical

Alcance uma latência ultrabaixa em um DSP de áudio para FPGA com Vitis HLS

A equipe de pesquisa Emeraude da INSA Lyon está trabalhando no desenvolvimento de novas técnicas de processamento de sinal para sistemas de áudio incorporados. A equipe implementou um programa de DSP de áudio de latência ultrabaixa usando a ferramenta AMD Vitis HLS. Clique aqui para saber mais sobre como a ferramenta Vitis HLS ajudou a equipe a alcançar latência ultrabaixa em uma compilação de áudio de DSP para FPGA.

Estudo de caso do cliente

Exploração de espaço do projeto mais rápida com o Vitis HLS

"A principal vantagem da ferramenta AMD Vitis™ HLS, do meu ponto de vista, é o recurso de exploração de espaço do projeto. Você pode gerar diferentes arquiteturas e implementações em um tempo razoável usando diretivas de otimização (pipeline, unroll etc.). Isso não pode ser feito se você codificar manualmente com VHDL/Verilog. Um bom recurso do Vitis HLS é a possibilidade de fazer uma cossimulação e uma validação do código HDL para garantir que o código HDL esteja funcionalmente correto." Dr. Frank Kesel — Professor da Universidade de Pforzheim, Alemanha

Estudo de caso do cliente

Recursos

Notas de rodapé

- Com base em testes realizados em 10 de agosto de 2023, em 1.000 projetos de biblioteca de códigos do Vitis L2/L3, com o Vitis HLS versão 2023.2 em comparação com o Vitis HLS 2023.1. Configuração do sistema durante os testes: CPU Intel Xeon E5-2690 v4 a 2,6 GHz, 256 GB de RAM e RedHat Enterprise Linux 8.6. Há variação no desempenho real. Os fabricantes de sistemas podem variar as configurações, gerando resultados diferentes. -VGL-04

- Os testes de valor de referência foram realizados em todos os 1.208 projetos de código C da biblioteca do Vitis L1 em 12 de fevereiro de 2023. Todos os projetos foram executados usando um sistema com 2P CPUs Intel Xeon E5-2690 com CentOS Linux, SMT habilitado e Turbo Boost desabilitado. Não se espera que a configuração de hardware tenha efeito nos resultados dos testes de software. Os resultados podem variar com base nas configurações e configurações de software e firmware — VGL-03

- Com base em testes realizados em 10 de agosto de 2023, em 1.000 projetos de biblioteca de códigos do Vitis L2/L3, com o Vitis HLS versão 2023.2 em comparação com o Vitis HLS 2023.1. Configuração do sistema durante os testes: CPU Intel Xeon E5-2690 v4 a 2,6 GHz, 256 GB de RAM e RedHat Enterprise Linux 8.6. Há variação no desempenho real. Os fabricantes de sistemas podem variar as configurações, gerando resultados diferentes. -VGL-04

- Os testes de valor de referência foram realizados em todos os 1.208 projetos de código C da biblioteca do Vitis L1 em 12 de fevereiro de 2023. Todos os projetos foram executados usando um sistema com 2P CPUs Intel Xeon E5-2690 com CentOS Linux, SMT habilitado e Turbo Boost desabilitado. Não se espera que a configuração de hardware tenha efeito nos resultados dos testes de software. Os resultados podem variar com base nas configurações e configurações de software e firmware — VGL-03