Présentation

AMD Vitis™ HLS pour une conception intuitive et une productivité accrue

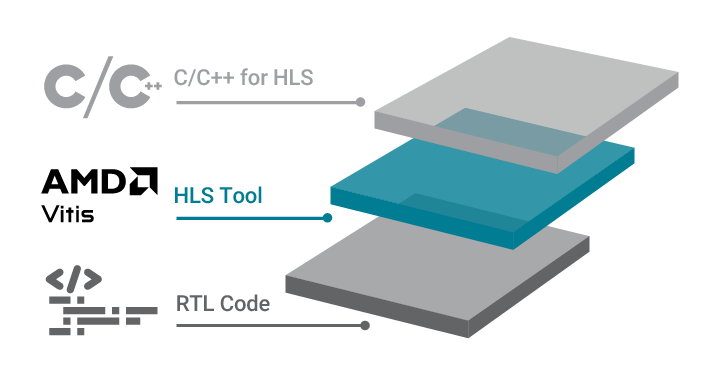

L'outil AMD Vitis™ HLS permet aux utilisateurs de créer facilement des algorithmes FPGA complexes en synthétisant une fonction C/C++ dans le RTL. L'outil Vitis HLS est étroitement intégré à Vivado™ Design Suite pour la synthèse, le placement et le routage, ainsi qu'à la plateforme software unifiée Vitis™ pour les conceptions et applications de systèmes hétérogènes.

- À l'aide du flux Vitis HLS, les utilisateurs peuvent appliquer des directives au code C pour créer le RTL spécifique à la mise en œuvre souhaitée.

- Plusieurs architectures de conception peuvent être créées à partir du code source C et un chemin pour un RTL correct par construction de haute qualité est activé.

- La simulation C peut être utilisée pour valider la conception et permettre des itérations plus rapides qu'une simulation RTL traditionnelle.

- L'outil Vitis HLS est doté d'un ensemble complet d'outils d'analyse et de débogage qui facilitent l'optimisation de la conception.

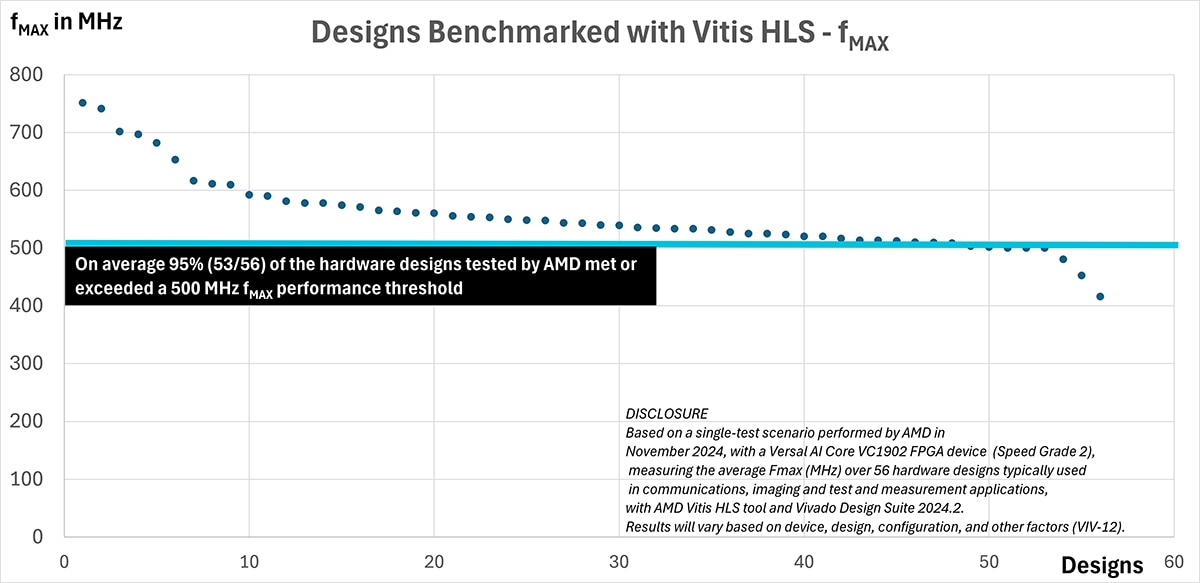

Pragma de performances AMD Vitis™ HLS

AMD Vitis HLS dispose d'un nouveau pragma de performances de haut niveau qui vous aide à atteindre une qualité des résultats élevée. Consultez le module technique pour plus d'informations sur l'utilisation de cette nouvelle fonctionnalité.

Méthodologie de conception

Modèle de programmation Vitis HLS

Le code Vitis HLS C est conçu pour tirer parti des avantages et des caractéristiques offerts par l'architecture des SoC et FPGA adaptatifs AMD.

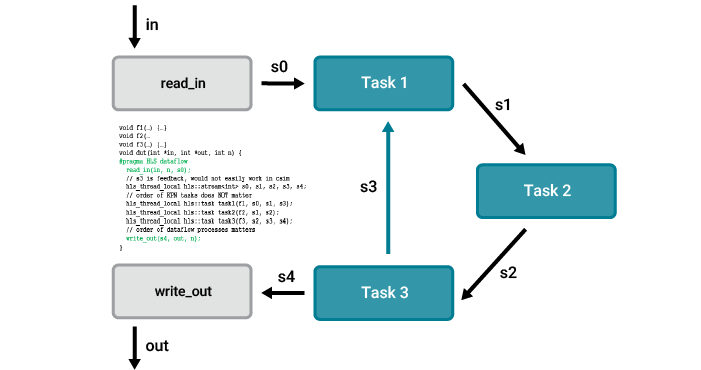

L'outil Vitis HLS prend en charge les constructions de programmation parallèle afin de modéliser une mise en œuvre souhaitée. Ces constructions comprennent :

- Des tâches HLS permettant la simultanéité au niveau du processus

- Des vecteurs HLS permettant le parallélisme au niveau des données

- Des flux HLS permettant la communication entre les tâches simultanées

- Les pragmas de synthèse peuvent être utilisés pour contrôler les résultats. Ces pragmas comprennent le pipeline, le déblocage, le partitionnement de matrices et les protocoles d'interface.

- Pour plus de détails, voir la section « Guide des programmeurs HLS » dans le Guide d'utilisation de la synthèse de haut niveau Vitis.

Génération de code de MATLAB vers HLS C++

Les fonctions développées dans MATLAB® peuvent être synthétisées en code C++ compatible avec AMD Vitis™ HLS via les capacités de génération de code de MathWorks HDL Coder disponibles dans MATLAB R2025a.

Ce code C++ synthétisable généré peut être utilisé comme entrée pour Vitis™ HLS. Ce flux de travail permet d'accélérer le processus de traduction d'une conception d'algorithme de haut niveau (généralement réalisée dans MATLAB) vers une implémentation RTL de bas niveau.

Utilisez MATLAB et HDL Coder pour concevoir et créer des bancs d'essai, puis utilisez la fonction de génération de code de HDL Coder pour la saisie dans Vitis HLS à des fins de simulation et de synthèse sur les SoC adaptatifs et les FPGA d'AMD.

Pour en savoir plus, consultez la page HDL Coder de MathWorks.

Conversion C vers RTL

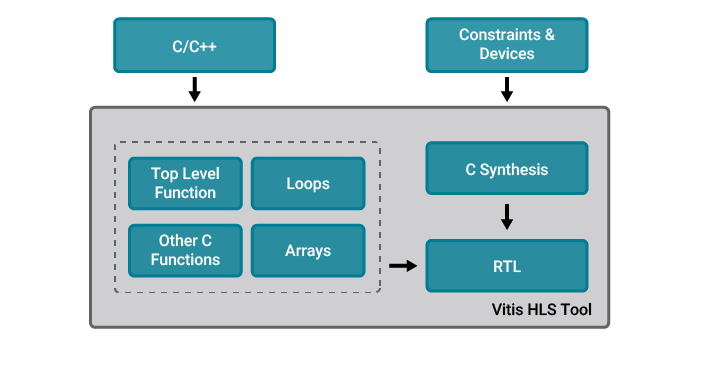

L'outil Vitis HLS synthétise différemment les différentes parties du code C :

- Les arguments de fonction de premier niveau du code C/C++ sont synthétisés dans les ports d'E/S RTL et sont automatiquement mis en œuvre avec un protocole hardware de synthèse d'interface.

- Les autres fonctions C sont synthétisées en blocs RTL, ce qui permet de maintenir la hiérarchie de conception.

- Les boucles de fonction C sont maintenues roulées ou mises en pipeline pour améliorer les performances.

- Les baies du code C peuvent être ciblées vers n'importe quelle ressource mémoire, telle que BRAM, LUTRAM et URAM.

- Les mesures de performances, telles que la latence, l'intervalle de lancement, la latence d'itération de boucle et l'utilisation des ressources, peuvent être examinées à l'aide de rapports de synthèse.

- Les directives de pragmas et d'optimisation de l'outil Vitis HLS permettent de configurer les résultats de synthèse pour le code C/C++.

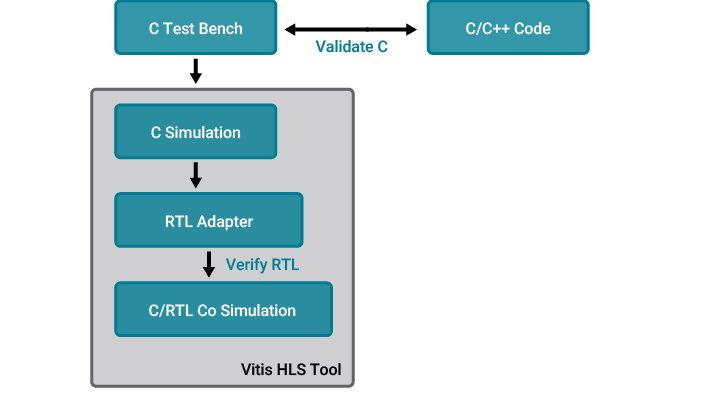

Simulation et vérification

L'outil Vitis HLS intègre des flux de simulation pour accélérer les temps de vérification :

- La simulation C valide la fonctionnalité du code C. Cette étape est rapide et utilise un banc d'essai C.

- La co-simulation C/RTL réutilise le banc d'essai C pour effectuer la validation sur le RTL généré, en vérifiant que le RTL est fonctionnellement identique au code source C.

- Le flux dispose de fonctionnalités intégrées d'analyse, de débogage et d'affichage de forme d'onde, ainsi que d'une prise en charge de simulateur populaire.

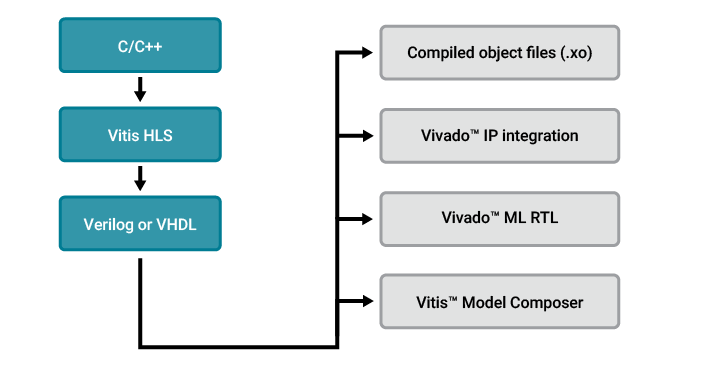

Exportation IP

La sortie de l'outil Vitis HLS est une implémentation RTL qui peut être intégrée dans un fichier objet compilé (.xo) ou exportée vers une IP RTL :

- Les fichiers objet compilés (.xo) sont utilisés pour créer des fonctions d'accélération hardware à utiliser dans le flux de développement de l'application Vitis.

- L'IP RTL peut être utilisée de trois façons :

- Ajoutée à l'aide de l'outil d'intégration Vivado™ IP

- Importée en tant que bloc RTL dans l'IDE Vivado

- Utilisée comme bloc unique dans Vitis Model Composer pour les applications DSP

Nouveautés

- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

Points forts de la version 2025.2

- Améliorations du pragma de performances

- Le pragma de performances s'optimisera désormais en fonction du nombre de déclenchements calculé par CSIM

- Les optimisations du pragma de performances peuvent être converties en directives dans un fichier de configuration

- Contrôle conditionnel des pragmas, y compris du pragma de performances

- Nouvelle prise en charge IP

- SSR à fréquence fractionnelle pour FIR et FFT - Pour FFT, le SSR dans SPFP32 prend désormais en charge jusqu'à SSR=64.

- Prise en charge ECC pour les tampons de flux de données implémentés avec RAM en mode bloc ou UltraRAM

- Fonctionnalités faciles à utiliser

- Prise en charge du redémarrage automatique dans CSIM et CoSim

- Cache multiport pour M-AXI

- Nouvelles API pour les flux AXI avec signaux de bandes latérales

Points forts de la version 2025.1

- Générez du code C++ compatible avec Vitis HLS à partir de conceptions MATLAB (.m) en utilisant HDL Coder et MATLAB R2025a

- Nouvelles fonctionnalités de Vitis HLS faciles à utiliser

- Modélisation des entrées filaires et des entrées AXI Lite qui changent pendant l'exécution ( E/S directes)

- Pragma de performances pour la conception HLS de premier niveau (accès anticipé ouvert)

- Prise en charge du Complex Multiplier de Versal via la bibliothèque intrinsèque dédiée

- Améliorations apportées à la GUI de Vitis HLS

- Prise en charge initiale de C++17 via Clang 16

Points forts de la version 2024.2

Vitis HLS version 2024.2 inclut une multitude de fonctionnalités qui facilitent le développement et le débogage d'une conception HLS, notamment :

- Modélisation des entrées scalaires/filaires qui changent pendant l'exécution (E/S directes)

- Prise en charge des types de précision arbitraire à virgule flottante

- Mappage du code HLS vers les blocs DSP

- Séquence d'exécution du code déterminée par l'utilisateur

- Débogueur HLS affichant les types de données de manière conviviale (à l'aide de la technologie d'impression élégante du débogueur GNU)

Points forts de la version 2024.1

- Un nouveau pragma stencil simplifie le code HLS C++ pour les filtres d'images et de vidéos.

Les nouveaux assistants de fonctions de bibliothèque s'intègrent aux référentiels GitHub des bibliothèques AMD Vitis

- Créez des IP « Solver » et « Vision » (compatibles OpenCV) pour l'outil de conception AMD Vivado

- Exécutez des exemples de bibliothèque disponibles

Pragma pour Memory Interface (ap_memory) peut désormais regrouper des ports pour AMD Vivado IP Integrator

La nouvelle comparaison des composants HLS affiche des mesures côte à côte pour 2 composantsou plus

Prise en charge du code RTL de l'utilisateur pour remplacer une fonction C++ (flux de boîte noire)

Code Analyzer peut désormais dissocier les membres C++ struct pour ajuster l'analyse des performances

Nouveau contrôle utilisateur pour le codage HLS global FSM et la sélection de l'état de sécurité

Accès aux sanitizers Clang pendant la simulation C pour effectuer des vérifications d'adresse et d'initialisation

Points forts de la version 2023.2

- Nouvel IDE unifié Vitis™ pour composants HLS

- Nouvelles exigences de licence Vitis HLS

- Nouvelle fonctionnalité d'analyseur de code permettant d'obtenir des estimations de performances avant d'exécuter la synthèse C.

- Améliorations apportées à l'interface AXI :

- Améliorations apportées à la prise en charge des canaux latéraux HLS AXI Stream

- Prise en charge de la mise en cache principale AXI configurable par l'utilisateur

- Autres améliorations :

- Nouveau rapport sur la complexité du code permettant d'identifier les problèmes de taille de conception pendant la synthèse C

- Améliorations du temps de compilation : Amélioration moyenne du temps de compilation de 20 % en 2023.2 par rapport à 2023.11

Points forts de la version 2023.1

- Amélioration des performances2 : Amélioration moyenne de la latence de 5,2 % dans la version 2023.1 par rapport à 2022.2

- Méthode simple pour télécharger, visualiser et instancier les fonctions des bibliothèques L1 dans l'outil Vitis HLS. Regarder la vidéo

- Prise en charge améliorée pour les transactions AXI et les rapports de rafales dans l'outil Vitis HLS

Points forts de la version 2022.2

- Nouvelle façon d'écrire du code « parallèle au niveau des tâches » pour les applications de traitement de données

- L'utilisateur peut définir explicitement le parallélisme au niveau des tâches à l'aide de la nouvelle fonction hls::task

- Plus facile à modéliser pour les conceptions purement en streaming (par ex., commutation de paquets)

- Améliorations des performances et de la durée

- L'outil infère automatiquement les données de restauration, de pipeline, de partitions de baie et de pragmas en ligne pour de meilleures performances

- Améliorations de l'analyse et du débogage

- Nouvelle fonctionnalité permettant de synthétiser les déclarations d'impression de la source C dans le code RTL généré

- Lorsque RTL est simulé, cela permet de tracer l'exécution d'un bloc de code et la valeur d'une variable

- Facilité d'utilisation

- L'interface hls::stream est désormais prise en charge pour les IP FFT et FIR

Points forts de la version 2022.1

- Nouvelle visionneuse de suivi de chronologie

- Affiche le profil d'exécution de toutes les fonctions restantes de votre conception, c'est-à-dire celles qui sont converties en modules

- Particulièrement utile pour voir le comportement des régions de flux de données après la co-simulation. Natif de Vitis™ HLS : plus besoin de lancer la visionneuse de formes d'onde xsim

- Nouveau pragma de performance

- HLS de votre objectif de débit en utilisant les performances #pragma hls

- HLS tentera d'atteindre l'objectif, si possible, en utilisant le moins de ressources possible

- HLS indique les transformations effectuées, et s'il ne peut pas atteindre la cible, il indique le facteur de limitation

- Prise en charge de la partition de matrice pour le type de flux de blocs

- Amélioration hls::steram dans laquelle chaque élément est une matrice

- Peut être utilisé pour diviser le traitement de grandes matrices en petites parties en pipeline

Points forts de la version 2021.2

- Inférence Burst contrôlée par l'utilisateur

- L'utilisateur peut adopter une nouvelle optimisation manuelle des rafales

- Une nouvelle classe « hls::burst_maxi » a été ajoutée pour prendre en charge le contrôle manuel du comportement de rafale. De nouvelles API HLS sont fournies pour être utilisées avec la nouvelle classe.

- Les utilisateurs doivent comprendre le protocole AXI AMBA et la modélisation au niveau des transactions hardware dans la conception HLS

- Améliorations de la synchronisation et de la QoR

- Améliorez la précision de l'estimation de la durée HLS. Lorsque HLS signale une fermeture, la synthèse de Vivado™ RTL doit également respecter le calendrier

- Améliorations d'EoU

- Ajouter le rapport des adaptateurs d'interface dans le rapport de synthèse C

- Les utilisateurs doivent connaître l'impact des ressources sur leur conception des adaptateurs d'interface

- Les adaptateurs d'interface ont des propriétés variables qui ont un impact sur la QoR de conception

- Ajouter une nouvelle section dans le rapport de synthèse pour afficher la liste des pragmas et des avertissements sur les pragmas

- Améliorations de l'analyse et des rapports

- Nouvelle fonctionnalité de zoom avant et arrière basée sur le glissement de la souris

- Nouvelle fonction Aperçu qui affiche le graphique complet et permet à l'utilisateur d'effectuer un zoom avant sur des parties du graphique d'ensemble

- Toutes les fonctions et boucles sont affichées avec leurs données de simulation

- Une nouvelle visionneuse de suivi de chronologie est désormais disponible après la simulation. Cette visionneuse affiche le profil d'exécution de votre conception et permet à l'utilisateur de rester dans la GUI (interface graphique utilisateur) de Vitis HLS

Points forts de la version 2021.1

- Nouveau « Flow Navigator » dans la GUI (interface graphique utilisateur) pour un accès rapide aux phases de flux et aux rapports. Les vues contextuelles « synthèse, analyse, débogage » sont fusionnées dans un contexte général par défaut

- Nouvelle section de rapport de synthèse pour les directives BIND_OP et BIND_STORAGE

- Un nouveau rapport de texte post-synthèse reflète les informations fournies dans le rapport de synthèse GUI

- Les widgets d'exécution de l'exportation IP et de l'implémentation de Vivado™ ont été repensés avec des options permettant de transmettre les fichiers de paramètres et de contraintes à Vivado.

- Nouvelle visionneuse de graphiques d'appels de fonction permettant de visualiser les fonctions et les boucles qui peuvent être mises en évidence avec une carte thermique en option pour détecter les points sensibles d'utilisation, de latence ou DSP/BRAM

- Étalonnage de la temporisation Versal™ et nouveaux contrôles pour les opérations à virgule flottante natives du bloc DSP (option de précision pour config_op)

- L'option alternative de pipeline purgeable a été améliorée (pipeline libre, appelé « frp »)

- Dans Vitis, le remodelage des interfaces m_axi doit être effectué via les types hls::vector

- De nouvelles options de personnalisation pour le stockage de données s_axilite et m_axi, qui peuvent être « auto », « uram », « bram » ou « lutram », vous permettant d'ajuster l'utilisation de la RAM dans votre conception

- Dans Vitis, nous avons introduit un nouveau mode d'exécution continu (appelé « sans fin ») pour le noyau

- L'option d'horloge secondaire axi_lite a été rétablie

Témoignages

Témoignage client sur Vitis HLS : Intuitive Surgical

Intuitive Surgical, le leader mondial des robots chirurgicaux, utilise des FPGA pour répondre à certaines de ses exigences en matière d'imagerie hautes performances.

L'une des fonctions qu'il fallait prototyper concernait la déformation d'une image pour une résolution 4K à 60 images par seconde (FPS). La conception avait des exigences strictes en matière de temps de latence. En raison de contraintes de temps, Intuitive Surgical a décidé de mettre en œuvre cette fonction à l'aide de Vitis HLS. Le code a été développé à partir de zéro avec l'assistance technique de l'équipe AMD Vitis HLS. L'ensemble du processus de conception a pris environ deux semaines et les objectifs de performance ont été atteints.

« La déformation d'image est une opération complexe dans les FPGA et peut nécessiter plusieurs mois lorsqu'elle est mise en œuvre à l'aide de RTL. L'approche basée sur Vitis HLS nous a permis de mettre rapidement en œuvre cette conception. Bien que cette dernière n'ait pas été entièrement optimisée, la vitesse à laquelle nous avons réalisé le prototypage a été phénoménale, démontrant ainsi les avantages de la HLS. Cette méthode a accéléré les itérations et, grâce au soutien de l'équipe HLS d'AMD et aux ajustements apportés aux pragmas appliqués, nous avons réussi à exécuter la conception sur le SoC FPGA dans un temps record. Nous utilisons et avons l'intention de continuer à utiliser HLS pour nos fonctions d'imagerie. »

Azhar Sufi, responsable senior, micrologiciel – Imagerie, Intuitive Surgical

Obtenez une latence ultra-faible dans un DSP audio vers FPGA avec Vitis HLS

L'équipe de recherche Emeraude de l'INSA Lyon travaille au développement de nouvelles techniques de traitement des signaux pour les systèmes audio intégrés. L'équipe a mis en œuvre un programme DSP audio à très faible latence à l'aide de l'outil AMD Vitis HLS. Cliquez ici pour en savoir plus sur la façon dont l'outil Vitis HLS a aidé l'équipe à atteindre une latence ultra-faible dans une compilation DSP-vers-FPGA audio.

Étude de cas client

Exploration plus rapide de l'espace de conception avec Vitis HLS

« Le principal avantage de l'outil AMD Vitis™ HLS, de mon point de vue, est la fonction d'exploration de l'espace de conception. Vous pouvez générer différentes architectures et mises en œuvre dans un délai raisonnable en utilisant des directives d'optimisation (pipeline, restauration, etc.). Cela ne peut pas être fait si vous codez manuellement avec VHDL/Verilog. Une fonctionnalité intéressante de Vitis HLS est la possibilité de faire une co-simulation et une validation du code HDL afin d'être sûr que le code HDL est bien fonctionnel. » Dr Frank Kesel - Professeur à l'université de Pforzheim, Allemagne

Étude de cas client

Ressources

Notes de bas de page

- Selon des tests réalisés le 10 août 2023, sur 1 000 conceptions de bibliothèque de code Vitis L2/L3, avec Vitis HLS version 2023.2 par rapport à Vitis HLS 2023.1. Configuration du système pendant le test : CPU Intel Xeon E5-2690 V4 @ 2,6 GHz, 256 Go de RAM, RedHat Enterprise Linux 8.6. Les performances réelles varient. Les résultats peuvent varier en fonction des configurations créées par les fabricants de systèmes. -VGL-04

- Les tests de référence ont été effectués sur les 1 208 conceptions de la bibliothèque Vitis L1 C-code à compter du 12 février 2023. Toutes les conceptions ont été exécutées à l'aide d'un système équipé de CPU Intel Xeon E5-2690 2P avec CentOS Linux, SMT activé, Turbo Boost désactivé. La configuration hardware ne devrait pas affecter les résultats du test software. Les résultats peuvent varier en fonction des paramètres et configurations du software et du micrologiciel - VGL-03

- Selon des tests réalisés le 10 août 2023, sur 1 000 conceptions de bibliothèque de code Vitis L2/L3, avec Vitis HLS version 2023.2 par rapport à Vitis HLS 2023.1. Configuration du système pendant le test : CPU Intel Xeon E5-2690 V4 @ 2,6 GHz, 256 Go de RAM, RedHat Enterprise Linux 8.6. Les performances réelles varient. Les résultats peuvent varier en fonction des configurations créées par les fabricants de systèmes. -VGL-04

- Les tests de référence ont été effectués sur les 1 208 conceptions de la bibliothèque Vitis L1 C-code à compter du 12 février 2023. Toutes les conceptions ont été exécutées à l'aide d'un système équipé de CPU Intel Xeon E5-2690 2P avec CentOS Linux, SMT activé, Turbo Boost désactivé. La configuration hardware ne devrait pas affecter les résultats du test software. Les résultats peuvent varier en fonction des paramètres et configurations du software et du micrologiciel - VGL-03