Übersicht

AMD Vitis™ HLS für intuitive Konzeptentwicklung und Produktivität

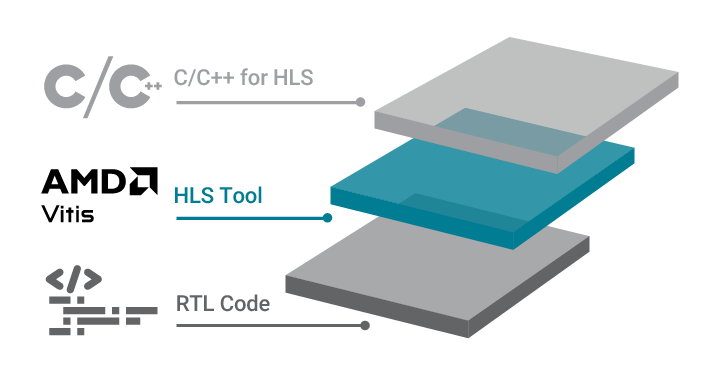

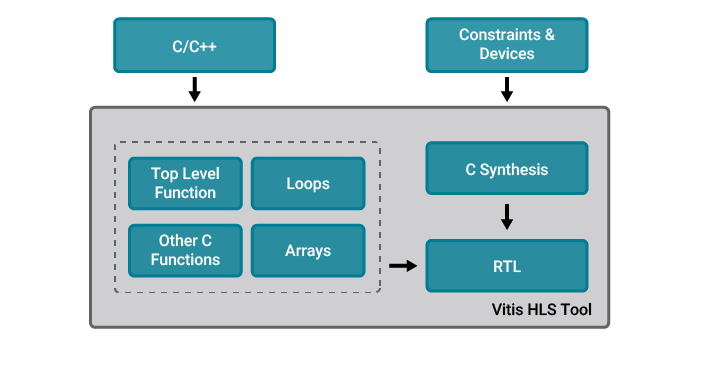

Mit dem AMD Vitis™ HLS Tool können Sie durch Synthetisieren einer C/C++-Funktion in der RTL komplexe FPGA-Algorithmen generieren. Das Vitis HLS Tool bietet eine enge Integration mit der Vivado™ Design Suite, sodass Synthese- und Place-and-Route-Funktionen genutzt werden können, sowie mit der Vitis™ Unified Software Platform, auf der heterogene Systemkonzepte und Anwendungen entwickelt werden.

- Mithilfe des Vitis HLS Flows können Benutzer Anweisungen auf den C-Code anwenden, um die RTL speziell für eine gewünschte Implementierung zu erstellen.

- Aus dem C-Quellcode können mehrere Designarchitekturen erstellt werden. Außerdem wird Benutzern ermöglicht, qualitativ hochwertige Correct-by-Construction-RTL zu erstellen.

- Durch C-Simulation können Sie das Konzept validieren und schnellere Iterationen vornehmen als mit einer herkömmlichen RTL-basierten Simulation.

- Das Vitis HLS Tool bietet eine Vielzahl von Analyse- und Debugging-Tools zur Konzeptoptimierung.

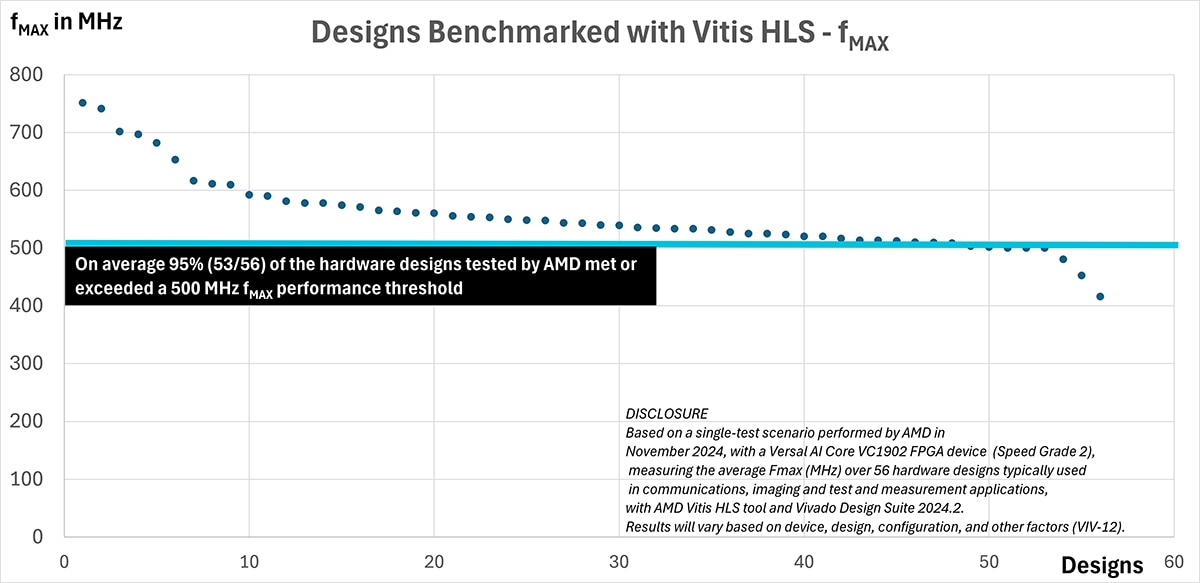

AMD Vitis™ HLS Performance-Pragma

AMD Vitis HLS verfügt über ein neues Pragma mit Performance der Spitzenklasse, mit dem eine hohe QoR erreicht werden kann. Weitere Informationen zur Verwendung dieser neuen Funktion finden Sie im technischen Modul.

Design Methodology

Vitis HLS-Programmierungsmodell

Der Vitis HLS C-Code ist darauf ausgerichtet, die Vorteile und Eigenschaften der Architektur der adaptiven SoCs und FPGAs von AMD zu nutzen.

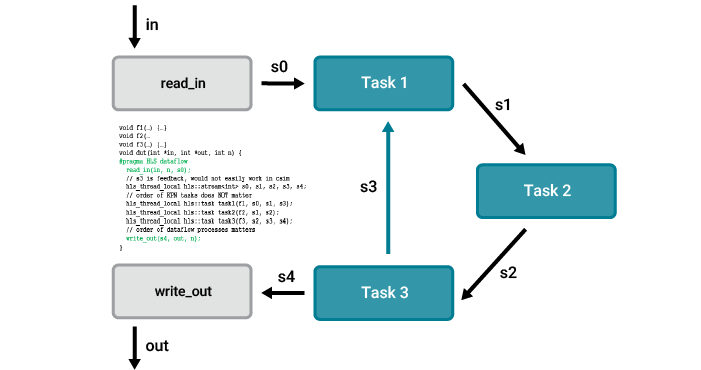

Das Vitis HLS Tool unterstützt parallele Programmierungskonstrukte für die Modellierung einer gewünschten Implementierung. Zu diesen Konstrukten gehören:

- HLS-Aufgaben, die die gleichzeitige Verarbeitung auf Prozessebene zulassen

- HLS-Vektoren, die Parallelität auf Datenebene zulassen

- HLS-Streams, die die Kommunikation zwischen gleichzeitigen Aufgaben ermöglichen

- Synthese-Pragmen können zur Kontrolle der Ergebnisse verwendet werden. Zu diesen Pragmen gehören Pipeline-, Unroll-, Array-Partitionierungs- und Schnittstellenprotokolle.

- Weitere Einzelheiten finden Sie im Abschnitt HLS-Programmierhandbuch im Benutzerhandbuch für die Vitis High-Level-Synthese.

MATLAB-zu-HLS C++-Codegenerierung

In MATLAB® entwickelte Funktionen können über die Codegenerierungsfunktionen von MathWorks HDL Coder, der in MATLAB R2025a verfügbar ist, in AMD Vitis™ HLS-freundlichem C++-Code synthetisiert werden.

Dieser generierte, synthetisierbare C++-Code kann als Eingang für Vitis™ HLS dienen. Dieser Workflow kann den Übersetzungsprozess von einem Algorithmuskonzept auf hoher Ebene (normalerweise in MATLAB) zu einer RTL-Implementierung auf niedriger Ebene beschleunigen.

Verwenden Sie den MATLAB- und HDL-Coder, um Testbenches zu entwerfen und zu erstellen, und verwenden Sie dann die Codegenerierungsfunktion in HDL Coder, um in Vitis HLS zur Simulation und Synthese auf adaptiven AMD SoCs und FPGAs einzugeben.

Weitere Informationen finden Sie auf der Seite HDL Coder von MathWorks.

C-zu-RTL-Konvertierung

Das Vitis HLS Tool synthetisiert verschiedene Teile des C-Codes unterschiedlich:

- Funktionsargumente der obersten Ebene des C/C++-Codes werden in RTL-I/O-Ports synthetisiert und automatisch mit einem Hardwareprotokoll für die Schnittstellensynthese implementiert.

- Andere C-Funktionen werden zu RTL-Blöcken synthetisiert, wodurch die Konzepthierarchie beibehalten wird.

- C-Funktionsschleifen bleiben aufgerollt oder werden per Pipelining verarbeitet, um die Performance zu verbessern.

- Arrays im C-Code können auf jede Speicherressource wie BRAM, LUTRAM und URAM ausgerichtet werden.

- Performance-Metriken wie Latenz, Initiierungsintervall, Schleifeniterationslatenz und Ressourcenauslastung können mit Syntheseberichten überprüft werden.

- Über die Pragmen und Optimierungsanweisungen des Vitis HLS Tools können Sie die Syntheseergebnisse für den C/C++-Code konfigurieren.

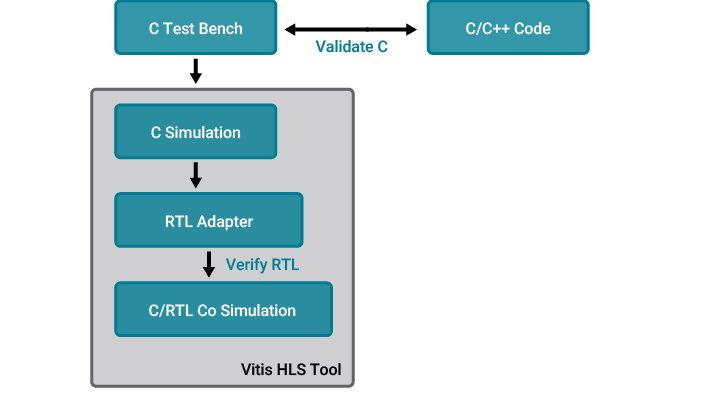

Simulation und Verifizierung

Das Vitis HLS Tool verfügt über integrierte Simulations-Flows, die kürzere Verifizierungszeiten ermöglichen:

- Die C-Simulation validiert die Funktionalität des C-Codes. Dies ist ein schneller Schritt, bei dem eine C-Testbench zum Einsatz kommt.

- Die C/RTL-Co-Simulation führt ebenfalls mit der C-Testbench eine Validierung der generierten RTL durch, wodurch überprüft wird, ob die RTL funktional mit dem C-Quellcode identisch ist.

- In den Flow sind Anzeigefunktionen für Analyse, Debugging und Wellenform sowie die beliebte Simulatorunterstützung integriert.

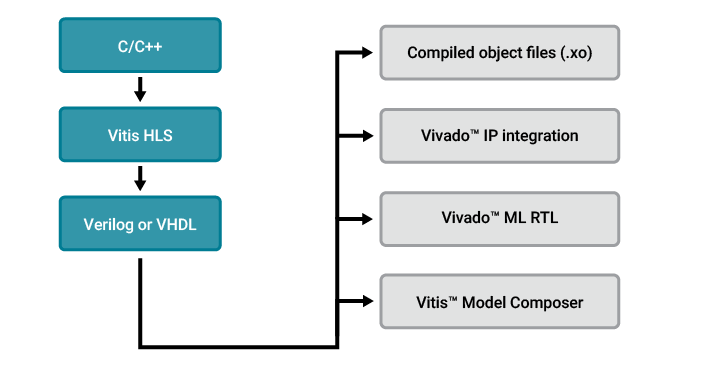

IP-Export

Das Vitis HLS Tool gibt eine RTL-Implementierung aus, die entweder in eine kompilierte Objektdatei (.xo) verpackt oder in eine RTL-IP exportiert werden kann:

- Mit kompilierten Objektdateien (.xo) werden Hardwarebeschleunigungsfunktionen für die Verwendung im Entwicklungs-Flow der Vitis Anwendung erstellt.

- Die RTL-IP kann auf drei Arten verwendet werden:

- Durch Hinzufügen mit dem Vivado™ IP Integrator-Tool

- Durch Import als RTL-Block in die Vivado IDE

- Als einzelnes Blockset in Vitis Model Composer für DSP-Anwendungen

Neues

- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

Highlights des Release 2025.2

- Erweiterungen von Performance-Pragma

- Performance-Pragma wird nun basierend auf dem von CSIM berechneten Trip-Count optimiert

- Performance-Pragma-Optimierungen können in Anweisungen in einer Konfigurationsdatei umgewandelt werden

- Bedingte Pragmen-Steuerung, einschließlich Performance-Pragma

- Unterstützung neuer IP

- Fractional-Rate-SSR für FIR und FFT – für FFT bietet SSR in SPFP32 jetzt Unterstützung bis zu SSR=64.

- ECC-Unterstützung für Datenflusspuffer, implementiert mit Block RAM oder UltraRAM

- Benutzerfreundliche Funktionen

- Unterstützung für automatischen Neustart in CSIM und CoSim

- Multi-Port-Cache für M-AXI

- Neue APIs für AXI-Streams mit Seitenbandsignalen

Highlights des Release 2025.1

- Generieren von Vitis HLS-freundlichem C++-Code aus MATLAB (.m)-Konzepten mit HDL Coder und MATLAB R2025a

- Neue benutzerfreundliche Funktionen von Vitis HLS

- Modellierung von kabelgebundenen Eingängen und AXI Lite-Eingängen, die sich während der Ausführung ändern (Direct I/O)

- Performance-Pragma für das HLS-Konzept auf oberster Ebene (offener Early Access)

- Unterstützung des Versal Complex Multipliers über die dedizierte intrinsische Bibliothek

- Verbesserungen der Vitis HLS-GUI

- Anfängliche C++17-Unterstützung über Clang 16

Highlights des Release 2024.2

Vitis HLS Version 2024.2 enthält eine Vielzahl von Funktionen, die es Benutzern erleichtern, ein HLS-Konzept zu entwickeln und zu debuggen. Dazu gehören unter anderem:

- Modellierung skalarer/kabelgebundener Eingänge, die sich während der Ausführung ändern (Direct I/O)

- Unterstützung für Gleitkomma-Datentypen für Langzahlarithmetik

- Zuordnung von HLS-Code zu DSP-Blöcken

- Benutzerdefinierte Sequenz der Codeausführung

- HLS-Debugger, der Datentypen benutzerfreundlich anzeigt (mit der PrettyPrint-Technologie des GNU-Debuggers)

Highlights des Release 2024.1

- Ein neues Schablonen-Pragma vereinfacht den HLS C++-Code für Bild- und Videofilter

Neue Assistenten für Bibliotheksfunktionen greifen auf das GitHub-Repository der AMD Vitis Bibliotheken zu

- „Solver“- und „Vision“-IPs (OpenCV-kompatibel) für AMD Vivado Designtoolerstellen

- Verfügbare Bibliotheksbeispiele ausführen

Das Pragma für Memory Interface (ap_memory) kann jetzt Ports für AMD Vivado IP Integratorbündeln

Der neue HLS-Komponentenvergleich zeigt Metriken für mindestens 2 Komponenten nebeneinander an

Unterstützung für vom Benutzer bereitgestellten RTL-Code zum Ersetzen einer C++-Funktion (Black-Box-Flow)

Code Analyzer kann nun Elemente von C++-Konstrukten aufteilen, um die Performance-Analyse zu optimieren

Neue Benutzersteuerung für die globale HLS-FSM-Codierung und Auswahl des Status „Safe“

Zugriff auf Clang Sanitizers während C-Simulation zur Durchführung von Adress- und Initialisierungsprüfungen

Highlights des Release 2023.2

- Neue Vitis™ Unified IDE für HLS-Komponenten

- Neue Vitis HLS-Lizenzanforderungen

- Neue Code-Analyzer-Funktion zum Abrufen von Performance-Schätzungen vor der Ausführung der C-Synthese

- Verbesserungen der AXI-Schnittstelle:

- Verbesserungen der Side-Channel-Unterstützung für HLS AXI-Streams

- Unterstützung für vom Benutzer konfigurierbares AXI-Master-Caching

- Weitere Verbesserungen:

- Neuer Bericht zur Codekomplexität, um Probleme mit der Konzeptgröße während der C-Synthese zu identifizieren

- Verbesserungen der Kompilierungszeit: Durchschnittliche Verbesserung der Kompilierungszeit um 20 % in Release 2023.2 gegenüber 2023.11

Highlights des Release 2023.1

- Performance-Verbesserungen2: Durchschnittliche Latenzverbesserungen um 5,2 % in Release 2023.1 gegenüber 2022.2

- Einfache Möglichkeit zum Download, Anzeigen und Instanziieren von L1-Bibliotheksfunktionen im Vitis HLS-Tool. Video ansehen

- Verbesserte Unterstützung für AXI-Transaktionen und Burst-Berichte im Vitis HLS-Tool

Highlights des Release 2022.2

- Neue Möglichkeit, Code mit Aufgabenparallelität für Datenverarbeitungsanwendungen zu schreiben

- Mit der neuen hls::task-Funktion können Benutzer Aufgabenparallelität explizit definieren

- Einfachere Modellierung für reine Streaming-Konzepte (z. B. Paketvermittlung)

- Verbesserungen bei Performance und Timing

- Das Tool leitet zwecks Performance-Verbesserung Unroll-, Pipeline-, Array-Partitions- und Inline-Pragmen automatisch ab

- Verbesserungen bei Analyse und Debugging

- Neue Funktion zur Synthese von Druckanweisungen aus dem C-Quellcode im generierten RTL-Code

- Bei der RTL-Simulation können Sie die Ausführung eines Codeblocks und den Wert einer Variablen nachverfolgen

- Benutzerfreundlichkeit

- hls::stream-Schnittstelle wird jetzt für FFT- und FIR-IPs unterstützt

Highlights des Release 2022.1

- Neuer Zeitachsentrace-Viewer

- Zeigt das Laufzeitprofil aller noch vorhandenen Funktionen in Ihrem Design an, d. h. der Funktionen, die in Module konvertiert werden

- Besonders nützlich, um das Verhalten von Datenflussbereichen nach der Co-Simulation anzuzeigen. Nativ für Vitis™ HLS – der xsim-Wellenform-Viewer muss nicht mehr gestartet werden

- Neues Performance-Pragma

- Ermittelt Ihr Durchsatzziel per HLS mit „#pragma hls performance“

- Es wird versucht, per HLS das Ziel wenn möglich mit möglichst wenigen Ressourcen zu erreichen

- Nach dem HLS-Vorgang werden durchgeführte Transformationen angezeigt. Bei Nichterreichen des Ziels wird ein limitierender Faktor genannt

- Unterstützung von Array-Partitionen für den Typ „Stream of Blocks“

- Verbesserung von hls::stream, wobei jedes Element ein Array ist

- Kann verwendet werden, um die Verarbeitung großer Arrays in kleinere, in Pipelines unterteilte Stücke aufzuteilen

Highlights des Release 2021.2

- Vom Benutzer gesteuerte Burst-Inferenz

- Benutzer können die neu eingeführte manuelle Burst-Optimierung übernehmen

- Die neue Klasse „hls::burst_maxi“ wird hinzugefügt, um das manuelle Steuern des Burst-Verhaltens zu unterstützen. Neue HLS-APIs werden zur Verwendung mit der neuen Klasse bereitgestellt.

- Benutzer müssen mit dem AXI-AMBA-Protokoll und der Modellierung auf Hardware-Transaktionsebene im HLS-Konzept vertraut sein

- Verbesserungen bei Timing und QoR

- Verbesserte Genauigkeit der HLS-Zeitabschätzung. Bei einer Timing-Closure-Meldung durch HLS sollte auch die Vivado™ RTL-Synthese das Timing erfüllen

- EoU-Verbesserungen

- Schnittstellenadapter-Bericht im C-Synthesebericht hinzufügen

- Benutzer müssen wissen, welche Auswirkungen Schnittstellenadapter auf ihr Konzept haben

- Schnittstellenadapter haben variable Eigenschaften, die sich auf die Ergebnisqualität des Konzepts auswirken

- Neuen Abschnitt im Synthesebericht hinzufügen, um eine Liste der Pragmen und Warnungen zu Pragmen anzuzeigen

- Verbesserungen bei Analyse und Berichterstellung

- Neue Möglichkeit zum Vergrößern und Verkleinern der Ansicht durch Ziehen der Maus

- Neue Übersichtsfunktion, die den vollständigen Graphen anzeigt und dem Benutzer ermöglicht, Teile des Gesamtgraphen zu vergrößern

- Alle Funktionen und Schleifen werden zusammen mit ihren Simulationsdaten angezeigt

- Nach der Simulation ist jetzt ein neuer Zeitachsentrace-Viewer verfügbar. Dieser Viewer zeigt das Laufzeitprofil Ihres Konzepts an und ermöglicht dem Benutzer, in der Vitis HLS-GUI zu bleiben

Highlights des Release 2021.1

- Neuer „Flow Navigator“ in der GUI für schnellen Zugriff auf Flow-Phasen und Berichte. Die kontextbezogenen Ansichten für Synthese/Analyse/Debugging werden in einem allgemeinen Standardkontext zusammengeführt

- Neuer Abschnitt im Synthesebericht für die Anweisungen BIND_OP und BIND_STORAGE

- Ein neuer Textbericht nach der Synthese spiegelt die im GUI-Synthesebericht enthaltenen Informationen wider

- Die Widgets für IP-Export und Vivado™ Implementierungslauf wurden überarbeitet und bieten jetzt Optionen zur Übergabe von Einstellungen und Einschränkungsdateien an Vivado

- Neue Graph-Anzeige für Funktionsaufrufe zur Visualisierung von Funktionen und Schleifen, die mit einer optionalen Heatmap hervorgehoben werden können, um II-, Latenz- oder DSP/BRAM-Auslastungs-Hotspots zu erkennen

- Versal™ Timing-Kalibrierung und neue Steuerelemente für native Gleitkommaoperationen des DSP-Blocks (die -precision-Option für config_op)

- Alternative Option zum Pipeline-Flushing wurde verbessert (Free Running Pipeline, „FRP“)

- In Vitis sollte die Umformung von m_axi-Schnittstellen über die hls::vector-Typen erfolgen

- Neue Anpassungsoptionen für s_axilite und m_axi-Datenspeicher („auto“, „uram“, „bram“ oder „lutram“), mit denen Sie die RAM-Auslastung in Ihrem Konzept optimieren können

- Einführung eines neuen kontinuierlichen („nie endenden“) Ausführungsmodus für Kernel in Vitis

- Die sekundäre axi_lite-Taktungsoption wurde erneut aktiviert

Erfolgsgeschichten

Vitis HLS-Kundenerfolg: Intuitive Surgical

Intuitive Surgical, der weltweit führende Anbieter von Chirurgierobotern, setzt FPGAs ein, um einige seiner Anforderungen an die High-Performance-Bildgebung zu erfüllen.

Eine Funktion, die für die Prototypenerstellung benötigt wurde, war eine Bildverzerrungsfunktion für 4K-Auflösung bei 60 Bildern pro Sekunde (FPS). Das Konzept hatte strenge Anforderungen bezüglich Latenz. Aus Zeitgründen entschied man sich, diese Funktion mit Vitis HLS zu implementieren. Der Code wurde mit technischer Unterstützung vom AMD Vitis HLS-Team von Grund auf neu entwickelt. Der gesamte Konzeptprozess dauerte etwa zwei Wochen und die Performance-Ziele wurden erreicht.

„Bildverzerrung ist ein komplexer Vorgang in FPGAs und kann mehrere Monate dauern, wenn die Implementierung über RTL erfolgt. Der auf Vitis HLS basierende Ansatz ermöglichte es uns, das Konzept schnell umzusetzen. Obwohl das Konzept nicht vollständig optimiert war, war die Geschwindigkeit, mit der wir Prototypen erstellen konnten, phänomenal und zeigte die Vorteile von HLS. Diese Methode ermöglichte schnelle Iterationen, und mit Unterstützung des AMD HLS-Teams und Anpassungen an die angewandten Pragmen konnten wir das Konzept in beispielloser Zeit erfolgreich auf dem FPGA SoC einrichten. Wir haben bisher HLS für unsere Bildgebungsfunktionen genutzt und beabsichtigen, dies auch weiterhin zu tun.“

- Azhar Sufi, Senior Manager, Firmware – Bildgebung, Intuitive Surgical

Mit Vitis HLS eine extrem niedrige Latenz in einem Audio-DSP-zu-FPGA erzielen

Das Emeraude Research Team von INSA Lyon arbeitet an der Entwicklung neuer Signalverarbeitungstechniken für integrierte Audiosysteme. Das Team hat mit dem AMD Vitis HLS-Tool ein Audio-DSP-Programm mit extrem niedriger Latenz implementiert. Klicken Sie hier, um mehr darüber zu erfahren, wie das Vitis HLS-Tool dem Team dabei half, eine extrem niedrige Latenz in einer Audio-DSP-zu-FPGA-Kompilierung zu erzielen.

Kunden-Fallstudie

Schnellere Exploration des Entwurfsraums mit Vitis HLS

„Der Hauptvorteil des AMD Vitis™ HLS-Tools besteht aus meiner Sicht in der Funktion zur Exploration des Entwurfsraums. Sie können verschiedene Architekturen und Implementierungen in einem angemessenen Zeitraum durch Verwendung von Optimierungsanweisungen (Pipelining, Unrolling usw.) generieren. Dies ist nicht möglich, wenn Sie manuell mit VHDL/Verilog codieren. Eine sehr nützliche Funktion von Vitis HLS ist die Möglichkeit, eine Co-Simulation und Validierung des HDL-Codes durchzuführen, um sicherzustellen, dass der HDL-Code korrekt funktioniert.“ Dr. Frank Kesel – Professor an der Universität Pforzheim

Kunden-Fallstudie

Ressourcen

Fußnoten

- Basierend auf Tests am 10. August 2023 in 1.000 Designs der Vitis-Codebibliothek auf L2/L3 mit Vitis HLS Release 2023.2 gegenüber Vitis HLS 2023.1. Systemkonfiguration während des Tests: Intel Xeon E5-2690 v4 mit 2,6 GHz CPU, 256 GB RAM, RedHat Enterprise Linux 8.6. Die tatsächliche Performance kann abweichen. Systemhersteller wählen möglicherweise andere Konfigurationen, was zu anderen Ergebnissen führen kann. -VGL-04

- Die Benchmark-Tests wurden an allen 1208 C-Code-Designs der Vitis L1-Bibliothek mit Stand vom 12. Februar 2023 durchgeführt. Alle Designs wurden mit einem System mit 2P Intel Xeon E5-2690 CPUs mit CentOS Linux ausgeführt, SMT aktiviert, Turbo Boost deaktiviert. Die Hardwarekonfiguration hat der Erwartung nach keine Auswirkungen auf die Ergebnisse des Softwaretests. Die Ergebnisse können je nach Software- und Firmware-Einstellungen und -Konfigurationen variieren – VGL-03

- Basierend auf Tests am 10. August 2023 in 1.000 Designs der Vitis-Codebibliothek auf L2/L3 mit Vitis HLS Release 2023.2 gegenüber Vitis HLS 2023.1. Systemkonfiguration während des Tests: Intel Xeon E5-2690 v4 mit 2,6 GHz CPU, 256 GB RAM, RedHat Enterprise Linux 8.6. Die tatsächliche Performance kann abweichen. Systemhersteller wählen möglicherweise andere Konfigurationen, was zu anderen Ergebnissen führen kann. -VGL-04

- Die Benchmark-Tests wurden an allen 1208 C-Code-Designs der Vitis L1-Bibliothek mit Stand vom 12. Februar 2023 durchgeführt. Alle Designs wurden mit einem System mit 2P Intel Xeon E5-2690 CPUs mit CentOS Linux ausgeführt, SMT aktiviert, Turbo Boost deaktiviert. Die Hardwarekonfiguration hat der Erwartung nach keine Auswirkungen auf die Ergebnisse des Softwaretests. Die Ergebnisse können je nach Software- und Firmware-Einstellungen und -Konfigurationen variieren – VGL-03