Descripción general

AMD Vitis™ HLS para un diseño y una productividad intuitivos

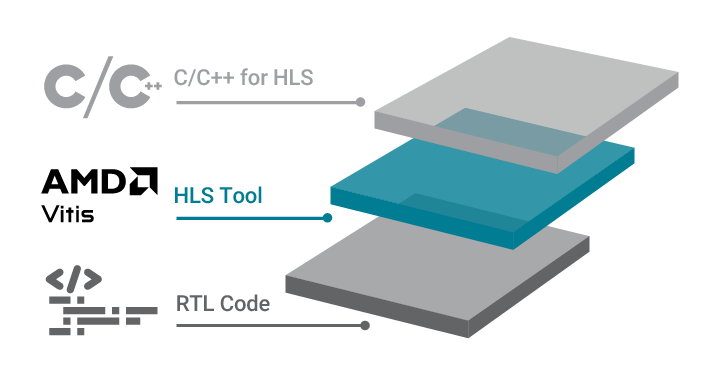

La herramienta AMD Vitis™ HLS permite a los usuarios crear con facilidad algoritmos de FPGA (Field-Programmable Gate Arrays, matriz de puertas lógicas programable en campo) complejos sintetizando una función C/C++ en el RTL (register transfer level, nivel de transferencia de registros). La herramienta Vitis HLS está estrechamente integrada en Vivado™ Design Suite para funciones de síntesis y colocación y ruta, y con la plataforma de software unificado de Vitis™ para diseños y aplicaciones de sistemas heterogéneos.

- Utilizando el flujo de Vitis HLS, los usuarios pueden aplicar directivas al código en C y crear el RTL específico para una implementación deseada.

- Se pueden crear múltiples arquitecturas de diseño a partir del código fuente en C y se habilita una ruta para RTL de corrección por construcción de alta calidad.

- La simulación de C se puede utilizar para validar el diseño y permite iteraciones más rápidas que una simulación tradicional basada en RTL.

- La herramienta Vitis HLS cuenta con un amplio conjunto de herramientas de análisis y depuración que facilitan la optimización del diseño.

Pragma de rendimiento de AMD Vitis™ HLS

AMD Vitis HLS tiene un nuevo pragma de rendimiento de alto nivel que te ayuda a alcanzar una QoR (Quality-of-Results, calidad de los resultados) más alta. Ve el módulo técnico para obtener más información sobre cómo usar esta nueva función.

Metodología de diseño

Modelo de programación de Vitis HLS

El código en C de Vitis HLS está orientado a aprovechar las ventajas y las características que ofrece la arquitectura de los SoC adaptables y las FPGA de AMD.

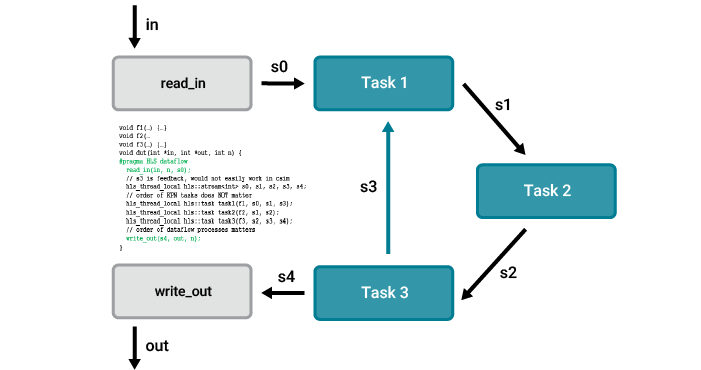

La herramienta Vitis HLS es compatible con las construcciones de programación paralela para modelar la implementación deseada. Estas construcciones incluyen las siguientes opciones:

- Tareas de HLS (high-level synthesis, síntesis de alto nivel) que permiten la concurrencia de procesos.

- Vectores de HLS que permiten el paralelismo de datos.

- Streams de HLS que permiten la comunicación entre tareas concurrentes.

- Los pragmas de síntesis se pueden utilizar para controlar los resultados. Estos pragmas incluyen canalización, desenrollamiento, creación de particiones por matrices y protocolos de interfaz.

- Para obtener más información, consulta la sección “Guía para programadores de HLS” de la Guía del usuario de síntesis de alto nivel de Vitis.

Generación de código MATLAB-to-HLS C++

Las funciones desarrolladas en MATLAB® se pueden sintetizar en código C++ amigable con AMD Vitis™ HLS a través de las capacidades de generación de código de MathWorks HDL Coder disponibles en MATLAB R2025a.

Este código C++ generado y sintetizable puede servir como entrada a Vitis™ HLS. Este flujo de trabajo puede acelerar el proceso de traducción desde un diseño de algoritmo de alto nivel (normalmente hecho en MATLAB) hasta una implementación de RTL de bajo nivel.

Utiliza MATLAB y HDL Coder para diseñar y crear bancos de pruebas. A continuación, usa la función de generación de código en HDL Coder para ingresar en Vitis HLS a fin de simular y sintetizar SoC y FPGA adaptables de AMD.

Para obtener más información, visita la página de MathWorks HDL Coder.

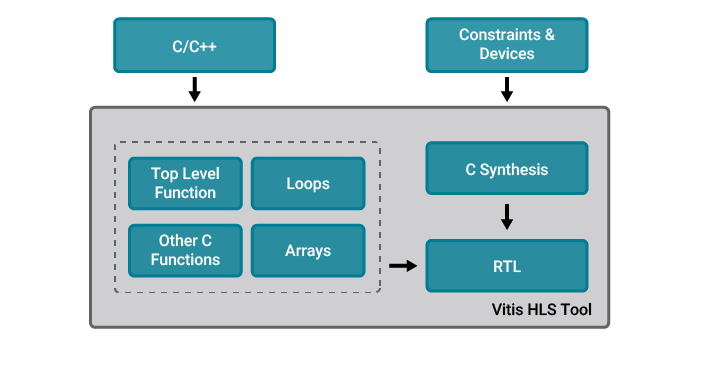

Conversión de C a RTL

La herramienta Vitis HLS sintetiza diferentes partes del código en C de manera diferente:

- Los argumentos de función de nivel superior del código en C/C++ se sintetizan en puertos de E/S de RTL y se implementan automáticamente con un protocolo de hardware de síntesis de interfaz.

- Otras funciones en C se sintetizan en bloques RTL, manteniendo la jerarquía de diseño.

- Los bucles de función en C se mantienen enrollados o canalizados para mejorar el rendimiento.

- Las matrices en el código en C se pueden orientar a cualquier recurso de memoria, como BRAM, LUTRAM y URAM.

- Las métricas de rendimiento, como la latencia, el intervalo de iniciación, la latencia de iteración de bucles y la utilización de recursos, se pueden revisar con informes de síntesis.

- Las pragmas y las directivas de optimización de Vitis HLS permiten configurar los resultados de síntesis para el código en C/C++.

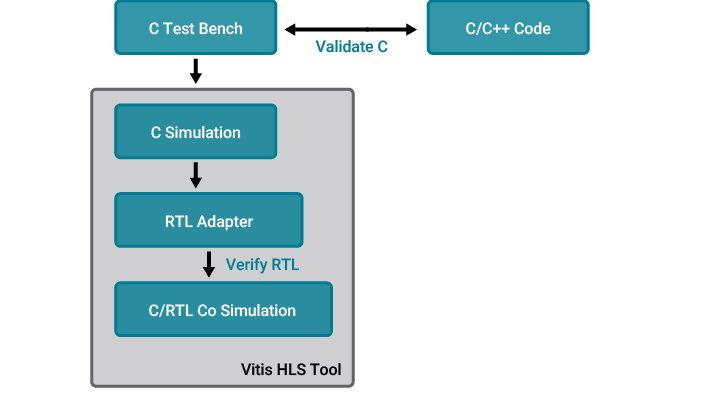

Simulación y verificación

La herramienta Vitis HLS presenta flujos de simulación integrados para permitir tiempos de verificación más rápidos:

- La simulación de C valida la funcionalidad del código en C. Este paso es rápido y utiliza un banco de prueba en C.

- La simulación conjunta de C/RTL reutiliza el banco de prueba en C para realizar la validación en el RTL generado, verificando que el RTL sea funcionalmente idéntico al código fuente en C.

- El flujo tiene compatibilidad integrada de análisis, depuración y visualización de formas de onda, así como compatibilidad con los simuladores más conocidos.

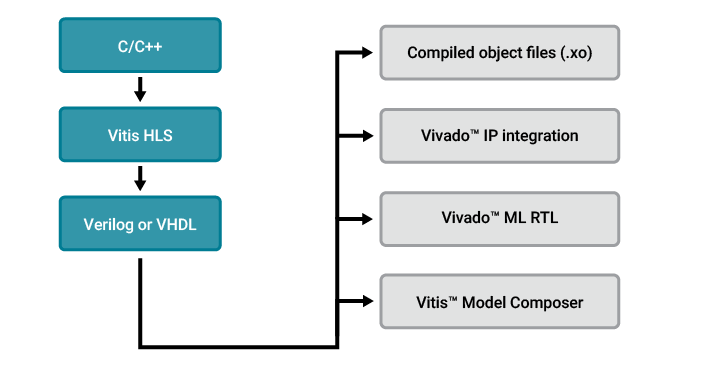

Exportación de IP

La salida de la herramienta Vitis HLS es una implementación de RTL que se puede empaquetar en un archivo de objeto compilado (.xo) o exportar a una IP de RTL:

- Los archivos de objeto compilado (.xo) se utilizan a fin de crear funciones de aceleración de hardware para usar en el flujo de desarrollo de aplicaciones de Vitis.

- La IP de RTL se puede utilizar de tres maneras:

- agregarla usando la herramienta de integrador de IP de Vivado™;

- importarla como un bloque RTL en el IDE de Vivado; o

- utilizarla como un único conjunto de bloques en Vitis Model Composer para aplicaciones de DSP (Digital Signal Processing, procesamiento de señales digitales).

Lo nuevo

- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

Aspectos destacados de la versión 2025.2

- Mejoras en el pragma de rendimiento

- El pragma de rendimiento ahora se optimizará en función del recuento de iteraciones calculado por CSIM.

- Las optimizaciones del pragma de rendimiento pueden convertirse en directivas dentro de un archivo de configuración.

- Control condicional de pragmas, incluido el pragma de rendimiento

- Nueva compatibilidad de IP

- SSR de tasa fraccional para FIR y FFT: para FFT, la SSR en SPFP32 ahora admite hasta SSR = 64.

- Compatibilidad con ECC para búferes de flujo de datos implementados con Block RAM o UltraRAM

- Funciones fáciles de usar

- Compatibilidad con el reinicio automático en CSIM y CoSim

- Caché multipuerto para M-AXI

- Nuevas API para flujos AXI con señales laterales

Aspectos destacados de la versión 2025.1

- Genera código C++ simple con Vitis HLS a partir de diseños de MATLAB (.m) con HDL Coder y MATLAB R2025a

- Nuevas funciones de Vitis HLS de facilidad de uso

- Modelado de entradas de cable y AXI Lite que cambian durante la ejecución (E/S directa)

- Pragma de rendimiento para el diseño HLS de nivel superior (acceso anticipado abierta)

- Compatibilidad con el multiplicador complejo de Versal a través de la biblioteca intrínseca dedicada

- Mejoras en la interfaz gráfica de usuario de Vitis HLS

- Compatibilidad inicial de C++17 a través de Clang 16

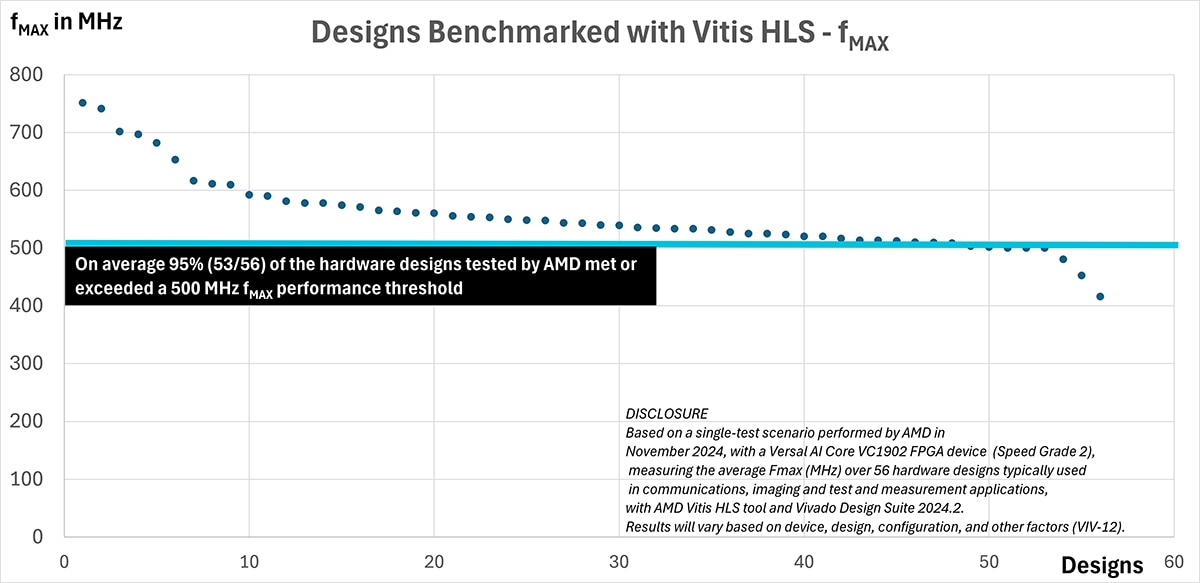

Lo más destacado de la versión 2024.2

La versión 2024.2 de Vitis HLS incluye una serie de funciones que facilitan a los usuarios el desarrollo y la depuración de un diseño HLS; estas incluyen las siguientes opciones:

- modelado de entradas escalares/cableadas que cambian durante la ejecución (E/S directa);

- compatibilidad con tipos de puntos flotantes de precisión arbitraria;

- asignación de código HLS a bloques DSP;

- Secuencia determinada por el usuario de ejecución de código

- depurador HLS que muestra los tipos de datos de una manera fácil de usar (utilizando la tecnología prettyprint del depurador GNU).

Lo más destacado de la versión 2024.1

- Un nuevo pragma de símbolos simplifica el código HLS en C++ para filtros de imágenes y videos.

Los nuevos wizards de función de biblioteca aprovechan el repositorio GitHub de las bibliotecas de AMD Vitis.

- Crea IP “Solver” y “Vision” (compatibles con OpenCV) para la herramienta de diseño AMD Vivado.

- Ejecuta los ejemplos de biblioteca disponibles.

El pragma para la interfaz de memoria (ap_memory) ahora puede agrupar puertos para AMD Vivado IP Integrator.

La nueva comparación de componentes HLS muestra métricas lado a lado para dos o más componentes.

Compatibilidad con el código RTL de usuario-proveedor para reemplazar una función en C++ (flujo de caja negra).

Code Analyzer ahora puede desagregar miembros de estructuras en C++ para ajustar con precisión el análisis de rendimiento.

Nuevo control de usuario para la codificación de FSM global de HLS y la selección de un estado seguro.

Acceso a desinfectantes de Clang durante la simulación de C para realizar comprobaciones de dirección e inicialización.

Lo más destacado de la versión 2023.2

- Nuevo IDE unificado de Vitis™ para componentes HLS

- Nuevos requisitos de licencia de Vitis HLS

- Nueva función de analizador de código para obtener estimaciones de rendimiento antes de ejecutar la síntesis de C

- Mejoras en la interfaz AXI:

- Mejoras en la compatibilidad para canales laterales HLS de AXI Stream

- Compatibilidad para el almacenamiento en caché maestro de AXI configurable por el usuario

- Otras mejoras:

- Nuevo informe de complejidad de código para permitir la identificación de problemas de tamaño de diseño durante la síntesis de C

- Mejoras en el tiempo de compilación: Mejora media del tiempo de compilación del 20 % en la versión 2023.2 en comparación con 2023.11

Lo más destacado de la versión 2023.1

- Mejoras en el rendimiento2: mejoras de latencia promedio del 5,2 % en la versión 2023.1 en comparación con 2022.2.

- Una forma sencilla de descargar, ver y crear instancias con las funciones de las bibliotecas de L1 en la herramienta Vitis HLS. Mira el video

- Compatibilidad mejorada para transacciones AXI e informes de ráfaga dentro de la herramienta Vitis HLS.

Lo más destacado de la versión 2022.2

- Nueva forma de escribir código “paralelo a nivel de tareas” para aplicaciones de procesamiento de datos

- El usuario puede definir explícitamente el paralelismo de tareas utilizando la nueva función hls::task.

- Más fácil de modelar para diseños puramente de streaming (por ejemplo, conmutación de paquetes).

- Mejoras de rendimiento y sincronización

- La herramienta infiere automáticamente el desenrollado, la canalización, la creación de particiones de matrices y los pragmas en línea para un mejor rendimiento.

- Análisis y mejoras de depuración

- Nueva función para sintetizar sentencias de impresión de la fuente en C en el código de RTL generado.

- Cuando se simula el RTL, esto permite rastrear la ejecución de un bloque de código y el valor de una variable.

- Facilidad de uso

- La interfaz hls::stream ahora es compatible con las IP de FFT y FIR.

Lo más destacado de la versión 2022.1

- Nuevo visor de rastreo de línea de tiempo

- Muestra el perfil en tiempo de ejecución de todas las funciones vigentes en tu diseño, es decir, aquellas que se convierten en módulos.

- Especialmente útil para ver el comportamiento de las regiones de flujo de datos después de la simulación conjunta. Nativo de Vitis™ HLS: no hay necesidad de iniciar el visor de forma de onda xsim.

- Nuevo pragma de rendimiento

- HLS indica cuál es tu objetivo de rendimiento utilizando el rendimiento de #pragma hls.

- HLS intentará alcanzar el objetivo, si es posible, utilizando menos recursos.

- HLS indicará las transformaciones realizadas y, si no puede cumplir con el objetivo, indicará el factor limitante.

- Compatibilidad con la creación de particiones de matrices para el tipo Transmisión de bloques

- Mejora de hls::stream en la que cada elemento es una matriz.

- Se puede utilizar para dividir el procesamiento de matrices grandes en trozos canalizados más pequeños.

Lo más destacado de la versión 2021.2

- Inferencia de ráfaga controlada por el usuario

- El usuario puede adoptar la optimización de ráfaga manual recién introducida.

- Se agrega una nueva clase “hls::burst_maxi” para brindar compatibilidad con el comportamiento de control manual de ráfagas. Se proporcionan nuevas API de HLS para usar junto con la nueva clase.

- Los usuarios necesitan entender el protocolo AXI AMBA y el modelado de nivel de transacciones de hardware en el diseño HLS.

- Mejoras de sincronización y QoR

- Mejora la precisión de la estimación de sincronización de HLS. Cuando HLS informa el cierre de sincronización, la síntesis del RTL de Vivado™ también debe esperar cumplir con la sincronización.

- Mejoras de EoU

- Agrega el informe de adaptadores de interfaz en el informe de síntesis de C.

- Los usuarios necesitan conocer el impacto en los recursos que tienen los adaptadores de interfaz en su diseño.

- Los adaptadores de interfaz tienen propiedades variables que impactan en la QoR del diseño.

- Agrega una nueva sección en el informe de síntesis para mostrar la lista de pragmas y advertencias sobre ellos.

- Mejoras en el análisis y la presentación de informes

- Nueva compatibilidad para acercar o alejar basada en el arrastre del mouse.

- Nueva función de visión general que muestra el gráfico completo y permite al usuario acercar partes del gráfico general.

- Todas las funciones y todos los bucles se muestran junto con sus datos de simulación.

- Un nuevo visor de rastreo de línea de tiempo está ahora disponible después de la simulación. Este visor muestra el perfil de tiempo de ejecución de tu diseño y permite al usuario permanecer en la GUI de Vitis HLS.

Lo más destacado de la versión 2021.1

- Nuevo “Flow Navigator” en la GUI para un acceso rápido a las fases de flujo y los informes. Las vistas contextuales de “síntesis, análisis, depuración” se fusionan en un contexto predeterminado general.

- Nueva sección de informe de síntesis para las directivas BIND_OP y BIND_STORAGE.

- Un nuevo informe de texto posterior a la síntesis refleja la información proporcionada en el informe de síntesis de la GUI.

- Los widgets de ejecución de implementación de Vivado™ y exportación de IP se rediseñaron con opciones para pasar ajustes y archivos de restricciones a Vivado.

- Nuevo visor gráfico de llamada de funciones para visualizar funciones y bucles que se pueden resaltar con un mapa térmico opcional para detectar zonas activas de utilización de DSP/BRAM, II (initiation interval, intervalo de iniciación) o latencia.

- Calibración de sincronización de Versal™ y nuevos controles para las operaciones nativas de punto flotante del bloque DSP (la opción -precision para config_op).

- Se mejoró la opción de canalización de vaciado alternativa (canalización de funcionamiento libre conocida como “frp”).

- En Vitis, la remodelación de las interfaces m_axi debe hacerse a través de los tipos hls::vector.

- Nuevas opciones de personalización para el almacenamiento de datos s_axilite y m_axi que pueden ser “auto”, “uram”, “bram” o “lutram”, lo que permite ajustar la utilización de la RAM en tu diseño.

- En Vitis, introducimos un nuevo modo de ejecución continua (también conocido como “never-ending”) para el kernel.

- La opción de reloj secundario axi_lite se restableció.

Historias de éxito

Éxito del cliente de Vitis HLS: Intuitive Surgical

Intuitive Surgical, el líder mundial en robots quirúrgicos, utiliza FPGA para implementar algunos de sus requisitos de imágenes de alto rendimiento.

Necesitaban el prototipo de una función de deformación de imágenes en una resolución 4K a 60 cuadros por segundo (FPS). El diseño tenía requisitos de latencia estrictos. Debido a limitaciones de tiempo, se decidió implementar esta función con Vitis HLS. El código se desarrolló desde cero con el apoyo técnico del equipo AMD Vitis HLS. Todo el proceso de diseño tomó alrededor de dos semanas, y se cumplieron los objetivos de rendimiento.

“La deformación de imágenes es una operación compleja en FPGA y puede requerir varios meses cuando se implementa con RTL. El enfoque basado en Vitis HLS nos permitió implementar rápidamente el diseño. Aunque el diseño no estaba completamente optimizado, la velocidad con la que llegamos al prototipo fue fenomenal, y demostró los beneficios de HLS. Este método facilitó iteraciones rápidas, y con el apoyo del equipo de HLS de AMD y ajustes a los pragmas aplicados, se pudo poner en marcha con éxito el diseño en el SoC de FPGA en un tiempo sin precedentes. Buscamos seguir utilizando HLS para nuestras funciones de imagen”.

- Azhar Sufi, gerente sénior, Firmware e Imágenes, Intuitive Surgical

Obtén una latencia ultrabaja en una compilación de DSP de audio a FPGA con Vitis HLS

El equipo de investigación Emeraude de INSA Lyon está trabajando en el desarrollo de nuevas técnicas de procesamiento de señales para sistemas de audio integrados. El equipo implementó un programa DSP de audio de latencia ultrabaja utilizando la herramienta AMD Vitis HLS. Haz clic aquí para obtener más información sobre cómo la herramienta Vitis HLS ayudó al equipo a lograr una latencia ultrabaja en una compilación de DSP de audio a FPGA.

Caso de estudio de clientes

Exploración de espacio de diseño más rápida con Vitis HLS

“La principal ventaja de la herramienta AMD Vitis™ HLS, desde mi perspectiva, es la función de exploración del espacio de diseño. Puedes generar diferentes arquitecturas e implementaciones en un tiempo razonable utilizando directivas de optimización (canalización, desenrollamiento, etc.). Esto no se puede hacer codificando manualmente con VHDL/Verilog. Una buena función de Vitis HLS es la posibilidad de realizar una simulación conjunta y una validación del código de HDL para asegurarse de que sea funcionalmente correcto”. Dr. Frank Kesel, profesor de la Universidad de Pforzheim, Alemania

Caso de estudio de clientes

Recursos

Notas al pie

- Basado en pruebas realizadas el 10 de agosto del 2023, en 1000 diseños de biblioteca de códigos de L2/L3 de Vitis, con Vitis HLS versión 2023.2 en comparación con Vitis HLS 2023.1. Configuración del sistema durante las pruebas: CPU Intel Xeon E5-2690 v4 a 2,6 GHz, 256 GB de RAM, Red Hat Enterprise Linux 8.6. El rendimiento real variará. Los fabricantes de sistemas pueden variar las configuraciones, lo que arroja resultados diferentes. -VGL-04

- Las evaluaciones comparativas se realizaron en los 1208 diseños de código en C de la biblioteca de L1 de Vitis al 12 de febrero del 2023. Todos los diseños se ejecutaron utilizando un sistema con CPU 2P Intel Xeon E5-2690 con CentOS Linux, SMT habilitado y Turbo Boost deshabilitado. No se espera que la configuración de hardware afecte los resultados de las pruebas de software. Los resultados pueden variar en función de la configuración del software y del firmware: VGL-03

- Basado en pruebas realizadas el 10 de agosto del 2023, en 1000 diseños de biblioteca de códigos de L2/L3 de Vitis, con Vitis HLS versión 2023.2 en comparación con Vitis HLS 2023.1. Configuración del sistema durante las pruebas: CPU Intel Xeon E5-2690 v4 a 2,6 GHz, 256 GB de RAM, Red Hat Enterprise Linux 8.6. El rendimiento real variará. Los fabricantes de sistemas pueden variar las configuraciones, lo que arroja resultados diferentes. -VGL-04

- Las evaluaciones comparativas se realizaron en los 1208 diseños de código en C de la biblioteca de L1 de Vitis al 12 de febrero del 2023. Todos los diseños se ejecutaron utilizando un sistema con CPU 2P Intel Xeon E5-2690 con CentOS Linux, SMT habilitado y Turbo Boost deshabilitado. No se espera que la configuración de hardware afecte los resultados de las pruebas de software. Los resultados pueden variar en función de la configuración del software y del firmware: VGL-03