Vitis Embedded

Vitis Embedded

Vitis™ Embedded es un paquete de desarrollo de software integrado independiente que permite desarrollar aplicaciones host que se ejecutan en procesadores integrados Arm.

Versión 2025.2 disponible ahora

La plataforma de software AMD Vitis™ es un entorno de desarrollo para diseños destinados a la estructura de FPGA, procesadores Arm® y motores de IA, que funciona junto con AMD Vivado™ Design Suite para proporcionar un nivel más alto de abstracción.

El software Vitis incluye Vitis Embedded para el desarrollo de aplicaciones en C/C++ para procesadores Arm, compiladores y simuladores de motores de IA, Vitis HLS para IP de FPGA basado en C/C++, Vitis Model Composer para diseño basado en modelos en Simulink® y bibliotecas optimizadas para rendimiento como DSP, Vision, Solver, Ultrasound y BLAS para implementación en FPGA o motor de IA.

Aprende a crear una solución de sistema integrada utilizando el sistema de flujo heterogéneo unificado de Vitis.

(Tradicionalmente llamado SDK integrado para familias de FPGA anteriores)

Los diseñadores que desarrollan código C/C++ para el subsistema de procesador integrado Arm® en SoC adaptables de AMD normalmente utilizarán este flujo.

Los desarrolladores pueden realizar toda la verificación a nivel del sistema dentro del software Vitis Embedded y generar imágenes de arranque para iniciar la aplicación.

(Hardware y software)

Los diseñadores de sistemas que integran las partes de software y hardware de su diseño en SoC adaptables de AMD normalmente utilizarán este flujo.

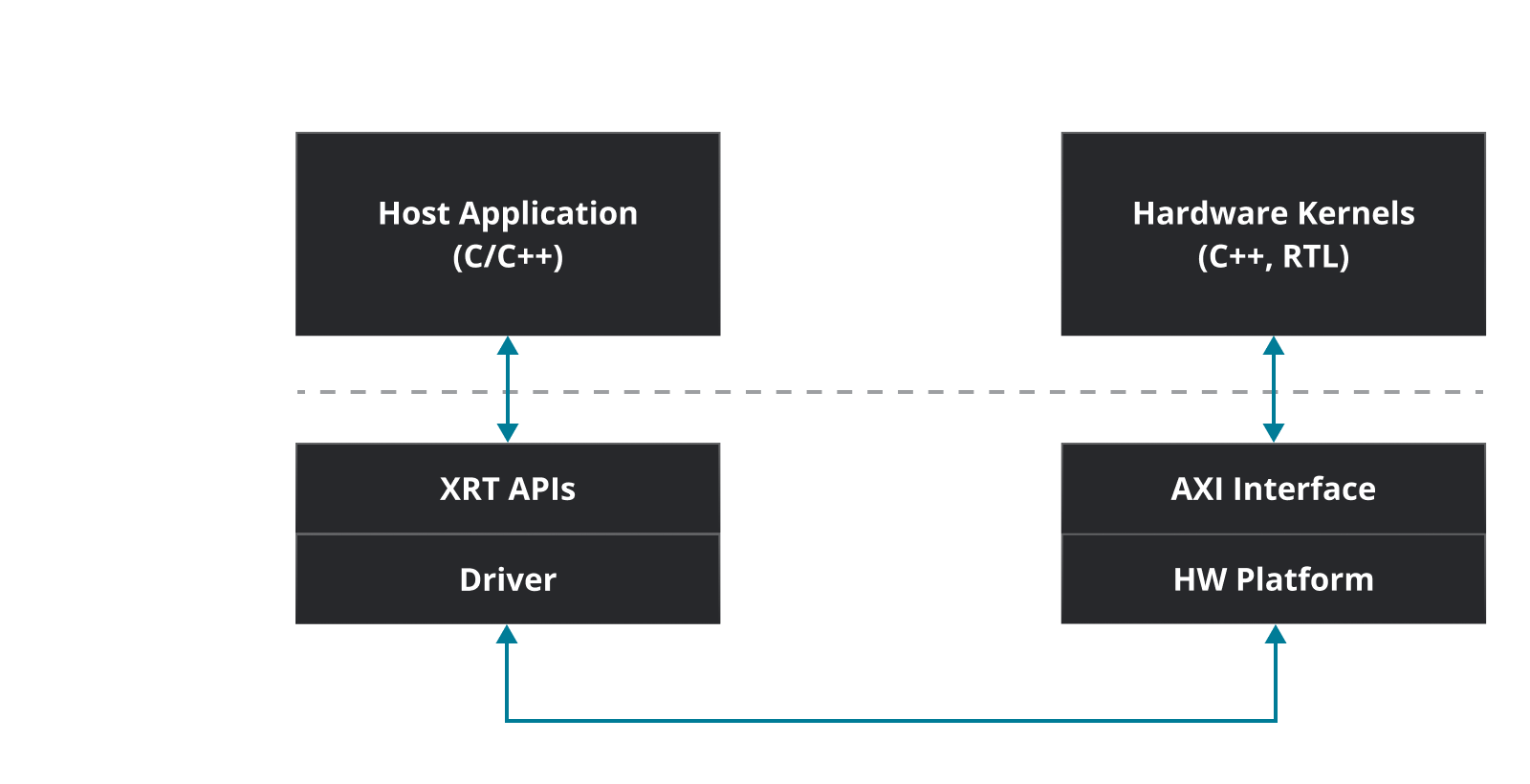

Este flujo se utiliza para desarrollar diseños de sistemas integrados heterogéneos que comprenden aplicaciones de software que se ejecutan en procesadores integrados Arm® y núcleos de procesamiento que se ejecutan en PL (programmable logic, lógica programable) o matrices de motores de IA de Versal™.

Este flujo comprende:

Las tarjetas aceleradoras del centro de datos AMD Alveo™ emplean el mismo flujo de diseño de sistema: el programa de software se ejecuta en un host x86 y los núcleos se ejecutan en la FPGA en una tarjeta de aceleración conectada a PCIe®.

Simulaciones en tus herramientas preferidas

• Utiliza los bancos de pruebas de MATLAB®, Python™, C++ o HDL existentes

• Evita reescribir los bancos de pruebas o aprender nuevos flujos de trabajo

• Acelera la iteración de algoritmo a hardware

Simulación unificada del motor de IA + PL (Vitis Subsystem)

• Simule el motor de IA y la PL juntos

• Reemplaza los flujos fragmentados con una metodología uniforme

• Detecta los problemas de integración con anticipación

Validación de hardware en el bucle (HIL)

• Acorta el tiempo de validación a nivel de sistema

• Transmite datos de E/S reales a través del chip para obtener una depuración más rápida

• Verifica el rendimiento integral antes de que el hardware final esté listo