Vitis 软件平台开发环境

AMD Vitis™ 软件平台是面向 FPGA 结构、Arm® 处理器和 AI 引擎设计的开发环境,可与 AMD Vivado™ Design Suite 配合使用,提供更高级别的抽象。

Vitis 软件包括:用于 Arm 处理器 C/C++ 应用开发的 Vitis Embedded;AI 引擎编译器和仿真器;用于基于 C/C++ 的 FPGA IP 的 Vitis HLS;用于 Simulink® 中基于模型设计的 Vitis Model Composer;以及用于 FPGA 或 AI 引擎部署的性能优化库(如 DSP、Vision、Solver、Ultrasound 和 BLAS)。

设计和仿真流程

Adam Taylor 讲解:基于 Vitis 统一平台的分步系统设计方法

了解如何使用 Vitis 统一异构系统流程构建嵌入式系统解决方案。

Vitis 嵌入式软件开发流程

(以前称为嵌入式 SDK,主要针对早期的 FPGA 系列)

从 Vivado 导出硬件,作为平台文件

开发应用代码

调试并生成引导映像

在 AMD 自适应 SoC 中为 Arm® 嵌入式处理器子系统开发 C/C++ 代码的设计人员通常会使用该流程。

- 通过使用 AMD Vivado™ Design Suite,硬件工程师不仅可以设计可编程逻辑,还可将硬件导出为 Xilinx Support Archive (XSA) 文件。

- 软件工程师可将这些硬件设计信息整合到他们的目标平台中,并可使用 Vitis 嵌入式软件开发应用代码。

开发人员可在 Vitis 嵌入式软件中执行所有系统级验证,并通过生成启动镜像来启动应用。

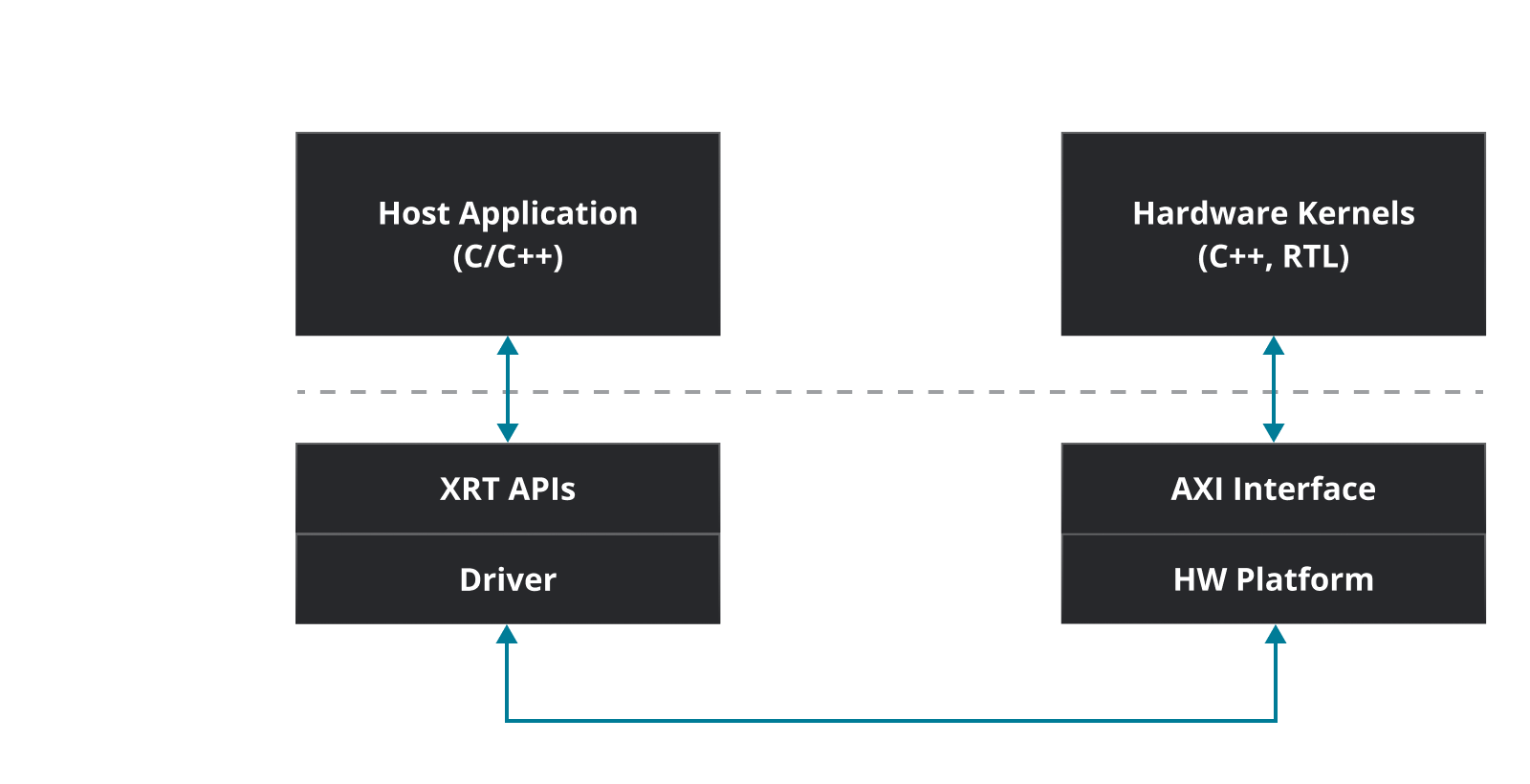

Vitis 系统设计流程

(硬件与软件)

在 AMD 自适应 SoC 中集成其设计软硬件部分的系统设计人员通常会使用该流程。

该流程用于开发异构嵌入式系统设计,其中包括运行在 Arm® 嵌入式处理器上的软件应用,以及运行在可编程逻辑 (PL) 和/或 Versal™ AI 引擎阵列上的计算内核等。

该流程包括:

- 采用 C/C++ 编写的软件主机应用,通常运行在嵌入式 Arm 处理器子系统上。使用通过 AMD Vitis 运行时库实现的本机 API 与 AMD 器件内的硬件内核进行交互。

- 硬件内核可使用 AMD Vitis™ HLS 工具从 C++ 生成,也可使用 AMD Vivado™ Design Suite 直接在 RTL 中描述。

AMD Alveo™ 数据中心加速卡采用相同的系统设计流程:软件程序运行在 x86 主机上,内核运行在 PCIe® 连接的加速卡上的 FPGA 中。

Vitis 异构仿真流程

在您偏好的工具中进行仿真

• 使用现有的 MATLAB®、Python™、C++ 或 HDL 测试激励文件

• 避免重写测试激励文件或学习新的工作流程

• 加速从算法到硬件的迭代

统一的 AI 引擎 + PL 仿真(Vitis 子系统)

• AI 引擎和 PL 协同仿真

• 用一致的方法取代分散的流程

• 及早发现集成问题

硬件在环 (HIL) 仿真验证

• 缩短系统级验证时间

• 通过芯片传输真实 I/O 数据,以加快调试速度

• 在最终硬件就绪前验证端到端吞吐量

工具和库

2025.2 版新增功能

基于 AMD Versal™ AI Engine 的设计流程优化

- AI 引擎 API 增强

- 全新和增强的数据类型

- 编程模型更新和优化

- 全新和增强的 DSP 库函数

- 经过改进的 AI 引擎映射器与布线器

简化了 Versal AI Engine 设计验证

- Vitis 功能仿真工作流程更新

- 使用 MATLAB® 和 Python™ 测试激励文件进行硬件在环仿真(抢先体验版)

- 详细了解 Versal AI Engine

针对 AIE DSP 设计改进了 Vitis Model Composer

- 超采样率 (SSR) 设计的易用性更新

- 提供更多适用于 AI 引擎和 HDL 的块

- 详细了解 Vitis Model Composer

针对嵌入式开发的 Vitis IDE 更新

- Vitis Embedded 现在支持集成第三方 AI 代码助手

- 允许使用基于 Eclipse Theia 的 VS 代码编辑器

- 支持 Zephyr (RTOS)

- 通过 PS 追踪增强了调试功能

- 详细了解 Vitis IDE