AMD Versal™ AI Engine 助力释放 DSP 算力

Versal AI Engine 技术全面赋能,满足高性能数字信号处理 (DSP) 需求

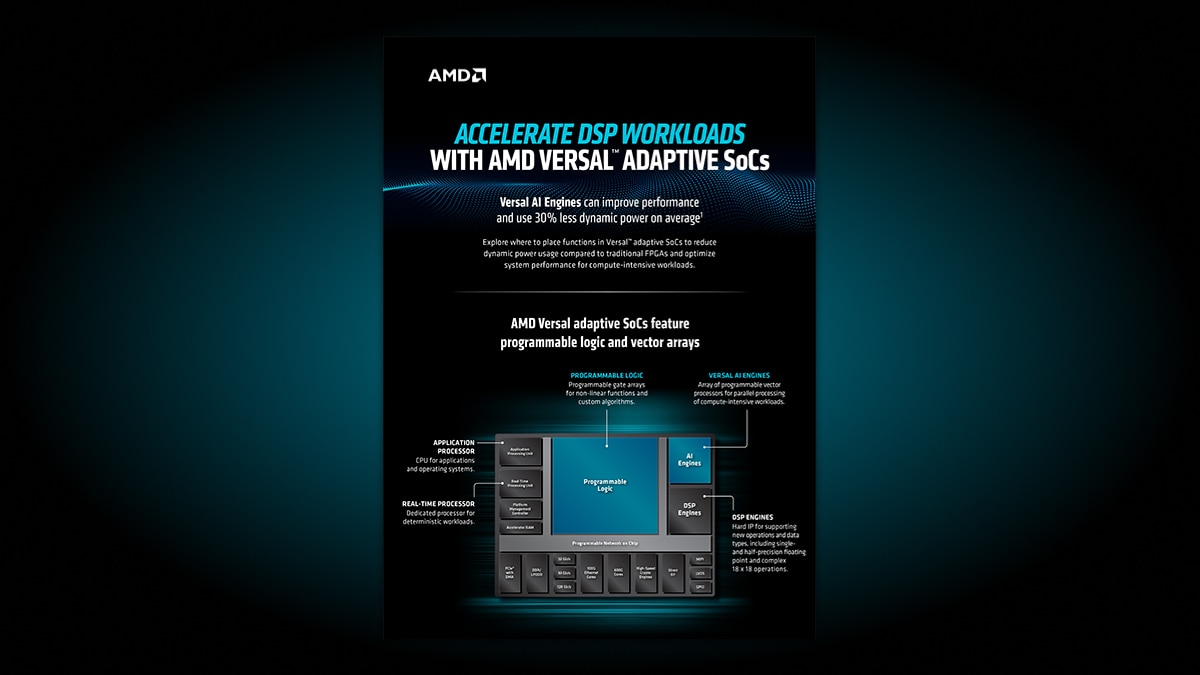

如果客户要处理新一代 DSP 应用,就需要强大的算力;而传统 FPGA 架构无法有效满足这一需求。FIR、FFT 和通用矩阵乘法等计算密集型 DSP 应用需要使用大量 DSP 块和可编程逻辑资源。

由于算法非常复杂,可能会大幅消耗传统可编程逻辑器件上可用的总体算力。从可扩展性角度而言,对于具有严苛功耗预算要求的密集型 DSP 工作负载,仅单纯增加可用的 DSP 块和可编程逻辑资源并不是行之有效的解决方案。Versal AI Engine 经过精心设计,能够针对这种情况提供更加高效的算力解决方案。

我们的操作视频库旨在提供必要的技术信息,助您快速入门。

AI 引擎 DSP 设计流程

针对 AMD Versal™ AI 引擎设计高性能 DSP 功能,可使用 AMD Vitis™ 开发工具完成,也可使用 Vitis Model Composer 流程完成,充分发挥 MathWorks Simulink® 工具的仿真及图形功能优势。

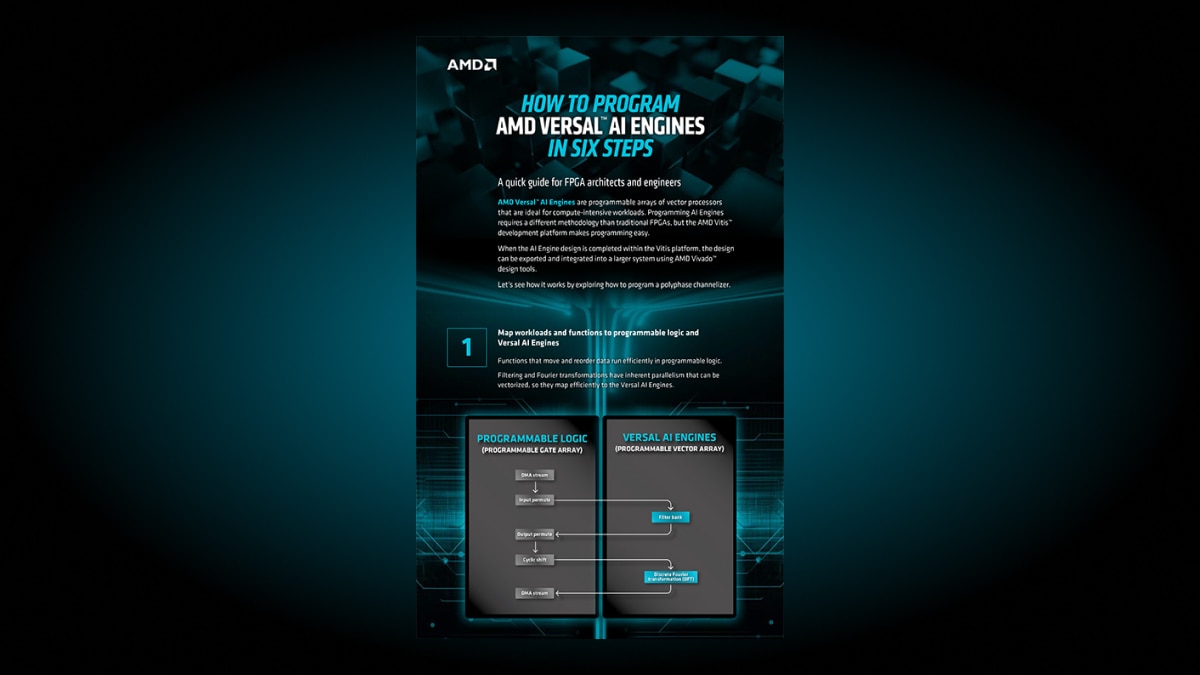

在任何一种情况下,无论是将 DSP 应用映射到在 FPGA 或 AI 引擎中要实现的功能中,还是将其映射到 FPGA 逻辑和 AI 引擎的组合中,都至关重要。这需要了解器件功能以及整个系统。

通常,计算密集型功能更适合 AI 引擎执行,而需要数据移动/重新排序的功能则更适合 FPGA 执行。

在下面所示的示例中,复杂的滤波和傅立叶变换通常更适合 AI 引擎阵列。

一旦功能被明确确定为适合 AI 引擎,就可使用以下任何一种选项将其实施在 AI 引擎中。

注意:使用以下列表中的多个选项的混合方法也是可行的。

编程环境

Vitis 平台提供两种编程环境,支持利用 DSP 库、API 和内部函数

- 使用 C/C++ 构建

- 使用 Vitis Model Composer 基于模型的设计流程

使用 C/C++ 构建

Vitis 平台提供多个开源构建块,支持常用 DSP 算法、函数和器件图表。您可以按原样使用它们以加速测试,也可以根据需求进行自定义。

C/C++ 流程

要开始使用 AI 引擎加速 DSP,强烈建议从 Vitis DSP 库函数(基于 C 语言)入手。虽然手动编码可确保更好地实现功能,但下述方法是使用 AI 引擎加速 DSP 的最快捷途径,同时也可带来超高性能。(下面列出了多种方法,您也可以结合使用不同的方法)

选项 1

Vitis DSP 库函数调用

dsplib::fft::dit1ch::fft_ifft_dit_1ch

- 简单易用

- 可参数化

- 极快的开发

选项 2

使用 AI 引擎 API 实现矢量化编程

aie::vector<int8_t, sizeTileA> A0

aie::vector<int8_t, sizeTileA> A1

- 可定制

- 加快开发

选项 3

带内部函数的矢量化编程

Acc0 = mac16(acc0, Bbuff, 0, 0x00000000, 8, 0x3120, Abuff0, 0, 0xCC884400, 2, 0x3210);

Acc0 = mac16(acc0, Bbuff, 32, 0x00000000, 8, 0x3120, Abuff0, 0, 0xCC884400, 2, 0x3210);

- 完全的低层次自定义

- 开发极其漫长

不同的 AI 引擎功能随后可使用计算图 C 代码进行互连,该代码是描述多个 AI 引擎单元的网络的 C++ 代码。

仿真和验证步骤

| 设计 | 仿真选项 |

| 仅 AI 引擎 | X86 仿真器(快速)和 AIE 仿真器(周期近似) |

| AI 引擎 + PL 子系统 (PL 使用 Vitis HLS 进行编码) |

使用 MATLAB 或 Python 进行 Vitis 功能仿真 |

| AI 引擎 + PL 子系统 (PL 使用 HDL 进行编码) |

使用 Vivado™ XSIM 通过 HDL 测试激励文件进行功能仿真 |

| AI 引擎 + PL + PS | 在 Vitis 中进行硬件仿真 使用 QEMU 进行 PS 仿真 使用 XSIM(HDL 测试激励文件)进行 PL 仿真 使用 AIE 仿真器 (SystemC) 进行 AIE 仿真 |

有关仿真流程的更多信息,请参阅:Versal 自适应 SoC 设计指南 (UG1273)

使用 Vitis Model Composer 基于模型的设计流程

此设计工具将开发流程引入 MathWorks MATLAB®/Simulink® 环境,让您可以在该环境中生成 Versal AI Engine 所需的内核、集成可编程逻辑模块以及进行系统仿真。

Vitis Model Composer 流程

使用 Vitis Model Composer,可在不同 AI 引擎功能之间实现图形互连。该图形表示可通过 Vitis Model Composer 将按钮转换成计算图 C 代码。还可利用 MathWorks Simulink 环境的强大仿真功能验证设计。

要了解有关使用 Vitis Model Composer 开发 Versal AI Engine 的更多信息,请访问使用 Vitis Model Composer 开发 Versal AI Engine 页面。

资源

操作视频

研讨会

文档

培训课程

立即体验

AI 引擎工具许可:编译器和仿真器

虽然 AI 引擎编译器和仿真器工具是 AMD Vitis™ 软件安装程序的一部分,但这些工具仍然需要免费许可才能使用。您可以从产品许可网站获取此许可证。

输入您的详细信息,然后选择“AI 引擎工具许可证”选项。

了解 Versal AI Engine 与传统可编程逻辑技术的基准测试结果对比情况

如需直接比较仅使用可编程逻辑设计与使用 AMD Versal 自适应 SoC 和 AI Engine 的新一代设计的基准测试结果,请联系销售或 FAE 以获取基准测试结果和源设计。

附注

- 基于 AMD 在 2024 年 2 月委托第三方进行的基准测试,比较了 AMD Versal 自适应 SoC(使用 Vitis AI 设计工具)与传统可编程逻辑(使用 Vivado 软件和 Vitis Model Composer Tool,2023.1 版)在实现信号处理应用 FIR 方面的性能表现。结果基于 3 种设计的平均分值。结果因设计规格而异。(VER-034)

- 基于 AMD 在 2024 年 2 月委托第三方进行的基准测试,比较了 AMD Versal 自适应 SoC(使用 Vitis AI 设计工具)与传统可编程逻辑(使用 Vivado 软件和 Vitis Model Composer Tool,2023.1 版)在实现信号处理应用 FIR 方面的性能表现。结果基于 3 种设计的平均分值。结果因设计规格而异。(VER-034)