AMD Versal™ AI Engine で DSP の演算能力を解き放つ

Versal AI エンジン テクノロジは、高性能なデジタル信号処理 (DSP) を実現します

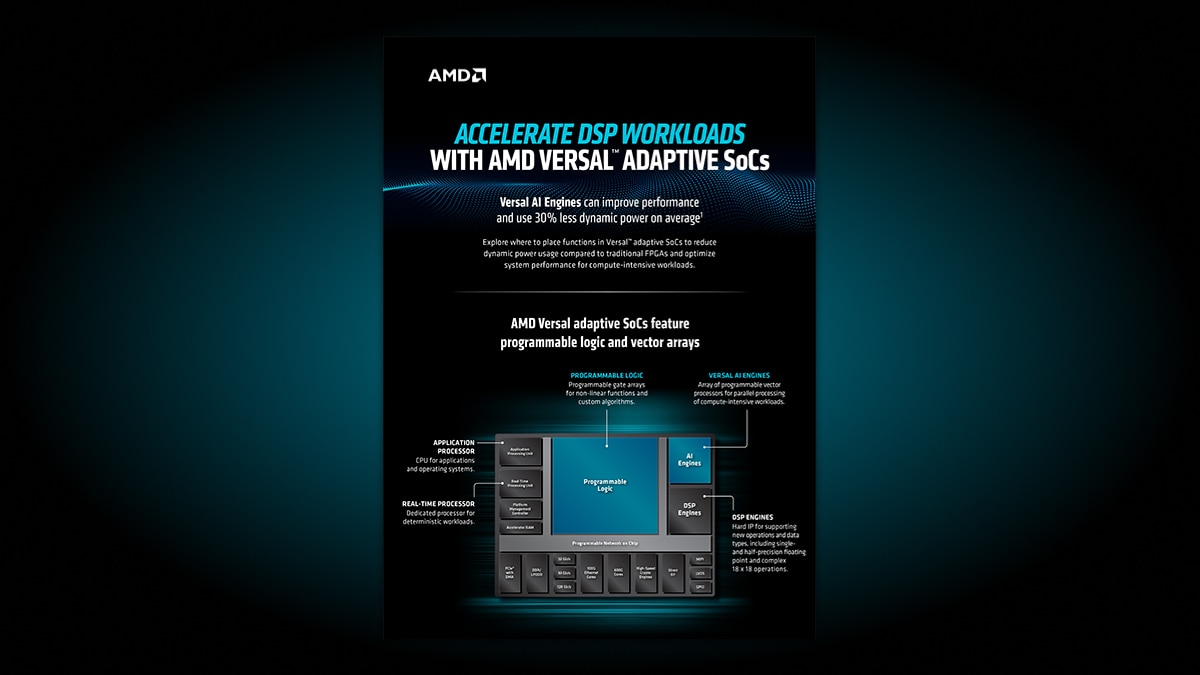

次世代 DSP アプリケーションの開発に取り組むお客様は膨大な演算能力を必要としますが、従来の FPGA アーキテクチャでは効率的に実装できるものではありません。FIR、FFT、GeMM などの高い演算処理能力を必要とする DSP アプリケーションは、大量の DSP ブロックとプログラマブル ロジック リソースを使用します。

こうしたアルゴリズムの複雑性により、従来型のプログラマブル ロジック デバイスで利用できる全体的な計算能力は大きく制約される可能性があります。使用できる DSP ブロックやプログラマブル ロジックの数を増やすだけでは、消費電力のバジェットが制限される負荷の高い DSP ワークロードに対するスケーラブルなソリューションとは言えません。Versal AI Engine は、このようなケースにおいてより効率的な演算ソリューションを提供するように設計されています。

解説動画ライブラリでは、設計開始に役立つ基本的な技術情報を提供します。

AI エンジン DSP デザイン プロセス

AMD Versal™ AI エンジンをターゲットとする高性能 DSP 機能の設計には、AMD Vitis™ 開発ツールを使用する方法と、MathWorks Simulink® ツールのシミュレーションやグラフィック機能を活用する Vitis Model Composer フローを使用する方法があります。

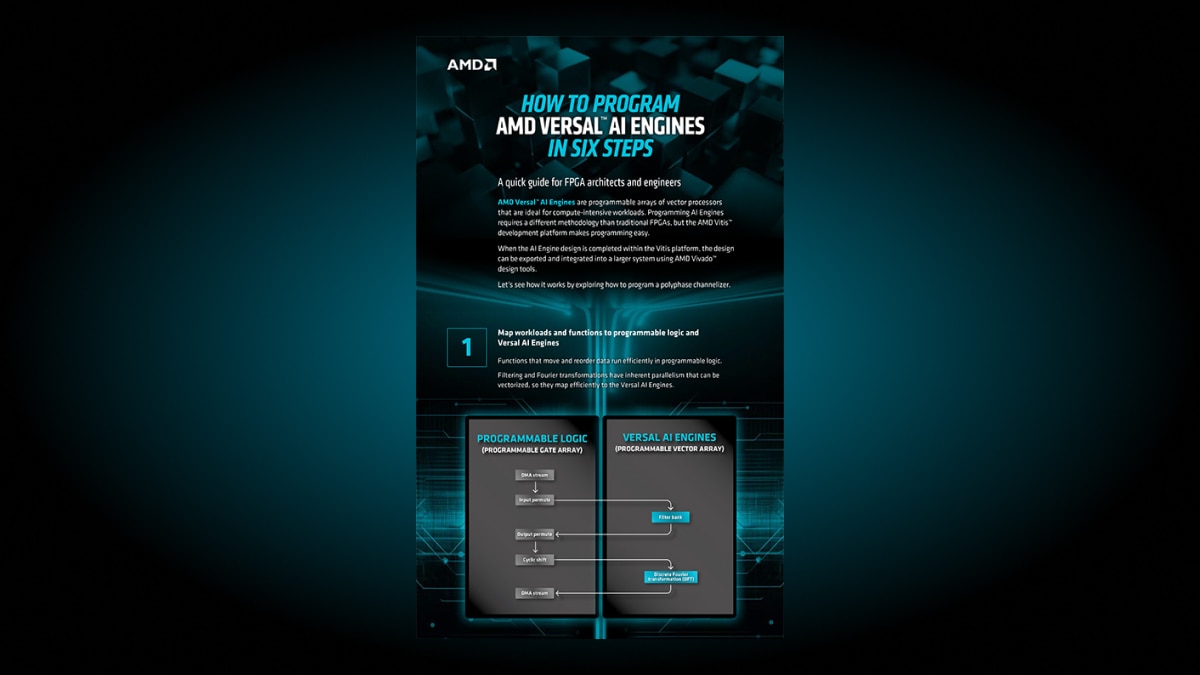

いずれの場合も、DSP アプリケーションを FPGA または AI エンジンで実行、あるいは FPGA ロジックと AI エンジンの組み合わせで実行するために、関数に適切に割り当てることが非常に重要です。この場合、システム全体だけでなく、各デバイスの能力も理解しておく必要があります。

一般的に、演算負荷の高い関数は AI エンジンに実装し、データの移動や再配置を目的とする関数は FPGA に実装します。

次の例で示すように、複雑なフィルタリングとフーリエ変換は、AI エンジン アレイに実装することが推奨されています。

関数が AI エンジンで効果的に実行できることが確認できると、次のオプションのいずれかを使用して AI エンジンに実装できます。

注記: 以下のオプションを複数組み合わせたハイブリッドなアプローチも可能です。

プログラミング環境

Vitis プラットフォームは、DSP ライブラリ、API、イントリンシクス関数を活用する 2 つのプログラミング環境を提供

- C/C++ で開発

- Vitis Model Composer を使用したモデルベースのフロー

C/C++ で開発

Vitis プラットフォームには、一般的な DSP アルゴリズムや関数、デバイス グラフ向けのオープンソースの構築ブロックが用意されています。これらをそのまま使用して迅速にテストを実行することも、用途に合わせてカスタマイズすることも可能です。

C/C++ フロー

DSP 向けの AI エンジン開発を開始する場合、Vitis DSP ライブラリ関数 (C ベース) の利用を推奨しています。手動コーディングは最適化の余地がありますが、次に示す方法を使うことで、高性能を維持しつつ、DSP 向けの AI エンジンを最速で適用できます。これらのオプションを複数組み合わせたハイブリッドなアプローチも可能です。

オプション 1

Vitis DSP ライブラリ関数呼び出し

dsplib::fft::dit1ch::fft_ifft_dit_1ch

- 最も簡単に使用できる

- パラメーター指定可能

- 最も速く開発できる

オプション 2

AI エンジンの API を使用したベクトル化プログラミング

aie::vector<int8_t, sizeTileA> A0

aie::vector<int8_t, sizeTileA> A1

- カスタマイズ可能

- より速く開発できる

オプション 3

イントリンシクスを使用したベクトル化プログラミング

Acc0 = mac16(acc0, Bbuff, 0, 0x00000000, 8, 0x3120, Abuff0, 0, 0xCC884400, 2, 0x3210);

Acc0 = mac16(acc0, Bbuff, 32, 0x00000000, 8, 0x3120, Abuff0, 0, 0xCC884400, 2, 0x3210);

- 低レベルでの完全なカスタマイズが可能

- 開発に最も時間がかかる

その後、異なる AI エンジン関数を連携させるため、graph C コードという C++ コードを記述して、複数の AI エンジン タイルからなるネットワークを構築します。

シミュレーションおよび検証の手順

| デザイン | シミュレーション オプション |

| AI エンジンのみ | x86 シミュレータ (高速) および AIE シミュレータ (サイクル近似) |

| AI エンジン + PL サブシステム (PL を Vitis HLS でコーディング) |

MATLAB または Python を用いた Vitis 機能シミュレーション |

| AI エンジン + PL サブシステム (PL を HDL でコーディング) |

HDL テストベンチを用いた Vivado™ XSIM 機能シミュレーション |

| AI エンジン + PL + PS | Vitis でのハードウェア エミュレーション PS: QEMU を使用してシミュレーション PL: XSIM (HDL テスト ベンチ) を使用してシミュレーション AIE: AIE シミュレータ (SystemC) を使用してシミュレーション |

シミュレーション フローの詳細は、Versal アダプティブ SoC デザイン ガイド (UG1273) を参照してください。

Vitis Model Composer を使用したモデルベースのフロー

Vitis Model Composer を使用すると、MathWorks の MATLAB®/Simulink® 環境上で開発が可能になり、Versal AI エンジン用のカーネル生成、プログラマブル ロジックとの統合、システム シミュレーションを実行できます。

Vitis Model Composer フロー

Vitis Model Composer を使用すれば、異なる AI エンジンの関数をグラフィカルに接続できます。Vitis Model Composer ではこのグラフィック表示をボタン操作でグラフ C コードに変換できます。デザインの検証には、MathWorks Simulink 環境のシミュレーション機能を利用することも可能です。

Vitis Model Composer を使用した Versal AI Engine 開発の詳細は、Vitis Model Composer を使用する Versal AI Engine 開発のページを参照してください。

リソース

解説動画

ウェビナー

資料

トレーニング コース

開発を開始

AI エンジン ツールのライセンス取得: コンパイラとシミュレータ

AI エンジン コンパイラおよびシミュレータ ツールは、AMD Vitis™ ソフトウェア インストーラーに含まれていますが、これらのツールを使用するにはライセンス (無償) が必要です。ライセンスは、製品のライセンス取得ページから取得可能です。

詳細を入力して [AI Engine Tools License] オプションを選択してください。

Versal AI Engine と従来のプログラマブル ロジック テクノロジを比較したベンチマークへのアクセス

AMD Versal アダプティブ SoC を使用した、プログラマブル ロジックのみのデザインとアダプティブ SoC + AI エンジン デザインのベンチマークの直接比較をご希望の場合は、ベンチマーク結果とソース デザインについて、営業担当者または FAE にお問い合わせください。

脚注

- 2024 年 2 月に AMD が委託したサードパーティによるベンチマーク テストに基づいています。信号処理アプリケーションにおける FIR 実装で、AI 設計ツール用の Vitis を使用した AMD Versal アダプティブ SoC と、Vivado ソフトウェアおよび Vitis Model Composer (バージョン 2023.1) を使用した従来のプログラマブル ロジックを比較しています。結果は 3 つのデザインの平均値であり、設計仕様によって異なります。(VER-034)

- 2024 年 2 月に AMD が委託したサードパーティによるベンチマーク テストに基づいています。信号処理アプリケーションにおける FIR 実装で、AI 設計ツール用の Vitis を使用した AMD Versal アダプティブ SoC と、Vivado ソフトウェアおよび Vitis Model Composer (バージョン 2023.1) を使用した従来のプログラマブル ロジックを比較しています。結果は 3 つのデザインの平均値であり、設計仕様によって異なります。(VER-034)