使用 AMD Versal™ AI Engine 釋放 DSP 運算能力

Versal AI Engine 技術能滿足高效能數位訊號處理 (DSP)。

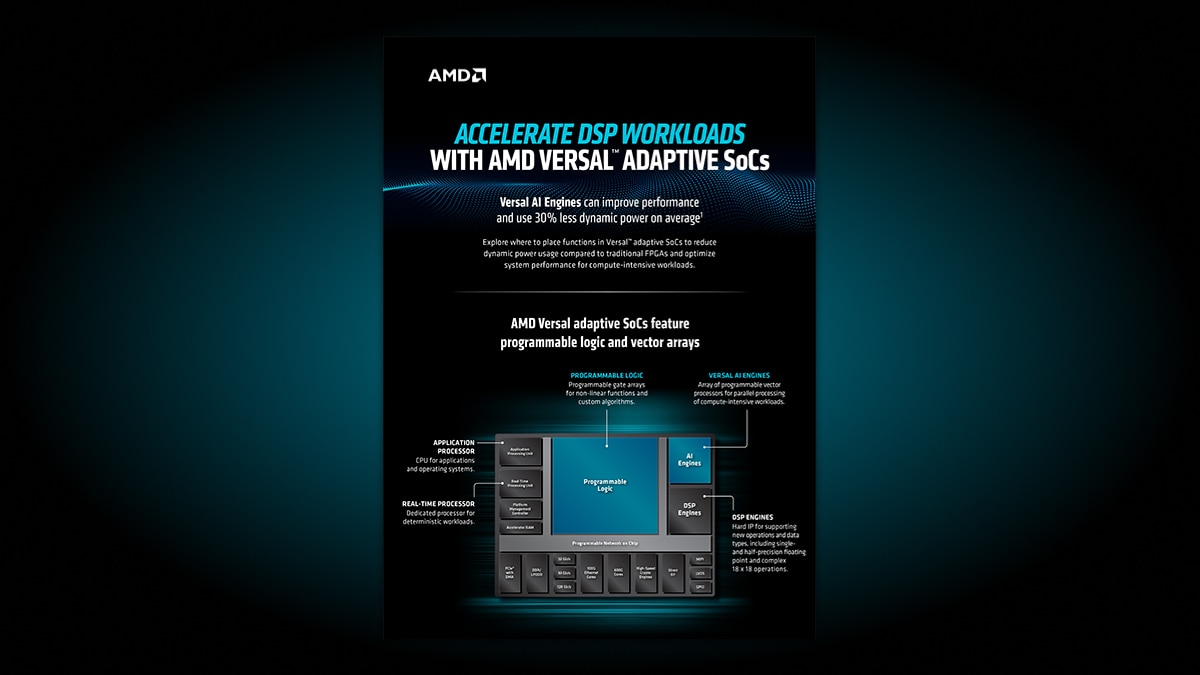

使用新一代 DSP 應用程式的客戶需要非常強大的運算能力,但這種能力卻無法透過傳統 FPGA 架構有效實現。運算密集型的 DSP 應用,例如 FIR、FFT 和一般矩陣乘法,有可能會占用大量的 DSP 區塊和可程式化邏輯資源。

這般的演算法複雜度會大幅降低傳統可程式化邏輯裝置上的整體運算量能。對於電力預算吃緊的密集型 DSP 工作負載而言,單純增加 DSP 區塊與可程式化邏輯,並非能夠大規模運用的解決之道。Versal AI Engine 的設計可在這些情況下提供更有效率的運算解決方案。

我們的指南影片庫提供基本的技術資訊,可協助您迅速上手。

AI 引擎 DSP 設計流程

您可以使用 AMD Vitis™ 開發工具,或使用 Vitis Model Composer 流程來設計目標為 AMD Versal™ AI 引擎的高效能 DSP 功能,藉此善用 MathWorks Simulink® 工具的模擬與圖形功能。

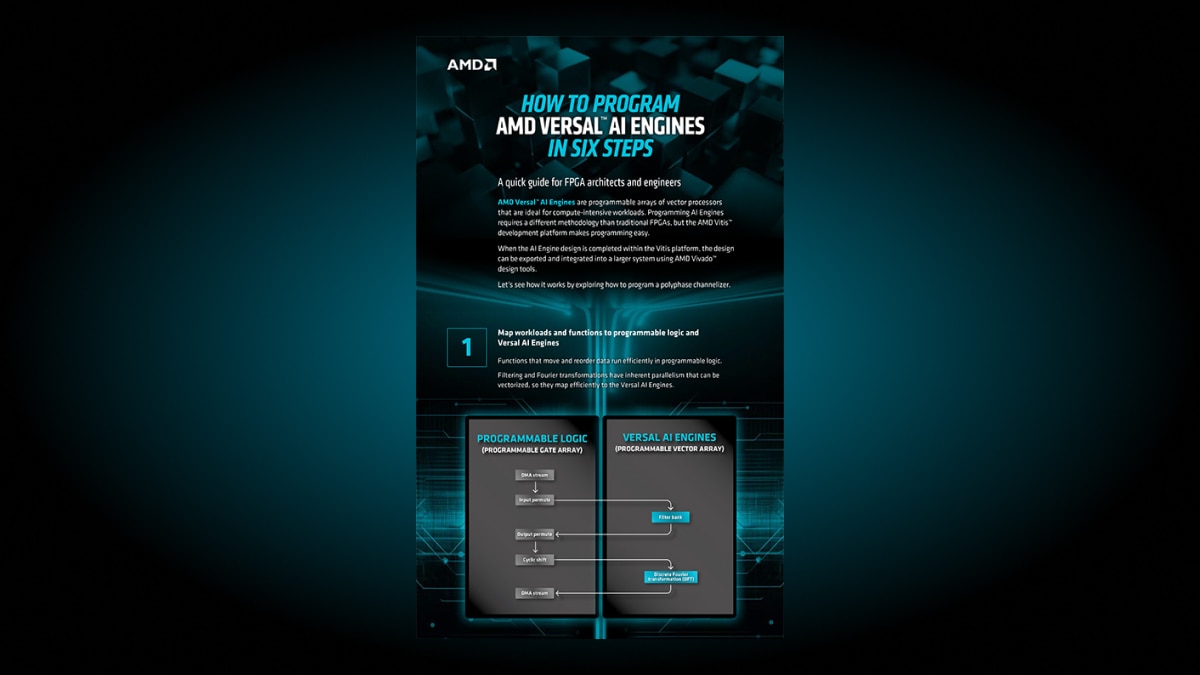

無論採用何種方式,重要的是將 DSP 應用對映至函數,然後實作於現場可程式化閘陣列 (Field Programmable Gate Array, FPGA)、AI 引擎,或 FPGA 邏輯加上 AI 引擎。這需要對於器件功能及整體系統,有相當程度的瞭解。

通常而言,運算密集型函數較適合在 AI 引擎上實作,至於需要移動/重新排序資料的函數,較適合在 FPGA 上實作。

從下方所示範例可見,複雜的過濾和傅立葉變換,通常更適合用於 AI 引擎陣列。

一旦清楚確定函數適合 AI 引擎,就可以使用以下任一選項,將其實作至 AI 引擎中。

附註:也可以從下表中挑選不只一個選項,採用混合式方法進行。

程式設計環境

Vitis 平台為 DSP 程式庫、API 和內在函數之運用,提供兩種程式設計環境

- 以 C/C++ 建置

- 採用 Vitis 模型編輯器之以模型為基礎的流程

以 C/C++ 建置

Vitis 平台擁有開放原始碼建構模塊,適用於常見的 DSP 演算法、函數和裝置圖。您可以為了快速測試,而照原樣使用這些建構模塊,或是根據您的需求加以客製化。

C/C++ 流程

若打算用 AI 引擎設計 DSP,強烈建議從 Vitis DSP 程式庫函數(以 C 語言為基礎)著手。雖然手動編碼可實現更接近理想的實作成果,但採用下述方法卻是使用 AI 引擎設計 DSP 的最快方式,同時還能提供強大效能。(也可以從下表中挑選不只一個選項,採用混合式方法進行)

選項 1

Vitis DSP 程式庫函數呼叫

dsplib::fft::dit1ch::fft_ifft_dit_1ch

- 使用最簡單

- 可以參數化

- 開發最快速

選項 2

使用 AI 引擎 API 進行向量化程式設計

aie::vector<int8_t, sizeTileA> A0

aie::vector<int8_t, sizeTileA> A1

- 可以客製化

- 開發較快速

選項 3

使用內在函數進行向量化程式設計

Acc0 = mac16(acc0, Bbuff, 0, 0x00000000, 8, 0x3120, Abuff0, 0, 0xCC884400, 2, 0x3210);

Acc0 = mac16(acc0, Bbuff, 32, 0x00000000, 8, 0x3120, Abuff0, 0, 0xCC884400, 2, 0x3210);

- 全面低階客製化

- 開發時間最長

接著就可以透過以 C++ 語言編寫的 Graph C 程式碼,描述多個 AI 引擎磚之間的網路關係,將不同的 AI 引擎函數互連在一起。

模擬與驗證步驟

| 設計 | 模擬選項 |

| 僅限 AI Engine | X86 模擬器(快速)與 AIE 模擬器(週期近似) |

| AI Engine + PL 子系統 (以 Vitis HLS 編碼的 PL) |

使用 MATLAB 或 Python 的 Vitis 功能模擬 |

| AI Engine + PL 子系統 (以 HDL 編碼的 PL) |

使用 Vivado™ XSIM 的 HDL 測試平台功能模擬 |

| AI Engine + PL + PS | Vitis 中的硬體模擬 PS 使用 QEMU 進行模擬 PL 使用 XSIM(HDL 測試平台)進行模擬 AIE 使用 AIE 模擬器 (SystemC) 進行模擬 |

如需模擬流程的詳細資訊,請參閱:Versal 自適應 SoC 設計指南 (UG1273)

採用 Vitis 模型編輯器之以模型為基礎的流程

編輯器可將開發工作導入 MathWorks MATLAB®/Simulink® 環境,讓您在其中產生 Versal AI Engine 內核、整合可程式化邏輯模組,以及模擬系統。

Vitis 模型編輯器流程

使用 Vitis 模型編輯器,則可透過圖形化的方式,互連不同的 AI 引擎函數。這種圖形化表示形式,能夠透過 Vitis 模型編輯器,一鍵轉換為 Graph C 程式碼。MathWorks Simulink 環境的強大模擬功能,亦可在設計驗證上發揮功用。

若要瞭解更多有關使用 Vitis 模型編輯器開發 Versal AI Engine 的資訊,請造訪使用 Vitis 模型編輯器開發 Versal AI Engine 頁面。

資源

指南影片

網路研討會

說明文件

訓練課程

開始

授權 AI 引擎工具:編譯器和模擬器

AMD Vitis™ 軟體安裝工具中,雖然有 AI 引擎編譯器和模擬器工具,但這些工具仍需取得免費授權才可使用。您可以從產品授權網站取得授權。

請輸入您的詳細資料,然後選擇「AI 引擎工具授權」此一選項。

取得基準測試,將 Versal AI Engine 與先前可程式化邏輯技術進行比較

如需純可程式化邏輯設計與使用 AMD Versal 自適應 SoC 的自適應 SoC + AI Engine 設計之直接基準測試比較,請與銷售人員或您的 FAE 聯絡,以取得基準測試結果與來源設計。

尾註

- 根據 AMD 在 2024 年 2 月委託第三方進行的基準測試。以採用 Vitis for AI 設計工具的 AMD Versal 自適應 SoC,與採用 Vivado 軟體及 Vitis Model Composer Tool 2023.1 版的傳統可程式化邏輯進行比較,測試項目為訊號處理應用程式 FIR 實作。結果為 3 個設計的平均值。結果可能會因設計規格而有所不同。(VER-034)

- 根據 AMD 在 2024 年 2 月委託第三方進行的基準測試。以採用 Vitis for AI 設計工具的 AMD Versal 自適應 SoC,與採用 Vivado 軟體及 Vitis Model Composer Tool 2023.1 版的傳統可程式化邏輯進行比較,測試項目為訊號處理應用程式 FIR 實作。結果為 3 個設計的平均值。結果可能會因設計規格而有所不同。(VER-034)