AMD Versal™ AI Engine으로 강력한 DSP 컴퓨팅 성능 발휘

Versal AI Engine 기술로 고성능 DSP(Digital Signal Processing) 구현

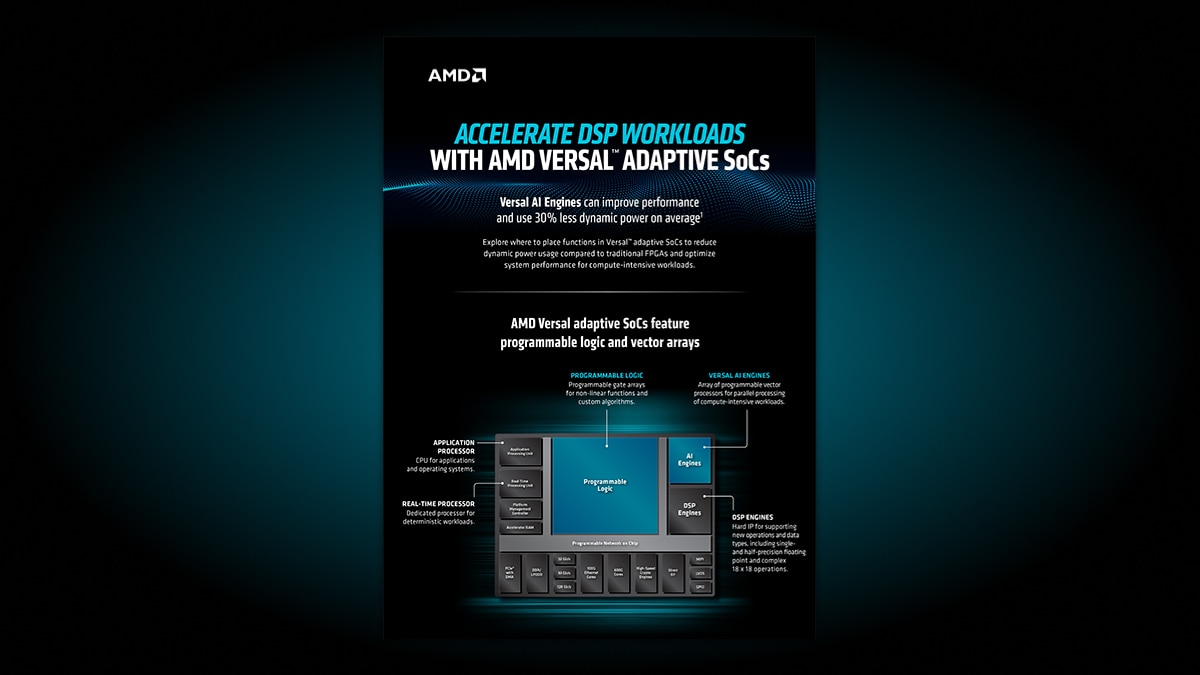

차세대 DSP 애플리케이션을 사용하는 고객에게는 기존 FPGA 아키텍처에서는 효율적으로 구현할 수 없는 엄청난 컴퓨팅 기능이 필요합니다. FIR, FFT, General Matrix Multiply와 같은 컴퓨팅 집약적 DSP 애플리케이션은 상당한 양의 DSP 블록과 프로그래밍 가능한 로직 리소스를 사용할 수 있습니다.

이와 같은 알고리즘 복잡성으로 인해 기존의 프로그래밍 가능 로직 디바이스에서 사용할 수 있는 전체 컴퓨팅 용량이 크게 감소할 수 있습니다. 단순히 DSP 블록과 프로그래밍 가능한 로직을 늘리는 방안은 전력 예산이 엄격하고 강도가 높은 DSP 워크로드를 위해 확장 가능한 솔루션이 아닙니다. Versal AI Engine은 이러한 경우에 보다 효율적인 컴퓨팅 솔루션을 제공하도록 설계되었습니다.

사용 방법 동영상 라이브러리는 시작하는 데 필요한 필수 기술 정보를 제공합니다.

AI Engine DSP 설계 흐름

AMD Versal™ AI Engine을 대상으로 하는 고성능 DSP 기능을 설계하려면 AMD Vitis™ 개발 도구 또는 Vitis Model Composer 흐름을 사용하여 MathWorks Simulink® 도구의 시뮬레이션 및 그래픽 기능을 활용해야 합니다.

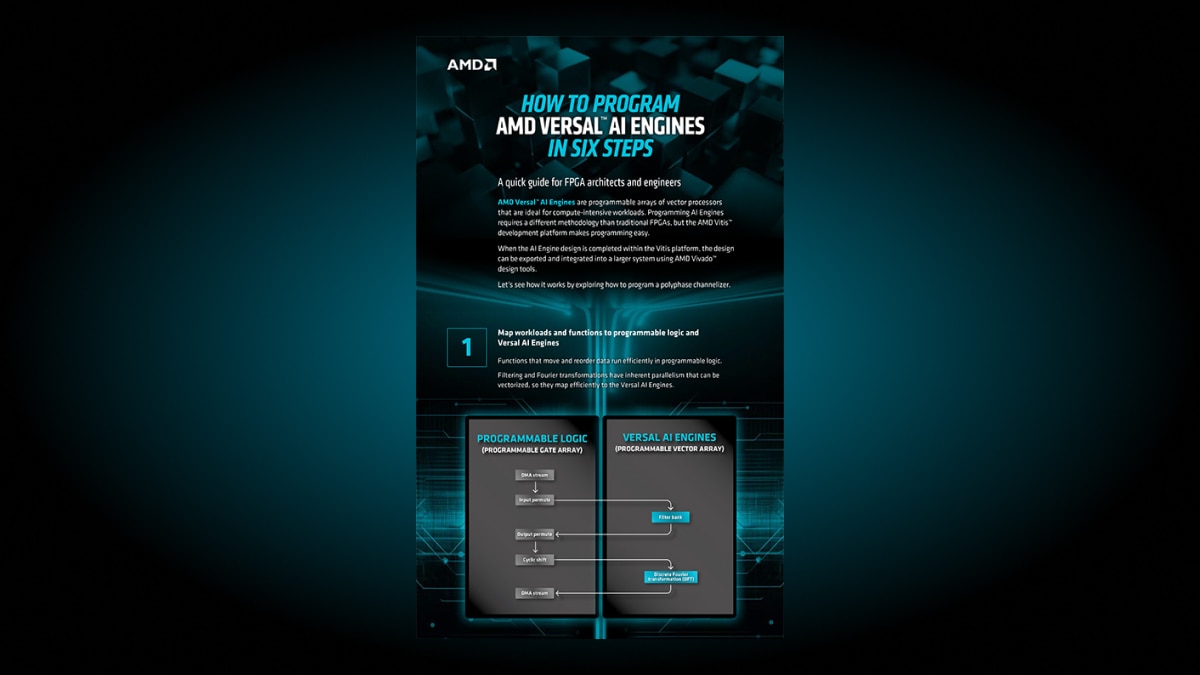

두 경우 모두 DSP 애플리케이션을 FPGA 또는 AI 엔진에서 구현할 기능에 매핑하거나 FPGA 로직과 AI 엔진을 조합하는 것이 중요합니다. 이를 위해서는 전체 시스템뿐만 아니라 디바이스 기능에 대한 이해가 필요합니다.

일반적으로 컴퓨팅 집약적인 기능은 AI 엔진 구현에 더 적합하고, 데이터 이동/재정렬이 필요한 기능은 FPGA 구현에 더 적합합니다.

아래에 나와 있는 예시에서는 복잡한 필터링과 푸리에 변환이 일반적으로 AI 엔진 어레이 내에서 더 적합합니다.

기능이 AI 엔진에 적합한 것으로 명확하게 식별되면 아래 옵션 중 하나를 사용하여 해당 기능을 AI 엔진에 구현할 수 있습니다.

참고: 아래 목록의 여러 옵션을 사용하는 하이브리드 접근 방식도 가능합니다.

프로그래밍 환경

Vitis 플랫폼은 DSP 라이브러리, API, 내장 함수를 활용하는 두 가지 프로그래밍 환경 제공

- C/C++에서 빌드

- Vitis 모델 컴포저를 통한 모델 기반 흐름

C/C++에서 빌드

Vitis 플랫폼은 일반적인 DSP 알고리즘, 함수, 디바이스 그래프를 위한 오픈 소스 빌딩 블록을 갖추고 있습니다. 신속한 테스트를 위해 있는 그대로 사용하거나 필요에 맞게 사용자 지정할 수 있습니다.

C/C++ 흐름

AI 엔진을 DSP에 적용하기 위해 시작하려면 Vitis DSP 라이브러리 함수(C 기반)부터 시작하는 것을 강력히 권장합니다. 수동 코딩을 사용하면 더 최적화된 구현이 가능하지만, 아래 방법을 사용하면 DSP용 AI 엔진을 가장 빠르게 시작하면서 우수한 성능을 제공할 수 있습니다. (아래 목록의 여러 옵션을 사용하는 하이브리드 접근 방식도 가능)

옵션 1

Vitis DSP 라이브러리 함수 호출

dsplib::fft::dit1ch::fft_ifft_dit_1ch

- 가장 간편한 사용

- 파라미터화 가능

- 가장 빠른 개발

옵션 2

AI 엔진 API를 사용하는 벡터화된 프로그래밍

aie::vector<int8_t, sizeTileA> A0

aie::vector<int8_t, sizeTileA> A1

- 커스텀 가능

- 더 빠른 개발

옵션 3

내장 함수를 사용하는 벡터화된 프로그래밍

Acc0 = mac16(acc0, Bbuff, 0, 0x00000000, 8, 0x3120, Abuff0, 0, 0xCC884400, 2, 0x3210);

Acc0 = mac16(acc0, Bbuff, 32, 0x00000000, 8, 0x3120, Abuff0, 0, 0xCC884400, 2, 0x3210);

- 전체, 저수준 맞춤화

- 가장 오래 지속되는 개발

그러면 다양한 AI 엔진 함수가 그래프 C 코드를 사용하여 상호 연결됩니다. 그래프 C 코드는 여러 AI 엔진 타일의 네트워크를 설명하는 C++ 코드입니다.

시뮬레이션 및 검증 단계

| 디자인 | 시뮬레이션 옵션 |

| AI 엔진 전용 | x86 시뮬레이터(고속) 및 AIE 시뮬레이터(주기 근사치) |

| AI 엔진 + PL 하위 시스템 (Vitis HLS를 사용하여 PL 코딩됨) |

MATLAB 또는 Python을 사용한 Vitis 기능 시뮬레이션 |

| AI 엔진 + PL 하위 시스템 (HDL을 사용하여 PL 코딩됨) |

Vivado™ XSIM을 사용한 HDL 테스트 벤치의 기능 시뮬레이션 |

| AI 엔진 + PL + PS | Vitis의 하드웨어 에뮬레이션 QEMU를 사용하여 시뮬레이션된 PS XSIM(HDL 테스트 벤치)을 사용한 PL 시뮬레이션 AIE 시뮬레이터(시스템 C)를 사용하여 시뮬레이션된 AIE |

시뮬레이션 흐름에 대한 자세한 내용은 다음을 참조하세요. Versal Adaptive SoC 설계 가이드(UG1273)

Vitis 모델 컴포저를 통한 모델 기반 흐름

이 컴포저는 MathWorks MATLAB®/Simulink® 환경에 개발 기능을 도입하여 Versal AI Engine용 커널을 생성하고 프로그래밍 가능 로직 모듈을 통합하며 시스템을 시뮬레이션할 수 있습니다.

Vitis 모델 컴포저 흐름

Vitis 모델 컴포저를 사용하면 다양한 AI 엔진 함수 간의 그래픽 상호 연결이 가능합니다. 이 그래픽 표현은 Vitis 모델 컴포저를 통해 푸시 버튼을 그래프 C 코드로 변환할 수 있습니다. MathWorks Simulink 환경의 강력한 시뮬레이션 기능을 활용하여 설계를 검증할 수도 있습니다.

Vitis 모델 컴포저를 사용하는 Versal AI Engine 개발에 대해 자세히 알아보려면 Vitis 모델 컴포저를 사용하는 Versal AI Engine 개발 페이지를 참조하세요.

리소스

사용 방법 동영상

웨비나

문서

교육 과정

시작하기

AI 엔진 도구 라이선스: 컴파일러 및 시뮬레이터

AI 엔진 컴파일러 및 시뮬레이터 도구는 AMD Vitis™ 소프트웨어 설치 프로그램의 일부이지만, 이러한 도구를 사용하려면 무료 라이선스가 필요합니다. 이 라이선스는 제품 라이선스 사이트에서 얻을 수 있습니다.

세부 정보를 입력하고 "AI Engine Tools License(AI 엔진 도구 라이선스)" 옵션을 선택하세요.

Versal AI Engine과 기존의 프로그래밍 가능한 로직 기술을 비교한 벤치마크 액세스

AMD Versal Adaptive SoC를 사용하는 프로그래밍 가능 로직 전용 설계와 Adaptive SoC + AI Engine 설계의 일대일 벤치마크 비교에 대해서는 영업 담당자 또는 FAE에 벤치마크 결과 및 소스 설계에 대해 문의하세요.

각주

- 2024년 2월 AMD가 의뢰한 타사 벤치마크 테스트를 기반으로, 신호 처리 애플리케이션 FIR 구현에서 Vivado 소프트웨어 및 Vitis Model Composer Tool, 버전 2023.1을 사용한 기존 프로그래밍 가능 로직과 AI 설계 도구용 Vitis를 탑재한 AMD Versal Adaptive SoC를 비교한 결과입니다. 결과는 3가지 이상의 설계의 평균입니다. 결과는 설계 사양에 따라 달라질 수 있습니다. (VER-034)

- 2024년 2월 AMD가 의뢰한 타사 벤치마크 테스트를 기반으로, 신호 처리 애플리케이션 FIR 구현에서 Vivado 소프트웨어 및 Vitis Model Composer Tool, 버전 2023.1을 사용한 기존 프로그래밍 가능 로직과 AI 설계 도구용 Vitis를 탑재한 AMD Versal Adaptive SoC를 비교한 결과입니다. 결과는 3가지 이상의 설계의 평균입니다. 결과는 설계 사양에 따라 달라질 수 있습니다. (VER-034)