Vitis エンベデッド

Vitis エンベデッド

Vitis™ エンベデッドは、エンベデッド Arm プロセッサ上で実行されるホスト アプリケーションを開発するためのスタンドアロンのエンベデッド ソフトウェア開発パッケージです。

2025.2 リリースが利用可能に

AMD Vitis™ ソフトウェア プラットフォームは、FPGA ファブリック、Arm® プロセッサ、および AI エンジンを対象とした設計のための開発環境です。AMD Vivado™ Design Suite と連携して動作し、より高い抽象度の開発環境を提供します。

Vitis ソフトウェアには、Arm プロセッサ上で C/C++ アプリケーションを開発するための Vitis Embedded、AI エンジン向けのコンパイラおよびシミュレータ、C/C++ ベースで FPGA IP を開発するための Vitis HLS、Simulink® 上でモデルベース設計を行うための Vitis Model Composer が含まれています。さらに、FPGA または AI エンジンでの実装向けに最適化された DSP、Vision、Solver、Ultrasound、BLAS などの高性能ライブラリも提供されています。

Vitis 統合ヘテロジニアス システム フローを使用したエンベデッド システム ソリューションの作成方法を説明します。

(従来の FPGA ファミリではエンベデッド SDK と呼称)

AMD アダプティブ SoC の Arm® エンベデッド プロセッサ サブシステムの C/C++ コード開発は、通常次のフローで行われます。

開発者は、Vitis エンベデッド ソフトウェア内でシステム レベルのすべての検証を実行して、アプリケーションを起動するためのブート イメージを生成できます。

(ハードウェアおよびソフトウェア)

通常、システム設計者が AMD のアダプティブ SoC 内でソフトウェアとハードウェアを統合する場合、このフローを使用します。

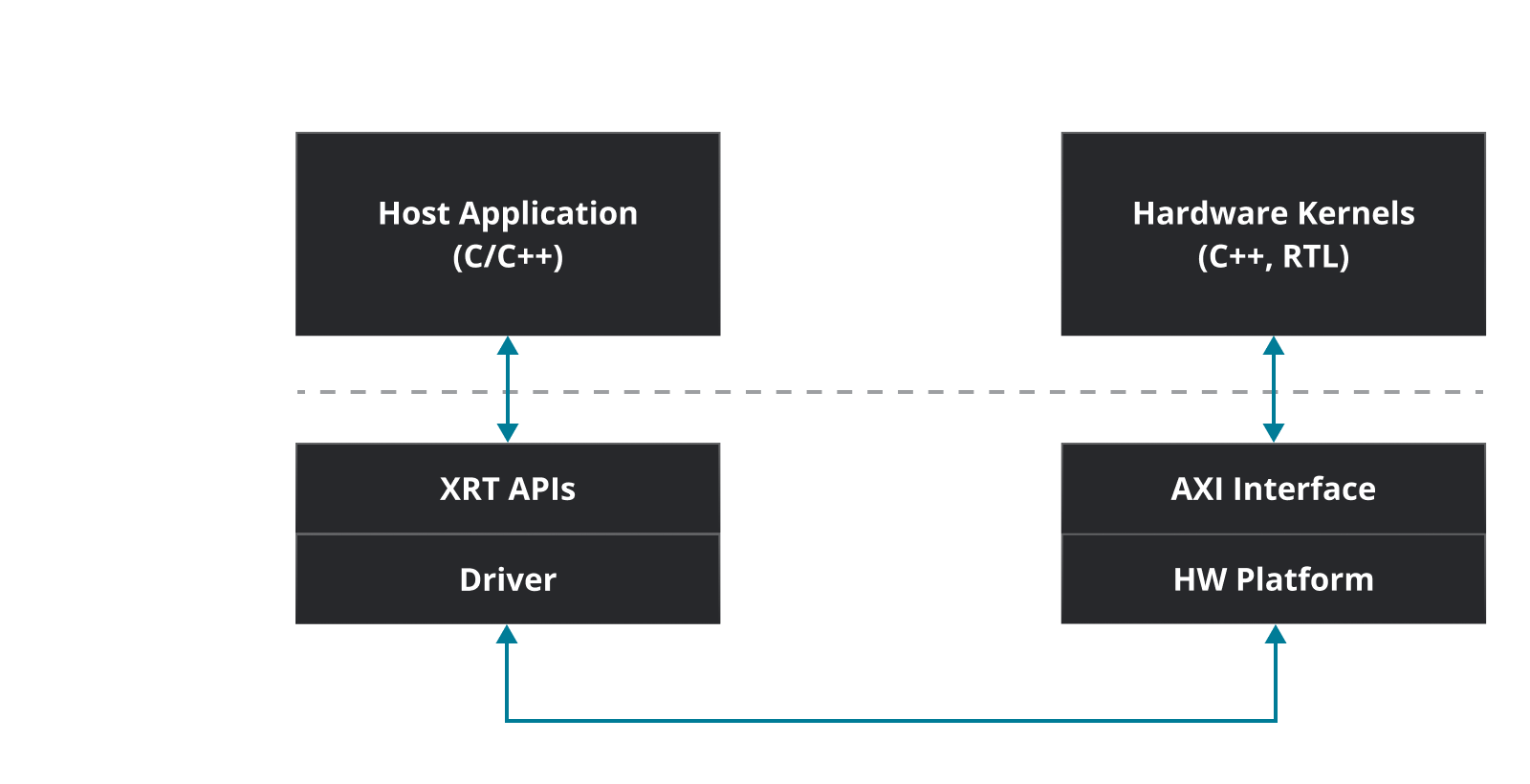

このフローは、Arm® エンベデッド プロセッサ上で動作するソフトウェア アプリケーションと、プログラマブル ロジック (PL) および/または Versal™ AI エンジン アレイ上で動作するコンピュート カーネルで構成されるヘテロジニアス エンベデッド システムの設計開発に使用されます。

このフローの内容:

AMD Alveo™ データセンター アクセラレータ カードを使用する場合、同じシステム設計フローを使用します。ソフトウェア プログラムは x86 ホスト上で実行され、カーネルは PCIe® で接続されたアクセラレーション カードの FPGA で実行されます。

使い慣れたツールでシミュレーション

• 既存の MATLAB®、Python™、C++、または HDL テストベンチを使用

• テストベンチの書き換えや新しいワークフローを学ぶ必要がない

• アルゴリズムからハードウェア実装までの反復開発を高速化

AI エンジン + PL の統合シミュレーション (Vitis サブシステム)

• AI エンジンと PL を同時にシミュレーション

• 分断されていたフローを、一貫した単一の手法に統合

• 統合時の問題を早期に検出

HIL (Hardware-in-the-Loop) 検証

• システム レベルの検証時間を短縮

• 実際の I/O をシリコン経由でストリーム処理し、デバッグを高速化

• 最終ハードウェア完成前にエンドツーエンドのスループットを検証