- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

- 2020.2

- 2020.1

AMD Vitis™ ソフトウェア プラットフォーム 2025.2 リリースのハイライト

Versal™ AI エンジンを使用した設計フローを強化

- Versal AI エッジおよび Versal AI エッジ シリーズ Gen 2 (AIE-ML/AIE-ML v2) 向けの AI エンジン API が強化

- 新規および強化されたデータ型

- 新規: ブロック浮動小数点 MX6

- 新規: ブロック浮動小数点 MX4

- 新規: cbfloat16 (エミュレーション)

- 強化: cfloat & cbfloat16 (FFT および行列乗算関数で利用可能)

- 強化: cint16 & cint32 (FFT で cint16 のツイドル係数を使用できるようになった)

- 新規および強化されたデータ型

- プログラミング モデルを更新

- 読み取り専用の共有バッファーを作成可能

- MEM タイルを複数回読み出し可能 (AIE-ML/AIE-ML v2)

- AIE-ML および AIE-ML v2 で DMA-FIFO をサポート

- Ping-pong バッファーを隣接する 2 つの MEM タイルにまたがって配置可能

(AIE-ML & AIE-ML v2) - ローカル タイル メモリ間でパラメーター共有が可能

- パケット スイッチング機能を強化 (AIE-ML および AIE-ML v2 対応)

- Versal AI エンジン向けの新規および強化された DSP ライブラリ関数

- 新しい Cumulative Sum (累積和)

- 新しい Euclidean Distance (ユークリッド距離)

- 新しい Function Approximation (RTP 更新または LUT による呼び出しで実行)

- パケット スイッチングに対応する強化された TDM FIR (PLIO を節約)

- AI エンジンと PL を使用する強化された 1D FFT (必要な PL リソースを削減)

- FIR が強化 (スループットを最適化)

- AI エンジンのマッピングとルーティング機能を強化 - コンパイラが複数のフットプリント/レイアウトを自動探索できるため、より効率的な実装を実現

Versal AI エンジン デザインの検証が容易

- C++ 対応の Vitis Functional Simulation ワークフロー (アーリー アクセス)

- MATLAB® および Python テストベンチを活用した Hardware-in-the-Loop 検証 (アーリー アクセス)

AI エンジン DSP デザイン向け Vitis Model Composer の機能強化

- AI エンジンを使用した SSR (Super Sample Rate) デザイン フローの使いやすさを改善 (アーリー アクセス)

- AIE および HDL の両方で利用できるブロックが追加:

- AIE、AIE-ML、AIE-ML v2

- 新規: Function Approximation (関数近似)

- 新規: Correlation/Convolution (相関/たたみ込み)

- 新規: Cumulative Sum (累積和)

- HDL ライブラリ ブロック

- 強化: FFT (ネイティブ浮動小数点 SSR = 32、64 に対応)

- 強化: FIR (SSR を用いたフラクショナル レート補間に対応)

- AIE、AIE-ML、AIE-ML v2

エンベデッド開発向け Vitis IDE のアップデート

- Python™ API によるビルド構成の更新に対応

- Python 環境で Vitis™ API を実行可能

- 対応コアでは PS トレースがデフォルトで表示される

- デバッグ機能の強化 — Watch View と Register View で更新された値がハイライト表示される

- バックエンド タスクのキャンセル/終了

- Linux/Windows 間で BSP ファイル パスを統一

- Theia AI 統合 (アーリー アクセス) - 任意の LLM/コード アシスタントを利用できるようになる

- Python API による DFX Platform の作成

- ワークスペースのバックアップ/共有

- コンフィギュレーション ファイルのログ機能を強化

- 新しい「Integration Project」コンポーネント

Vitis 最新情報 (カテゴリ別)

次の各セクションを展開して AMD Vitis 2025.2 の新機能と拡張機能の詳細を確認してください。サポートされているプラットフォーム、動作の変更、既知の問題については、Vitis ソフトウェア プラットフォーム 2025.2 リリース ノートのアプリケーション アクセラレーション フローおよびエンベデッド ソフトウェア開発フローを参照してください。

強化された DSP ライブラリ関数

- 新しい Cumulative Sum (累積和)

- 新しい Euclidean Distance (ユークリッド距離)

- 新しい Function Approximation (RTP 更新または LUT による呼び出しで実行)

- パケット スイッチングに対応する強化された TDM FIR (PLIO を節約)

- AIE と PL を使用する強化された 1D FFT (必要な PL リソースを削減)

- FIR が強化 (スループットを最適化)

該当製品:

- Versal™ AI コア (AIE 搭載)

- Versal AI エッジ (AIE-ML 搭載)

- Versal AI エッジ シリーズ Gen 2 (AIE-ML v2 搭載)

- Vitis サブシステムの論理シミュレーションを C++ で実行可能 (アーリー アクセス)

- Vitis Analyzer による、AI エンジン デザインのレイテンシおよびスループット測定機能が強化

- 各 AIE パーティションを実行中に個別制御

- AI エンジンを使用した SSR (Super Sample Rate) デザイン フローの使いやすさを改善 (アーリー アクセス)

- AIE および HDL の両方で利用できるブロックが追加

- AIE、AIE-ML、AIE-ML v2

- 新規: Function Approximation (関数近似)

- 新規: Correlation/Convolution (相関/たたみ込み)

- 新規: Cumulative Sum (累積和)

- HDL ライブラリ ブロック

- 強化: FFT (ネイティブ浮動小数点 SSR = 32、64 に対応)

- 強化: FIR (SSR を用いたフラクショナル レート補間に対応)

- パフォーマンス プラグマの強化

- パフォーマンス プラグマが、CSIM で算出されたトリップカウントに基づいて最適化される

- パフォーマンス プラグマの最適化は、コンフィギュレーション ファイル内のディレクティブに変換可能

- プラグマの条件付き制御 (パフォーマンス プラグマを含む)

- 新しい IP サポート

- FIR/FFT でフラクショナル レート SSR に対応 (FFT は SPFP32 SSR = 最大 64 までサポート)

- ECC を備えたデータフロー バッファーを、ブロック RAM または UltraRAM で実装可能

- 使いやすさが向上

- CSIM および CoSim の自動再起動をサポート

- M-AXI 用マルチ ポート キャッシュ

- 側帯波信号に対応する AXI ストリーム用の新しい API

AMD Vitis™ ソフトウェア プラットフォーム 2025.1 リリースのハイライト

Versal AI エンジン対応の強化された設計フロー

- 新規および強化された DSP ライブラリ関数、AI エンジン API、新しいデータ型のサポート

Versal AI コア シリーズ (AIE 搭載):

- 2D 並列 AIE と PL アーキテクチャを活用した、AI エンジン向け GEMV/FFT の強化 (ポリフェーズ チャネライザに最適)

- ベクトル化された Bitonic SIMD ソート、相関、たたみ込み

Versal AI エッジ シリーズ (AIE-ML 搭載):

- 2D 並列 AIE-ML と PL アーキテクチャを活用した、AIE-ML エンジン向け FFT (ポリフェーズ チャネライザに最適)

- ベクトル化された Bitonic SIMD ソート、相関、たたみ込み

Versal AI エッジ シリーズ Gen 2 (AIE-ML v2 搭載):

- 2D FFT AIE-ML v2 + PL v1 (ポリフェーズ チャネライザに最適)

- TDM FIR (ポリフェーズ チャネライザに最適)

- GEMM/GEMV

- シングルレート FIR

- ハーフバンド FIR

- フラクショナル リサンプラー FIR

- レート変換 FIR

- FFT/iFFT

- DFT

- DDS ミキサー

- 関数近似処理

AI エンジン プログラミングのアップデート:

- ローカル メモリのタイリング パラメーターの仕様

- テストベンチ変更時のコンパイル時間を短縮

- AIE-ML による、DDR のピンポン バッファーを使用したデザインのパイプライン処理が高速化

- AIE-ML による、その他のメモリ アクセス機能が強化

Versal AI エンジン デザインの検証が容易

- MATLAB®& Python™ による、Vitis サブシステムの機能シミュレーション

- Vitis Analyzer による、AI エンジン デザインのレイテンシおよびスループット測定機能が強化

- 各 AIE パーティションを実行中に個別制御

AI エンジン DSP デザイン向け Vitis Model Composer の機能強化

- 複数の最上位 AI エンジン サブシステムをサポート

- SSR モード対応の高機能 FFT や、DSP58 リソースを節約できる複素乗算器など、AIE と HDL の両方で利用可能な追加ブロックを提供

エンベデッド開発向け Vitis IDE のアップデート

- Vitis Unified IDE (新しい GUI) がデフォルトになる - 従来の Vitis IDE は非推奨

- GCC や ARMClang など、サードパーティ製ツール チェーンのサポート

- Vitis IDE のマーケットプレース機能を通じて、サードパーティ製の生産性向上ツールをインストールして利用可能

Vitis 最新情報 (カテゴリ別)

次の各セクションを展開して AMD Vitis 2025.1 の新機能と拡張機能の詳細を確認してください。サポートされているプラットフォーム、動作の変更、既知の問題については、Vitis ソフトウェア プラットフォーム 2025.1 リリース ノートのアプリケーション アクセラレーション フローおよびエンベデッド ソフトウェア開発フローを参照してください。

Versal AI コア シリーズ (AIE 搭載):

- 2D 並列 AIE と PL アーキテクチャを活用した、AI エンジン向け GEMV/FFT の強化 (ポリフェーズ チャネライザに最適)

- ベクトル化された Bitonic SIMD ソート、相関、たたみ込み

Versal AI エッジ シリーズ (AIE-ML 搭載):

- 2D 並列 AIE-ML と PL アーキテクチャを活用した、AIE-ML エンジン向け FFT (ポリフェーズ チャネライザに最適)

- ベクトル化された Bitonic SIMD ソート、相関、たたみ込み

Versal AI エッジ シリーズ Gen 2 (AIE-ML v2 搭載)

- 2D FFT AIE-ML v2 + PL v1 (ポリフェーズ チャネライザに最適)

- TDM FIR (ポリフェーズ チャネライザに最適)

- GEMM/GEMV

- シングルレート FIR

- ハーフバンド FIR

- フラクショナル リサンプラー FIR

- レート変換 FIR

- FFT/iFFT

- DFT

- DDS ミキサー

- 関数近似処理

- MATLAB®& Python™ による、Vitis サブシステムの機能シミュレーション

- Vitis Analyzer による、AI エンジン デザインのレイテンシおよびスループット測定機能が強化

- 各 AIE パーティションを実行中に個別制御

複数の最上位 AI エンジン サブシステムをサポート

AIE および HDL の両方で使用可能な追加ブロック

AI エンジン

- Bitonic ソート (Versal AI コア シリーズ、Versal AI エッジ シリーズ、Versal AI エッジ シリーズ Gen2)

- DFT/FFT (Versal AI エッジ シリーズ Gen2)

- FIR – シングル レート、ハーフバンド、レート変換、フラクショナル リサンプラー (Versal AI エッジ シリーズ Gen2)

- DDS/ミキサー (Versal AI エッジ シリーズ Gen2)

HDL ライブラリ

- 拡張 FFT – SSR モードの追加

- SSR 8、16、32、64 (ネイティブ浮動小数点)

- SSR 2、4 (固定小数点)

- 強化された複素乗算器 (DSP58 リソースの使用を削減)

- CFLOAT MAC の新規サポート

- ベクトル IFFT 浮動小数点演算 – 新しいブロック

- R2025a で MATLAB (.m) から直接 HLS 向け C++ コードを生成

- 使いやすさを追求した Vitis HLS の新機能

- 実行中に変化するワイヤ入力や AXI Lite 入力のモデリングに対応 (Direct I/O)

- トップレベル HLS デザイン向け性能最適化プラグマ (オープン EA)

- 専用の組込みライブラリを介した Versal 複素乗算器のサポート

- Vitis HLS GUI の改善

- Clang 16 による C++17 の初期サポート

AMD Vitis™ ソフトウェア プラットフォーム 2024.2 リリースのハイライト

AMD Versal AI Engine DSP デザインの強化機能

- Vitis アナライザーを使用したレイテンシとスループットの見積もり

- Vitis アナライザーを使用した利用不可能な PLIO の識別

- AMD Versal™ AI Engine デザインの迅速なプロトタイピング

- ヒープ/スタック メモリおよびプロラム メモリのレポート生成

Versal AI Engine 向けの強化された新しい Vitis ライブラリ関数

- AI エンジン (AIE) 用に強化された DSP ライブラリ関数 (Versal AI コアおよび Versal プレミアム シリーズで利用可能)

- 性能が向上した時分割多重 (TDM) FIR フィルター関数

- 高性能バージョンを提供:

- GEMV (一般行列ベクトル積)

- GEMM (一般行列乗算)

- 2D IFFT – AIE と PL に分割して高性能化

- AIE-ML 用の新しい DSP ライブラリ関数 (Versal AI エッジで利用可能)

- 性能が向上した TDM FIR フィルター関数

- Radix-3/Radix-5 FFT のサポート

- GEMV

- GEMM

Vitis IDE の使いやすさが向上 (GUI の刷新)

- 新しいシリアル端子: ハードウェアからのシリアル メッセージを監視可能

- サードパーティ拡張機能の導入と活用

- PS トレース: エンベデッド システムのデバッグや性能最適化を支援

AI エンジン DSP デザイン向け Vitis Model Composer の機能強化

- AI エンジン DSP ライブラリの更新

- AIE (Versal AI コア、Versal プレミアム シリーズで利用可能)

- Mixed Radix (混合基数) FFT

- Stockham FFT の性能向上

- TDM FIR

- AIE-ML (Versal AI エッジ シリーズで利用可能)

- TDM FIR

- ダイレクト デジタル合成 (DDS – 波形生成に使用)

- Mixer (周波数シフトに使用)

- AIE-MLv2 (Versal AI エッジ Gen 2 シリーズで利用可能)

- FIR

- DFT

- DDS

- Mixer

- AIE (Versal AI コア、Versal プレミアム シリーズで利用可能)

- Vitis Model Composer にデータ型が追加

- cbfloat16 をサポート

- カスケード信号向けのデータ型を追加

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- Vitis Model Composer から AIE/HLS カーネル デザインを Vitis にエクスポートし、Vitis サブシステム (VSS) として利用可能

- Vitis デバッガーを使用して、Vitis Model Composer に搭載された AIE/HLS カーネルをデバッグ

- Vitis Model Composer の HDL ブロックセットの更新

- Vitis Model Composer のその他の機能強化

- コード生成の応答時間が改善

- すべてのデザインに対してシミュレーションを 1 回のみ実行

- Hub ブロックの設定を JSON ファイルとして保存 (迅速なプロトタイピングやバッチ処理に有効)

- MATLAB R2024a のサポートを追加

- Red Hat Enterprise Linux (RHEL) 8.10、9.4 のサポートを追加

- コード生成の応答時間が改善

- デザイン ルール チェック (DRC) (設計上の考慮点がなくなる)

Vitis 最新情報 (カテゴリ別)

次の各セクションを展開して AMD Vitis 2024.2 の新機能と拡張機能の詳細を確認してください。サポートされているプラットフォーム、動作の変更、既知の問題については、Vitis ソフトウェア プラットフォーム 2024.2 リリース ノートのアプリケーション アクセラレーション フローおよびエンベデッド ソフトウェア開発フローを参照してください。

AIE 用に強化された DSP ライブラリ関数 (Versal AI コアおよび Versal プレミアム シリーズで利用可能)

- 性能が向上した時分割多重 (TDM) FIR フィルター関数

- 高性能バージョンを提供:

- GEMV (一般行列ベクトル積)

- GEMM (一般行列乗算)

- 2D IFFT – AIE と PL に分割して高性能化

AIE-ML 用の新しい DSP ライブラリ関数 (Versal AI エッジで利用可能)

- 性能が向上した時分割多重 (TDM) FIR フィルター関数

- Radix-3/Radix-5 FFT のサポート

- GEMV (一般行列ベクトル積)

- GEMM (一般行列乗算)

- Vitis アナライザーを使用したレイテンシとスループットの見積もり

- Vitis アナライザーを使用した利用できない PLIO の識別

- AI エンジン DSP ライブラリの更新

- AIE (Versal AI コア、Versal プレミアム シリーズで利用可能)

- Mixed Radix (混合基数) FFT

- Stockham FFT の性能向上

- TDM FIR

- AIE-ML (Versal AI エッジ シリーズで利用可能)

- TDM FIR

- DDS (ダイレクト デジタル合成 – 波形生成に使用)

- Mixer (周波数シフトに使用)

- AIE-MLv2 (Versal AI エッジ Gen 2 シリーズで利用可能)

- FIR

- DFT

- DDS

- Mixer

- AIE (Versal AI コア、Versal プレミアム シリーズで利用可能)

- Vitis Model Composer にデータ型が追加

- cbfloat16 をサポート

- カスケード信号向けのデータ型を追加

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- Vitis Model Composer から AIE/HLS カーネル デザインを Vitis にエクスポートし、Vitis サブシステム (VSS) として利用可能

- Vitis デバッガーを使用して、Vitis Model Composer に搭載された AIE/HLS カーネルをデバッグ

- Vitis Model Composer の HDL ブロックセットの更新

- Vitis Model Composer のその他の機能強化

- コード生成の応答時間が改善

- すべてのデザインに対してシミュレーションを 1 回のみ実行

- Hub ブロックの設定を JSON ファイルとして保存 (迅速なプロトタイピングやバッチ処理に有効)

- MATLAB R2024a のサポートを追加

- Red Hat Enterprise Linux (RHEL) 8.10、9.4 のサポートを追加

- デザイン ルール チェック (DRC) (設計上の考慮点がなくなる)

- 実行中に変化するスカラー/ワイヤ入力のモデリング (ダイレクト I/O)

- 任意精度の浮動小数点型をサポート

- HLS コードの DSP ブロックへのマッピング

- ユーザーが任意に決定できるコード実行シーケンス

- データ型をわかりやすく表示する HLS デバッガー (GNU デバッガーの Pretty Print 技術を使用)

AMD Vitis™ ソフトウェア プラットフォーム 2024.1 リリースのハイライト

AMD Versal™ AI エンジン DSP デザインの改善点

- AMD Versal AI コア シリーズ向けの強化された DSP ライブラリ関数

- SSR > 1 の場合での時分割多重 (TDM) FIR フィルター関数

- 32 ビットの回転因子を使用する FFT

- Mixed-Radix 3 および Mixed-Radix 5 FFT

- Kronecker Matrix Product (クロネッカー積)

- 安定性向上のためのハウスホルダー変換による QRD ソルバー

- SSR > 1 の場合での DFT

- AIE ML 搭載 AMD Versal AI エッジ シリーズ向けの新しい DSP ライブラリ関数

- SSR 対応の GEMV (一般行列ベクトル積)

- SSR 対応の GEMM (一般行列乗算)

- AIE API の機能強化

- Radix-3/Radix-5 FFT をサポート

- AIE シミュレータ機能向上

- Control, Interface, and Processing System (CIPS) IP コアを必要としない、PL を使用する AI エンジン デザイン向けのサイクル近似シミュレーション機能

- AMD Vitis アナライザーが VCS、Questa、Xcelium、および Riviera などのサードパーティ シミュレータと連携したハードウェア エミュレーションに対応

Vitis 統合ソフトウェア プラットフォームの主な改善点

- 新しいデバイスをサポート: AMD Versal™ プレミアム VP1902 アダプティブ SoC、AMD MicroBlaze™ V プロセッサ

- Windows® 環境でのエンベデッド アプリケーション開発および BSP 生成を強化

- 外部ツールでコンパイルされたエンベデッド アプリケーションをデバッグするためのユーザー管理フロー

- 新しい Bootgen GUI

- プラットフォーム プロジェクトでインクリメンタル ビルドが可能

AMD Vitis IDE (新しい GUI) の主な改善点

- プロセッシング サブシステムの階層型デバッグのサポートを追加

- プロジェクト/ワークスペースのエクスポートおよびインポートのサポートを追加

- Python インタープリターおよび API のサポートを追加

- 新機能のプレビュー ページ

- エンベデッド、AIE、プラットフォーム プロジェクトの新しいファイル変更通知機能

Vitis 最新情報 (カテゴリ別)

次の各セクションを展開して AMD Vitis 2024.1 の新機能と拡張機能の詳細を確認してください。サポートされているプラットフォーム、動作の変更、既知の問題については、Vitis ソフトウェア プラットフォーム 2024.1 リリース ノートのアプリケーション アクセラレーション フローおよびエンベデッド ソフトウェア開発フローを参照してください。

AMD Versal AI コア シリーズ向けの DSP ライブラリ関数

- SSR > 1 の時分割多重 (TDM) FIR フィルター関数

- 32 ビットの回転因子を使用する FFT

- Mixed-Radix 3 および Mixed-Radix 5 FFT

- Kronecker Matrix Product (クロネッカー積)

- 安定性向上のためのハウスホルダー変換による QRD ソルバー

- SSR > 1 の場合での DFT

AIE ML 搭載 AMD Versal AI エッジ シリーズ向けの新しい DSP ライブラリ関数

- SSR 対応の一般行列ベクトル積 (GEMV)

- SSR 対応の一般行列乗算 (GEMM)

AIE API の機能向上

Radix-3/Radix-5 FFT をサポート

AI エンジン シミュレータの改善点

- Control, Interface, and Processing System (CIPS) IP コアを必要としない、PL を使用する AI エンジン デザイン向けのサイクル近似シミュレーション機能

- Vitis アナライザーが VCS、Questa、Xcelium、および Riviera などのサードパーティ シミュレータと連携したハードウェア エミュレーションに対応

- Vitis アナライザーのテーブルを CSV フォーマットでエクスポート可能

- AMD Vitis Model Composer 内で AIE および AIE-ML 向けの新しい DSP 機能をサポート

- 時分割多重 (TDM) FIR フィルター関数

- 1 GSPS 以上のスループットのポリフェーズ チャネライザを構築

- DFT/IDFT – SSR のサポート

- 小規模データセットでスループットとレイテンシを向上させるために最適化された変換

- FFT/IFFT – CINT32 ビットの回転因子のサポート追加

- Mixed-Radix (混合基数) FFT/IFFT – AIE ML のサポート

- Model Composer Hub ブロックの使いやすさ向上

- ハードウェア検証フローが強化

- v 2024.1 で OS および MATLAB® のバージョン サポートが追加

- RHEL 9

- MATLAB R2023a および R2023b

GitHub.で新たなサンプル デザインを利用可能

新しいステンシル プラグマにより、イメージおよびビデオ フィルター用の HLS C++ コードが簡素化

新しいライブラリ関数ウィザードで AMD Vitis ライブラリの GitHub リポジトリを利用可能

- AMD Vivado 設計ツール用の Solver および Vision (OpenCV 互換) IP を作成

- ライブラリ サンプルを実行

AMD Vivado IP インテグレーターでメモリ インターフェイスのプラグマ (ap_memory) を使用してポートをバンドル可能

新しい HLS コンポーネント比較機能では、2 つ以上のコンポーネントのメトリクスを並べて表示可能

ユーザーが提供する RTL コードで C++ 関数を置き換えることが可能 (ブラック ボックス フロー)

コード アナライザー機能では、C++ の構造体を細分化して解析し、パフォーマンスを微調整可能

HLS グローバル FSM エンコーディングやセーフ ステートの選択をユーザーが制御可能

C シミュレーション時に Clang サニタイザーを利用してアドレスや初期化をチェック

Vitis™ ソフトウェア プラットフォーム 2023.2 リリースのハイライト

Versal™ AI エンジン DSP デザインの改善点

- 新しい DSP ライブラリ関数

- DSP 関数向けの新しい API サポート

- AI エンジン コンパイラおよびシミュレータの新機能

新しいスタンドアロンの Vitis エンベデッド ソフトウェア

- C コードを使用して Arm® エンベデッド サブシステムを構築する設計者向けのコンパクトなスタンドアロン インストーラー

- Bootgen や XSCT などのすべてのエンベデッド機能が提供される

新しい Vitis 統合設計環境

- すべての Vitis ワークフローで共通の GUI と CLI を使用

- 次世代の Eclipse Theia ベース GUI により、柔軟性と使いやすさが改善され、作業効率が向上

Vitis 最新情報 (カテゴリ別)

以下の各セクションを展開して Vitis 2023.2 の新機能と拡張機能の詳細を確認してください。サポートされているプラットフォーム、動作の変更、既知の問題については、Vitis ソフトウェア プラットフォーム 2023.2 リリース ノートのアプリケーション アクセラレーション フローおよびエンベデッド ソフトウェア開発フローを参照してください。

AI エンジン向けの新しい DSP ライブラリ関数

- Mixed Radix (混合基数) FFT

- Discrete Fourier Transform (DFT)

- 一般行列ベクトル積 (GEMV)

DSP 関数向けの新しい API サポート

- cint32 twiddle データ型の FFT IP

- Radix-4 FFT API の cint16 サポート

- ベクトル化された「fix2flt」と「flt2fix」を API で実装

AIE ML 向けの新しい API サポート

- API が sliding_mul() 関数で int32/cint32 データ型に対応

- API が sliding_mul() 関数で <float> データ型に対応

- スパース行列の乗算に必要なすべての AIE API ルーチンを提供

主なコンポーネントのアップデート

- U-boot 2024.1

- Arm トラステッド ファームウェア 2.10

- Linux カーネル 6.6_LTS

- Qemu 8.1

- Xen 4.18

- OpenAMP 2023.10

旧 BSP:

- AMD Microblaze™: VCU118、KCU105、KC705、AC701

- Zynq: zc706

- AMD Versal™: VMK180-EMMC、VMK180-OSPI

- Zynq MP: ZCU111

新しい BSP (XSCT):

- 新しい ETH Phy を備えた VEK280 プロダクション BSP

新しいシステム デバイス ツリー フロー (SDT) BSP:

- ZCU102、ZCU104、ZCU105、ZCU216

- ZCU208、ZCU208-sdfec、ZCU670

- VCK190

- VMK180

- VPK120

- VPK180

- VEK280

- AIE コンパイラは 2D および 3D アレイを入力/出力としてサポート可能

- Vitis アナライザーは FIFO サイズを調整するためのガイダンス レポートを生成

- マルチスレッド シミュレータ カーネルと VCD (Value Change Dump) アナライザーの高速化をサポート

- MATLAB® 環境および Python トラフィック ジェネレーターとの外部インターフェイス

- PLIO アライメントで空サイクルと待機サイクルに対応するように強化された AXI Stream モデル

- デザイン ルール チェック機能が強化

- 高速デバッグによる AI エンジン トレースのオフロード

- Vitis 環境で NoC およびハード DDRMC のプロファイリングが可能

- Vitis ツールで VEK280 および Alveo™ V70 AI 推論アクセラレータ カード向けの AIE-ML トレースをサポート

- AI エンジン ブロックのアップデート

- AIE-ML Graph をブロックとして Vitis Model Composer にインポート可能

- Vitis Model Composer で AIE および AIE-ML の実装に使用できる新しい DSPlib 関数

- Simulink® ツールで内部信号に対する AIE シミュレータ出力を可視化

- HLS Kernel ブロックのアップデート

- テストベンチの自動生成

- HLS カーネル ブロックのデータ型サポートを拡張

- Vitis Model Composer と Vitis ツールを統合

- Vitis Model Composer から .xo および libadf.a ファイルを直接生成可能

- その他の改善点

- サポートされる MATLAB® ツールのバージョン: R2021a、R2021b Update 6、R2022a Update 6、R2022b

- ハードウェア検証フローで新たなトポロジをサポート

- GitHub で新しい参照資料を入手可能

- HLS コンポーネント対応の新しい Vitis 統合 IDE

- 新しい Vitis HLS ライセンス要件

- C 合成前の性能を予測する新しいコード アナライザー機能

- AXI インターフェイスが強化:

- HLS AXI ストリームのサイド チャネルに対応

- AXI マスターのキャッシングをユーザーが設定可能

- その他の機能強化:

- 新しいコード複雑度レポートで、C 合成中にデザイン サイズの問題を特定可能

- コンパイル時間の改善: 2023.2 バージョンでは、2023.1 と比較して平均で約 20% のコンパイル時間を短縮できる1

Vitis ソフトウェア プラットフォーム 2023.1 リリースのハイライト:

Versal™ AI エンジン (AIE) アレイ用の新しい Vitis™ ライブラリ関数

- DSP ライブラリ関数 – 多様な FIR フィルター構成

- ソルバー ライブラリ関数 – 高性能化

Versal AI コアおよび AI エッジ シリーズのデザイン フローが強化

- AIE コンパイラは 2D および 3D アレイを入力/出力としてサポート

- AIE シミュレータのガイダンス機能により、適切な FIFO サイズを決定してデッドロックを回避できる

- AIE ステータス レポート機能が強化

- Vitis アナライザーの新しいデフォルト GUI

Vivado™ 環境への Vitis 環境のエクスポートをサポート

- Vitis で開発するチームと Vivado で開発するチームが共通のインターフェイスを使用して並行して作業できる

Vitis 最新情報 (カテゴリ別)

次の各セクションを展開して AMD Vitis 2023.1 の新機能と拡張機能の詳細を確認してください。サポートされているプラットフォーム、動作の変更、既知の問題については、Vitis ソフトウェア プラットフォーム 2023.1 リリース ノートのアプリケーション アクセラレーション フローおよびエンベデッド ソフトウェア開発フローを参照してください。

DSP ライブラリ - FIR フィルター

- フラクショナル リサンプラー FIR、シングル レート FIR、ハーフ バンド FIR、およびレート チェンジ FIR の機能が強化され、データ ビット幅を上回る係数ビット幅を設定可能

- フラクショナル リサンプラー FIR は、複数の AIE タイルを使用した SSR 操作にも対応し、係数再ロード機能を搭載

ソルバー ライブラリ

- 高性能ストリーミング デザイン (約 300 タイル) で API の性能が向上

- AIE アレイからのデータ読み書きを支援するため、4D データ ムーバー関数で QR 分解と コレスキー分解をサポート

- 1D アレイに加えて 2D および 3D アレイを入力/出力としてサポート。

- グラフ内のグラフ (サブグラフ) 構成や条件付きポート構成をサポート。

- 新しい AIE CINT-to-CFLOAT データ変換 API。

- AIE ステータス レポート機能が改善され、デザイン内のタイルやイベントの情報、また AIE-ML や AIE タイルの追加レジスタに関する情報を含むファイルを生成。

- Versal デバイスのメモリに保存する代わりに、高速差動ペア (HSDP) を介して外部メモリを使用することで AIE イベント トレースをオフロード。

- Vitis 環境で NoC およびハード DDR MC のプロファイリングが可能。

- アプリケーションの特定部分を検査する AIE ウィンドウ イベント トレース機能。

- デッドロックを回避するために適切な FIFO サイズを決定するガイダンス機能。

- AIE シミュレータでレポートされるノードを選択できるため、シミュレータの VCD ファイル サイズが削減されて、シミュレーションが高速化。

- AIE シミュレータでは、どの AIE でメモリ アクセス違反が発生したか、それがグラフ C コードのどの行に対応するかを示すレポートを生成できる (Vitis アナライザーで表示)。

- トレース ビュー データの可視化が AIE ML アレイにも対応。

- Versal AI エンジン向けの FIR フィルター構成に対応する新しいデータ型をサポート

- Versal アダプティブ SoC の DSP58 向けに最適化された 2 つの新しい浮動小数点関数

- Versal AI Engine 向けのすべての Vitis Model Composer ライブラリ関数の応答時間が短縮

- その他の機能強化:

- HLS カーネル ブロックの機能強化

- Vitis Model Composer Hub ブロックが改善

- MATLAB ツール バージョン R2021a、R2021b、R2022a をサポート

- 性能向上2: 2023.1 では 2022.2 よりも平均 5.2% のレイテンシが向上

- Vitis HLS ツールで L1 ライブラリ関数を簡単にダウンロード、表示、インスタンシエート可能

- Vitis HLS ツールでの AXI トランザクションとバースト レポート機能のサポートが強化

Vitis ソフトウェア プラットフォーム 2022.2 リリースのハイライト:

Versal™ AI エンジン (AIE) アレイ用の新しい Vitis™ ライブラリ関数

- DSP ライブラリ関数 – 機能が強化

- ソルバー ライブラリ関数

- ビジョン ライブラリ関数

- 超音波診断ライブラリ関数

Versal AI コアおよび AI エッジ シリーズのデザイン フローが強化

- AI エンジン アレイにおけるカーネルの相対配置 - 性能と使用率が向上

- AIE x86 シミュレータの機能強化 - x86 シミュレータでのデッドロックのモデリングが改善

- AIE API の強化 - Radix 3/5 FFT および Matrix 'x' Vector API が追加

- Versal デザインのプロファイリングおよびデバッグ機能が強化 - デッドロック検出、大規模なトレース データ収集、RTL/Python テストベンチのサポート

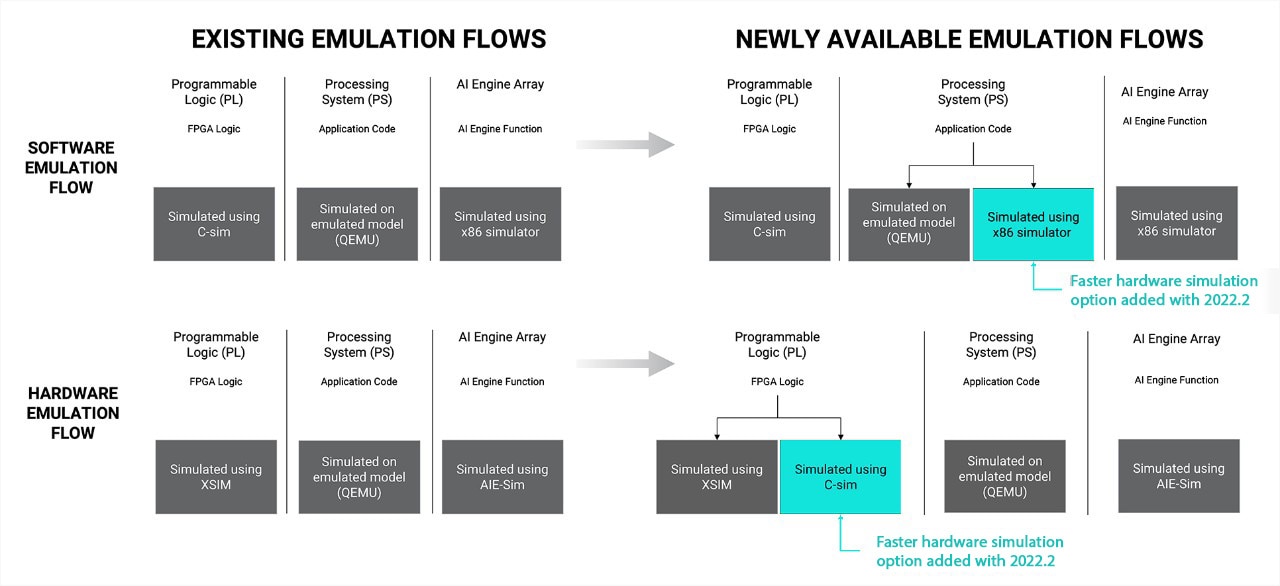

- Vitis でヘテロジニアス デザイン向けの新しいシミュレーション オプション

Vitis 最新情報 (カテゴリ別)

次の各セクションを展開して AMD Vitis 2022.2 の新機能と拡張機能の詳細を確認してください。サポートされているプラットフォーム、動作の変更、既知の問題については、Vitis ソフトウェア プラットフォーム 2022.2 リリース ノートのアプリケーション アクセラレーション フローおよびエンベデッド ソフトウェア開発フローを参照してください。

DSP ライブラリ関数

- AI エンジンでのスーパー サンプル レート (SSR) FIR フィルターのインプリメンテーションで係数リロード機能とダイナミック ポイント サイズをサポート

- AI エンジン アレイ向けの FFT 関数に FFT のウィンドウイング要素を追加

ソルバー ライブラリ関数

- Quadrature Rotation (QR) 分解

- Cholesky 分解

ビジョン ライブラリ関数

- AI エンジン アレイ向けの 4 つの新しいビデオ機能

超音波診断ライブラリ関数

- 医療用超音波デザインの構築を支援する各種機能

- AI エンジン アレイにおけるカーネルの相対配置を制御する制約を追加する機能 - 性能と使用率が向上

- x86 シミュレータでの AIE デッドロックのモデリングが改善

- 新しい AIE API - Radix 3/5 FFT および Matrix 'x' Vector API が追加

- HW エミュレーションでの AI エンジンのプロファイリング レポートを生成

- AI エンジンと PL ベース デザインに対して XSDB (ザイリンクス システム デバッガー) を使用したデッドロックの検出

- ザイリンクス ランタイム (XRT) 制御による、PLIO での AI エンジン イベント トレースの継続的なオフロード

- x86 ホスト マシンの PS アプリケーションで SW エミュレーションをサポート

- HW エミュレーションで、RTL の代わりに SystemC の機能モデルを使用可能

- シンプルな RTL テストベンチまたは Python スクリプト ベースのトラフィック ジェネレーターを使用して AI エンジン カーネルのシミュレーションが可能

- Vitis™ アナライザーを使用して HW エミュレーション中に AI エンジンの状態を解析

Vitis 2022.2 環境の新しいシミュレーション オプション: プロセッサ システム x86 シミュレーションおよび AI エンジン x86 シミュレーション: x86 シミュレータを使用してプログラマブル ロジック シミュレーションを実行可能。

- Versal AI Engine デザインの機能

- AI エンジンの DSP ライブラリ ブロック デザインにグラフ制約を追加できる – 性能と使用率が向上

- AIE デザイン向けサイクル近似シミュレーションの新機能

- AI エンジン グラフ インポート ブロックによる RTP (Run Time Parameter) ポートの自動検出

- DSP ライブラリ ブロックの機能強化と追加

- 一般的な機能

- PL および AIE アレイを使用したヘテロジニアス システム デザイン向けのハードウェア検証フロー

- Vitis Model Composer の Hub ブロックがヘテロジニアス設計に対応

- 有効な AI エンジン、HDL、HLS のサブシステムを自動検出

- ハードウェア検証フローが強化され、Versal プラットフォームに対しては HDL ブロックのみを含むデザインおよび HDL - AI エンジン間ブロックを含むデザインをサポート

- タスク レベルの並列性を向上させたコーディング スタイルをサポート

- C シミュレーションの高速化と QoR 向上

- 性能とタイミングが向上

- バースト推論の精度向上

- Unroll、Pipeline、Array_Partition、inline の各プラグマを自動的に推測し、性能を向上させる

- タイミング精度の向上により、より高い周波数でタイミング クロージャを達成可能

- その他の機能

- 解析とデバッグ: RTL での合成後でも C コードに挿入された printf をサポート

- 使いやすさ向上: 指定されたトランザクション間隔を自動で達成するための新しいパフォーマンス プラグマ

- FFT および FIR IP で HLS::stream インターフェイスがサポートされる

Vitis ソフトウェア プラットフォーム 2022.1 リリースのハイライト:

Versal™ ACAP および AI エンジンの Vitis™ フローが向上

- 1 つのスタティック領域と 1 つの DFX 領域を備えた AMD ベースの DFX プラットフォームをサポート

- AIE プロファイリングでストール/デッドロックの検出をサポートし、Vitis アナライザーで表示するための AI エンジン ステータス (エラー イベントを含む) を生成できる

- x86sim、AIEsim、SW エミュレーションの外部トラフィック ジェネレーターの柔軟性が向上し、シミュレーションやエミュレーション フローへの挿入が簡単になる

- Vitis Model Composer によるハードウェアでの検証、Linux および HW エミュレーションが可能

Vitis (DC および Vitis HLS)

- ダイナミック領域の生成プロセスをサポートする新しいレポート機能が追加され、3 つの新規/アップデート済みレポートでフロー レポートが強化

- Vitis の PL プロファイリングが改善され、トレースをメモリ リソース (推奨) または PL の FIFO にオフロードして性能を向上

- ランタイム プロファイルを表示できる新しい Timeline Trace ビューアーでは、シミュレーション後もそのまま Vitis HLS GUI でタイムラインを確認できる

- Vitis HLS で新しいパフォーマンス プラグマ (set_performance_directive) を使用して、よりスマートな構築が可能

- L3 API が強化 (カーネルの呼び出しを 1 ms 短縮) されパフォーマンスが向上した Vitis グラフ ライブラリ

Vitis 最新情報 (カテゴリ別)

次の各セクションを展開して AMD Vitis 2022.1 の新機能と拡張機能の詳細を確認してください。サポートされているプラットフォーム、動作の変更、既知の問題については、Vitis ソフトウェア プラットフォーム 2022.1 リリース ノートのアプリケーション アクセラレーション フローおよびエンベデッド ソフトウェア開発フローを参照してください。

- 新たにゲノム解析用アクセラレータ ライブラリを追加 (L1、L2、L3)

- グラフ ライブラリ、L3 が強化されパフォーマンスが向上

- Vitis データベース ライブラリ、GQE Multi-Functional カーネル

- ビジョン ライブラリに新しい機能を追加

- Vitis AIE ビジョン ライブラリに新しい機能を追加/強化

- Vitis AIE DSP ライブラリ、FIR リサンプラーが FIR フラクショナル インターポレーターにとって代わる

- Vitis コーデック ライブラリの新しい API: API jxlEnc、API ‘leptonEnc’、API ‘resize’、API ‘WebpEnc’

Vitis データ圧縮ライブラリ

- ZLIB 圧縮が改善、8KB ソリューション向けのカスタマイズされたオクタコア圧縮

- ZLIB 解凍が改善、8KB ファイル サイズ向けのカスタマイズされた IP

- Platform Capability Query が改善

- HBM の使いやすさ向上、カーネル M_AXI に対して HMSS への特定の S_AXI エントリ ポイントを選択可能、コンフィギュレーション ファイルからの RAMA 挿入

Vitis AI エンジン コンパイラ

- ハードウェアでの AI エンジンの自動ストール/デッドロック検出および分析

- 自動ステータス出力の分析

- 自動ステータス出力の分析 – バッファー

- ハードウェアでの手動ステータス出力の分析

- 手動ステータス出力の分析

- AI エンジン イベントのトレースの強化

- 外部トラフィック ジェネレーター AIEsim

- ハードウェアでの AI エンジン プロファイリングの向上

- ブロードキャスト ウィンドウ向けの AI エンジン サポート

- Vitis AI エンジン コンパイラの強化されたグラフ プログラミング モデル

- Vitis AI エンジン コンパイラ - ADF グラフの PLIO/GMIO

Vitis HLS

- 分析機能が強化、新しい Timeline Trace ビューアー

- コーディング スタイルが強化、ストリーム オブ ブロック タイプで Array Partition をサポート

- Pragma Abstraction、新しいパフォーマンス プラグマ (および指令)

- Vitis Core 「ワン ライナー」、Vitis HLS - 新しい Timeline Trace ビューアー、新しい PERFORMANCE プラグマ、ストリーム オブ ブロック サポート ウィンドウ

- 新しいビューアー

- デザインに含まれるすべての生存関数 (モジュール化された関数など) のランタイム プロファイルを表示

- 特に、協調シミュレーション後にデータフロー領域のビヘイビアーを確認するのに便利

- Vitis HLS にネイティブ対応 - XSIM 波形ビューアーの起動が不要になった (外部ツール)

Vitis アナライザー

- Vitis アナライザーの改善、タイムライン カスタマイズの保存/復元

- レポート機能の強化、report_qor_assessment、xclbin クロッキング情報、Vivado オートメーション サマリ

- プロファイリングの強化、新しい PL プロファイリング インフラの有効化、複数のメモリ モニターを挿入するために複数の trace_memory オプションを追加可能 (HW のみ)、SLR0 ~ DDR0 のすべての CU と SLR1 ~ DDR1 のすべての CU でトレース データをオフロードするための v++ リンカーのサンプル config ファイル

Vitis IDE

- Versal 用に Bootgen GUI をアップデート

- ツールチェーンの更新

- XSCT、STAPL 対応、リンカー スクリプト生成コマンドを追加

- システム コンパイル フロー、システム コンパイルの資料を参照

Vitis エミュレーション

- 自動再起動のソフトウェア エミュレーション サポートと、常時稼働カーネルのメールボックス サポートを追加

- フリーランニング カーネルは sw-emu で while(1) が不要

- 外部トラフィック ジェネレーターのソフトウェア エミュレーション サポートを追加

- ハードウェア エミュレーションは、Streaming IP に HLS C ソース コード機能モデルを使用できます。

- デバイス数を確認するための API xrt::system を追加

- メッセージを記録するための API xrt::message を追加

- XRT ネイティブ API を使用するホスト コードは次が必須となる

-std=c++17 またはそれ以上 - 同期動作の非同期実行のために試験的に xrt::queue API を追加

- xbutil で AIE FIFO カウンターを表示し、AIE のデッドロックの状況をデバッグ

- xbutil -- レガシ オプションを削除。

- xclbinutil --info ユーティリティでエンベデッド プラットフォームのクロック情報を提供

- Arm で xbutil を使用して SOM イメージをロード可能

- xbtop スタンドアロン ユーティリティは Linux の Top コマンドのような出力を表示 (レガシ xbutil -top の代わりとなる)

- XRT ユーティリティで、Tab キーを使用する Bash の自動補完をサポート

- Alveo プラットフォームのアップデート、プラットフォーム アップデートで安定性向上、カード マネージメント機能のアップデート、SC ファームウェア アップデート ツール

- エンベデッド プラットフォーム、新しい VCK190 DFX プラットフォーム: xilinx_vck190_base_dfx_202210_1、Vitis のインストールにエンベデッド プラットフォームが含まれる、Vivado に新しいカスタマイズ可能サンプル デザインを追加: MPSoC 用 Vitis プラットフォーム

- Vitis Model Composer Hub ブロック全体を見直し、スケーラビリティと使いやすさが向上

- ハードウェア検証フローがベアメタルに続き Linux もサポート

- "AIE to HDL" および "HDL to AIE" ブロックに HDL ゲートウェイ ブロックが含まれない

- 2022.1 では、インターネットにアクセスできないお客様のためにサンプル デザインのスナップショットを同梱する。このツールで、GitHub から最新のサンプル デザイン リビジョンをダウンロードするよう促す。

- 使いやすさを考慮し、コード生成に含まれないユーティリティ ブロックは、背景色を白に変更

- 使いやすさ向上のため、ライブラリ ブラウザーを改善

- RHEL 8.x サポート

- MATLAB サポート - R2021a および R2021b

Vitis ソフトウェア プラットフォーム 2021.2 リリースのハイライト:

- 新しいドメイン特化型開発環境

- VCK5000 および Varium C1100 カードに対応するエンド ツー エンドのフル フロー サポート

- コア ツールの強化機能

- Vitis AI エンジン コンパイラの C/C++ を使用する抽象度の高い API、プラグマの自動推論、エリア グループ制約

- Vitis AI エンジン ツールの x86 シミュレータ機能が強化: トレース レポート、メモリ アクセス違反およびデッドロックの検出

- Vitis HLS の使いやすさ向上、タイミングおよび QoR の機能強化、HLS API によるユーザー制御のバースト推論

- Vitis アナライザー機能が強化 (タイムライン トレース レポートの改善、データの可視化、ストールの解析)

- Vitis XRT (AI エンジン グラフを制御するための、AI エンジンによる複数プロセスと複数スレッド サポート)

- AI エンジンのトレース、AI エンジン アプリケーションの SW エミュレーションをサポートする Vitis IDE およびエミュレーション ツール

- 新たに 39 の C/C++ ライブラリ関数を提供 (DSP、データ分析、ビジョン、圧縮、データベース、グラフ、セキュリティなど多岐にわたる合計 1000 以上を提供)

- Vitis Model Composer

- 並列コンパイルにより、コンパイル/シミュレーション時間は 1/3 に削減、コンパイル時間は 1/7 に削減

- 新しいハードウェア検証フローおよび強化協調シミュレーション

Vitis 最新情報 (カテゴリ別)

次の各セクションを展開して AMD Vitis 2021.2 の新機能と拡張機能の詳細を確認してください。サポートされているプラットフォーム、動作の変更、既知の問題については、Vitis ソフトウェア プラットフォーム 2021.2 リリース ノートのアプリケーション アクセラレーション フローおよびエンベデッド ソフトウェア開発フローを参照してください。

注記: Vitis アクセラレーション ライブラリは、個別にダウンロードして入手します。これらは、GitHub からダウンロードできますが、Vitis IDE 内で直接ダウンロードすることも可能です。

| ライブラリ | 2021.1 | 2021.2 | 21.2 での新機能 |

|---|---|---|---|

| xf_blas | 167 | 167 | 0 |

| xf_codec | 3 | 3 | 0 |

| xf_DataAnalytics | 33 | 36 | 3 |

| xf_database | 62 | 65 | 3 |

| xf_compression | 78 | 93 | 15 |

| xf_dsp | 94 | 96 | 2 |

| xf_graph | 53 | 59 | 6 |

| xf_hpc | 37 | 37 | 0 |

| xf_fintech | 116 | 116 | 0 |

| xf_security | 135 | 140 | 5 |

| xf_solver | 11 | 11 | 0 |

| xf_sparse | 11 | 11 | 0 |

| xf_utils_hw | 55 | 57 | 2 |

| xf_opencv | 147 | 150 | 3 |

| 合計 | 1002 | 1041 | 39 |

注記: ビジョンの場合、各 API には異なるタイプ用に複数のテストがあるため、L*/tests のサブフォルダー数をカウントしてください。

Vitis ビジョン ライブラリ

- プログラマブル ロジック (PL)

- CLAHE TMO によるエンドツーエンドのモノクロ画像処理 (ISP)

- RGB-IR および RGB-IR 画像処理 (ISP) パイプライン

- グローバル トーン マッピング (GTM)、および GTM を用いた ISP パイプライン

| 新機能 | Cat | カスタマー/ターゲット | セグメント | 説明 |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | オートモーティブ、ISM | • 4x4 RGB-IR デモザイキングをサポート • 主にインキャビン モニタリング システム向け • 低照度監視カメラ |

| モノクロ (CCCC) | ISP | 目的に応じて使用 | オートモーティブ、ISM、A&D | •マシン ビジョン •低照度アプリケーション |

| グローバル トーン マッピング (GTM) | ISP | 目的に応じて使用 | オートモーティブ、ISM、A&D | • ダイナミックレンジとコントラストが向上 • ローカル トーン マッピング (LTM) より低コスト |

| 高密度オプティカル フロー TV-L1 | CV | NTT | ISM | • オプティカル フローの照明、ノイズ、オクルージョンに対するロバスト性が向上 |

AI エンジン (AIE)

- BlobFromImage

- バッチ サイズ 3 に対応する連続 filter2D

| 新機能 | Cat | カスタマー/ターゲット | セグメント | 説明 |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | オートモーティブ、ISM | • 4x4 RGB-IR デモザイキングをサポート • 主にインキャビン モニタリング システム向け • 低照度監視カメラ |

| ML+X | ISP | 目的に応じて使用 | オートモーティブ、ISM、A&D | • ML 干渉の前処理 |

| ガウシアン ピラミッド | CV | 目的に応じて使用 | オートモーティブ、ISM、A&D | • マルチスケール画像処理の基本 |

| ボックス フィルター | CV | 目的に応じて使用 | オートモーティブ、ISM、A&D | 平滑化を行うロー パス フィルターの基本 |

Vitis データ分析ライブラリ

- Vitis ライブラリを利用した Vitis ブロックチェーン ソリューション

- イーサリアム向けのすぐに使えるマイニング ソリューション

- C++ を使用した Vitis ライブラリによるオープンソースと簡単な運用

- Vitis ライブラリによる柔軟性と拡張性

- 多様なコインのマイニングにも柔軟に対応

- カスタマイズしてハードウェアにコンパイル

- 高度に最適化されたデザイン

- CSV パーサー API をライブラリに追加

- CSV パーサーは、CSV (Comma Separated Values) 形式ファイルを解析し、DataFrame API と簡単に接続できるオブジェクト ストリームを生成する

Vitis グラフ ライブラリ

- 新しい L2 ライブラリを追加

- リナンバリングされた Louvain

- リナンバリング

- 「重み」は Cosine Similarity で対応

Vitis データベース ライブラリ

- GQE が複数カードのサポートに加え、非同期の入出力機能にも対応する。

- 非同期サポートによって、一部の入力データの準備が整うと、FPGA が処理を開始できるようになる。

- マルチカード サポートによって、作業に適した複数の Alveo カードを識別できるようになる。

Vitis データ圧縮ライブラリ

- ZSTD マルチコア圧縮

- 新しい ZSTD マルチコア アーキテクチャを作成し、クワッド コアを使用して 1 GB/s を超えるスループットを提供。

- ZSTD 解凍の最適化

- ZSTD 解凍が、性能 (20% 向上) とリソース (最大 30% 削減) に最適化

- IBM 向けの GZIP/ZLIB ストリーム コアが改善

- カスタマイズされたスタティック/ダイナミック圧縮ストリーミング IP (4KB & 8KB)

- TUSER ポートに圧縮サイズを提供する機能を追加

- IBM 向けの GZIP/ZLIB 解凍が改善

- ハフマン デコーダーが最適化されて、レイテンシを 1.5K サイクル未満に削減

- リソースが大幅に削減 (最大 6.9K 削減) (旧バージョンは 9K 超)

- ADLR32 チェックサム機能を追加

- GZIP システム コンパイラ PoC

- GZIP 圧縮ソリューションのシステム コンパイラ PoC を作成し、OpenCL Host とのベンチマークを実施。

Vitis DSP ライブラリ

- DSP ライブラリ (2021 年より Github で提供)

- Fast Fourier Transform (FFT/iFFT)

- ポイント サイズが 32k に増加 (データ型によって異なる)

- ストリーム API とウィンドウ API をサポート

- パラレル電源 (0-4)

- スループットの向上と対応ポイント サイズの範囲拡大

- FIR フィルター

- シングル レート非対称/対称 FIR のイニシャル ストリーム サポート

- DDS/Mixer

- 2021.2 の新しいライブラリ ユニット

Vitis セキュリティ ライブラリ

- KECCAK-256 (ハッシュ関数) と CRC32C (チェックサム関数) がリリース

Vitis ユーティリティ ライブラリ

- ハードウェアのデバッグ用に 2 つのデータ ムーバーを追加。

- LoadDdrToStreamWithCounter: AXI ストリームを介して PL の DDR から AI エンジンにデータをロードし、AI エンジンに転送するデータ数を記録する。

- StoreStreamToMasterWithCounter: AXI ストリームを介して AI エンジンからデータを受け取り、PL の DDR に保存して、DDR に転送するデータ数を記録する。

AI エンジン API

- C++ ヘッダー オンリー ライブラリとして実装される。このライブラリは、効率的な AI エンジンの組み込み関数に変換されるデータ型と動作を提供する。

- パラメーター指定可能なデータ型により、汎用プログラミングが可能

- 一般的な演算は、データ型が異なっても共通の方法でインプリメント可能

- 高レベルのプリミティブを最適化された AI エンジンの組み込み関数へ透過的に変換

- AI エンジン アーキテクチャ間での移植性を改善

AI エンジン API は AI エンジン カーネルのプログラミングに不可欠となる

高レベルの最適化

AI エンジン コンパイラの最適化オプション

- --xlopt=0 最適化は適用されない。

- --xlopt=1 ヒープ サイズの自動計算、LLVM IR 解析からガイダンスを生成。

- --xlopt=2 自動インライン展開、展開されたループに対するループ ピーリング、プラグマ挿入。

性能を向上させるために --xlopt=2 を導入。ただしデフォルトは --xlopt=1。

- 自動インライン展開

- 関数に __inline または inline が使用されていなくても、有益で可能な場合に関数を自動的にインライン展開する。

- プラグマの自動挿入

- カーネル コードに自動的にプラグマを挿入する。(詳細は、次のスライドを参照)

プラグマ推論

カーネルの最適化に不可欠

- 有効で適切な chess プラグマの挿入が求められるユーザーの負担を軽減する

2021.2 で 5 つのプラグマの自動推論をサポート

- 性能:

- chess_prepare_for_pipelining は、最内周ループ、およびトリップカウントがわかっている外周ループ。

- chess_loop_range は、トリップカウントがわかっているループ。

- chess_unroll_loop/chess_flatten_loop は、トリップカウントが分かっている最内周ループ。

- 適正:

- chess_unroll_loop_preamble は、トリップカウントが指定した展開係数の倍数でない場合。

グラフ プログラミング モデル PLIO および GMIO を更新

モデルの変更点:

- simulation::platform の使用方法が変更

- グラフ内の PLIO/GMIO オブジェクトとの相互作用、位置によって入力/出力が決定。

- グラフ内のグローバル PLIO/GMIO オブジェクトが変更。

- グラフの connect<> 文が変更。

ADF グラフの PLIO/GMIO

最新

- PLIO、GMIO、simulation::platform、および接続をグローバル スコープで記述

GMIO gm0(“GMIO_In0”, 64, 1);

GMIO gm1(“GMIO_In1”, 64, 1);

…

GMIO gm7(“GMIO_In7”, 64, 1);

PLIO pl0(“PLIO_Out0”, plio_32_bits, “data/output0.txt”, 250.0);

PLIO pl1(“PLIO_Out1”, plio_32_bits, “data/output1.txt”, 250.0);

…

PLIO pl7(“PLIO_Out7”, plio_32_bits, “data/output7.txt”, 250.0);

simulation::platform<8,8> plat(&gm0, &gm1,…, &gm7, &pl0, &pl1,…, &pl7,);

subgraph g;

connect<> net0(plat.src[0], g.in[0]);

connect<> net1(plat.src[1], g.in[1]);

…

connect<> net7(plat.src[7], g.in[7]);

connect<> net8(g.out[0], plat.sink[0]);

connect<> net9(g.out[1], plat.sink[1]);

…

connect<> net15(g.out[7], plat.sink[7]);

別の方法

- 最上位グラフを作成し、PLIO、GMIO、および接続を内部に移動

- for ループ内で接続を操作可能

class topgraph

{

input_gmio gm[8];

output_plio pl[8];

subgraph sg;

topgraph()

{

for (i=0; i<8; i++)

{

gm[i] = input_gmio::create(“GMIO_In”+std::to_string(i), 64, 1);

pl[i] = output_plio::create(“PLIO_Out”+std::to_string(i), plio_32_bits, “data/output”+std::to_string(i)+”.txt”, 250.0);

connect<>(gm[i].out[0], sg.in[i]);

connect<>(sg.out[i], pl[i].in[0]);

}

}

};

topgraph g;

エリア グループ制約の改善

ADF グラフでフラグを使用したり、制約ファイルを使用して、マッパーやルーターを制御可能

- -contain_routing – true を指定すると、nodeGroup 内のノード間のネットを含むすべての配線が、エリア グループ内に含まれるようになる。

- -exclusive_routing - true を指定すると、nodeGroup からノード間のネットを除く、すべての配線がエリア グループから除外される。

- -exclusive_placement - true を指定すると、nodeGroup に含まれていないすべてのノードが、エリア グループの境界ボックス内に配置されなくなる。

スナップショット

スナップショットとは、すべてのカーネル ポートに関するコメントおよびデータを含むテキスト ファイル

- ストリーム、パケット ストリーム、カスケード ストリーム

- ウィンドウ、バッファー

- RTP

すべてのプラットフォーム ポートも含まれる

- PLIO、GMIO、RTP

ユーザーは、デバッガーを使用せず、またカーネル コードの計測を必要とせずに、カーネル ポートのデータ トラフィックを確認できようになる

デッドロックの検出

- 入力データが不十分な場合や再収束パス上の FIFO 深度が不均衡な場合に x86 シミュレーションでデッドロックを検出する

- オプションの --stop-on-deadlock を指定して、x86 シミュレーション中の stop-on-deadlock 機能を有効にする必要がある

- デッドロックでシミュレーションが停止すると、オプションの -trace --timeout を指定して再実行するようにエラー メッセージが表示される

メモリ アクセス違反の検出

Valgrind を統合してメモリ アクセス違反を検出

- 検出

- 境界外の読み出し/書き込み

- 初期化されていないメモリの読み出し

- コンパイルに必要な特定フラグがない

- シミュレーション フラグ:

- --valgrind : 通常どおりにシミュレーションが実行され、valgrind がレポートを表示する

- --valgrind-gdb: 同じだが、gdb によるデバッグが同時に実行される

トレース レポート

デッドロック状態になると、シミュレーションの出力が不十分となり、バグの原因分析が難しくなる

X86 シミュレーションのトレース オプションを使用する場合、シミュレータは多様なタイムスタンプ情報を記録できる

- カーネル反復の開始/終了

- ストリーム ストールの開始/終了

- ロック ストールの開始/終了

x86 シミュレーションと AI エンジン シミュレーションでは、タイムスタンプが異なる

ユーザー制御のバースト推論

- Vitis HLS ツールによる自動バースト推論に満足できない場合は、新しく導入された手動のバースト最適化を利用可能

- 新しいクラスの「hls::burst_maxi」がバースト ビヘイビアーの手動制御をサポートする。新しいクラスに使用する新しい HLS API が提供されている

- ユーザーは、HLS デザインの AXI AMBA プロトコルおよびハードウェア トランザクション レベル モデリングについて理解している必要がある

タイミングおよび QoR の機能強化:

- 高位のスループット制約を入力できる

- HLS のタイミング見積もり精度が向上。HLS がタイミング クロージャをレポートするときには、Vivado の RTL 合成でもタイミングを満たしている

EoU の機能強化

C 合成レポートにインターフェイス アダプター レポートを追加

- インターフェイス アダプターがデザインに与えるリソース インパクトについて、ユーザーが把握する必要がある

- インターフェイス アダプターにはデザインの QoR に影響を与える可変のプロパティがある

- これらのプロパティの中には、ユーザーに報告すべき関連付けられたユーザー制御がある

- bind_op レポートと bind_storage レポートのテキスト版を提供

合成レポートに新しいセクションが追加され、プラグマ リストとプラグマに関する警告を表示

- ユーザーは問題があるプラグマを簡単に識別できる。

解析およびレポート機能の強化

関数呼び出しグラフ ビューアーの新機能

- マウス ドラッグによる拡大/縮小機能

- グラフ全体を表示し、部分的に拡大表示できる Overview 機能

- シミュレーション データと共にすべての関数とループが表示される

シミュレーション後に Timeline Trace ビューアーが利用可能になりました。このビューアーでデザインのランタイム プロファイルを表示できます。ユーザーは Vitis HLS GUI からそのままアクセス可能です。

リンク サマリが改善

- AI エンジン、プラットフォーム、演算ユニットのクロック周波数情報を提供

- 新しい表「Clocks in system diagram and platform diagram」を提供

プラットフォームのエクスポートが改善

- XSA ファイルを Vivado からエクスポート可能で、ローカルにソース ファイルは不要

- XSA ファイルを Vivado からエクスポート可能で、プロジェクト構造の変更はない

- IP リポジトリ全体をパッケージ化するのではなく、ハードウェア プラットフォーム プロジェクトで使用される IP をパッケージ化する

AI エンジン アプリケーションのエミュレーション機能が強化

- aiesimulation への外部テストベンチの統合をサポート

- x86 シミュレーションへの外部テストベンチの統合をサポート

- x86 シミュレーションでの GDB デバッグの実行をサポート

- x86 シミュレーションのグラフでカーネル間のデータのスナップショットをサポート

- x86 シミュレーションでアクセス違反チェックをサポート

- x86 シミュレーションでデッドロック時の停止に対応

AI エンジン トレースをサポート

AI エンジン アプリケーションの SW エミュレーションをサポート

Verilog/System Verilog の外部トラフィック ジェネレーターをサポート

プロファイリング モニターを挿入してメモリを監視

- 現在、プロファイリング モニター ロジックは、カーネル/CU ポート ベースに挿入可能。この機能により、ユーザーがメモリ インターフェイスに直接モニター ロジックを挿入できようになる

- 可視化されたメモリ インターフェイスのメモリ帯域幅をプロファイル サマリ レポートに反映できる

- DDR メモリと PLRAM をサポート

- ハードウェア フローをサポート

- この機能を有効にするには、リンク段階と XRT の両方で設定が必要

- memory=all

- data_transfer_trace= coarse|fine or

- opencl_device_counter=true

プロファイリング モニターを挿入してメモリを監視

- メモリ インターフェイスの監視を可能にする vadd サンプル

- 新しい表「Memory Bank Data Transfer」を提供

Vitis アナライザーの強化

OpenCL 以外のアプリケーション向けに生成される一般的なプロファイル サマリ レポート

- XRTAPI と HALAPI アプリケーションに同レベルのサポートを提供する。

- ユーザーが希望するレポートの種類を選択すると、ツールが自動的に生成して、Vitis アナライザーで可視化する。

PL イベントのタイムラインに OpenCL コマンドを追加

- プロファイリングはオーバーヘッドを増加するが、XRT でオーバーヘッドなしにタイムライン トレースに OpenCL イベントをダンプできる。

- Vitis アナライザーが XRT 出力を処理し、Timeline Trace ビューアーに表示する。

- xrt.ini で xocl_debug=true に設定する必要がある。

タイムライン トレース レポートの信号の階層をフラット化

- デフォルトでは、タイムライン トレース レポートの信号が階層的に表示される。

- Vitis アナライザーでは、「Flatten Signal」に切り替えることで階層をフラット化できる。

- タイムライン トレースをフラットにした場合、波形を比較できる。

Vitis アナライザー – データの可視化

- AI エンジン デザインで AI エンジン カーネルへの入力/出力データを表示

- 入出力データを時系列で表示し、AI エンジン デザインのデバッグに役立つ

- aiesimulator と連携

- サポート

- ウィンドウ/ストリーム/カスケード データ型

- パケット ストリーム

- テンプレート化されたカーネル

- データ ダンプ ユーティリティ

Vitis アナライザー – AI エンジンのストール解析

- Vitis アナライザーの視覚化機能を活用して、ストールの根本的な原因を特定できる

- サポート

- パフォーマンス メトリクス

- ロック ストールの解析

- ストリーム ストールの解析

- カスケード ストールの解析

- メモリ ストールの解析

- サポート フロー

- aiesimulator

- HW エミュレーション

ザイリンクス ランタイム ライブラリ (XRT):

- XRT API

- XRT ネイティブ API で xrt::ip を使用したユーザー管理のカーネル制御が可能

- XRT ユーティリティ

- xbutil および xbmgmt ツールがデフォルトになる

- レガシ ユーティリティを使用するには、レガシ サブコマンドを持つ xbutil --legacy または xbmgmt --legacy を使用する

- 新しいユーティリティ xball

- インストールされているデータセンター カードのすべてまたは一部に xbutil または xbmgmt コマンドを適用。詳細は、xball --help を参照

- 新しいコマンド xbutil configure

- PCIe ホスト メモリおよび PCIe ピアツーピア機能を有効化、無効化、または構成。詳細は、XRT 資料を参照

- すべての XRT ユーティリティで、ユーザーの介入をスキップする --force オプションをグローバルにサポート。

- xbutil および xbmgmt ツールがデフォルトになる

- プロファイリング

- プロファイリング オプションをイネーブルにしたときにプロファイル サマリ レポートを生成。

- 該当するサマリ表およびガイダンスは、xrt.ini ファイルでイネーブルにしているプロファイリング オプションに基づいて生成される。

- 新しいデータ転送サマリ表により、デザインのメモリ リソースにモニターが追加されたときのメモリ リソースに関する集約情報を提供。

- 新しいプロファイリング メトリック セットにより、(1) AIE の浮動小数点例外、(2) タイル実行カウント、(3) ストリームの入力および取得など、さまざまなイベントをカウント。

- エンベデッド

- sptag をサポートするため zocl メモリ マネージャーを改善。

Vitis XRT による AI エンジンの複数プロセス サポート

- C および C++ API でアクセス モードを定義して、複数プロセスが同じ AI エンジン アレイやグラフへのアクセスを共有できる。

- AI エンジンのアレイとグラフへの不明なアクセスを防止する。

- AI エンジンのアレイおよびグラフへのアクセス モードは 3 つある

- Exclusive Mode (ほかのプロセスからのアクセスを防ぐ)

- Primary Mode (その他のプロセスによる非破壊的アクセスのみを許可)

- Shared Mode (非破壊的アクセスのみ可能)

- 複数プロセスのサポートが必要な場合に考慮すべき事項。例:

- その他のプロセスによる AI エンジン アレイへのアクセスを防止する (排他的アクセス)

- 複数ユーザーが異なるグラフを別々に制御する (複数アプリケーション サポート)

- プライマリ ユーザーがグラフを制御し、その他のユーザーは実行ステータスを確認できる (プライマリ/共有アクセス)

Vitis XRT による AI エンジンのサポート ステータス

C および C++ API

- C バージョンの API

- AI エンジン アレイの場合:

- xrtAIEDeviceOpenExclusive (Exclusive モード)

- xrtAIEDeviceOpen (Primary モード)

- xrtAIEDeviceOpenShared (Shared モード)

- AI エンジン グラフの場合:

- xrtGraphOpenExclusive (Exclusive モード)

- xrtGraphOpen (Primary モード)

- xrtGraphOpenShared (Shared モード)

- AI エンジン アレイの場合:

- C++ バージョンの API

- xrt::aie::device クラスがコンストラクターでアクセス モードをサポート

- enum class access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2 };

- xrt::graph クラスがコンストラクターでアクセス モードをサポート

- enum class access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2, none = 3 };

- xrt::aie::device クラスがコンストラクターでアクセス モードをサポート

- Alveo カードの最新の Vitis ターゲット プラットフォームにアクセスし、アクセラレータ カードの「設計開始」セクションを参照。

- Vitis をダウンロードして Alveo パッケージ セクションを参照

AI エンジン DSP ライブラリ – 新しいブロック

- AIE DDS

- AIE Mixer

並列コンパイル

- 2021.1 より時間が短縮 (次の数値は 200MHz TX チェーンの例)

- コンパイルとシミュレーションの時間が 3 分の 1 に短縮

- コンパイル時間が 7 分の 1 に短縮

- シミュレーション後のデッドタイムが 25 秒から 0 秒に短縮

制約エディターの機能強化

- 2021.2 でナビゲーション機能が改善

To Fixed Size ブロックが改善

To Variable Size ブロックが改善

論理回路の協調シミュレーション機能が強化

- AI エンジンの入力用に Matlab データをエクスポート - xmcVitisWrite

- AI エンジン データを Matlab にインポート - xmcVitisRead

- AI エンジン データを Matlab にインポート - xmcVitisRead

その他

- 入力 (ソース ブロック) なしで、AI エンジンまたは HLS カーネル ブロックをインポート

- 新しいデータ型をサポート

- AMD のデータ型 x_sfix64 および x_ufix64 の代わりとなる、AI エンジン開発用の Simulink のネイティブ データ型 int64 および uint64

- AI エンジン開発用の accfloat および caccfloat

- Ubuntu 20.04 のサポート

- MATALB 20a、20b、21a のサポート (MATLAB 21b は対象外)

- 新しいサンプルの追加

- 64 個のカーネルを使用するデュアル ストリーム SSR フィルターの例

- 疑似逆行列 (64x32) – commslib の例

- xmcLibraryPath コマンドを使用して、カスタム DSPLib の場所を指定する

- その他多数の機能強化とバグ修正

Vitis ソフトウェア プラットフォーム 2021.1 リリースのハイライト:

- AMD Kria SOM (システム オン モジュール) KV260 ビジョン AI スターター キットをサポート。ML (DPU 推論エンジン) + X (RTL カーネルと Vitis HLS ベースのコンピューター ビジョン カーネル) のための完全 Vitis フロー。詳細 >

- CPU/GPU より優れた FPGA や Versal ACAP 用の新しい C/C++ Vision、DSP、Graph (Louvain Modularity)、Codec による画像処理、圧縮 (GZIP、Facebook ZSTD、ZLIB アプリケーション全体の高速化) のパフォーマンス最適化ライブラリをサポート。

- Vitis™ コア開発キットでは、Versal ACAP デバイスを使用するデザイン フローを強化: AI エンジン デザインのトレース レポート視覚化を改善、GMIO を使用する AI エンジン イベント トレース、インクリメンタル リコンパイル、新しいブート イメージ ウィザード、暗号化された AI エンジンのソース ファイルをサポート。

- 新しい Vitis Model Composer ツールは、MathWorks の MATLAB および Simulink® 環境内でデザインをすばやく試行して検証でき、AI エンジンやプログラマブル ロジックなどのブロックの協調シミュレーション、コード生成、およびテストベンチの作成が可能。

- Vitis HLS の新しい Flow Navigator GUI を使用して、各フェーズやレポートにすばやくアクセス。合成、解析、デバッグの各ビューを一般的なデフォルト コンテキストに統合。

Vitis 最新情報 (カテゴリ別)

次の各セクションを展開して AMD Vitis 2021.1 の新機能と拡張機能の詳細を確認してください。サポートされているプラットフォーム、動作の変更、既知の問題については、Vitis ソフトウェア プラットフォーム 2021.1 リリース ノートのアプリケーション アクセラレーション フローおよびエンベデッド ソフトウェア開発フローを参照してください。

注記: Vitis アクセラレーション ライブラリは、個別にダウンロードして入手します。これらは、GitHub からダウンロードできますが、Vitis IDE 内で直接ダウンロードすることも可能です。

AIE DSP

- DSP ライブラリが Vitis アクセラレーション ライブラリ セットの一部として GitHub で公開されています。

- DSP ライブラリには、多くの高度な信号処理アプリケーションで使用される、一般的なパラメーター指定可能な DSP 関数が含まれています。現在、これらの関数はすべて、ストリーミング インターフェイス対応のウィンドウ インターフェイスをサポートしています。

FIR フィルター

機能 |

名前空間 |

シングル レート、非対称 |

dsplib::fir::sr_asym::fir_sr_asym_graph |

シングル レート、非対称 |

dsplib::fir::sr_sym::fir_sr_sym_graph |

補間非対称 |

dsplib::fir::interpolate_asym::fir_interpolate_asym_graph |

デシメーション、ハーフバンド |

dsplib::fir::decimate_hb::fir_decimate_hb_graph |

補間、ハーフバンド |

dsplib::fir::interpolate_hb::fir_interpolate_hb_graph |

デシメーション、非対称 |

dsplib::fir::decimate_asym::fir_decimate_asym_graph |

補間、分数、非対称 |

dsplib::fir::interpolate_fract_asym:: fir_interpolate_fract_asym_graph |

デシメーション、対称 |

dsplib::fir::decimate_sym::fir_decimate_sym_graph |

FFT/iFFT - この DSP ライブラリには、FFT/iFFT ソリューションが 1 つ含まれています。シングル チャンネル、シングル カーネルの DIT (Decimation in Time) であり、ポイント サイズ、複雑なデータ型、カスケード長、FFT/iFFT 関数を指定できます。

機能 |

名前空間 |

シングル チャネル FFT/iFFT |

dsplib::fft::fft_ifft_dit_1ch_graph |

行列乗算 (GeMM) - この DSP ライブラリには、Matrix Multiply/GEMM (一般行列乗算) ソリューションが 1 つ含まれています。2 つの行列 A と B の行列乗算をサポートするもので、派生した出力データ型を生成する入力データ型を指定できます。

機能 |

名前空間 |

Matrix Mult/GeMM |

dsplib::blas::matrix_mult::matrix_mult_graph |

ウィジェット ユーティリティ - これらのウィジェットは、DSP ライブラリ関数への入力に関するウィンドウとストリームの変換、DSP ライブラリ関数の出力に関するストリームとウィンドウの変換をサポートします (実数と複素数のデータ型変換のために追加されたウィジェット)。

機能 |

名前空間 |

ストリームからウィンドウ/ウィンドウからストリーム |

dsplib::widget::api_cast::widget_api_cast_graph |

実数から複素数/複素数から実数 |

dsplib:widget::real2complex::widget_real2complex_graph |

Vitis Model Composer では DSP ライブラリ関数をサポートしているため、ユーザーはこれらの関数を Matlab/Simulink 環境にプラグインするだけで、簡単に AI エンジン DSP ライブラリを評価したり、AI エンジン ADF グラフを開発できます。

Vitis HPC ライブラリのリリースでは、FPGA ベース HPC アプリケーション向けに HLS プリミティブ、ビルド済みカーネル、ソフトウェア API を提供しています。これらのアプリケーションを次に示します。

2D Acoustic RTM (Reverse Time Migration) FDTD (Finite Difference Time Domain) アルゴリズム (フォワード カーネルとバックワード カーネルを含む)

3D Acoustic RTM (Reverse Time Migration) FDTD (Finite Difference Time Domain) アルゴリズム (フォワード カーネルを含む)

MLP (多層パーセプトロン) コンポーネント: 活性化関数と完全接続ネットワーク カーネル

密行列と疎行列の両方に対応する PCG (Preconditioned Conjugate Gradient) ソルバー

- 最初のリリースに含まれる Versal AI Engine 向けの一部のビジョン関数:

利用可能な関数

Filter2D

absdiff

累積

accumulate_weighted

addweighted

blobFromImage

colorconversion

convertscaleabs

erode

gaincontrol

gaussian

laplacian

pixelwise_mul

threshold

zero

xfcvDataMovers : 高解像度画像のタイリングを容易にし、AI エンジン コアのローカル メモリに転送するためのユーティリティ データ ムーバーです。2 種類のバリエーション

- PL カーネルを使用: 追加で PL リソースを使用する必要がありますが、高スループットを実現できます。

- GMIO を使用: PL カーネルを使用する場合よりスループットは低下しますが、Versal NoC (ネットワーク オン チップ) を使用するため、PL リソースは不要です。

- 新しいプログラマブル ロジック (PL) の機能と特長

- ISP パイプラインと機能:

- 2020.2 非 HDR パイプラインが改善

- 動作中に一部の ISP パラメーターを変更可能: 赤色/青色チャネルのゲイン パラメーター、AWB の有効/無効オプション、R/G/B のガンマ テーブル、AWB 正規化のために最小/最大を計算するためのピクセル値 (%pixels)。

- ガンマ補正と色空間変換 (RGB2YUYV) がパイプラインの一部となっています。

- 新しい 2021.1 HDR パイプライン: 2020.2 パイプライン + HDR サポート

- 短時間露光フレームと長時間露光フレームのデジタル オーバーラップを使用するセンサーに対応する二重露光の HDR マージ。

- 4 つのベイヤー パターンをサポート: RGGB、BGGR、GRBG、GBRB

- HDR マージ + isp パイプライン (ランタイム コンフィギュレーション オプション付き)。RGB 出力を返します。

- 抽出機能: HDR 抽出機能は前処理機能であり、入力としてデジタル オーバーラップ ストリームを 1 つ受け取り、2 つの出力露出フレーム (SEF、LEF) を返します。

- 短時間露光フレームと長時間露光フレームのデジタル オーバーラップを使用するセンサーに対応する二重露光の HDR マージ。

- 3DLUT: 色相、彩度、輝度などの複雑な色演算子を制御するための入出力マッピングを提供します。

- CLAHE: Contrast Limited Adaptive Histogram Equalization は、適応型ヒストグラム均等化を行う際にコントラストを制限することで、ほぼ一定の領域でコントラストを過剰に増幅しないようにする手法です。これにより、ノイズの問題も軽減されます。

- 2020.2 非 HDR パイプラインが改善

- 反転: 水平/垂直方向に画像を反転させます。

- カスタム CCA: 果物の欠陥を検出するための、カスタム バージョンの連結成分解析アルゴリズムです。果物の欠陥部分の計算とは別に、欠陥ピクセルと果物全体のピクセルを計算します。

- Canny の更新: Canny 関数が任意の画像解像度に対応するようになりました。

ライブラリ関連の変更点

- すべてのテストが OpenCV 3.4.2 の使用から OpenCV 4.4 の使用に対応できるようにアップグレードされました。

- Versal エッジ シリーズ (VCK190) のサポートが追加されました。

- ベンチマーキング セクションが更新され、リリースされたパイプライン/関数のベンチマーキング コラテラルが含まれています。

2021.1 リリースでは、Two-Gram テキスト分析を提供:

TGP (Two Gram Predicate) は、2 文字で転置インデックスを用いた検索を実行します。転置インデックスが確立されているデータセットでは、転置インデックスの各レコードの中から一致する ID を見つけることができます。

- コミュニティの検出: Louvain Modularity

- 2-Hop 検索

N/A

- L2 カーネルによる倍精度 SpMV (疎行列ベクトル積) の実装が追加されています。

2021.1 リリースでは、GQE で次の機能をアーリー アクセス サポートとして対応しています。

64 ビット結合: gqeJoin カーネルとそれに付随する gqePart カーネルが 64 ビットのキーとペイロードに拡張され、より大規模なデータをサポートできるようになりました。

初期ブルームフィルター サポート: gqeJoin カーネルには、ブルームフィルター プロービングを実行するモードがあります。これにより、初期段階でのデータサイズの最小化が重要になる特定のマルチノード フローを効率化します。

現在、これらの機能は L3 の純粋なソフトウェア API として提供されています。対応する L3 テストケースをご確認ください。

- GZIP マルチコア圧縮:

- 新しい GZIP マルチコア圧縮ストリーミング アクセラレータは、純粋なストリームのみのソリューション (フリーランニング カーネル) であり、4 KB、8 KB、16 KB、32 KB の異なるブロック サイズをサポートする豊富なバリエーションを備えています。

- Facebook ZSTD 圧縮コア:

- ブロック サイズが 32 KB の新しい Facebook ZSTD シングル コア圧縮アクセラレータです。より高いスループットを達成できるマルチコア ZSTD 圧縮を現在開発中です。

- GZIP 低レイテンシ解凍:

- 新バージョンの GZIP 解凍は、各ブロックのレイテンシが改善され、リソース使用率を削減でき (LUT は 35% 減、BRAM は 83% 減)、FMax が向上しています。

- ZLIB アプリケーション全体を高速化 (U50 を使用):

- U50 プラットフォーム向けの L3 GZIP ソリューションであり、6 つの圧縮コアを搭載し、PCIe 帯域幅を最大限に活用します。CPU libz.so ライブラリを高速化するための効率的な GZIP SW ソリューションが提供されているため、再コンパイルすることなく、エンドカスタマー ソフトウェアとのシームレスな API レベルの統合が可能になります。

- Versal プラットフォームをサポート

- AIE サポートが追加されています - 上記を参照してください。

- 2021.1 リリースで提供するサポート: BLS 向けの * RIPEMD160 * イニシャル サポート (未完成)

- 2021.1 リリースでは、データ ムーバーがこのライブラリに追加されています。この機能は、その他の C++ ベース API とは異なり、HLS ベースのカーネル設計の経験が少ない方を対象としており、ストリームベースのデザインを検証することをサポートします。データ ムーバーは、実際にカーネル ソース コードを生成する機能があり、AIE デバイスのようなデザインを駆動したり検証したりするための一般的なヘルパー カーネルの一覧を作成します。

- QoR メトリクスを作成 (Vitis QoR 生成 API)

- アプリケーション カーネルのサイクル

- ストール サイクル (VCD ファイルから計算)

- ラッパーでのオーバーヘッド サイクルを計測 (カーネル本体以外の機能にかかる時間)

- スループット

- 3 段階の最適化機能 XLOPT=0、1 (デフォルト)、2

- xlopt=2 の新機能:

- ループ フュージョン、単一反復の外側ループ平坦化、ループ ピーリング ヒューリスティックの強化

- 「__restrict」 の使用法を分析してガイダンスを提供する

- インクリメンタル リコンパイル: グラフが変わらない場合に、変更されたカーネルのみを再コンパイルする

- パケット交換式データ → 最大 32 分割 (従来は、最大 4 分割)

- 新しい DMA FIFO ロケーション制約 (リリース間のマッパー/ルーターの変更による性能への影響はない)

- 新しいコンパイルの制約条件としてマッピング ソリューションを使用: 性能に影響を与えるマッピングの変更を回避するため

- x86sim の機能サポートを aiesim レベルにする

- ADF グラフにおける PL カーネルの非推奨を開始 (2021.2 で非推奨を完了)

- フローのフェーズやレポートにすばやくアクセスできる新しい Flow Navigator GUI 合成、解析、デバッグの各ビューを一般的なデフォルト コンテキストに統合

- BIND_OP および BIND_STORAGE ディレクティブ用の新しい合成レポート セクション

- 合成後の新しいテキスト レポートには、GUI 合成レポートに提供される情報が反映される

- IP エクスポートや Vivado インプリメンテーション run のウィジェットが新しくなり、設定ファイルや制約ファイルを Vivado へ渡すオプションが追加されている

- 関数やループを可視化するための新しい関数呼び出しグラフ ビューアーでは、II、レイテンシ、DSP/BRAM の使用率をオプションのヒートマップでハイライトできる

- DSP ブロックのネイティブ浮動小数点演算用に Versal タイミング キャリブレーションと新しい制御機能 (config_op の -precision オプション)

- Vitis HLS 移行ガイド (旧 UG1391) が UG1399 の第 1 章に含まれる

- ユーザー ガイド (UG1399 およびウェブ) に新しい設計手法のセクションを追加

- 代替のフラッシュ可能なパイプライン オプションが改善 (フリーランニング パイプライン、通称 「frp」)

- Vitis では、最上位ポート ポインターを、グローバル メモリではなく、axi-lite アダプターにマッピング可能になる

- aggregate 指示子は、最大限のパッキングを行うための 「-compact bit」 オプションを提供する

- オプションのアンケートを使用して、[ヘルプ] メニューに [Leave Feedback] の項目を追加

- 一部の Linux システムで [Man Pages] タブに情報が表示されないというバグを修正

- Vitis では、m_axi インターフェイスの再形成を hls::vector 型で実行する必要がある

- s_axilite および m_axi データ ストレージ用の新たなカスタマイズ オプション ("auto"、"uram"、"bram"、"lutram") を使用して、デザイン内の RAM 使用率を微調整できる

- Vitis では、カーネル用に継続的に動作する新モードをサポート (つまり「終わらない」)

- セカンダリ クロック オプションの axi_lite が再び利用可能に

- Vivado IP パッケージャーで RTL カーネル パッケージング機能のサポートが強化

- 製品化および一般リリースされた機能であり、適切な手法と資料を提供している

デフォルトで XRT がカーネルを制御

入力として暗号化された AIE ソース ファイルをサポートする

AIE コンパイラは暗号化された AIE ソース ファイルを受け入れることができ、残りのフローは v++ で対応

- Versal デバイス用に Create Boot Image ウィザードのサポートを追加

- AI エンジンのプログラミングおよびデバッグにおけるいくつかの改善点

- マイクロ コード ラベルのオン/オフが可能

- ソース コードとマイクロ コード間の静的なクロスプロービング

- マイクロ コードの全体表示

- パイプライン ビューで情報が更新されるたびに、最後の PC を可視エリアに移動

- パイプライン ビューでのインストラクション データの整列

- [Disassembly] ビューに単一命令モードのアクションを追加

- プラットフォーム プロジェクト用のデフォルト BIF ファイルを生成できる

- SD および eMMC 用のプログラム フラッシュに Raw モード サポートを追加

- AI エンジン開発フローにインコンテクストのヘルプ メッセージを追加

- GCC ツールチェーンのバージョンを 10.2 にアップグレード

- ユーザーは、Python/C++ などの外部プロセスを使用して、AXI-MM マスター/スレーブをエミュレートできます。これにより、ユーザーは AXI マスターや VIP の開発にリソースを費やすことなく、AXI マスター/スレーブをすばやく設計してデザインをエミュレートできるようになります。AXI-MM プロセス間通信 (IPC) は、2 つの FPGA 間の Chip to Chip 接続をエミュレートするのにも役立ちます。

- VCS 用 Versal モデルのコンパイルが可能

- プラットフォーム開発者は、スタンドアロン アプリケーションを使用してプラットフォーム上でハードウェア エミュレーションを実行できるため、初期段階でプラットフォームをテストできます。

- ユーザー レンジ プロファイリング情報とユーザー イベント情報がプロファイル サマリ レポートに集約。

Vitis アナライザーでクリティカルなタイミング パスを表示。

Vitis アナライザーでは、Vivado プロジェクトやネットリストを開かなくても、Vivado GUI タイミング レポートの簡易版を表示できます。

Vitis アナライザーの複数ストラテジ サポート

複数のストラテジを実行した結果は、Vitis アナライザーで可視化されます。

- プロファイリングとデバッグ用の新しい xrt.ini スイッチ

大規模アプリケーションのメモリおよび読み込み時間を削減

新しいプロファイル ツールは、少ないリソースで大規模な csv ファイルを処理できるため、読み込み時間が短縮し、クラッシュの問題も回避できます。

PL 連続トレース オフロード機能の改善

トレース データを格納するメモリ リソースとして DDR または HBM を使用

大容量データの負荷軽減をサポートする循環バッファー

トレース バッファーのサイズとオフロードの間隔は、xrt.ini で設定可能

AIE デザインのトレース レポート可視化機能が改善

すべての AIE 入力が表示される (ウィンドウ、ストリーム、カスケード ストリームなど)

すべての IO データ型をサポート

- 安定したネイティブ XRT API であり、C++ API を使用して AIE グラフの制御と実行、ソフトウェア エミュレーション、トレーシングが可能になります。

- XRT の新しいヘルパー API は、OpenCL API から $XILINX_XRT/include/CL/cl2xrt.hpp の XRT ネイティブ API への移行をサポートします。

- XRT の新しい API xrt::device.get_info() を使用して、デバイスのプロパティを抽出できます。

- 大幅に改良された次世代型の xbutil および xbmgmt ユーティリティがデフォルトになりました。

- xbutil では、電源の状態をレポートできます。

- xbmgmt では、ランタイム クロックのスケーリングをサポートし、ボードやサーバーを保護するために消費電力しきい値を設定できます。

- sysfs、xbmgmt、xbutil では、Alveo ボードの MAC アドレスをレポートできます。

- xocl の KDS Scheduler がリファクタリングされ、複数デバイスの複数演算ユニットを同時に実行する多数のプロセスのスループットが大幅に向上します。レガシ シェルでは、スループットがわずかに低下する可能性があります。詳細は AR を参照してください。

- debugfs /sys/kernel/debug/xclmgmt/ および /sys/kernel/debug/xocl/ による XRT ドライバーのデバッグ トレース

Alveo アクセラレータ カード向けの最新 Vitis ターゲット プラットフォームに関する情報は、www.xilinx.com/alveo を参照してください。使用を検討しているアクセラレータ カードの「設計開始」セクションをご覧ください。

Vitis ターゲット プラットフォームの最新リリース情報は、『Alveo データセンター アクセラレータ カード プラットフォーム ユーザー ガイド』 (UG1120) を参照してください。

新しいプラットフォーム

- Alveo U200 Gen3x16 XDMA 1RP

- 名前: xilinx_u200_gen3x16_xdma_1_202110_1

- 特長: スレーブ ブリッジ、P2P、GT カーネル、DDR セルフリフレッシュ

- Alveo U50 Gen3x16 noDMA 1RP

- Name: xilinx_u50_gen3x16_nodma_1_202110_1

- 特長: スレーブ ブリッジ、P2P、GT カーネル、クロック スロットル

Vitis エンベデッド プラットフォーム

- VCK190 ベース プラットフォームでは、DDR と LPDDR に ECC 機能が付いているため制約が簡潔になる。

- MPSoC ベース プラットフォームでは、CMA のサイズが 1536M に増加。すべての Vitis AI モデルは、この CMA サイズに対応可能。

- エンベデッド プラットフォームの構築フローが簡素化: デバイス ツリー ジェネレーターによる ZOCL ノードの自動生成。XSCT で BIF ファイルを生成可能。ベース プラットフォームのソース ファイルが削減。

- Kubernetes(K8s) クラスターのサポート: Xilinx FPGA Resource Manager (XRM) で Kubernetes がサポートされました。これにより、1 つのサーバーに接続された複数の Alveo アクセラレータ カードのさまざまな計算ユニット (CU) を実行/管理できる、Alveo カードを使用して複数のサーバーにアプリケーションを拡張できます。

- 包括的な制約エディターを使用して、Vitis Model Composer で AI エンジン カーネルのあらゆる制約を指定できる。生成された ADF グラフに、これらの制約が含まれる。

- ライブラリ ブラウザーへ AI エンジン FFT ブロックと IFFT ブロックを追加。

- ライブラリ ブラウザーのさまざまな AI エンジン FIR ブロックを利用できる。

- FIR フィルターの入力ポートを使用して、フィルター係数を指定できる。

- 2 つの新しいユーティリティ ブロック (RTP Source と To Variable Size) を追加。

- 機能強化された AIE カーネル インポート ブロックは、テンプレート化された AI エンジン機能のインポートにも対応。

- Hub ブロックで、AI エンジン デザイン用 AMD プラットフォームを指定できる。

- Hub ブロックからは、AIE シミュレーション実行後にいつでも Vitis アナライザーを再実行できる。

- Simulink データ インスペクターを使用して、サイクルの概算出力を可視化し、各出力の推定スループットを確認できる。

- グラフ ヘッダー ファイルのみを使用してグラフをブロックとして取り込む際の操作性が向上。

- キャンセル ボタンが付いて進捗状況バーが刷新。

- MATLAB の作業ディレクトリとモデルのディレクトリが異なる場合に、AI エンジン カーネルのインポートやデザインのシミュレーションを行う際の操作性が向上。

- 新しい TX チェーン 200 MHz の例。

- HLS、HDL、AI エンジン ブロックを使用するデザインを紹介する新しい 2D-FFT の例。

HDL

- SSR FIR (10 倍以上) および SSRFFT のシミュレーション速度が向上

- RAM や FIFO などのメモリ ブロックのシミュレーション速度が向上

- ブラック ボックス インポート フローで Questa Simulator が VHDL 2008 に対応

全般

- Vitis Model Composer には AMD の System Generator for DSP の機能がすべて含まれています。 AMD System Generator for DSP を使用していたユーザーは、今後 Vitis Model Composer を使用して開発を続けることができます。

- MATLAB サポート - R2020a、R2020b、R2021a

Vitis ソフトウェア プラットフォーム 2020.2 リリースのハイライト

- Vitis 2020.2 は、Versal アダプティブ SoC プラットフォームをターゲットとするアプリケーションの高速化とエンベデッド ソフトウェア開発をサポート

- Vitis コア開発キットには、Versal AI エンジン用の C/C++ アプリケーションをコンパイルするための AI エンジン コンパイラが含まれる。Versal AI コア シリーズの AI エンジンは演算負荷の高いアプリケーション向けのベクトル プロセッサである

- Vitis HLS は、高速化されたカーネルのコンパイル (Vitis) と C/C++ から RTL IP を作成するフロー (Vivado) の両方をデフォルトでサポート

- 性能に最適化された 13 のライブラリで 600 個以上の FPGA アクセラレーション関数を提供。2020.2 では高性能コンピューティング アプリケーションの高速化をサポートする新しい Vitis HPC ライブラリが導入され、既存のデータ分析、グラフ、BLAS、スパース、セキュリティ、およびデータベース ライブラリも強化および拡張されている

- 最終的な FPGA バイナリを作成および強化するために複数のインプリメンテーション ストラテジを評価して、Vitis アプリケーション内で簡単に RTL カーネルを統合できる

- その他の強化には、AI エンジン アプリケーションのプロファイリング サポート、Vitis プロジェクトの Git バージョン管理、Vitis アナライザー内での Vitis AI プロファイラー データの統合、エミュレーション モードの機能強化などが含まれる。

- MATLAB® および Simulink® 用アドオン: AMD の Model Composer と System Generator for DSP を統合。AI エンジンは、MATLAB および Simulink にアドオンできる新しいドメイン

脚注

- 2023 年 8 月 10 日に実施したテストに基づいています。このテストでは、Vitis HLS のリリース 2023.2 と 2023.1 を使用して、Vitis L2/L3 コード ライブラリ デザイン 1000 個を対象に比較しました。テスト システムは、Intel Xeon E5-2690 v4 @ 2.6 GHz CPU、256 GB RAM、RedHat Enterprise Linux 8.6 で構成されています。実際のパフォーマンスは異なる可能性があります。システム メーカーの構成によって、異なる結果が生じる場合があります。-VGL-04

- 2023 年 2 月 12 日時点で存在する 1208 個すべての Vitis L1 ライブラリの C コード デザインに対してベンチマーク テストを実施しました。すべてのデザインは、CentOS Linux を搭載した 2 つの Intel Xeon E5-2690 CPU を使用し、SMT が有効で Turbo Boost が無効に設定されたシステムを使用して実行しました。ハードウェアの構成がソフトウェアのテスト結果に影響を与えることはないと考えます。ソフトウェアやファームウェアの設定や構成によって結果が異なる可能性があります - VGL-03

- 2023 年 8 月 10 日に実施したテストに基づいています。このテストでは、Vitis HLS のリリース 2023.2 と 2023.1 を使用して、Vitis L2/L3 コード ライブラリ デザイン 1000 個を対象に比較しました。テスト システムは、Intel Xeon E5-2690 v4 @ 2.6 GHz CPU、256 GB RAM、RedHat Enterprise Linux 8.6 で構成されています。実際のパフォーマンスは異なる可能性があります。システム メーカーの構成によって、異なる結果が生じる場合があります。-VGL-04

- 2023 年 2 月 12 日時点で存在する 1208 個すべての Vitis L1 ライブラリの C コード デザインに対してベンチマーク テストを実施しました。すべてのデザインは、CentOS Linux を搭載した 2 つの Intel Xeon E5-2690 CPU を使用し、SMT が有効で Turbo Boost が無効に設定されたシステムを使用して実行しました。ハードウェアの構成がソフトウェアのテスト結果に影響を与えることはないと考えます。ソフトウェアやファームウェアの設定や構成によって結果が異なる可能性があります - VGL-03