- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

- 2020.2

- 2020.1

Points forts de la version 2025.2 de la plateforme software AMD Vitis™

Flux de conception amélioré avec les moteurs Versal™ AI Engine

- Améliorations de l'API AI Engine pour Versal AI Edge et série Versal AI Edge Gen2 (AIE-ML et AIE-ML v2)

- Nouveaux types de données et types de données améliorés

- Nouveau : Bloc à virgule flottante MX6

- Nouveau : Bloc à virgule flottante MX4

- Nouveau : cbfloat16 (émulé)

- Amélioré : cfloat et cbfloat16 (disponible dans les fonctions FFT et de multiplication de matrice)

- Amélioré : cint16 et cint32 (peut désormais utiliser les types de twiddle cint16 dans les FFT)

- Nouveaux types de données et types de données améliorés

- Programmation des mises à jour de modèles

- Création de tampon partagé en lecture seule

- Accès en lecture de tuile MEM répétée (AIE-ML et AIE-ML v2)

- Prise en charge DMA-FIFO dans AIE-ML et AIE-ML v2

- Les tampons ping-pong peuvent couvrir deux tuiles MEM adjacentes

(AIE-ML et AIE-ML V2) - Paramètres partagés pour la mémoire de tuile locale

- Améliorations de la commutation de paquets pour AIE-ML et AIE-ML v2

- Nouvelles fonctions et fonctions améliorées dans la bibliothèque de traitement de signal numérique pour les Versal AI Engines

- Nouvelle somme cumulée

- Nouvelle distance euclidienne

- Nouvelle approximation de fonction (appelée via la mise à jour RTP ou LUT)

- FIR TDM amélioré avec commutation de paquets (économise des PLIO)

- FFT 1D améliorée grâce à l'utilisation du moteur d'IA et du PL (réduit les ressources PL nécessaires)

- FIR amélioré (optimisation du débit)

- Routeur et mappeur AI Engine améliorés : le compilateur peut explorer différentes empreintes/dispositions pour une mise en œuvre plus efficace

Vérification simplifiée des conceptions Versal AI Engine

- Mises à jour du flux de travail de simulation fonctionnelle de Vitis avec prise en charge de C++ (accès anticipé)

- Hardware dans la boucle utilisant MATLAB® et le banc d'essai Python (accès anticipé)

Améliorations apportées à Vitis Model Composer pour les conceptions DSP AIE

- Mises à jour faciles à utiliser pour le flux de conception SSR avec les moteurs d'IA (accès anticipé)

- Blocs supplémentaires disponibles pour les moteurs d'IA et HDL :

- AIE, AIE-ML, AIE-ML v2

- Nouveau : Approximation de fonction

- Nouveau : Corrélation/Convolution

- Nouveau : Somme cumulée

- Blocs de bibliothèque HDL

- Amélioré : FFT (SSR natif à virgule flottante ajouté = 32, 64)

- Amélioré : FIR (prise en charge de l'interpolation de taux fractionnel avec SSR)

- AIE, AIE-ML, AIE-ML v2

Mises à jour de l'IDE Vitis pour le développement de systèmes embarqués

- API Python™ pour la mise à jour de la configuration de construction

- Exécutez l'API Vitis™ dans l'environnement Python

- Trace PS visible par défaut pour les cœurs pris en charge

- Amélioration du débogage : les valeurs mises à jour sont désormais mises en surbrillance dans les vues de visionnage et d'enregistrement

- Annuler ou terminer les tâches back-end

- Chemins de fichiers BSP de plateforme unifiés (Linux et Windows)

- Intégration de l'IA Theia (accès anticipé) : fournit l'infrastructure permettant aux développeurs d'utiliser leurs LLM et assistants de code préférés

- Création de plateforme DFX avec l'API Python

- Sauvegarde ou partage d'un espace de travail

- Journalisation améliorée des fichiers de configuration

- Nouveau composant « Projet d'intégration »

Nouveautés Vitis par catégorie

Développez les sections ci-dessous pour en savoir plus sur les nouvelles fonctionnalités et améliorations de la plateforme software AMD Vitis 2025.2. Pour plus d'informations sur les plateformes prises en charge, les changements de comportement et les problèmes connus, reportez-vous aux notes de publication de la plateforme software Vitis 2025.1 pour le flux d'accélération des applications et le flux de développement de softwares intégrés.

Fonctions améliorées de la bibliothèque DSP :

- Nouvelle somme cumulée

- Nouvelle distance euclidienne

- Nouvelle approximation de fonction (appelée via la mise à jour RTP ou LUT)

- FIR TDM amélioré avec commutation de paquets (économise des PLIO)

- FFT 1D amélioré avec AIE + PL (réduit les ressources PL nécessaires)

- FIR amélioré (optimisation du débit)

S'applique à :

- Versal™ AI Core avec AIE

- Versal AI Edge avec AIE-ML

- Série Versal AI Edge Gen2 avec AIE-ML v2

- Simulation fonctionnelle des sous-systèmes Vitis dans C++ (accès anticipé)

- Prise en charge améliorée de la mesure de la latence et du débit dans Vitis Analyzer, pour les conceptions AI Engine

- Contrôle d'exécution des partitions AIE indépendantes

- Mises à jour faciles à utiliser pour le flux de conception SSR avec les moteurs d'IA (accès anticipé)

- Blocs supplémentaires disponibles pour AI Engine et HDL :

- AIE, AIE-ML, AIE-ML v2

- Nouveau : Approximation de fonction

- Nouveau : Corrélation/Convolution

- Nouveau : Somme cumulée

- Blocs de bibliothèque HDL

- Amélioré : FFT (SSR natif à virgule flottante ajouté = 32, 64)

- Amélioré : FIR (prise en charge de l'interpolation de taux fractionnel avec SSR)

- Améliorations du pragma de performances

- Le pragma de performances s'optimisera désormais en fonction du nombre de déclenchements calculé par CSIM

- Les optimisations du pragma de performances peuvent être converties en directives dans un fichier de configuration

- Contrôle conditionnel des pragmas, y compris du pragma de performances

- Nouvelle prise en charge IP

- SSR à fréquence fractionnelle pour FIR et FFT - Pour FFT, le relais statique dans SPFP32 prend désormais en charge jusqu'à SSR=64.

- Prise en charge ECC pour les tampons de flux de données implémentés avec la RAM en mode bloc ou UltraRAM

- Fonctionnalités faciles à utiliser

- Prise en charge du redémarrage automatique dans CSIM et CoSim

- Cache multiport pour M-AXI

- Nouvelles API pour les flux AXI avec signaux de bandes latérales

Points forts de la version 2025.1 de la plateforme software AMD Vitis™

Flux de conception amélioré avec les moteurs Versal AI Engine

- Nouvelles fonctions de bibliothèque DSP améliorées, API de moteur AI Engine et prise en charge de nouveaux types de données

Série Versal AI Core avec AIE :

- GEMV et FFT améliorées pour moteur AI Engine utilisant une architecture AIE parallèle 2D + logique programmable (PL) (adaptée au canaliseur polyphasé)

- Tri bitonique vectorisé SIMD, corrélation, convolution

Série Versal AI Edge avec AIE-ML :

- FFT pour AIE-ML à l'aide de l'architecture AIE-ML + PL parallèle 2D (adaptée au canaliseur polyphasé)

- Tri bitonique vectorisé SIMD, corrélation, convolution

Série AI Edge Gen2 avec AIE-ML v2 :

- 2D FFT AIE-ML v2 + PL v1 (adaptée aux canaliseurs polyphasés)

- FIR TDM (adapté aux canaliseurs polyphasés)

- GEMM/GEMV

- FIR à débit unique

- FIR à demi-bande

- FIR à rééchantillonnage fractionnel

- Changement de débit FIR

- FFT/iFFT

- DFT

- Mélangeur DDS

- Approximation de fonction

Mises à jour de la programmation AI Engine :

- Spécifications des paramètres de morcellement pour la mémoire locale

- Temps de compilation réduits lors du changement de banc d'essai

- Pipelining plus rapide pour la conception à l'aide de tampons ping-pong en DDR dans AIE-ML

- Autres améliorations de l'accès à la mémoire dans AIE-ML

Vérification simplifiée des conceptions Versal AI Engine

- Simulation fonctionnelle des sous-systèmes Vitis dans MATLAB® et Python™

- Prise en charge améliorée de la mesure de la latence et du débit dans Vitis Analyzer, pour les conceptions AI Engine

- Contrôle d'exécution des partitions AIE indépendantes

Améliorations apportées à Vitis Model Composer pour les conceptions DSP AIE

- Prise en charge de plusieurs sous-systèmes d'AI Engine de premier niveau

- Blocs supplémentaires disponibles pour AIE et HDL, y compris FFT améliorée avec modes SSR supplémentaires et Complex Multipliers utilisant moins de ressources DSP58

Mises à jour de l'IDE Vitis pour le développement de systèmes embarqués

- L'IDE Vitis Unified (nouvelle GUI) sera défini par défaut - L'IDE Vitis classique est abandonné

- Prise en charge de chaînes d'outils tierces telles que GCC et ARMClang

- Des outils de productivité tiers peuvent désormais être installés et sont accessibles via un utilitaire Marketplace dans l'IDE Vitis

Nouveautés Vitis par catégorie

Développez les sections ci-dessous pour en savoir plus sur les nouvelles fonctionnalités et améliorations de la plateforme software AMD Vitis 2025.1. Pour plus d'informations sur les plateformes prises en charge, les changements de comportement et les problèmes connus, reportez-vous aux notes de publication de la plateforme software Vitis 2025.1 pour le flux d'accélération des applications et le flux de développement de softwares intégrés.

Série Versal AI Core avec AIE :

- GEMV et FFT améliorées pour moteur AI Engine utilisant une architecture AIE parallèle 2D + logique programmable (PL) (adaptée au canaliseur polyphasé)

- Tri bitonique vectorisé SIMD, corrélation, convolution

Série Versal AI Edge avec AIE-ML :

- FFT pour AIE-ML à l'aide de l'architecture AIE-ML + PL parallèle 2D (adaptée au canaliseur polyphasé)

- Tri bitonique vectorisé SIMD, corrélation, convolution

Série Versal AI Edge Gen2 avec AIE-ML v2

- 2D FFT AIE-ML v2 + PL v1 (adaptée aux canaliseurs polyphasés)

- FIR TDM (adapté aux canaliseurs polyphasés)

- GEMM/GEMV

- FIR à débit unique

- FIR à demi-bande

- FIR à rééchantillonnage fractionnel

- Changement de débit FIR

- FFT/iFFT

- DFT

- Mélangeur DDS

- Approximation de fonction

- Simulation fonctionnelle des sous-systèmes Vitis dans MATLAB® et Python™

- Prise en charge améliorée de la mesure de la latence et du débit dans Vitis Analyzer, pour les conceptions AI Engine

- Contrôle d'exécution des partitions AIE indépendantes

Prise en charge de plusieurs sous-systèmes d'AI Engine de premier niveau

Blocs supplémentaires disponibles pour AI Engine et HDL

Moteur d'IA

- Tri bitonique (série Versal AI Core, série Versal AI Edge, série Versal AI Edge Gen2)

- DFT/FFT (série Versal AI Edge Gen2)

- FIR - Débit unique, demi-bande, changement de débit, rééchantillonnage fractionnel (série Versal AI Edge Gen2)

- DDS/mixeur (série Versal AI Edge Gen2)

Bibliothèque HDL

- FFT améliorée – Modes SSR supplémentaires

- SSR 8, 16, 32, 64 (virgule flottante native)

- SSR 2, 4 (virgule fixe)

- Complex Multiplier amélioré – Moins de ressources DSP58

- Nouvelle prise en charge de CFLOAT MAC

- Virgule flottante IFFT vectorielle – Nouveau bloc

- Générez du code C++ compatible avec Vitis HLS à partir de conceptions MATLAB (.m) dans R2025a

- Nouvelles fonctionnalités de Vitis HLS faciles à utiliser

- Modélisation des entrées filaires et des entrées AXI Lite qui changent pendant l'exécution ( E/S directes)

- Pragma de performances pour la conception HLS de premier niveau (accès anticipé ouvert)

- Prise en charge du Complex Multiplier de Versal via la bibliothèque intrinsèque dédiée

- Améliorations apportées à la GUI de Vitis HLS

- Prise en charge initiale de C++17 via Clang 16

Points forts de la version 2024.2 de la plateforme software AMD Vitis™ :

Améliorations pour les conceptions DSP AMD Versal AI Engine

- Estimations de latence et de débit à l'aide de Vitis Analyzer

- Marquer les PLIO indisponibles à l'aide de Vitis Analyzer

- Prototypage rapide des conceptions d'AMD Versal™ AI Engine

- Création de rapports sur la pile de segments et la mémoire du programme

Nouvelles fonctions dans la bibliothèque de Vitis, améliorées pour les Versal AI Engines

- Fonctions de bibliothèque DSP améliorées pour AIE (disponibles sur Versal AI Core, Versal série Premium)

- Fonctions de filtre FIR TDM (Time Division Multiplexed) à performances améliorées

- Versions plus performantes de

- GEMV (General Matrix Vector)

- GEMM (General Matrix Multiply)

- 2D IFFT – partitionné entre AIE + PL pour de hautes performances

- Nouvelles fonctions de bibliothèque DSP pour AIE-ML (disponible sur Versal AI Edge)

- Fonctions de filtre TDM FIR à performances améliorées

- Prise en charge des FFT Radix-3/Radix-5

- GEMV

- GEMM

Nouvelles fonctionnalités simples d'utilisation dans l'IDE Vitis (nouvelle GUI)

- Nouveau terminal pour les numéros de série : surveillez les messages relatifs aux numéros de série provenant du hardware

- Installez et explorez des extensions tierces

- Suivi des systèmes de traitement : fonctionnalité de débogage et d'optimisation des performances des systèmes intégrés

Améliorations apportées à Vitis Model Composer pour les conceptions DSP AIE

- Mises à jour de la bibliothèque DSP AI Engine

- AIE (disponible sur Versal AI Core, Versal série Premium)

- FFT Radix mixte

- Améliorations des performances FFT de Stockham

- TDM FIR

- AIE-ML (disponible sur la série Versal AI Edge)

- TDM FIR

- Synthèse numérique directe (DDS - utilisée pour la génération de formes d'onde)

- Mélangeur (utilisé pour le changement de fréquence)

- AIE-MLv2 (disponible sur la série Versal AI Edge Gen2)

- FIR

- DFT

- DDS

- Mélangeur

- AIE (disponible sur Versal AI Core, Versal série Premium)

- Types de données supplémentaires pour Vitis Model Composer

- Prise en charge de cbfloat16

- Prise en charge de types de données supplémentaires pour les signaux en cascade

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- Exportez les conceptions de noyau AIE/HLS de Vitis Model Composer vers Vitis en tant que Vitis Subsystem (VSS)

- Déboguez les noyaux AIE/HLS intégrés à Vitis Model Composer à l'aide de Vitis Debugger

- Mises à jour du bloc HDL dans Vitis Model Composer

- Autres améliorations apportées à Vitis Model Composer

- Amélioration du temps de réponse pour la génération de code

- La simulation ne s'exécute qu'une seule fois pour toutes les conceptions

- Enregistrez les configurations de bloc Hub sous forme de fichier JSON (utile pour le prototypage rapide ou le traitement par lots)

- Ajout de la prise en charge de MATLAB R2024a

- Ajout de la prise en charge de Red Hat Enterprise Linux (RHEL) 8.10, 9.4

- Amélioration du temps de réponse pour la génération de code

- Vérifications des règles de conception (RDC) pour remplacer les considérations de conception

Nouveautés Vitis par catégorie

Développez les sections ci-dessous pour en savoir plus sur les nouvelles fonctionnalités et améliorations de la plateforme software AMD Vitis 2024.2. Pour plus d'informations sur les plateformes prises en charge, les changements de comportement et les problèmes connus, reportez-vous aux notes de publication de la plateforme software Vitis 2024.2 pour le flux d'accélération des applications et le flux de développement de softwares intégrés.

Fonctions améliorées des fonctions de la bibliothèque DSP pour AIE (disponible sur Versal AI Core, Versal série Premium)

- Fonctions de filtre FIR TDM (Time Division Multiplexed) à performances améliorées

- Versions plus performantes de

- GEMV (General Matrix Vector)

- GEMM (General Matrix Multiply)

- 2D IFFT – partitionné entre AIE + PL pour de hautes performances

Nouvelles fonctions de bibliothèque DSP pour AIE-ML (disponible sur Versal AI Edge)

- Fonctions de filtre FIR TDM (Time Division Multiplexed) à performances améliorées

- Prise en charge des FFT Radix-3/Radix-5

- GEMV (General Matrix Vector)

- GEMM (General Matrix Multiply)

- Estimation du temps de latence et du débit avec Vitis Analyzer

- Possibilité d'indiquer les PLIO non disponibles avec Vitis Analyzer

- Mises à jour de la bibliothèque DSP AI Engine

- AIE(disponible sur Versal AI Core, Versal série Premium)

- FFT Radix mixte

- Améliorations des performances FFT Stockham

- TDM FIR

- AIE-ML(disponible sur la série Versal AI Edge)

- TDM FIR

- DDS (Direct Digital Synthesis – utilisé pour la génération de formes d'onde)

- Mélangeur (utilisé pour le changement de fréquence)

- AIE-MLv2(disponible sur la série Versal AI Edge Gen 2)

- FIR

- DFT

- DDS

- Mélangeur

- AIE(disponible sur Versal AI Core, Versal série Premium)

- Types de données supplémentaires pour Vitis Model Composer

- Prise en charge de cbfloat16

- Prise en charge de types de données supplémentaires pour les signaux en cascade

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- Exportez les conceptions de noyau AIE/HLS de Vitis Model Composer vers Vitis en tant que VSS (Vitis Subsystem)

- Déboguez les noyaux AIE/HLS intégrés à Vitis Model Composer à l'aide du débogueur Vitis

- Mises à jour du bloc HDL dans Vitis Model Composer

- Autres améliorations apportées à Vitis Model Composer

- Amélioration du temps de réponse pour la génération de code

- La simulation ne s'exécute qu'une seule fois pour toutes les conceptions

- Enregistrez les configurations de bloc Hub sous forme de fichier JSON (utile pour le prototypage rapide ou le traitement par lots)

- Ajout de la prise en charge de MATLAB R2024a

- Ajout de la prise en charge de Red Hat Enterprise Linux (RHEL) 8.10, 9.4

- Vérifications des règles de conception (RDC) pour remplacer les considérations de conception

- Modélisation des entrées scalaires/filaires qui changent pendant l'exécution (E/S directes)

- Prise en charge des types de précision arbitraire à virgule flottante

- Mappage du code HLS vers les blocs DSP

- Séquence d'exécution du code déterminée par l'utilisateur

- Débogueur HLS qui affiche les types de données de manière conviviale (à l'aide de la technologie d'impression élégante du débogueur GNU)

Points forts de la version 2024.1 de la plateforme software AMD Vitis™ :

Améliorations pour les conceptions DSP AMD Versal™ AI Engine

- Fonctions de bibliothèque DSP améliorées pour la série AMD Versal AI Core

- Fonctions de filtre FIR multiplexé par répartition temporelle (TDM) pour SSR > 1

- FFT avec twiddle 32 bits

- FFT Mixed-Radix 3 et Mixed-Radix 5

- Produit de matrice de Kronecker

- Solveur QRD basé sur les propriétaires pour une meilleure stabilité

- DFT pour SSR > 1

- Nouvelles fonctions de bibliothèque DSP pour la série Versal AI Edge avec AIE-ML

- General Matrix Vector (GEMV) avec prise en charge SSR

- General Matrix Multiply (GEMM) avec prise en charge SSR

- Améliorations de l'API AIE

- Prise en charge des FFT Radix-3/Radix-5

- Améliorations du simulateur AIE

- Fonctionnalités de simulation approximative de cycle pour les conceptions AI Engine avec PL, sans besoin de contrôle, interfaces et système de traitement (CIPS) du noyau IP

- L'analyseur AMD Vitis prend en charge l'émulation hardware avec des simulateurs tiers tels que VCS, Questa, Xcelium et Riviera

Principales améliorations apportées à Vitis Unified Software Platform

- Prise en charge de nouveaux appareils : SoC adaptatif AMD Versal™ Premium VP1902, processeur AMD MicroBlaze™ V

- Amélioration du développement d'applications intégrées et de la génération BSP pour l'environnement Windows®

- Flux géré par l'utilisateur pour déboguer les applications intégrées compilées en externe

- Nouvelle GUI (interface graphique utilisateur) Bootgen

- Activez les builds incrémentiels pour le projet de la plateforme

Améliorations clés apportées à AMD Vitis IDE (nouvelle GUI (interface graphique utilisateur)

- Ajout de la prise en charge de la hiérarchie de débogage du sous-système

- Ajout de la prise en charge de l'exportation et de l'importation de projets/de l'espace de travail

- Ajout de la prise en charge de l'interpréteur Python et de l'API

- Nouvelle page d'aperçu de la fonctionnalité

- Notification de modification de nouveau fichier pour les projets intégrés, AIE et de plateforme

Nouveautés Vitis par catégorie

Développez les sections ci-dessous pour en savoir plus sur les nouvelles fonctionnalités et améliorations de la plateforme software AMD Vitis 2024.1. Pour plus d'informations sur les plateformes prises en charge, les changements de comportement et les problèmes connus, reportez-vous aux notes de publication de la plateforme software Vitis 2024.1 pour le flux d'accélération des applications et le flux de développement de softwares intégrés.

Fonctions de bibliothèque DSP améliorées pour AMD Versal série AI Core

- Fonctions de filtre FIR multiplexé par répartition temporelle (TDM) pour SSR > 1

- FFT avec twiddle 32 bits

- FFT Mixed-Radix 3 et Mixed-Radix 5

- Produit de matrice de Kronecker

- Solveur QRD basé sur le propriétaire pour une meilleure stabilité

- DFT pour SSR > 1

Nouvelles fonctions de bibliothèque DSP pour la série AMD Versal AI Edge avec la matrice AIE-ML

- General Matrix Vector (GEMV) avec prise en charge SSR

- General Matrix Multiply (GEMM) avec prise en charge SSR

Améliorations de l'API AIE

Prise en charge des FFT Radix-3/Radix-5

Améliorations du simulateur AI Engine

- Fonctionnalités de simulation approximative de cycle pour les conceptions AI Engine avec PL, sans CIPS (cœur d'IP de contrôle, d'interfaces et de système de traitement).

- Prise en charge de l'analyseur Vitis pour l'émulation hardware avec des simulateurs tiers tels que VCS, Questa, Xcelium et Riviera.

- Exporter les tableaux à partir de l'analyseur Vitis au format CSV

- Nouvelles fonctions DSP prises en charge pour AIE et AIE-ML dans AMD Vitis Model Composer

- Fonctions du filtre FIR multiplexé par répartition temporelle (TDM)

- Pour la construction de canaux polyphasés à 1 GSPS et débit supérieur

- DFT/IDFT – avec prise en charge SSR

- Transformations optimisées pour le débit/la latence sur les petites tailles

- FFT/IFFT – avec prise en charge étendue pour le twiddle CINT 32 bits

- FFT/IFFT Mixed-Radix – avec prise en charge AIE-ML

- Améliorations de la facilité d'utilisation du bloc Hub Model Composer

- Améliorations apportées au flux de validation hardware

- Prise en charge de la version du SE et de MATLAB® avec la v 2024.1 :

- RHEL 9

- MATLAB R2023a et R2023b

Nouveaux exemples de conceptions disponibles sur Github.

Un nouveau pragma stencil simplifie le code HLS C++ pour les filtres d'images et de vidéos.

Les nouveaux assistants des fonctions de bibliothèque utilisent le référentiel github des bibliothèques AMD Vitis

- Créez des adresses IP « Solver » et « Vision » (compatibles OpenCV) pour l'outil de conception AMD Vivado

- Exécutez des exemples de bibliothèque disponibles

Pragma pour l'interface mémoire (ap_memory) peut désormais regrouper des ports pour AMD Vivado IP Integrator

La nouvelle comparaison des composants HLS affiche des mesures côte à côte pour deux composantsou plus

Prise en charge du code RTL de l'utilisateur pour remplacer une fonction C++ (flux de boîte noire)

Code Analyzer peut désormais dissocier les membres C++ struct pour affiner l'analyse des performances

Nouveau contrôle utilisateur pour le codage HLS global FSM et la sélection de l'état de sécurité

Accès aux sanitizers Clang pendant la simulation C pour effectuer des vérifications d'adresse et d'initialisation

Principales caractéristiques de la version 2023.2 de Vitis™ Software Platform :

Améliorations pour les conceptions DSP Versal™ AI Engine

- Nouvelles fonctions de la bibliothèque DSP

- Nouvelle prise en charge de l'API pour les fonctions DSP

- Nouvelles fonctionnalités du compilateur et des simulateurs AI Engine

Nouveau software autonome Vitis intégré

- Un programme d'installation autonome de taille plus réduite pour les concepteurs qui écrivent du code C pour le sous-système intégré Arm®

- Toutes les fonctions intégrées sont fournies, y compris les utilitaires tels que Bootgen et XSCT

Nouvel environnement de conception intégré et unifié Vitis

- GUI (interface graphique utilisateur) et interface de ligne de commande cohérentes sur tous les workflows Vitis

- La GUI (interface graphique utilisateur) nouvelle génération basée sur Eclipse Theia offre une plus grande flexibilité et des fonctionnalités conviviales pour une meilleure efficacité au travail

Nouveautés Vitis par catégorie

Développez les sections ci-dessous pour en savoir plus sur les nouvelles fonctionnalités et améliorations de la plateforme software Vitis 2023.2. Pour plus d'informations sur les plateformes prises en charge, les changements de comportement et les problèmes connus, reportez-vous aux notes de publication de la plateforme software Vitis 2023.2 pour le flux d'accélération des applications et le flux de développement de softwares intégrés.

Nouvelles fonctions de bibliothèque DSP pour les AI Engines

- FFT Radix mixte

- Discrete Fourier Transform (DFT)

- General Matrix-Vector Multiply (GEMV)

Nouvelle prise en charge de l'API pour les fonctions DSP

- IP FFT avec types de données pour le twiddle cint32

- Prise en charge de cint16 pour les API FFT Radix-4

- Fonctions « fix2flt » et « flt2fix » vectorisées et mises en œuvre dans l'API

Nouvelle prise en charge de l'API pour AIE-ML

- Les API prennent désormais en charge les types de données int32/cint32 dans la fonction sliding_mul()

- Les API prennent désormais en charge les types de données <float> dans la fonction sliding_mul()

- Toutes les routines d'API AIE requises pour prendre en charge la multiplication de matrices éparses sont fournies

Mises à jour des principaux composants :

- U-boot 2024.1

- Micrologiciel approuvé Arm 2.10

- Linux Kernel 6.6_LTS

- Qemu 8.1

- Xen 4.18

- OpenAMP 2023.10

BSP Sunset :

- AMD MicroBlaze™ : VCU118, KCU105, KC705, AC701

- Zynq : zc706

- AMD Versal™ : VMK180-EMMC, VMK180-OSPI

- Zynq MP : ZCU111

Nouveaux BSP (XSCT) :

- BSP de production VEK280 avec nouveau PHY ETH

Nouveau BSP System Device Tree Flow (SDT) :

- ZCU102, ZCU104, ZCU105, ZCU216

- ZCU208, ZCU208-sdfec, ZCU670

- VCK190

- VMK180

- VPK120

- VPK180

- VEK280

- Le compilateur AIE peut désormais prendre en charge les matrices 2D et 3D en tant qu'entrées ou sorties

- Vitis Analyzer génère désormais un rapport d'orientation pour ajuster la taille FIFO

- Nouvelle prise en charge du kernel de simulateur multithread et accélération de l'analyseur de vidage des changements de valeur (VCD)

- Interface externe avec l'environnement MATLAB® et les générateurs de trafic Python

- Modèle AXI Stream amélioré avec prise en charge des cycles vides/d'attente dans l'alignement PLIO

- Vérification améliorée des règles de conception

- Transfert de la trace AI Engine via un débogage à haute vitesse

- Prise en charge du profilage NOC et DDRMC rigide dans l'environnement Vitis

- Vitis prend désormais en charge la trace AIE-ML pour VEK280 et la carte d'accélération d'inférence AI Alveo™ V70

- Mises à jour du bloc AI Engine

- Prise en charge de l'importation de graphiques AIE-ML en tant que blocs dans Vitis Model Composer

- Nouvelles fonctions DSPlib pour la mise en œuvre AIE et AIE-ML dans Vitis Model Composer

- Tracé de la sortie du simulateur AIE pour les signaux internes dans l'outil Simulink®

- Mises à jour du bloc noyau HLS

- Génération automatique de banc d'essai

- Prise en charge étendue des types de données pour les blocs noyau HLS

- Intégration de Vitis Model Composer et de l'outil Vitis

- Génération de fichiers .xo et libadf.a directement à partir de Vitis Model Composer

- Autres améliorations

- Prise en charge des versions de l'outil MATLAB® : R2021a, R2021b Update 6, R2022a Update 6, R2022b

- Topologies supplémentaires prises en charge pour le flux de validation du hardware

- Nouveaux exemples de supports disponibles auprès de GitHub

- Nouvel IDE Vitis Unified pour les composants HLS

- Nouvelles exigences de licence Vitis HLS

- Nouvelle fonctionnalité d'analyseur de code permettant d'obtenir des estimations de performances avant d'exécuter la synthèse C.

- Améliorations apportées à l'interface AXI :

- Prise en charge des canaux latéraux HLS AXI Stream

- Prise en charge de la mise en cache principale AXI configurable par l'utilisateur

- Autres améliorations :

- Nouveau rapport sur la complexité du code permettant d'identifier les problèmes de taille de conception pendant la synthèse C

- Améliorations du temps de compilation : Amélioration moyenne du temps de compilation de 20 % en 2023.2 par rapport à 2023.11

Principales caractéristiques de la version 2023.1 de Vitis Software Platform :

Nouvelles fonctions Vitis™ Library pour les matrices Versal™ AI Engine (AIE)

- Fonctions de la bibliothèque DSP : plus de configurations de filtre FIR

- Fonctions de bibliothèque Solver : améliorations pour des performances supérieures

Améliorations du flux de conception pour Versal AI Core et la série AI Edge

- Prise en charge du compilateur AIE pour les matrices 2D et 3D comme entrées/sorties

- Prise en charge du guidage par simulateur AIE pour le dimensionnement FIFO afin d'éviter les conditions de blocage

- Améliorations des rapports d'état AIE

- Nouvelle GUI (interface graphique utilisateur) par défaut pour l'analyseur Vitis

Prise en charge de l'exportation de l'environnement Vitis vers l'environnement Vivado™

- Permet aux équipes de développement d'outils Vitis et Vivado de travailler en parallèle sur la base d'un point de contrôle d'interface commun

Nouveautés Vitis par catégorie

Développez les sections ci-dessous pour en savoir plus sur les nouvelles fonctionnalités et améliorations de la plateforme software AMD Vitis 2023.1. Pour plus d'informations sur les plateformes prises en charge, les changements de comportement et les problèmes connus, reportez-vous aux notes de publication de la plateforme software Vitis 2023.1 pour le flux d'accélération des applications et le flux de développement de softwares intégrés.

Bibliothèque DSP - Filtres FIR

- FIR de rééchantillonnage fractionnel amélioré, FIR à débit unique, FIR demi-bande et FIR de changement de débit pour prendre en charge des largeurs de bits de coefficient supérieures à la largeur des bits de données

- Le rééchantillonnage fractionnel FIR prend également en charge le fonctionnement SSR à l'aide de plusieurs tuiles AIE et intègre une fonctionnalité de rechargement de coefficient

Bibliothèque Solver

- Performances API améliorées grâce à des conceptions de streaming hautes performances (~300 vignettes)

- Prise en charge de QR et de Cholesky Decomposition pour les fonctions de Data Mover 4D afin de faciliter la lecture ou l'écriture de données à partir des matrices AIE

- Le compilateur AIE peut désormais prendre en charge les matrices 2D et 3D en tant qu'entrées ou sorties en plus des matrices 1D.

- Le compilateur AIE prend en charge les constructions graphe dans le graphe (sous-graphiques) et les constructions de port conditionnelles.

- Nouvelles API de conversion de données AIE CINT vers CFLOAT.

- Amélioration du rapport d'état AIE pour générer un fichier contenant des informations sur les vignettes, les événements et les registres supplémentaires sur les mosaïques AIE-ML et AIE dans la conception.

- Déchargement de la trace d'événement AIE sur des paires différentielles haut débit (HSDP) au lieu de la stocker en mémoire sur des appareils Versal.

- Prise en charge du profilage NoC et DDR MC rigide dans l'environnement Vitis.

- Tracé d'événement fenêtré AIE pour l'inspection d'une partie spécifique d'une application.

- Conseils pour le dimensionnement FIFO afin d'éviter les blocages.

- Possibilité de sélectionner les nœuds signalés par le simulateur AIE afin de réduire la taille du fichier VCD du simulateur et d'accélérer la simulation.

- Le simulateur AIE génère désormais un rapport (qui peut être affiché dans l'analyseur Vitis) qui indique quel AIE présente des violations d'accès à la mémoire et comment elles correspondent aux lignes du code C du graphique.

- La visualisation des données de la vue de trace prend désormais également en charge la matrice AIE-ML.

- Nouvelle prise en charge des types de données pour les configurations de filtre FIR qui ciblent les Versal AI Engines

- Deux nouvelles fonctions à virgule flottante optimisées pour les DSP58 dans les SoC adaptatifs Versal

- Temps de réponse plus rapide pour toutes les fonctions de la bibliothèque Vitis Model Composer ciblant les Versal AI Engines

- Autres améliorations :

- Améliorations apportées aux blocs noyau HLS

- Améliorations apportées au Hub Vitis Model Composer

- Prise en charge des versions R2021a, R2021b, R2022a de l'outil MATLAB

- Amélioration des performances2 : Amélioration moyenne de la latence de 5,2 % dans la version 2023.1 par rapport à 2022.2

- Méthode simple pour télécharger, visualiser et instancier les fonctions des bibliothèques L1 dans l'outil Vitis HLS

- Prise en charge améliorée pour les transactions AXI et les rapports de rafales dans l'outil Vitis HLS

Principales caractéristiques de la version 2022.2 de Vitis Software Platform :

Nouvelles fonctions Vitis™ Library pour les matrices Versal™ AI Engine (AIE)

- Fonctions de la bibliothèque DSP : fonctionnalités améliorées

- Fonctions de bibliothèque Solver

- Fonctions de la bibliothèque Vision

- Fonctions de la bibliothèque d'ultrasons

Améliorations du flux de conception pour Versal AI Core et la série AI Edge

- Contrôlez le positionnement relatif des noyaux dans la matrice AI Engine pour de meilleures performances et une meilleure utilisation

- Améliorations du simulateur AIE x86 - modélisation améliorée des conditions de blocage dans le simulateur x86

- Améliorations de l'API AIE - Ajout des API Radix 3/5 FFT et Matrix « x » Vector

- Fonctionnalités de profilage et de débogage améliorées pour les conceptions Versal : détection de blocage, collecte de données de trace plus importante, prise en charge de banc d'essai RTL/Python

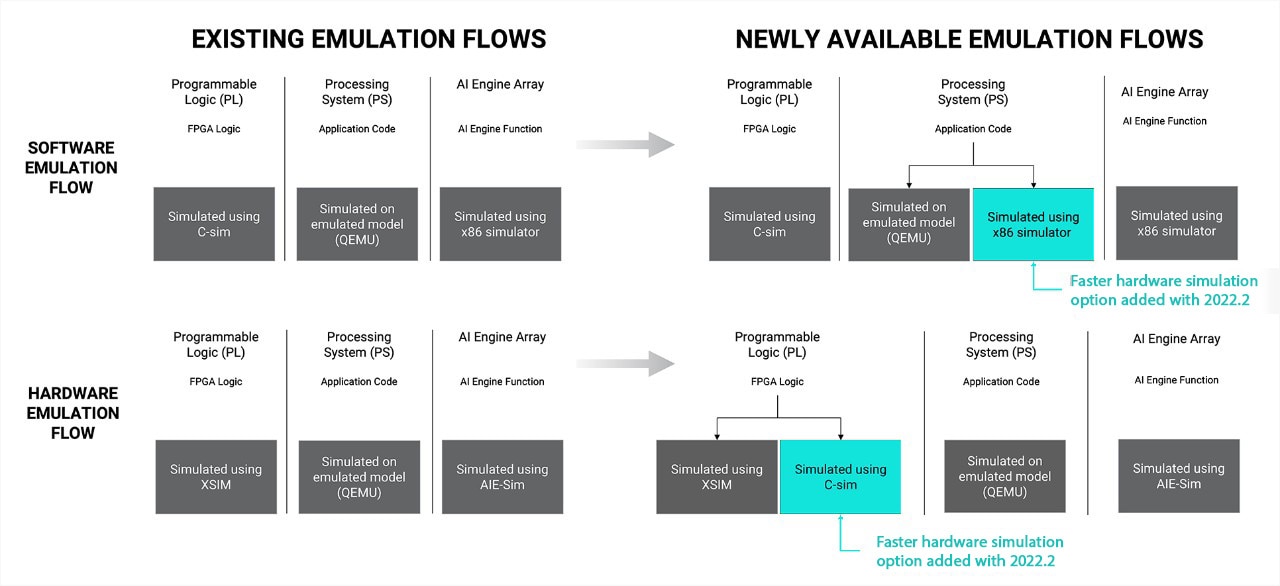

- Nouvelles options de simulation pour les conceptions hétérogènes dans Vitis

Nouveautés Vitis par catégorie

Développez les sections ci-dessous pour en savoir plus sur les nouvelles fonctionnalités et améliorations de la plateforme software AMD Vitis 2022.2. Pour plus d'informations sur les plateformes prises en charge, les changements de comportement et les problèmes connus, reportez-vous aux notes de mise à jour de la plateforme software Vitis 2022.2 pour le flux d'accélération d'applications et le flux de développement software intégré.

Fonctions de la bibliothèque DSP

- La mise en œuvre du filtre FIR à super taux d'échantillonnage (SSR) sur AI Engine prend désormais en charge la fonction de rechargement de coefficient et la taille de point dynamique

- Ajout d'un élément de fenêtrage FFT à la fonction FFT qui cible la matrice AI Engine

Fonctions de bibliothèque Solver

- Décomposition de la rotation en quadrature (QR)

- Décomposition de Cholesky

Fonctions de la bibliothèque Vision

- Quatre nouvelles fonctions vidéo ciblant la matrice AI Engine

Fonctions de la bibliothèque d'ultrasons

- Diverses fonctions permettant de créer des conceptions pour échographies médicales

- Possibilité d'ajouter des contraintes pour contrôler le positionnement relatif des noyaux dans la matrice AI Engine, ce qui permet aux utilisateurs d'obtenir des performances supérieures et une meilleure utilisation

- Amélioration de la modélisation des conditions de blocage AIE dans le simulateur x86

- Ajout d'une nouvelle API AIE - ajout des API Radix 3/5 FFT et Matrix « x » Vector

- Génération de rapports de profilage AI Engine dans l'émulation hardware

- Détection de verrouillage à l'aide de XSDB (AMD System Debugger) pour les conceptions AI Engine et celles reposant sur PL

- Déchargement continu contrôlé par Xilinx Runtime (XRT) de la trace des événements AI Engine sur PLIO

- Prend en charge l'application PS sur la machine hôte x86 pour l'émulation software

- Autorise les modèles fonctionnels SystemC pour l'émulation hardware au lieu de RTL

- Permet aux utilisateurs de simuler le noyau AI Engine à l'aide d'un banc d'essai RTL simple ou d'un générateur de trafic basé sur des scripts Python

- L'état AI Engine peut être analysé pendant l'émulation hardware avec l'analyseur Vitis™

Nouvelles options de simulation Vitis Environment 2022.2 : Simulation x86 du système de processeur et simulation x86 AI Engine : La simulation de logique programmable peut être effectuée à l'aide du simulateur x86.

- Fonctionnalités pour la conception de Versal AI Engine

- Possibilité d'ajouter des contraintes graphiques aux conceptions de blocs de la bibliothèque DSP AI Engine : utilisation et performances supérieures

- Nouvelle fonctionnalité de simulation approximative de cycle pour les conceptions AI Engine

- Le bloc d'importation de graphiques AI Engine détecte automatiquement les ports RTP (Run Time Parameter)

- Améliorations et ajouts aux blocs de la bibliothèque DSP

- Caractéristiques générales

- Flux de validation hardware pris en charge pour les conceptions de systèmes hétérogènes utilisant des matrices PL et AIE

- Bloc Vitis Model Composer Hub mis à jour pour prendre en charge la conception hétérogène

- Détection automatique des sous-systèmes AI Engine, HDL et HLS valides

- Le flux de validation hardware a été amélioré pour les conceptions en HDL uniquement et les conceptions en HDL → AI Engine → HDL pour les plateformes Versal

- Amélioration de la prise en charge du style de codage « parallélisme au niveau des tâches »

- Permet une simulation C plus rapide et une meilleure QoR

- Améliorations supplémentaires des performances et du temps

- Amélioration de l'inférence des rafales

- Inférence automatique des pragmas Unroll, Pipeline, Array_Partition et inline pour de meilleures performances

- Précision de synchronisation améliorée pour une meilleure fermeture de synchronisation à des fréquences plus élevées

- Autres fonctionnalités

- Analyse et débogage : la fonction printf insérée dans le code C est désormais prise en charge même après la synthèse dans le RTL

- Facilité d'utilisation : nouveau pragma de performance pour atteindre automatiquement un intervalle de transaction donné

- HLS : interfaces de flux désormais prises en charge par FFT et FIR IP

Principales caractéristiques de la version 2022.1 de Vitis Software Platform :

Amélioration du débit Vitis™ pour Versal™ ACAP et AI Engine

- Prend en charge la plateforme DFX de base AMD avec une région statique et une région DFX

- Le profilage AIE prend en charge la détection de blocage, génère la vue de rapports d'état AI Engine (y compris les événements d'erreur) dans Vitis Analyzer

- Les générateurs de trafic externe en x86sim, AIEsim et émulation software sont beaucoup plus flexibles et peuvent être insérés très facilement dans les flux de simulation et d'émulation

- Vitis Model Composer prend en charge la validation hardware, Linux et l'émulation hardware

Vitis pour DC et Vitis HLS

- Vitis fournit une prise en charge supplémentaire des rapports pour le processus dynamique de génération de régions. Les améliorations apportées aux rapports Flow incluent trois nouveaux rapports ou mis à jour

- Vitis améliore le profilage PL en choisissant de décharger la trace vers les ressources mémoire (de préférence) ou FIFO dans la PL pour de meilleures performances

- Une nouvelle visionneuse de trace chronologique affichant le profil d'exécution et permettant à l'utilisateur de rester dans la GUI (interface graphique utilisateur) de Vitis HLS est désormais disponible après la simulation

- Vitis HLS prend désormais en charge un type de construction « intelligente » de niveau supérieur via le nouveau pragma de performance ou la directive set_performance_directive

- Vitis Graph Library avec améliorations de l'API L3 (gain de temps de 1 ms pour l'appel du noyau) pour les performances

Nouveautés Vitis par catégorie

Développez les sections ci-dessous pour en savoir plus sur les nouvelles fonctionnalités et améliorations de la plateforme software AMD Vitis 2022.1. Pour plus d'informations sur les plateformes prises en charge, les changements de comportement et les problèmes connus, reportez-vous aux notes de publication de la plateforme software Vitis 2022.1 pour le flux d'accélération des applications et le flux de développement de softwares intégrés.

- Ajout d'une nouvelle bibliothèque Genomics Accelerator (L1, L2 et L3)

- Bibliothèque de graphiques, améliorations L3 pour les performances

- Bibliothèque de bases de données Vitis, noyau multifonctionnel GQE

- Nouvelles fonctions ajoutées dans Vision Library

- Nouvelles fonctions des ajouts/améliorations Vitis AIE Vision Library

- Bibliothèque DSP de Vitis AIE, le rééchantillonnage FIR remplace l'interpolateur fractionnel FIR

- La bibliothèque de codecs Vitis propose de nouvelles API : l'API jxlEnc, l'API « leptonEnc », l'API « resize » et l'API « WebpEnc ».

Bibliothèque de compression de données Vitis

- Amélioration de compression ZLIB, compression Octa-Core personnalisée pour la solution 8KB

- Amélioration de la décompression ZLIB, IP personnalisée pour une taille de fichier de 8 Ko

- Amélioration des requêtes de capacité de la plateforme

- Amélioration de la facilité d'utilisation de HBM, possibilité de choisir un point d'entrée S_AXI spécifique à HMSS pour un noyau M_AXI, insertion RAMA prise en charge à partir des fichiers de configuration

Compilateur Vitis AI Engine

- Détection et analyse automatisées des blocages AI Engine dans le hardware

- Analyse de la sortie d'état automatique

- Analyse de la sortie d'état automatique – Tampons

- Analyse de la sortie d'état manuel dans le hardware

- Analyse de la sortie d'état manuel

- Améliorations apportées au suivi des événements AI Engine

- Générateurs de trafic externe AIEsim

- Améliorations du profilage AI Engine sur le hardware

- Prise en charge d'AI Engine pour les fenêtres de diffusion

- Modèle de programmation graphique amélioré pour le compilateur Vitis AI Engine

- Compilateur Vitis AI Engine - PLIO/GMIO dans les graphiques ADF

Vitis HLS

- Améliorations de l'analyse, nouvelle visionneuse de suivi de chronologie

- Améliorations du style de codage, prise en charge de la partition de baie pour le type flux de blocs

- Abstraction Pragma, nouveau Pragma Performance (et directive)

- Vitis Core « One Liner », Vitis HLS - Nouvelle visionneuse de suivi de chronologie, nouveau pragma PERFORMANCE, fenêtres de prise en charge de flux de blocs

- Nouvelle visionneuse introduite

- Affiche le profil d'exécution de toutes les fonctions restantes de votre conception, c'est-à-dire celles qui sont converties en modules

- Particulièrement utile pour voir le comportement des régions de flux de données après la co-simulation

- Natif vers Vitis HLS - Plus besoin de lancer la visionneuse de forme d'onde xsim (outil externe)

Vitis Analyzer

- Amélioration de Vitis Analyzer, Enregistrer/Restaurer la personnalisation de la chronologie

- Amélioration des rapports, report_qor_assessment, informations de verrouillage xclbin, résumé de l'automatisation Vivado

- Amélioration du profilage, nouvelle infrastructure de profilage PL activée, plusieurs options trace_memory peuvent être ajoutées pour insérer plusieurs moniteurs de mémoire (hardware uniquement), exemple de fichier de configuration pour l'éditeur de ligne v++ pour décharger les données de trace de toutes les unités de commande de SLR0 vers DDR0 et identiques pour toutes les unités de commande de SLR1 vers DDR1

Vitis IDE

- Mise à jour de la GUI (interface graphique utilisateur) Bootgen pour Versal

- Mise à jour de la chaîne d'outils

- XSCT, prise en charge de STAPL, commande de génération de script d'ajout de liens

- Flux de compilation du système, reportez-vous au document de compilation du système

Vitis Emulation

- Ajout de la prise en charge de l'émulation software pour le redémarrage automatique et la prise en charge de la messagerie pour les noyaux toujours en cours d'exécution

- Le noyau libre n'a pas besoin de while(1) pour sw-emu

- Ajout de la prise en charge de l'émulation software pour le générateur de trafic externe

- L'émulation hardware peut utiliser le modèle de fonction de code source HLS C pour l'IP de diffusion.

- Ajouter l'API xrt::system pour la détection du nombre d'appareils

- Ajouter l'API xrt::message pour la journalisation des messages

- Le code d'hôte de l'API native du XRT requiert désormais

-std=c++17 ou version supérieur - Ajouter les API xrt::queue expérimentales pour l'exécution asynchrone de certaines opérations synchrones.

- xbutil peut afficher les compteurs FIFO AIE qui aident à déboguer les scénarios de blocage AIE

- L'option xbutil --legacy est supprimée.

- xclbinutil --info fournit des informations d'horloge pour les plateformes intégrées

- xbutil sur ARM peut charger des images SOM

- L'utilitaire autonome xbtop peut afficher la sortie linux top like (en remplacement de l'ancien xbutil -top)

- Les utilitaires XRT prennent en charge l'exécution automatique dans Bash avec la touche Tab.

- Mises à jour de la plateforme Alveo, mises à jour de la plateforme pour une meilleure stabilité, mises à jour de la gestion des cartes, outil de mise à jour du micrologiciel SC

- Plateforme intégrée, nouvelle plateforme VCK190 DFX : xilinx_vck190_base_dfx_202210_1, les plateformes intégrées sont désormais installées avec Vitis, Vivado ajoute un nouvel exemple de conception personnalisable : Plateforme Vitis pour MPSoC

- Révision majeure du bloc Hub Vitis Model Composer pour l'évolutivité et la facilité d'utilisation

- Le flux de validation hardware prend désormais en charge Linux en plus du système d'exploitation

- Les blocs « AIE vers HDL » et « HDL vers AIE » n'incluent plus les blocs de passerelle HDL

- La version 2022.1 propose désormais un aperçu des exemples pour les clients qui n'ont pas accès à Internet. L'outil invite l'utilisateur à télécharger une nouvelle version des exemples à partir de GitHub, le cas échéant

- Pour une plus grande facilité d'utilisation, les blocs utilitaires qui ne font pas partie de la génération de code sont désormais présentés avec un fond blanc

- Amélioration et réorganisation du navigateur de la bibliothèque pour une plus grande facilité d'utilisation

- Prise en charge de RHEL 8.x

- Prise en charge de MATLAB - R2021a et R2021b

Principales caractéristiques de la version 2021.2 de Vitis Software Platform :

- Nouveaux environnements de développement spécifiques au domaine

- SDK Vitis™ Video Analytics sur Kria™ SOM, Alveo™ U30/U50 et carte de développement VCK5000 Versal™ : En savoir plus >

- Solution de blockchain Vitis sur carte Varium™ C1100 avec Vitis libs : En savoir plus >

- Prise en charge du flux de bout en bout pour les cartes VCK5000 et Varium C1100

- Fonctionnalités de base améliorées

- API d'abstraction de haut niveau C/C++ du compilateur Vitis AI Engine, inférence automatique de Pragma, contraintes de groupe de zones

- Améliorations apportées à Vitis AI Engine x86simulator : rapport de trace, violation d'accès mémoire et détection de blocage

- Vitis HLS EoU, amélioration de la synchronisation et de la QoR, API HLS pour l'inférence de rafales contrôlée par l'utilisateur

- Amélioration de Vitis Analyzer pour un meilleur rapport de suivi chronologique, la visualisation des données et l'analyse des blocages

- Prise en charge de processus multiples Vitis XRT pour AI Engine et de multi-threads pour le contrôle de graphique AI Engine

- L'IDE et l'émulation Vitis prennent en charge la trace AI Engine et l'émulation software pour les applications AI Engine

- 39 nouvelles bibliothèques C/C++ dans divers domaines couvrant : DSP, analyse de données, vision, compression, base de données, graphique, sécurité... Au total, plus de 1 000 fonctions de bibliothèque, de base de données, de graphes, de sécurité…

- Model Composer Vitis

- Temps de compilation/simulation x3, temps de compilation divisé par 7 avec compilation parallèle

- Nouveau flux de validation hardware et co-simulation fonctionnelle améliorée

Nouveautés Vitis par catégorie

Développez les sections ci-dessous pour en savoir plus sur les nouvelles fonctionnalités et améliorations de la plateforme software AMD Vitis 2021.2. Pour plus d'informations sur les plateformes prises en charge, les changements de comportement et les problèmes connus, reportez-vous aux notes de publication de la plateforme software Vitis 2021.2 pour le flux d'accélération des applications et le flux de développement de softwares intégrés.

Remarque : Les Vitis Accelerated Libraries sont disponibles en téléchargement séparé. Elles peuvent être téléchargées à partir de GitHub ou directement à partir de Vitis IDE.

| Bibliothèque | 2021.1 | 2021.2 | Nouvelles fonctions dans la version 21.2 |

|---|---|---|---|

| xf_blas | 167 | 167 | 0 |

| xf_codec | 3 | 3 | 0 |

| xf_DataAnalytics | 33 | 36 | 3 |

| xf_database | 62 | 65 | 3 |

| xf_compression | 78 | 93 | 15 |

| xf_dsp | 94 | 96 | 2 |

| xf_graph | 53 | 59 | 6 |

| xf_hpc | 37 | 37 | 0 |

| xf_fintech | 116 | 116 | 0 |

| xf_security | 135 | 140 | 5 |

| xf_solver | 11 | 11 | 0 |

| xf_sparse | 11 | 11 | 0 |

| xf_utils_hw | 55 | 57 | 2 |

| xf_opencv | 147 | 150 | 3 |

| total | 1002 | 1041 | 39 |

Remarque : Pour la vision, il vous suffit de compter le nombre de sous-dossiers dans L*/tests, car chaque API comporte plusieurs tests pour différents types.

Bibliothèque Vitis Vision

- Programmable Logic (PL)

- Traitement d'image mono de bout en bout (ISP) avec CLAHE TMO

- RVB-IR et pipeline de traitement d'image RVB-IR (ISP)

- Global Tone Mapping (GTM) et pipeline ISP utilisant GTM

| Nouvelles fonctionnalités | Cat | Client/stratégique | Segments | Description |

|---|---|---|---|---|

| RVB-IR | FAI | Seeing Machines | Automobile, ISM | • Prise en charge du dématriçage RVB-IR 4x4 • Principalement pour le système de surveillance en cabine • Caméra de surveillance pour les conditions de faible luminosité |

| Mono (CCCC) | FAI | Stratégique | Automobile, ISM, A&D | • Vision artificielle • Applications pour les conditions de faible luminosité |

| Global Tone Mapping (GTM) | FAI | Stratégique | Automobile, ISM, A&D | • Amélioration de la plage dynamique et du contraste • Version moins coûteuse par rapport au Local Tone Mapping (LTM) |

| Flux optique dense TV-L1 | CV | NTT | ISM | • Amélioration de la robustesse (contre l'éclairage, le bruit, les occlusions) pour le flux optique |

AI Engine (AIE)

- BlobFromImage

- Filtre 2D dos à dos avec prise en charge de la taille de lot 3

| Nouvelles fonctionnalités | Cat | Client/stratégique | Segments | Description |

|---|---|---|---|---|

| RVB-IR | FAI | Seeing Machines | Automobile, ISM | • Prise en charge du dématriçage RVB-IR 4x4 • Principalement pour le système de surveillance en cabine • Caméra de surveillance pour les conditions de faible luminosité |

| ML+X | FAI | Stratégique | Automobile, ISM, A&D | • Prétraitement des interférences ML |

| Pyramide gaussienne | CV | Stratégique | Automobile, ISM, A&D | • Principes de base pour le traitement d'images à plusieurs échelles |

| Filtre de boîte | CV | Stratégique | Automobile, ISM, A&D | • Principes de base pour le lissage, filtre passe-bas |

Bibliothèque Vitis Data Analytics

- Solution blockchain Vitis basée sur les bibliothèques Vitis

- Solutions de minage clé en main pour Ethereum

- Open source, facile à utiliser et à déployer avec les bibliothèques Vitis à l'aide de C++

- Flexible et évolutif avec les bibliothèques Vitis

- Disposez de la flexibilité nécessaire pour miner plusieurs cryptomonnaies

- Personnalisez et compilez dans le hardware

- Conception hautement optimisée

- Ajout de l'API d'analyseur CSV dans la bibliothèque

- L'analyseur CSV peut analyser des fichiers de valeurs séparées par des virgules et générer un flux d'objets qui pourrait facilement être connecté aux API DataFrame

Bibliothèque Vitis Graph

- Ajout de nouvelles bibliothèques L2

- Louvain avec renumérotage

- Renumérotation

- La fonction « weight » (poids) est prise en charge pour la similarité Cosin

Bibliothèque de base de données Vitis

- GQE commence à prendre en charge la fonction d'entrée/sortie asynchrone, ainsi que la prise en charge multi-cartes.

- La prise en charge asynchrone permet au FPGA de démarrer le traitement dès qu'une partie des données d'entrée est prête.

- La prise en charge multicarte permet d'identifier plusieurs cartes Alveo adaptées au travail.

Bibliothèque de compression de données Vitis

- Compression multi-cœur ZSTD

- Création d'une nouvelle architecture multi-cœur ZSTD et apport d'un débit > 1 Go/s en utilisant un quadricœur.

- Optimisation de décompression ZSTD

- Décompression ZSTD optimisée pour les performances (augmentation de 20 %) et les ressources (réduction < 30 %)

- Amélioration du cœur de flux GZIP/ZLIB pour IBM

- IP de diffusion de compression statique et dynamique personnalisée (4 Ko et 8 Ko)

- Ajout d'une fonctionnalité permettant de fournir une taille compressée dans le port TUSER

- Amélioration de la décompression GZIP/ZLIB pour IBM

- Décodeur huffman optimisé pour réduire la latence < 1 500 cycles

- Réduction significative des ressources de 6,9 K (plus ancien > 9 K)

- Ajout de la fonctionnalité de somme de contrôle ADLR32

- PoC du compilateur système GZIP

- Création d'un PoC de compilateur système pour la solution de compression GZIP et benchmark avec l'hôte OpenCL.

Bibliothèque DSP Vitis

- DSPLib sur Github depuis 2021

- Fast Fourier Transform (FFT/iFFT)

- Augmentation de la taille des points à 32k (selon le type de données)

- Prise en charge des API de streaming et Windows

- Puissance parallèle (0-4)

- Permet un débit plus élevé et étend la plage de tailles de points prises en charge

- Filtres FIR

- Prise en charge du flux initial pour FIR asymétrique/symétrique à débit unique

- DDS/mélangeur

- Nouvelle unité de bibliothèque dans la version 2021.2

Bibliothèque de sécurité Vitis

- KECCAK-256 (fonction de hachage) et CRC32C (fonction de somme de contrôle) publiés

Bibliothèque d'utilitaires Vitis

- Deux implémentations de Data-Mover ont été ajoutées pour résoudre un problème hardware.

- LoadDdrToStreamWithCounter : Pour le chargement de données du DDR de PL vers AI Engine via le flux AXI et l'enregistrement du nombre de données envoyées à AI Engine.

- StoreStreamToMasterWithCounter : Pour recevoir des données AI Engine via le flux AXI et les enregistrer sur le DDR du PL, ainsi que pour enregistrer le nombre de données envoyées au DDR.

API AI Engine

- Mis en œuvre en tant que bibliothèque d'en-tête C++ uniquement qui fournit des types et des opérations traduits en intrinsèques efficaces AI Engine.

- Fournit des types de données paramétrables qui permettent la programmation générique

- Met en œuvre la plupart des opérations courantes de manière uniforme pour différents types de données

- Traduit de manière fluide les primitives de niveau supérieur en intrinsèques AI Engine optimisées

- Améliore la portabilité sur les architectures AI Engine

L'API AI Engine sera la principale méthode de programmation du noyau AI Engine

Optimisations de haut niveau

Options d'optimisation du compilateur AI Engine

- --xlopt=0, aucune optimisation appliquée.

- --xlopt=1, calcul automatique de la taille du segment de mémoire, génération de guidage à partir de l'analyse IR LLVM.

- --xlopt=2, insertion automatique, retrait de boucle pour boucles non laminées, insertion de pragma.

Introduction de --xlopt=2 pour améliorer les performances, la valeur par défaut reste --xlopt=1

- Insertion automatique

- Insère automatiquement les fonctions si cela est pratique et possible, même si les fonctions ne sont pas déclarées en tant que __inline ou en ligne

- Insertion automatique pragma

- Insérez automatiquement des pragmas dans le code du noyau (voir la diapositive suivante pour plus de détails).

Inférence pragma

Nécessaire à l'optimisation des noyaux

- Allégez la responsabilité d'ajouter des pragmas d'échecs efficaces et corrects pour l'utilisateur

Prise en charge de cinq pragmas auto-infer dans la version 2021.2

- pour les performances :

- chess_prepare_for_pipelining pour la boucle la plus interne et les boucles externes avec un nombre de déclenchements connu

- chess_loop_range pour les boucles avec nombre de déclenchements connu

- chess_unroll_loop/chess_aplate_loop pour les boucles les plus internes avec un nombre de déclenchements connu

- pour l'exactitude :

- chess_unroll_loop_preamble lorsque le nombre de déclenchements n'est pas un multiple d'un facteur Unroll

Mise à jour des modèles de programmation graphique PLIO et GMIO

Les modifications de modèle comprennent :

- Les modifications apportées à l'utilisation de « simulation::platform »

- L'interaction avec les objets PLIO/GMIO dans le graphique ; la position détermine l'entrée/la sortie.

- Les modifications des objets PLIO/GMIO globaux dans le graphique.

- Les modifications apportées aux instructions graph connect<>.

PLIO/GMIO dans les graphiques ADF

Actuel

- Écrivez PLIO, GMIO, simulation::platform et connexions à portée globale

GMIO gm0(“GMIO_In0”, 64, 1);

GMIO gm1(“GMIO_In1”, 64, 1);

…

GMIO gm7(“GMIO_In7”, 64, 1);

PLIO pl0(“PLIO_Out0”, plio_32_bits, “data/output0.txt”, 250.0);

PLIO pl1(“PLIO_Out1”, plio_32_bits, “data/output1.txt”, 250.0);

…

PLIO pl7(“PLIO_Out7”, plio_32_bits, “data/output7.txt”, 250.0);

simulation::platform<8,8> plat(&gm0, &gm1,…, &gm7, &pl0, &pl1,…, &pl7,);

subgraph g;

connect<> net0(plat.src[0], g.in[0]);

connect<> net1(plat.src[1], g.in[1]);

…

connect<> net7(plat.src[7], g.in[7]);

connect<> net8(g.out[0], plat.sink[0]);

connect<> net9(g.out[1], plat.sink[1]);

…

connect<> net15(g.out[7], plat.sink[7]);

Autre méthode

- Créez un graphe principal et déplacez PLIO, GMIO et les connexions à l'intérieur

- Gérez les connexions à l'intérieur d'une boucle

class topgraph

{

input_gmio gm[8];

output_plio pl[8];

subgraph sg;

topgraph()

{

for (i=0; i<8; i++)

{

gm[i] = input_gmio::create(“GMIO_In”+std::to_string(i), 64, 1);

pl[i] = output_plio::create(“PLIO_Out”+std::to_string(i), plio_32_bits, “data/output”+std::to_string(i)+”.txt”, 250.0);

connect<>(gm[i].out[0], sg.in[i]);

connect<>(sg.out[i], pl[i].in[0]);

}

}

};

topgraph g;

Améliorations des contraintes de groupe de zones

Possibilité d'utiliser des indicateurs dans le graphique ADF ou le fichier de contraintes pour contrôler le mappeur et le routeur

- -contain_routing : lorsque la valeur true est spécifiée, l'ensemble du routage, y compris les réseaux entre les nœuds contenus dans le groupe de nœuds, est contenu dans le groupe de zones.

- -exclusive_routing : lorsque la valeur TRUE est spécifiée, tous les routages, à l'exclusion des réseaux entre les nœuds du groupe de nœuds, sont exclus du groupe de nœuds.

- -exclusive_placement : lorsque la valeur TRUE est spécifiée, tous les nœuds non inclus dans le groupe de nœuds ne sont pas placés dans la boîte englobante du groupe de zones.

Aperçus

Les aperçus sont des fichiers texte contenant des commentaires et des données relatifs à tous les ports du noyau

- flux, flux de paquets, flux en cascade

- windows, mémoire tampon

- RTP

Inclut également tous les ports de la plateforme

- PLIO, GMIO, RTP

Permet aux utilisateurs d'inspecter le trafic de données au niveau des ports du noyau sans utiliser le débogueur et sans avoir besoin d'une instrumentation du code du noyau

Détection de blocage

- Détecte les blocages dans les simulations x86 si cette situation découle de données d'entrée insuffisantes ou d'une profondeur FIFO déséquilibrée sur un chemin convergent

- La fonction stop-on-deadlock doit être activée pendant la simulation x86 en spécifiant l'option --stop-on-deadlock

- Si la simulation est arrêtée en raison d'un blocage, le message d'erreur indique que vous devez réexécuter avec l'option -trace --timeout

Détection de violation d'accès mémoire

Intégration avec Valgrind pour la détection des violations d'accès à la mémoire

- Détectez

- la lecture et l'écriture hors limites

- la lecture de la mémoire non initialisée

- Aucun indicateur spécifique requis pour la compilation

- Les indicateurs de simulation peuvent être soit

- --valgrind : la simulation s'exécute comme d'habitude et valgrind affiche un rapport

- --valgrind-gdb : même chose, mais avec gdb debug en même temps

Rapport de suivi

La situation de blocage entraîne une mauvaise sortie de simulation et des difficultés à analyser l'origine du bogue

L'option de trace de simulation X86 permet au simulateur de sauvegarder diverses informations horodatées :

- Début/fin des itérations du noyau

- Début/fin des blocages de flux

- Début/fin du blocage

Les horodatages diffèrent entre la simulation x86 et la simulation AI Engine

Inférence Burst contrôlée par l'utilisateur

- Pour les cas d'utilisation qui ne satisfont pas à l'inférence automatique des rafales par l'outil Vitis HLS, l'utilisateur peut adopter la nouvelle optimisation manuelle des rafales

- Une nouvelle classe « hls::burst_maxi » permet de prendre en charge le contrôle manuel du comportement des rafales. De nouvelles API HLS sont fournies pour être utilisées avec la nouvelle classe

- L'utilisateur doit comprendre le protocole AXI AMBA et la modélisation au niveau des transactions hardware dans la conception HLS

Améliorations de la synchronisation et de la QoR

- Fournissez une assistance à l'utilisateur pour saisir des contraintes de débit de haut niveau

- Améliorez la précision de l'estimation de la durée HLS. Lorsque HLS signale la fermeture temporelle, la synthèse RTL dans Vivado devrait également respecter le délai

Améliorations d'EoU

Ajoutez le rapport d'adaptateurs d'interface dans les rapports de synthèse C

- Les utilisateurs doivent connaître l'impact des ressources sur leur conception des adaptateurs d'interface

- Les adaptateurs d'interface ont des propriétés variables qui ont un impact sur la QoR de conception

- Certaines de ces propriétés sont associées à des contrôles utilisateur qui doivent être signalés aux utilisateurs

- La version texte des rapports bind_op et bind_storage est fournie

Ajouter une nouvelle section dans le rapport de synthèse pour afficher la liste des pragmas et des avertissements sur les pragmas

- L'utilisateur peut facilement comprendre quels sont les pragmas qui présentent des problèmes.

Améliorations de l'analyse et des rapports

La visionneuse de graphiques d'appels de fonction dispose de nouvelles fonctionnalités

- Nouvelle fonctionnalité de zoom avant et arrière basée sur le glissement de la souris

- Nouvelle fonction Aperçu qui affiche le graphique complet et permet à l'utilisateur d'effectuer un zoom avant sur des parties du graphique d'ensemble

- Toutes les fonctions et boucles sont affichées avec leurs données de simulation

Une nouvelle visionneuse de suivi de chronologie est désormais disponible après la simulation. Cette visionneuse affiche le profil d'exécution de votre conception et permet à l'utilisateur de rester dans la GUI (interface graphique utilisateur) de Vitis HLS.

Amélioration du résumé des liens

- Fournissez des informations sur la fréquence d'horloge pour AI Engine, la plateforme et les unités de calcul

- Fournissez un nouveau tableau nommé Horloges dans le schéma du système et le schéma de la plateforme

Amélioration de l'exportation de plateforme

- L'exportation XSA à partir de Vivado n'exige aucun fichier source local au projet

- L'exportation XSA à partir de Vivado sans modification de la structure du projet

- Regrouper les IP utilisées dans le projet de plateforme hardware au lieu de regrouper l'intégralité du référentiel IP

Améliorations de l'émulation d'application AI Engine

- Fournissez une assistance pour l'intégration de bancs d'essai externes avec aiesimulation

- Fournissez une assistance pour l'intégration de banc d'essai externe avec x86simulation

- Prise en charge du débogage GDB avec x86simulation

- Fournissez une prise en charge des instantanés des données entre les noyaux dans un graphique pour x86simulation

- Fournissez une assistance pour la vérification des violations d'accès à x86sim

- Fournissez une assistance pour l'arrêt sur le blocage à x86sim

Prise en charge de la trace AI Engine

Prise en charge de l'émulation software pour les applications AI Engine

Prise en charge du générateur de trafic externe dans Verilog / System Verilog

Extension de l'insertion du moniteur de profilage à la mémoire du moniteur

- Actuellement, la logique du moniteur de profilage peut être insérée en fonction du port du noyau/CU. Cette fonction permet à l'utilisateur d'insérer directement la logique de surveillance dans Memory Interface

- La visualisation de la bande passante mémoire obtenue directement sur les interfaces mémoire peut être reflétée dans le rapport récapitulatif du profil

- Les mémoires DDR et PLRAM sont prises en charge

- Le flux hardware est pris en charge

- Pour activer cette fonctionnalité, la phase de liaison et le xrt doivent être configurés

- memory=all

- data_transfer_trace= coarse|fine ou

- opencl_device_counter=true

Extension de l'insertion du moniteur de profilage à la mémoire du moniteur

- Exemple vadd permettant la surveillance de Memory Interface

- Un nouveau tableau « Transfert de données de banque de mémoire » est inclus

Améliorations apportées à Vitis Analyzer

Rapport récapitulatif de profil générique généré pour les applications non-OpenCL

- Fournissez le même niveau de prise en charge pour les applications API XRT et HAL.

- Les utilisateurs sélectionnent les types de rapports qu'ils souhaitent créer, l'outil les génère automatiquement et les visualise dans Vitis Analyzer

Ajoutez des commandes OpenCL à la chronologie des événements PL

- Le profilage ajoute des frais supplémentaires et XRT permet de vider les événements OpenCL sur le suivi chronologique sans frais supplémentaires.

- Vitis Analyzer peut traiter la sortie XRT et l'afficher dans la vue de suivi chronologique.

- xocl_debug=true doit être défini dans le fichier xrt.ini.

Mettez à plat la hiérarchie des signaux dans le rapport de suivi chronologique

- Par défaut, le rapport de suivi chronologique affiche le suivi de signal de manière hiérarchique

- Vitis Analyzer permet de mettre à plat la hiérarchie en faisant basculer le symbole « Signal mis à plat »

- La comparaison de la forme d'onde est prise en charge pour le tracé de ligne de temps mise à plat

Vitis Analyzer – Visualisation des données

- Affichez les données d'entrée/sortie vers les noyaux AI Engine dans une conception AI Engine

- Aide à déboguer les conceptions AI Engine pour afficher les données d'entrée/sortie ainsi que la chronologie

- Fonctionne avec aiesimulator

- Prend en charge

- Types de données fenêtre/flux/cascade

- Flux de paquets

- Noyaux modélisés

- utilitaire data-dump

Vitis Analyzer - Analyse du blocage AI Engine

- Vitis Analyzer offre des fonctionnalités de visualisation permettant aux utilisateurs d'identifier la cause première des blocages

- Assistance

- Mesures de performances

- Analyse de blocage du verrouillage

- Analyse de blocage de flux

- Analyse de blocage en cascade

- Analyse de blocage de la mémoire

- Flux d'assistance

- aiesimulator

- Émulation hardware

Xilinx Runtime Library (XRT) :

- API XRT

- L'API native XRT prend en charge le contrôle du noyau géré par l'utilisateur avec xrt::ip

- Utilitaires XRT

- Les outils xbutil et xbmgmt sont désormais définis par défaut

- Pour utiliser les utilitaires hérités, utilisez xbutil --legacy ou xbmgmt --legacy avec les sous-commandes héritées

- Nouvel utilitaire, xball

- Appliquez les commandes xbutil ou xbmgmt à toutes les cartes de centre de données installées ou à une partie filtrée de celles-ci. Consultez xball --help pour plus de détails

- Une nouvelle commande, xbutil configure

- Vous permet d'activer, de désactiver ou de configurer la mémoire hôte PCIe et les fonctions PCIe Peer to Peer. Pour plus d'informations, reportez-vous à la documentation XRT

- Tous les utilitaires XRT prennent désormais en charge l'option --force pour ignorer la confirmation interactive de l'utilisateur

- Les outils xbutil et xbmgmt sont désormais définis par défaut

- Profilage

- Un rapport récapitulatif de profil est généré lorsqu'une option de profilage est activée.

- Tous les tableaux récapitulatifs et toutes les instructions applicables sont générés en fonction des options de profilage activées dans le fichier xrt.ini

- Nouveau tableau récapitulatif des transferts de données pour les informations agrégées sur une ressource de mémoire lorsque des moniteurs sont ajoutés aux ressources de mémoire dans la conception

- Les nouveaux ensembles de mesures de profilage AIE permettent de compter différents événements AIE, notamment (1) les exceptions à virgule flottante dans AIE, (2) le nombre d'exécutions de vignettes et (3) les « puts » et « gets » de flux

- Intégré

- Améliorations apportées au gestionnaire de mémoire zocl pour prendre en charge n'importe quel sptag

Vitis XRT pour la prise en charge de plusieurs processus AI Engine

- API C et C++ pour définir les modes d'accès de plusieurs processus afin de partager l'accès aux mêmes graphiques et à la même matrice AI Engine.

- Protégez les graphiques et la matrice AI Engine contre tout accès indésirable.

- Trois modes sont pris en charge pour l'ouverture des graphiques et de la matrice AI Engine

- Mode exclusif (empêcher l'accès à tout autre processus)

- Mode principal (autoriser uniquement les autres processus à effectuer un accès non destructif)

- Mode partagé (accès non destructif uniquement)

- Tenez compte des cas où plusieurs processus doivent être pris en charge. Par exemple :

- Empêcher d'autres personnes d'accéder à la matrice AI Engine (accès exclusif)

- Plusieurs utilisateurs pour contrôler différents graphiques séparément (prise en charge de plusieurs applications)

- Un utilisateur principal pour contrôler le graphique et permettre aux autres d'analyser l'état d'exécution (accès principal et partagé)

État de prise en charge de Vitis XRT pour AI Engine

API C et C++

- API version C

- Pour la matrice AI Engine :

- xrtAIEDeviceOpenExclusive (mode exclusif)

- xrtAIEDeviceOpen (mode principal)

- xrtAIEDeviceOpenShared (mode partagé)

- Pour le graphique AI Engine :

- xrtGraphOpenExclusive (mode exclusif)

- xrtGraphOpen (mode principal)

- xrtGraphOpenShared (mode partagé)

- Pour la matrice AI Engine :

- API version C++

- mode d'accès de prise en charge de la classe xrt::aie::device en constructeur

- classe enum access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2 };

- mode d'accès de prise en charge de la classe xrt::graph en constructeur

- classe enum access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2, none = 3 };

- mode d'accès de prise en charge de la classe xrt::aie::device en constructeur

- Accédez aux dernières plateformes cibles Vitis pour les cartes Alveo et reportez-vous à la section Mise en route de la carte d'accélération.

- Téléchargez Vitis et consultez la section Alveo Packages

Bibliothèque DSP AI Engine – Nouveaux blocs

- DDS AIE

- Mélangeur AIE

Compilation parallèle

- Temps réduits par rapport à la version 2021.1 (par exemple, les chiffres suivants concernent la chaîne TX 200 MHz) :

- Temps de compilation et de simulation divisé par 3

- Temps de compilation divisé par 7

- Temps mort après simulation réduit de 25 s à ~0 s

Amélioration de l'éditeur de contraintes

- Navigation améliorée dans la version 2021.2

Pour les améliorations de taille fixe

Pour les améliorations des blocs de taille variable

Fonctionnalités améliorées de co-simulation fonctionnelle

- Exporter les données Matlab pour l'entrée AI Engine – xmcVitisWrite

- Importer les données AI Engine dans Matlab – xmcVitisRead

- Importer les données AI Engine dans Matlab - xmcVitisRead

Autres

- Importer un AI Engine ou un bloc de noyau HLS sans entrée (bloc source)

- Prise en charge de nouveaux types de données

- Les int64 et uint64 natifs de Simulink pour le développement AI Engine au lieu des types de données AMD, x_sfix64 et x_ufix64.

- accfloat et cacfloat pour le développement AI Engine

- Prise en charge d'Ubuntu 20.04

- Prise en charge de MATALB 20a, 20b, 21a (pas de prise en charge de MATLAB 21b)

- Ajout de nouveaux exemples

- Exemple de filtre SSR double flux avec 64 noyaux

- Pseudo inverse(64x32) – exemple commslib.

- Utilisez la commande xmcLibraryPath pour pointer vers un emplacement DSPLib personnalisé.

- De nombreuses autres améliorations et corrections de bugs

Principales caractéristiques de la version 2021.1 de Vitis Software Platform :

- Prise en charge du kit de démarrage Vision AI AMD Kria System-on-Modules (SOM) KV260. Le flux complet de Vitis pour l'apprentissage automatique (moteur d'inférence DPU) + X (noyau RTL et noyaux de vision informatique basés sur Vitis HLS). En savoir plus >

- Prise en charge des nouvelles bibliothèques C/C++ Vision, DSP, Graph (modularité Louvain), codec dans le traitement d'image, compression (GZIP, Facebook ZSTD, accélération d'applications complètes ZLIB) optimisées pour les performances sur FPGA et/ou Versal ACAP sur CPU/GPU

- Flux de conception du kit de développement de base Vitis™ amélioré sur les appareils Versal ACAP : améliorations de la visualisation pour le rapport de suivi de conception d'AI Engines, suivi des événements des AI Engines via GMIO, recompilation incrémentielle, nouvel assistant d'image de démarrage et prise en charge des fichiers source d'AI Engines chiffrés

- Le nouvel outil Vitis Model Composer permet d'explorer et de vérifier rapidement les conceptions dans l'environnement MathWorks MATALB et Simulink®, ce qui permet la co-simulation de blocs ciblant les AI Engines et Programmable Logic, la génération de code et la création de bancs d'essai.

- Nouvelle GUI (interface graphique utilisateur) du navigateur de flux HLS de Vitis pour un accès rapide aux phases de flux et aux rapports. Intégrez les vues de synthèse, d'analyse et de débogage dans un contexte général par défaut

Nouveautés Vitis par catégorie

Développez les sections ci-dessous pour en savoir plus sur les nouvelles fonctionnalités et améliorations de la plateforme software AMD Vitis 2021.1. Pour plus d'informations sur les plateformes prises en charge, les changements de comportement et les problèmes connus, reportez-vous aux notes de publication de la plateforme software Vitis 2021.1 pour le flux d'accélération des applications et le flux de développement de softwares intégrés.

Remarque : Les Vitis Accelerated Libraries sont disponibles en téléchargement séparé. Elles peuvent être téléchargées à partir de GitHub ou directement à partir de Vitis IDE.

DSP AIE

- DSPLib publié dans le cadre de la bibliothèque d'accélération Vitis définie sur Github

- DSPLib contient des fonctions DSP paramétrables courantes utilisées dans de nombreuses applications avancées de traitement des signaux. Toutes les fonctions prennent actuellement en charge les interfaces de fenêtre avec prise en charge des interfaces de diffusion.

Filtres FIR