- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

- 2020.2

- 2020.1

AMD Vitis™ 软件平台 2025.2 版本亮点

基于 Versal™ AI Engine 的设计流程优化

- 适用于 Versal AI Edge 和第二代 Versal AI Edge 系列(AIE-ML 和 AIE-ML v2)的 AI 引擎 API 增强功能

- 全新和增强的数据类型

- 新增:块浮点 MX6

- 新增:块浮点 MX4

- 新增:cbfloat16(仿真)

- 增强:cfloat 和 cbfloat16(在 FFT 和矩阵乘法函数中可用)

- 增强:cint16 和 cint32(现在可以在 FFT 中使用 cint16 旋转类型)

- 全新和增强的数据类型

- 编程模型更新

- 创建只读共享缓冲区

- 重复的 MEM 模块读取访问(AIE-ML 和 AIE-ML v2)

- AIE-ML 和 AIE-ML v2 中的 DMA-FIFO 支持

- 乒乓缓冲区可以跨越两个相邻的 MEM 模块

(AIE-ML 和 AIE-ML v2) - 本地模块内存的共享参数

- AIE-ML 和 AIE-ML v2 的分组交换增强功能

- 适用于 Versal AI Engine 的全新增强型 DSP 库函数

- 新增累积和

- 新增欧几里得距离

- 新增函数逼近(通过 RTP 更新或 LUT 调用)

- 具有分组交换功能的增强型 TDM FIR(节省 PLIO)

- 使用 AI 引擎 + PL 的增强型 1D FFT(减少所需的 PL 资源)

- 增强型 FIR(吞吐量优化)

- 改进的 AI 引擎映射器和布线器 - 编译器将探索不同的占用空间/布局策略,以提升实现效率

简化了 Versal AI Engine 设计验证

- 更新了 Vitis 功能仿真工作流程,支持 C++(抢先体验版)

- 使用 MATLAB® 和 Python 测试激励文件进行硬件在环仿真(抢先体验版)

针对 AIE DSP 设计改进了 Vitis Model Composer

- 通过 AI 引擎实现超采样率 (SSR) 设计流程的易用性更新(抢先体验版)

- 提供更多适用于 AI 引擎和 HDL 的模块:

- AIE、AIE-ML、AIE-ML v2

- 新增:函数逼近

- 新增:相关性/卷积

- 新增:累积和

- HDL 库块

- 增强:FFT(添加了原生浮点 SSR = 32、64)

- 增强:FIR(支持采用 SSR 的分数倍插值)

- AIE、AIE-ML、AIE-ML v2

针对嵌入式开发的 Vitis IDE 更新

- Python™ API 用于更新构建配置

- 在 Python 环境中运行 Vitis™ API

- 支持的核的 PS Trace 默认可见

- 调试增强功能 – 更新后的值在“监视”视图和“寄存器”视图中突出显示

- 取消或终止后端任务

- 统一平台 BSP 文件路径(Linux 和 Windows)

- Theia AI Integration(抢先体验版) – 为开发人员提供了使用其偏好的 LLM 和代码助手所需的基础设施

- 使用 Python API 创建 DFX 平台

- 备份或共享工作空间

- 增强的配置文件日志记录

- 新的"集成项目"组件

Vitis 新增内容(按类别)

展开以下部分,进一步了解 AMD Vitis 软件平台 2025.2 的新增特性与增强功能。有关支持的平台、更改的行为和已知问题等方面的信息,请参阅 Vitis 软件平台 2025.2 版本说明,了解应用加速流程和嵌入式软件开发流程。

增强的 DSP 库函数:

- 新增累积和

- 新增欧几里得距离

- 新增函数逼近(通过 RTP 更新或 LUT 调用)

- 具有分组交换功能的增强型 TDM FIR(节省 PLIO)

- 使用 AIE + PL 的增强型 1D FFT(减少所需的 PL 资源)

- 增强型 FIR(吞吐量优化)

适用于:

- Versal™ AI Core 系列(含 AIE)

- Versal AI Edge 系列(含 AIE-ML)

- 第二代 Versal AI Edge 系列(含 AIE-ML v2)

- 使用 C++ 对 Vitis 子系统进行功能仿真(抢先体验版)

- 针对 AI 引擎设计,改进了 Vitis 分析器对于延迟和吞吐量测量的支持

- 针对独立 AIE 分区的运行时控制

- 通过 AI 引擎实现超采样率 (SSR) 设计流程的易用性更新(抢先体验版)

- 提供更多适用于 AI 引擎和 HDL 的块:

- AIE、AIE-ML、AIE-ML v2

- 新增:函数逼近

- 新增:相关性/卷积

- 新增:累积和

- HDL 库块

- 增强:FFT(添加了原生浮点 SSR = 32、64)

- 增强:FIR(支持采用 SSR 的分数倍插值)

- 性能编译指示增强功能

- 性能编译指示将根据 CSIM 计算出的循环次数进行优化

- 性能编译指示优化可以转换为配置文件中的指令

- 编译指示的条件控制,包括性能编译指示

- 支持新 IP

- FIR 和 FFT 的分数速率 SSR - 对于 FFT,SPFP32 中的 SSR 现在最多支持 SSR=64。

- 通过块 RAM 或 UltraRAM 实现 ECC 对数据流缓冲区的支持

- 易于使用的功能

- 支持在 CSIM 和 CoSim 中自动重启

- 支持用于 M-AXI 的多端口高速缓存

- 提供新 API,用于具有边带信号的 AXI Stream

AMD Vitis™ 软件平台 2025.1 版本亮点

基于 Versal AI Engine 的设计流程优化

- 全新增强型 DSP 库函数、AI 引擎 API 以及对新数据类型的支持

Versal AI Core 系列(含 AIE):

- 用于 AI 引擎的增强型 GEMV 与 FFT,基于二维并行 AIE + 可编程逻辑 (PL) 架构(适用于多相信道化器)

- 矢量化双调 SIMD 排序、相关及卷积运算

Versal AI Edge 系列(含 AIE-ML):

- 用于 AIE-ML 的 FFT,基于二维并行 AIE + PL 架构(适用于多相信道化器)

- 矢量化双调 SIMD 排序、相关及卷积运算

第二代 Versal AI Edge 系列(含 AIE-ML v2):

- 二维 FFT AIE-ML v2 + PL v1(适用于多相信道化器)

- TDM FIR(适用于多相信道化器)

- GEMM/GEMV

- 单速率 FIR

- 半带 FIR

- 分数倍重采样 FIR

- 速率转换 FIR

- FFT/iFFT

- DFT

- DDS 混频器

- 函数逼近

AI 引擎编程更新:

- 针对本地存储器的平铺参数规范

- 缩短了更改测试激励文件时的编译时间

- 利用 AIE-ML 中的 DDR 乒乓缓冲器实现了更快的设计流水线

- AIE-ML 中的其他内存访问增强功能

简化了 Versal AI Engine 设计验证

- 基于 MATLAB® 和 Python™ 的 Vitis 子系统功能仿真

- 针对 AI 引擎设计,改进了 Vitis 分析器对于延迟和吞吐量测量的支持

- 针对独立 AIE 分区的运行时控制

针对 AIE DSP 设计改进了 Vitis Model Composer

- 支持多个顶层 AI 引擎子系统

- 提供更多适用于 AI 引擎和 HDL 的模块,包括支持更多 SSR 模式的增强型 FFT 以及可节省 DSP58 资源的 Complex Multiplier

针对嵌入式开发的 Vitis IDE 更新

- Vitis Unified IDE(全新图形用户界面)将为默认选项,旧版 Vitis IDE 已弃用

- 支持第三方工具链,如 GCC 和 ARMClang

- 现在,可通过 Vitis IDE 中的商城实用程序安装和获取第三方生产力工具

Vitis 新增内容(按类别)

展开以下部分,进一步了解 AMD Vitis 软件平台 2025.1 的新增特性与增强功能。有关支持的平台、更改的行为和已知问题等方面的信息,请参阅 Vitis 软件平台 2025.1 版本说明,了解应用加速流程和嵌入式软件开发流程。

Versal AI Core 系列(含 AIE):

- 用于 AI 引擎的增强型 GEMV 与 FFT,基于二维并行 AIE + 可编程逻辑 (PL) 架构(适用于多相信道化器)

- 矢量化双调 SIMD 排序、相关及卷积运算

Versal AI Edge 系列(含 AIE-ML):

- 用于 AIE-ML 的 FFT,基于二维并行 AIE + PL 架构(适用于多相信道化器)

- 矢量化双调 SIMD 排序、相关及卷积运算

第二代 Versal AI Edge 系列(含 AIE-ML v2)

- 二维 FFT AIE-ML v2 + PL v1(适用于多相信道化器)

- TDM FIR(适用于多相信道化器)

- GEMM/GEMV

- 单速率 FIR

- 半带 FIR

- 分数倍重采样 FIR

- 速率转换 FIR

- FFT/iFFT

- DFT

- DDS 混频器

- 函数逼近

- 基于 MATLAB® 和 Python™ 的 Vitis 子系统功能仿真

- 针对 AI 引擎设计,改进了 Vitis 分析器对于延迟和吞吐量测量的支持

- 针对独立 AIE 分区的运行时控制

支持多个顶层 AI 引擎子系统

提供更多适用于 AI 引擎和 HDL 的模块

AI 引擎

- 双调排序(Versal AI Core 系列、Versal AI Edge 系列、第二代 Versal AI Edge 系列)

- DFT/FFT(第二代 Versal AI Edge 系列)

- FIR – 单速率、半带、速率转换、分数倍重采样(第二代 Versal AI Edge 系列)

- DDS/混频器(第二代 Versal AI Edge 系列)

HDL 库

- 增强型 FFT – 更多 SSR 模式

- SSR 8、16、32、64(原生浮点)

- SSR 2 和 4(定点)

- 增强型 Complex Multiplier – 节省 DSP58 资源

- 新增对 CFLOAT MAC 的支持

- 矢量 IFFT 浮点运算 – 新增块

- 通过 MATLAB R2025a 中的 MATLAB (.m) 设计生成适用于 Vitis HLS 的 C++ 代码

- 全新 Vitis HLS 易用性功能

- 针对在执行过程中更改的线输入和 AXI Lite 输入(直接 I/O)进行建模

- 针对顶层 HLS 设计的性能编译指示(开放 EA)

- 通过专用的内部库对 Versal Complex Multiplier 提供支持

- Vitis HLS GUI 优化

- 通过 Clang 16 初步支持 C++17

AMD Vitis™ 软件平台 2024.2 版本亮点:

AMD Versal AI Engine DSP 设计优化

- 使用 Vitis 分析器估算延迟和吞吐量

- 使用 Vitis 分析器标记不可用的 PLIO

- 实现 AMD Versal™ AI 引擎设计的快速原型开发

- 报告堆栈和程序内存使用情况

适用于 Versal AI Engine 的全新增强型 Vitis 库函数

- 面向 AIE 的增强型 DSP 库函数(适用于 Versal AI Core、Versal Premium 系列)

- 性能增强型时分复用 (TDM) FIR 滤波器函数

- 更高性能版本的

- 一般矩阵矢量 (GEMV)

- 一般矩阵乘法 (GEMM)

- 2D IFFT — 跨 AIE + PL 进行分区以实现超高性能

- 面向 AIE-ML 的全新 DSP 库函数(适用于 Versal AI Edge)

- 性能增强的 TDM FIR 滤波器函数

- 支持 Radix-3/Radix-5 FFT

- GEMV

- GEMM

在 Vitis IDE 中新增了易用性功能(全新图形用户界面)

- 全新串口终端:监控来自硬件的串口消息

- 安装并查看第三方扩展程序

- PS 跟踪功能,用于调试和优化嵌入式系统性能

针对 AIE DSP 设计改进了 Vitis Model Composer

- AI 引擎 DSP 库更新

- AIE(适用于 Versal AI Core、Versal Premium 系列)

- 混合基数 FFT

- Stockham FFT 性能改进

- TDM FIR

- AIE-ML(适用于 Versal AI Edge 系列)

- TDM FIR

- 直接数字综合(DDS – 用于波形生成)

- 混频器(用于变频)

- AIE-MLv2(适用于第二代 Versal AI Edge 系列)

- FIR

- DFT

- DDS

- 混频器

- AIE(适用于 Versal AI Core、Versal Premium 系列)

- 为 Vitis Model Composer 添加了更多数据类型

- 支持 cbfloat16

- 针对级联信号的更多数据类型支持

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- 将 AIE/HLS 内核设计作为 Vitis子系统 (VSS) 从 Vitis Model Composer 导出到 Vitis

- 使用 Vitis 调试器调试 Vitis Model Composer 中内置的 AIE/HLS 内核

- Vitis Model Composer 中的 HDL 块集更新

- Vitis Model Composer 的其他增强功能

- 缩短了生成代码的响应时间

- 对于任何设计,仿真只运行一次

- 将 Hub 块配置另存为 JSON 文件(用于快速原型设计或批处理)

- 增加了对 MATLAB R2024a 的支持

- 增加了对 Red Hat Enterprise Linux (RHEL) 8.10、9.4 的支持

- 缩短了生成代码的响应时间

- 旨在取代设计注意事项的设计规则检查 (DRC)

面向 AIE 的增强型 DSP 库函数(适用于 Versal AI Core、Versal Premium 系列)

- 性能增强型 TDM(时分复用)FIR 滤波器函数

- 更高性能版本的

- GEMV(一般矩阵矢量)

- GEMM(一般矩阵乘法)

- 2D IFFT — 跨 AIE + PL 进行分区以实现超高性能

面向 AIE-ML 的全新 DSP 库函数(适用于 Versal AI Edge)

- 性能增强型 TDM(时分复用)FIR 滤波器函数

- 支持 Radix-3/Radix-5 FFT

- GEMV(一般矩阵矢量)

- GEMM(一般矩阵乘法)

- 使用 Vitis 分析器估算延迟和吞吐量

- 使用 Vitis 分析器标记不可用的 PLIO

- AI 引擎 DSP 库更新

- AIE(适用于 Versal AI Core、Versal Premium 系列)

- 混合基数 FFT

- Stockham FFT 性能改进

- TDM FIR

- AIE-ML(适用于 Versal AI Edge 系列)

- TDM FIR

- DDS(直接数字综合 – 用于波形生成)

- 混频器(用于变频)

- AIE-MLv2(适用于第二代 Versal AI Edge 系列)

- FIR

- DFT

- DDS

- 混频器

- AIE(适用于 Versal AI Core、Versal Premium 系列)

- 为 Vitis Model Composer 添加了更多数据类型

- 支持 cbfloat16

- 针对级联信号的更多数据类型支持

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- 将 AIE/HLS 内核设计作为 VSS(Vitis 子系统)从 Vitis Model Composer 导出到 Vitis

- 使用 Vitis 调试器调试 Vitis Model Composer 中内置的 AIE/HLS 内核

- Vitis Model Composer 中的 HDL 块集更新

- Vitis Model Composer 的其他增强功能

- 缩短了生成代码的响应时间

- 对于任何设计,仿真只运行一次

- 将 Hub 块配置另存为 JSON 文件(用于快速原型设计或批处理)

- 增加了对 MATLAB R2024a 的支持

- 增加了对 Red Hat Enterprise Linux (RHEL) 8.10、9.4 的支持

- 旨在取代设计注意事项的设计规则检查 (DRC)

- 针对在执行过程中更改的标量/线输入(直接 I/O)进行建模

- 支持任意精度浮点类型

- 将 HLS 代码映射到 DSP 块

- 用户确定的代码执行顺序

- 以用户友好的方式显示数据类型的 HLS 调试器(使用 GNU 调试器的 prettyprint 技术)

AMD Vitis™ 软件平台 2024.1 版本亮点:

AMD Versal™ AI 引擎 DSP 设计优化

- 面向 AMD Versal AI Core 系列的增强型 DSP 库函数

- 面向 SSR > 1 的时分复用 (TDM) FIR 滤波器函数

- 支持 32 位旋转的 FFT

- 混合基数 3 及混合基数 5 FFT

- Kronecker 矩阵积

- 基于 Householder 的 QRD 求解器,可提高稳定性

- 面向 SSR > 1 的 DFT

- 面向 AMD Versal AI Edge 系列(含 AIE-ML)的全新 DSP 库函数

- 支持 SSR 的一般矩阵矢量 (GEMV)

- 支持 SSR 的一般矩阵乘法 (GEMM)

- AIE API 增强

- 支持基数 3/ 基数 5 FFT

- AIE 仿真器增强

- 支持 AI 引擎与 PL 协同设计的周期近似仿真功能,无需控制、接口和处理系统 (CIPS) IP 核

- AMD Vitis 分析器支持通过 VCS、Questa、Xcelium 和 Riviera 等第三方仿真器仿真硬件

Vitis 统一软件平台的重大改进

- 新器件支持:AMD Versal™ Premium VP1902 自适应 SoC、AMD MicroBlaze™ V 处理器

- 针对 Windows® 环境的增强型嵌入式应用开发及 BSP 生成

- 由用户管理的外部编译嵌入式应用调试流程

- 全新 Bootgen 图形用户界面

- 支持平台项目增量构建

AMD Vitis IDE 的重大改进(全新图形用户界面)

- 增加了对处理子系统层级调试的支持

- 增加了对项目/工作区导出与导入的支持

- 增加了对 Python 解释器及 API 的支持

- 新特性预览页面

- 嵌入式、AIE 及平台项目的新文件变更通知

面向 AMD Versal AI Core 系列的增强型 DSP 库函数

- 面向 SSR > 1 的时分复用 (TDM) FIR 滤波器函数

- 支持 32 位旋转的 FFT

- 混合基数 3 及混合基数 5 FFT

- Kronecker 矩阵积

- 基于 Householder 的 QRD 求解器,可提高稳定性

- 面向 SSR > 1 的 DFT

面向 AMD Versal AI Edge 系列(含 AIE-ML)的全新 DSP 库函数

- 支持 SSR 的一般矩阵矢量 (GEMV)

- 支持 SSR 的一般矩阵乘法 (GEMM)

AIE API 增强

支持基数 3/ 基数 5 FFT

AI 引擎仿真器增强

- 支持 AI 引擎与 PL 协同设计的周期近似仿真功能,无需控制、接口和处理系统 IP 核 (CIPS)。

- Vitis 分析器支持通过 VCS、Questa、Xcelium 和 Riviera 等第三方仿真器仿真硬件

- 将表格从 Vitis 分析器导出为 CSV 格式

- AMD Vitis Model Composer 中新增适用于 AIE 和 AIE-ML 的 DSP 函数

- 时分复用 (TDM) FIR 滤波器函数

- 用于构建 1GSPS 多相信道化器,实现更高的吞吐量

- DFT/IDFT - 提供 SSR 支持

- 针对小尺寸进行了吞吐量/时延转换的优化

- FFT/IFFT - 针对 CINT32 位旋转提供更广泛的支持

- 混合基数 FFT/IFFT - 提供 AIE-ML 支持

- 改进了 Model Composer Hub 块的易用性

- 改进了硬件验证流程

- v 2024.1 新增了对操作系统和 MATLAB® 版本的支持:

- RHEL 9

- MATLAB R2023a 和 R2023b

Github 上提供新的设计示例。

新模具编译指示可简化图像和视频过滤器的 HLS C++ 代码

新的库函数向导可以接入 AMD Vitis 库 GitHub 仓库

- 为 AMD Vivado 设计工具创建“Solver”和“Vision”(兼容 OpenCV)IP

- 运行可用库示例

内存接口的编译指令 (ap_memory) 现在可以捆绑 AMD Vivado IP Integrator 的端口

最新 HLS 组件比较可并列显示 2 个或更多组件的指标

支持用户提供程序 RTL 代码替换 C++ 函数(黑盒流程)

代码分析器现在可解聚 C++ 结构体成员,以精细化性能分析

适用于 HLS 全局 FSM 编码和安全状态选择的新用户控制

在 C 仿真期间访问 Clang 消错工具,以执行地址及初始化检查

Vitis™ 软件平台 2023.2 版本亮点:

Versal™ AI 引擎 DSP 设计优化

- 全新 DSP 库函数

- 针对 DSP 函数的全新 API 支持

- AI 引擎编译器及仿真器的新特性

全新的独立 Vitis 嵌入式软件

- 为针对 Arm® 嵌入式子系统编写 C 代码的设计人员提供的较小独立式安装程序

- 提供了所有的嵌入式特性,其中包括 Bootgen 和 XSCT 等实用工具

全新 Vitis 统一集成型设计环境

- 在所有 Vitis 工作流程中提供一致的图形用户界面和 CLI

- 基于 Eclipse Theia 的新一代图形用户界面提供更优的灵活性与用户友好特性,显著提升工作效率

适用于 AI 引擎的全新 DSP 库函数

- 混合基数 FFT

- Discrete Fourier Transform (DFT)

- 一般矩阵矢量乘法 (GEMV)

针对 DSP 函数的全新 API 支持

- 支持 cint32 旋转数据类型的 FFT IP

- 支持 Radix-4 FFT API 的 cint16

- 在 API 中实现了矢量化“fix2flt”和“flt2fix”

针对 AIE-ML 的全新 API 支持

- API 现在支持在 sliding_mul() 函数中使用 int32/cint32 数据类型

- API 现在支持在 sliding_mul() 函数中使用 <float> 数据类型

- 提供支持稀疏矩阵乘法所需的所有 AIE API 例程

主要组件更新:

- U-boot 2024.1

- Arm Trusted Firmware 2.10

- Linux Kernel 6.6_LTS

- Qemu 8.1

- Xen 4.18

- OpenAMP 2023.10

已停止支持的 BSP:

- AMD Microblaze™:VCU118、KCU105、KC705、AC701

- Zynq:zc706

- AMD Versal™:VMK180-EMMC、VMK180-OSPI

- Zynq MP:ZCU111

新 BSP (XSCT):

- VEK280 量产版 BSP(含全新以太网 PHY 支持)

新的基于系统设备树 (SDT) 流程的 BSP:

- ZCU102、ZCU104、ZCU105、ZCU216

- ZCU208、ZCU208-sdfec、ZCU670

- VCK190

- VMK180

- VPK120

- VPK180

- VEK280

- AIE 编译器现在可按输入输出支持 2D 及 3D 阵列

- Vitis 分析器现在可生成指导报告来调整 FIFO 大小

- 为多线程仿真器内核及值更改转储 (VCD) 分析器加速提供的最新支持

- 与 MATLAB® 环境和 Python 流量生成器的外部接口连接

- 增强型 AXI Stream 模型,支持 PLIO 对齐中的空周期/等待周期

- 增强型设计规则检查

- 通过高速调试实现的 AI 引擎跟踪分载

- Vitis 环境中的 NoC 和硬 DDRMC 剖析支持

- Vitis 工具现在支持 VEK280 和 Alveo™ V70 AI 推理加速器卡的 AIE-ML 跟踪

- AI 引擎块更新

- 支持将 AIE-ML 计算图按块导入 Vitis Model Composer 中

- 用于在 Vitis Model Composer 中实现 AIE 和 AIE-ML 的最新 DSPlib 函数

- 在 Simulink® 工具中针对内部信号绘制 AIE 仿真器输出图

- HLS 内核块更新

- 自动生成测试激励文件

- 扩大了 HLS 内核块的数据类型支持范围

- Vitis Model Composer 和 Vitis 工具的完美整合

- 直接从 Vitis Model Composer 生成 .xo 和 libadf.a 文件

- 其他增强功能

- MATLAB® 工具版本支持:R2021a、R2021b Update 6、R2022a Update 6、R2022b

- 硬件验证流程支持更多拓扑

- GitHub 提供新的示例附属资料

- 面向 HLS 组件的全新 Vitis Unified IDE

- 最新 Vitis HLS 许可证要求

- 用于在运行 C 综合之前获得性能估计的最新代码分析器特性

- AXI 接口的增强功能:

- 支持 HLS AXI Stream 侧信道

- 支持用户可配置的 AXI 主接口缓存

- 其他增强功能:

- 新的代码复杂性报告,可在 C 合成过程中识别设计大小问题

- 编译时间缩短:与 2023.1 相比,2023.2 的平均编译时间缩短 20%1

Vitis 软件平台 2023.1 版本亮点:

适用于 Versal™ AI Engine (AIE) 阵列的全新 Vitis™ 库函数

- DSP 库函数 - 更多 FIR 滤波器配置

- 求解器库函数 - 功能增强,性能提升

针对 Versal AI Core 和 AI Edge 系列的设计流程增强

- 为作为输入/输出的 2D 及 3D 阵列提供 AIE 编译器支持

- 为 FIFO 容量规划提供 AIE 仿真器指导支持,以避免死锁情况

- AIE 状态报告增强

- Vitis 分析器的最新默认图形用户界面

支持 Vitis 环境导出到 Vivado™ 环境

- 助力 Vitis 及 Vivado 工具开发团队基于通用接口检查点并行工作

DSP 库 - FIR 滤波器

- 增强型分数倍重采样 FIR、单速率 FIR、半带 FIR 及速率转换 FIR 滤波器,支持系数位宽大于数据位宽

- 分数倍重采样 FIR 还支持使用多个 AIE 计算单元的 SSR 操作,并整合系数重载功能

求解器库

- 通过高性能串流设计(大约 300 个计算单元)优化 API 性能

- 为 4D 数据移动器函数提供 QR 及 Cholesky 分解支持,协助从 AIE 阵列读取或写入数据

- 除 1D 外,AIE 编译器现在可按输入输出支持 2D 及 3D 阵列。

- AIE 编译器支持嵌套计算图构造(子计算图)和条件端口构造。

- 全新 AIE CINT 至 CFLOAT 数据转换 API。

- AIE 状态报告增强功能,用于生成一个文件,其中包含有关设计中 AIE-ML 和 AIE 计算单元上的计算单元、事件及其他寄存器的信息。

- 通过高速差分(信号)对 (HSDP) 分载 AIE 事件跟踪,而不是将其存储在 Versal 器件的内存中。

- Vitis 环境中的 NoC 和硬 DDR MC 剖析支持。

- AIE 窗口事件跟踪,可用于检查应用的特定部分。

- FIFO 容量规划指南,以免死锁。

- 能够选择 AIE 仿真器报告的节点,以缩小仿真器 VCD 文件的大小并加速仿真。

- AIE 仿真器现在可生成一个报告(其可在 Vitis 分析器中查看),该报告会显示哪个 AIE 有内存访问违例,以及这些违例如何与计算图 C 代码中的行对应。

- 此外,跟踪视图数据可视化现在还支持 AIE-ML 阵列。

- 为针对 Versal AI Engine 的 FIR 滤波器配置提供最新数据类型支持

- 在 Versal 自适应 SoC 中提供针对 DSP58 优化的两个新浮点函数

- 所有面向 Versal AI Engine 的 Vitis Model Composer 库函数的响应速度更快

- 其他增强功能:

- HLS 内核块的增强功能

- Vitis Model Composer Hub 的增强功能

- 支持 MATLAB 工具 R2021a、R2021b 以及 R2022a 版本

- 性能提升2:与 2022.2 相比,2023.1 的平均时延缩短了 5.2%

- 在 Vitis HLS 工具中下载、查看和实例化 L1 库函数的简单方法

- 在 Vitis HLS 工具中增强了对 AXI 事务处理及突发报告的支持

Vitis 软件平台 2022.2 版本亮点:

适用于 Versal™ AI Engine (AIE) 阵列的全新 Vitis™ 库函数

- DSP 库函数 – 增强特性

- 求解器库函数

- 视觉库函数

- 超声库函数

针对 Versal AI Core 和 AI Edge 系列的设计流程增强

- 在 AI 引擎阵列中控制内核的相对位置,提升性能和利用率

- AIE x86 仿真器增强功能 - 在 x86 仿真器中改进了死锁条件的建模

- AIE API 增强功能 - 增加了基数 3/5 FFT 和矩阵“x”矢量 API

- 增强了 Versal 设计的分析和调试功能 - 支持死锁检测、更大规模的跟踪数据收集以及 RTL/Python 测试激励文件

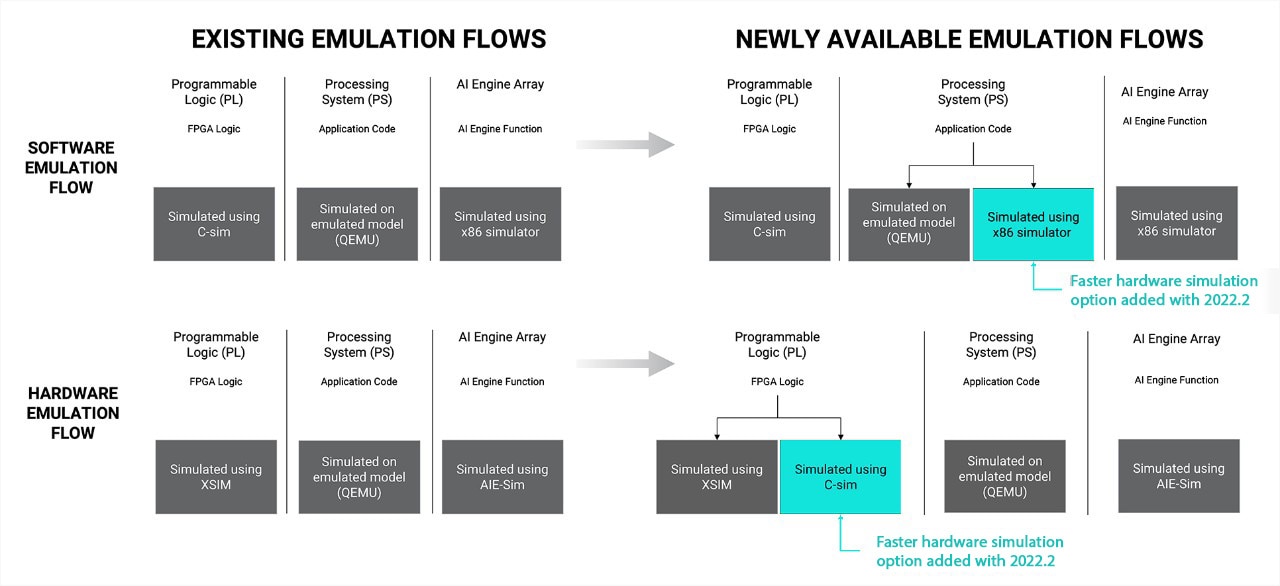

- 在 Vitis 中为异构设计提供了新的仿真选项

DSP 库函数

- AI 引擎上的超采样率 (SSR) FIR 滤波器执行方案现在支持系数重新加载特性和动态点大小

- 为面向 AI 引擎阵列的 FFT 函数新增 FFT 开窗元件

求解器库函数

- 正交旋转 (QR) 分解

- Cholesky 分解

视觉库函数

- 面向 AI 引擎阵列的四个新视频函数

超声库函数

- 协助构建医疗超声设计的各种函数

- 能够通过添加约束来控制 AI 引擎阵列中内核的相对位置,有助于用户提高性能和利用率

- 改进了 x86 仿真器中 AIE 死锁条件的建模

- 新增 AIE API,增加了基数 3/5 FFT 和矩阵“x”矢量 API

- 在硬件仿真中生成 AI 引擎剖析报告

- 使用 AMD 系统调试器 (XSDB) 对 AI 引擎设计以及基于 PL 的设计进行死锁检测

- Xilinx 运行时 (XRT) 控制的 AI 引擎事件跟踪通过 PLIO 持续分载

- Versal AI Engine 设计的特点

- 能够为 AI 引擎 DSP 库块设计添加计算图约束,从而可提高利用率和性能

- 为 AI 引擎设计提供周期近似仿真的新功能

- AI 引擎计算图导入块可自动检测运行时参数 (RTP) 端口

- DSP 库块的增强功能和新增功能

- 一般功能

- 为使用 PL 及 AIE 阵列的异构系统设计提供了硬件验证流程支持

- 更新了 Vitis Model Composer Hub 块以支持异构设计

- 自动检测有效的 AI 引擎、HDL 和 HLS 子系统

- 针对 HDL 专用设计以及 Versal 平台的 HDL → AI 引擎 → HDL 设计增强了硬件验证流程

- 改进的“任务级别并行处理”编码风格支持

- 实现更快的 C 仿真和更好的 QoR

- 性能和时序方面的额外改进

- 改进了突发推理

- 自动推断 Unroll、Pipeline、Array_Partition 和 inline 编译指示以实现更好的性能

- 提高了定时精度,能够以更高的频率更完美地完成时序收敛

- 其他功能

- 分析和调试:现在支持在 C 代码中插入的 printf,即使在 RTL 中综合后也是如此

- 易用性:新的性能编译指示可自动实现给定的事务处理时间间隔

- FFT 和 FIR IP 现在支持 HLS::stream 接口

Vitis 软件平台 2022.1 版本亮点:

面向 Versal™ ACAP 和 AI 引擎的 Vitis™ 流程提升

- 支持 AMD 基础 DFX 平台,该平台具有一个静态区域和一个 DFX 区域

- AIE 剖析不仅支持失速/死锁检测,而且还可在 Vitis 分析器中生成 AI 引擎状态(包括错误事件)视图报告

- x86sim、AIEsim 和软件仿真中的外部流量生成器现可实现更高灵活性,并可便捷嵌入仿真和硬件仿真流程中

- Vitis Model Composer 支持硬件验证、Linux 和硬件仿真

面向 DC 的 Vitis 和 Vitis HLS

- Vitis 可为动态区域生成进程和流量报告增强功能提供额外的报告支持,包括 3 个全新或更新的报告

- Vitis 改进了 PL 剖析,提供了将追踪分载至存储器资源(首选)或分载至 PL 中的 FIFO 的选项,从而提升了性能

- 现已提供在仿真后可用的全新时间轴跟踪查看器,其可显示运行时概况,并允许用户留在 Vitis HLS GUI 中

- 通过新的性能编译指示或 set_performance_directive,Vitis HLS 现在可支持更高层次的“智能”构造

- Vitis Graph Library,通过 L3 API 增强功能(单次内核调用节省 1mS 的时间)实现性能优化

- 新增基因组学加速器库(L1、L2 和 L3)

- Graph Library,通过 L3 增强功能实现性能优化

- Vitis Database 库、GQE 多功能内核

- 在视觉库中增加了新函数

- Vitis AIE 视觉库增加/增强的新函数

- Vitis AIE DSP 库,FIR 重采样器取代 FIR 分数插值器

- Vitis 编解码器库新 API,API jxlEnc、API“leptonEnc”、API“resize”、API“WebpEnc”

Vitis 数据压缩库

- ZLIB 压缩改进,为 8KB 解决方案提供了定制八核压缩

- ZLIB 解压改进,为 8KB 文件大小提供了定制 IP

- 平台功能查询改进

- HBM 易用性改进,能够为 M_AXI 内核选择一个进入 HMSS 的特定 S_AXI 入口点,并可从配置文件支持 RAMA 插入

Vitis AI Engine 编译器

- AI 引擎的硬件自动失速/死锁检测和分析

- 分析自动状态输出

- 分析自动状态输出 - 缓冲区

- 分析硬件手动状态输出

- 分析手动状态输出

- AI 引擎事件跟踪增强

- 外部流量生成器 AIEsim

- AI 引擎硬件剖析改进

- AI 引擎支持广播窗口

- Vitis AI Engine 编译器增强了计算图编程模型

- Vitis AI Engine 编译器 - ADF 计算图中的 PLIO/GMIO

Vitis HLS

- 增强分析功能,全新时间轴跟踪查看器

- 编码风格增强,为块流类型提供阵列分区支持

- 编译指示抽象,最新性能编译指示(和指令)

- Vitis Core“单行方式”Vitis HLS - 全新时间轴跟踪查看器、全新 PERFORMANCE 编译指示、块流支持窗口

- 推出新的查看器

- 显示设计中所有存活函数(即那些转换到模块的函数)的运行时配置文件

- 查看数据流区域在协同仿真后的行为特别实用

- Vitis HLS 原生 - 不再需要启动 xsim 波形查看器(外部工具)

Vitis 分析器

- 改进了 Vitis 分析器,保存/恢复时间轴自定义

- 报告增强、report_qor_assessment、xclbin 时钟信息、Vivado 自动摘要

- 增强了剖析功能,启用全新 PL 剖析基础设施,可以添加多个 trace_memory 选项来插入多个内存监控器(仅限硬件),v++ 链接器的示例配置文件不仅可将 SLR0 中所有 CU 的跟踪数据分载至 DDR0,而且还可将 SLR1 中所有 CU 的跟踪数据分载至 DDR1

Vitis IDE

- 为 Versal 更新了 Bootgen 图形用户界面

- 工具链更新

- XSCT,支持 STAPL 并添加链接器脚本生成命令

- 系统编译流程,请参见系统编译文档

Vitis 仿真

- 为自动重启添加软件仿真支持并为始终运行的内核添加邮箱支持

- 自由运行的内核不需要为 sw-emu 提供 while(1)

- 为外部流量生成器添加软件仿真支持

- 硬件仿真可以为流式处理 IP 使用 HLS C 源代码函数模型。

- 增加 API xrt::system,用于剖析器件数量

- 为日志消息添加 API xrt::message

- XRT 本地 API 主机代码现在需要

-std=c++17 或以上 - 为同步执行异步运行添加实验性 xrt::queue API

- xbutil 可以显示 AIE FIFO 计数器,其有助于调试 AIE 死锁场景

- xbutil --legacy 选项已删除。

- xclbinutil --info 可为嵌入式平台提供时钟信息

- ARM 上的 xbutil 可加载 SOM 镜像

- xbtop 独立实用工具,用于显示 Linux top 类似输出(取代传统 xbutil -top)

- XRT 实用工具支持在 Bash 中使用制表键自动补全。

- Alveo 平台更新、可实现更高稳定性的平台更新、板卡管理更新、SC 固件更新工具

- 嵌入式平台,新的 VCK190 DFX 平台:xilinx_vck190_base_DFX_202210_1,嵌入式平台现已随 Vitis 一起安装,Vivado 新增了一个新的可定制示例设计:面向 MPSoC 的 Vitis 平台

- 针对可扩展性和易用性对 Vitis Model Composer hub 块进行了重大升级

- 硬件验证流程现在除了支持裸机外,还支持 Linux

- “AIE 到 HDL”和“HDL 到 AIE”块不再包括 HDL 网关

- 2022.1 现在随附示例快照,供无法访问互联网的客户使用。发布新版示例后,该工具将提示用户从 GitHub 下载新版示例

- 为了便于使用,不属于代码生成部分的实用工具块现在以白色为背景

- 为了方便使用,增强并重组了库浏览器

- 支持 RHEL 8.x

- MATLAB 支持 - R2021a 和 R2021b

Vitis 软件平台 2021.2 版本亮点:

- 特定领域的全新开发环境

- 全面端到端流程支持 VCK5000 和 Varium C1100 卡

- 增强的核工具功能

- Vitis AI Engine Compiler C/C++ 高层次抽象 API、自动编译指示推断及区域组约束功能

- Vitis AI Engine x86 仿真器增强功能:跟踪报告、内存访问违例和死锁检测

- Vitis HLS EoU、时序和 QoR 增强、HLS API,用于用户控制的突发推断

- 改进了 Vitis 分析器,可提供更好的时间轴跟踪报告、数据可视化、停滞分析

- 面向 AI 引擎多进程的 Vitis XRT 和面向 AI 引擎计算图控制的多线程支持

- Vitis IDE 和仿真支持 AI 引擎跟踪和软件仿真,适用于 AI 引擎应用

- 不同域中 39 个全新 C/C++ 库涵盖 DSP、数据分析、视觉、压缩、数据库、计算图、安全,……总计超过 1000 个库函数、数据库、计算图、安全……

- Vitis Model Composer

- 并行编译将编译/仿真时间缩短 3 倍,将编译时间缩短 7 倍

- 全新的硬件验证流程和增强的功能协同仿真

注意:Vitis 加速库可单独下载。它们可以从 GitHub 下载,也可以直接从 Vitis IDE 中下载。

| 库 | 2021.1 | 2021.2 | 21.2 版的新函数 |

|---|---|---|---|

| xf_blas | 167 | 167 | 0 |

| xf_codec | 3 | 3 | 0 |

| xf_DataAnalytics | 33 | 36 | 3 |

| xf_database | 62 | 65 | 3 |

| xf_compression | 78 | 93 | 15 |

| xf_dsp | 94 | 96 | 2 |

| xf_graph | 53 | 59 | 6 |

| xf_hpc | 37 | 37 | 0 |

| xf_fintech | 116 | 116 | 0 |

| xf_security | 135 | 140 | 5 |

| xf_solver | 11 | 11 | 0 |

| xf_sparse | 11 | 11 | 0 |

| xf_utils_hw | 55 | 57 | 2 |

| xf_opencv | 147 | 150 | 3 |

| 总计 | 1002 | 1041 | 39 |

注意:对于视觉,只需统计 L*/test 中的子文件夹数,因为每个 API 都有针对不同类型的多个测试

Vitis 视觉库

- 可编程逻辑 (PL)

- 基于 CLAHE TMO 的端到端单声道图像处理 (ISP)

- RGB-IR 和 RGB-IR 图像处理 (ISP) 流水线

- 全局色调映射 (GTM) 以及使用 GTM 的 ISP 流水线

| 全新功能 | 目录 | 客户/战略 | 细分市场 | 描述 |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | 汽车、ISM | •支持 4x4 RGB-IR 去马赛克 •主要用于舱内监控系统 •微光监控摄像头 |

| 单通道 (CCCC) | ISP | 战略性 | 汽车,ISM,A&D | •机器视觉 •低光应用 |

| 全局色调映射 (GTM) | ISP | 战略性 | 汽车,ISM,A&D | •扩大了动态范围,提高了对比度 •与本地色调映射 (LTM) 相比,是一个成本更低的版本 |

| 密集光流算法 TV-L1 | CV | NTT | ISM | •改进了光流对光照、噪声及遮挡的稳定性 |

AI 引擎 (AIE)

- BlobFromImage

- 支持批量 3 的背靠背 filter2D

| 全新功能 | 目录 | 客户/战略 | 细分市场 | 描述 |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | 汽车、ISM | •支持 4x4 RGB-IR 去马赛克 •主要用于舱内监控系统 •微光监控摄像头 |

| ML+X | ISP | 战略性 | 汽车,ISM,A&D | •ML 干扰预处理 |

| 高斯金字塔 | CV | 战略性 | 汽车,ISM,A&D | •多尺度图像处理的基本知识 |

| 方框滤波器 | CV | 战略性 | 汽车,ISM,A&D | •流畅低通滤波器的基本知识 |

Vitis 数据分析库

- 基于 Vitis 库的 Vitis 区块链解决方案

- 以太坊的开创性采矿解决方案

- 使用 C++ 通过 Vitis 库实现开源与易用性及易于部署性

- 通过 Vitis 库实现灵活性和可扩展性

- 灵活地开采多种比特币

- 定制并编译成硬件

- 高度优化的设计

- 将 CSV 解析器 API 添加到库中

- CSV 解析器可解析逗号分隔值文件并生成对象流,其可轻松与 DataFrame API 连接

Vitis Graph Library

- 新增全新 L2 库

- Louvain 与重新编号

- 重新编号

- 余弦相似度支持“权重”特性

Vitis Database 库

- GQE 开始支持异步输入/输出功能,并支持多卡。

- 异步支持允许 FPGA 在部分输入数据准备就绪时立即开始处理。

- 多卡支持允许识别多个适合工作的 Alveo 卡。

Vitis 数据压缩库

- ZSTD 多核压缩

- 创建了新的 ZSTD 多核架构,并使用四核提供了 >1GB/s 的吞吐量。

- ZSTD 解压缩优化

- ZSTD 解压缩针对性能(提升 20%)和资源(减少 <30%)进行了优化

- 针对 IBM 的 GZIP/ZLIB 流处理核心改进方案

- 自定义静态和动态压缩流式处理 IP(4KB 和 8KB)

- 增加了在 TUSER 端口提供压缩量的功能

- 针对 IBM 的 GZIP/ZLIB 解压缩改进

- 经过优化的 Huffman 解码器可将延迟缩短到 < 1.5K 个周期

- 资源锐减到 6.9K(以前 > 9K)

- 添加 ADLR32 校验和功能

- GZIP 系统编译器 PoC

- 开发了面向 GZIP 压缩解决方案的系统编译器 PoC,并针对 OpenCL 主机进行了基准测试。

Vitis DSP 库

- 自 2021 年起,在 Github 上提供 DSPLib

- 快速傅立叶变换 (FFT/iFFT)

- 点大小增加到 32k(取决于数据类型)

- 支持数据流 API 和窗口 API

- 并行功率 (0-4)

- 允许更高的吞吐量并扩展支持的点大小范围

- FIR 滤波器

- 对单速率非对称/对称 FIR 的初始流支持

- DDS/混频器

- 2021.2 中的全新库单元

Vitis 安全库

- 发布 KECCAK-256(散列函数)和 CRC32C(校验和函数)

Vitis 实用工具库

- 为调试硬件问题添加了两个数据移动器实现方案。

- LoadDdrToStreamWithCounter:用于通过 AXI 流把 PL 的 DDR 数据加载至 AI 引擎,并记录发送至 AI 引擎的数据数。

- StoreStreamToMasterWithCounter:用于通过 AXI 流从 AI 引擎接收数据并将其保存至 PL 的 DDR,同时记录发送至 DDR 的数据数。

AI 引擎 API

- 按 C++ 报头专用文件库实现,其所提供的类型和运算可转换为有效的 AI 引擎内嵌原语。

- 提供的可参数化数据类型可实现泛型编程

- 以统一的方式为不同的数据类型实现最常见的运算

- 透明地将高级原语转换为优化的 AI 引擎内嵌原语

- 提高 AI 引擎架构间的可移植性

AI 引擎 API 将是 AI 引擎内核编程的主要方法

高层次优化

AI 引擎编译器优化选项

- --xlopt=0,没有应用优化。

- --xlopt=1,自动计算堆量,根据 LLVM IR 分析生成指导。

- --xlopt=2,自动内联、为展开的环路剥离环路并进行编译指示插入。

引入 --xlopt=2,以提高性能,默认情况下仍是 --xlopt=1

- 自动内联

- 即使函数未声明为 __inline 或 inline,但如果切实可行,则会自动内联函数

- 自动插入编译指示

- 自动将编译指示插入内核代码。(查看下一张幻灯片,了解更多详情)

编译指示推断

必须优化内核

- 减轻用户添加有效而正确的象棋编译指示的责任

2021.2 中支持自动推断五种编译指示

- 对于性能:

- chess_prepare_for_pipelining 用于最内循环和具有已知循环次数的外部循环

- Chess_loop_range 用于已知循环次数

- chess_unroll_loop/chess_flatten_loop 用于已知循环次数的最内层环路

- 对于正确性:

- chess_unroll_loop_preamble 用于循环次数不是展开系数的倍数的情况

更新了计算图编程模型 PLIO 和 GMIO

模型变化包括:

- “simulation::platform”用法的变化

- 与计算图中的 PLIO/GMIO 对象交互,位置可确定输入输出。

- 计算图中全局 PLIO/GMIO 对象的变化。

- 与计算图 connect<> 语句有关的更改。

ADF 计算图中的 PLIO/GMIO

当前

- 在全局范围内写入 PLIO、GMIO、simulation::platform 和连接

GMIO gm0(“GMIO_In0”, 64, 1);

GMIO gm1(“GMIO_In1”, 64, 1);

…

GMIO gm7(“GMIO_In7”, 64, 1);

PLIO pl0(“PLIO_Out0”, plio_32_bits, “data/output0.txt”, 250.0);

PLIO pl1(“PLIO_Out1”, plio_32_bits, “data/output1.txt”, 250.0);

…

PLIO pl7(“PLIO_Out7”, plio_32_bits, “data/output7.txt”, 250.0);

simulation::platform<8,8> plat(&gm0, &gm1,…, &gm7, &pl0, &pl1,…, &pl7,);

subgraph g;

connect<> net0(plat.src[0], g.in[0]);

connect<> net1(plat.src[1], g.in[1]);

…

connect<> net7(plat.src[7], g.in[7]);

connect<> net8(g.out[0], plat.sink[0]);

connect<> net9(g.out[1], plat.sink[1]);

…

connect<> net15(g.out[7], plat.sink[7]);

其他方法

- 创建顶层计算图并在其中移动 PLIO、GMIO 和连接

- 允许针对环路内部管理连接

class topgraph

{

input_gmio gm[8];

output_plio pl[8];

subgraph sg;

topgraph()

{

for (i=0; i<8; i++)

{

gm[i] = input_gmio::create(“GMIO_In”+std::to_string(i), 64, 1);

pl[i] = output_plio::create(“PLIO_Out”+std::to_string(i), plio_32_bits, “data/output”+std::to_string(i)+”.txt”, 250.0);

connect<>(gm[i].out[0], sg.in[i]);

connect<>(sg.out[i], pl[i].in[0]);

}

}

};

topgraph g;

区域组约束改进

能够在 ADF 计算图或约束文件中使用标志,以控制映射器和路由器

- -contain_routing - 当指定的真实值可确保所有路由时,包括 nodeGroup 中包含的节点之间的网,都包含在区域组中。

- -exclusive_routing - 当指定的真实值可确保所有路由时,除了 nodeGroup 的节点之间的网,都可从区域组中排除。

- -exclusive_placement - 当指定的真实值可防止未包含在 nodeGroup 中的所有节点被布置在区域组边界框中时。

快照

快照是包含与所有内核端口相关的注释和数据的文本文件

- 数据流、软件包数据流、级联数据流

- Windows、缓冲区

- RTP

还包括所有平台端口

- PLIO、GMIO、RTP

允许用户在不使用调试器和不需要检测内核代码的情况下检查内核端口上的数据流量

死锁检测

- 在 x86 仿真中检测锁死,无论这种情况是由输入数据不足引起的,还是由于重新收敛路径上的 FIFO 深度不平衡引起的,均是如此

- 在 x86 仿真过程中,必须通过指定 --stop-on-deadlock 选项来启用锁死停止特性

- 如果仿真因锁死而停止,则错误消息将指示您应该使用 -trace --timeout 选项重新运行

内存访问冲突检查

与 Valgrind 集成,以便进行内存访问冲突检查

- 检测

- 读写超出界限

- 读取未初始化的内存

- 编译无需特定标志

- 封装标志可以是:

- --valgrind:仿真照常运行,Valgrind 显示报告

- --valgrind-gdb:情况是一样的,但同时要使用 gdb 调试

追踪报告

锁死情况会导致仿真输出差,难以分析漏洞来源

X86 仿真跟踪选项允许仿真器为各种时间戳信息提供日志:

- 内核迭代的开始/结束

- 数据流停止的开始/结束

- 锁定失速的开始/结束

x86 仿真和 AI 引擎仿真的时间戳不同

用户控制的突发推理

- 对于 Vitis HLS 工具无法满足自动突发推断的使用案例,用户可以采用新引入的手动突发优化功能

- 新类别“hls::burst_maxi”支持手动控制突发行为。提供全新 HLS API,与新类别一起使用

- 在 HLS 设计中,用户需要了解 AXI AMBA 协议和硬件事务处理层面的建模

时序与 QoR 增强

- 为用户输入高层次吞吐量限制提供支持

- 提高了 HLS 时序估算精度。当 HLS 报告时序收敛时,Vivado 的 RTL 综合也应预期满足时序要求

EoU 增强

在 C 语言综合报告中添加接口适配器报告

- 用户需要知道接口适配器对其设计的资源影响

- 接口适配器具有可影响设计 QoR 的可变属性

- 其中一些属性的相关用户控件应该向用户报告

- 提供 bind_op 和 bind_storage 报告的文字版本

在综合报告中添加新章节,以显示编译指示列表和编译指示警告

- 用户可以轻松了解添加的哪些编译指示有问题。

增强分析与报告功能

函数调用图查看器有一些新特性

- 全新鼠标拖动式缩放功能

- 全新概观特性,不仅可显示全图,而且用户还可放大整体图形的各部位

- 所有函数及环路都与它们的仿真数据一起显示

现已提供可在仿真后使用的全新时间轴跟踪查看器。该查看器可显示设计的运行时概况,并允许用户保留在 Vitis HLS GUI 中。

链接摘要增强功能

- 为 AI 引擎、平台和计算单元提供时钟频率信息

- 在系统图和平台图中提供一个名为时钟的新表

平台导出增强功能

- XSA 从 Vivado 导出,不需要源文件位于项目本地

- XSA 从 Vivado 导出,不会改变项目结构

- 对硬件平台项目中使用的 IP 进行打包,而不是对整个 IP 资源库进行打包

AI 引擎应用仿真增强功能

- 为外部测试激励文件集成 aiesimulation 提供支持

- 为 x86 仿真环境的外部测试记录文件集成提供支持

- 通过 x86 仿真支持 GDB 调试

- 在 x86 仿真图中为内核间的数据提供快照支持

- 为 x86sim 的访问违规检查提供支持

- 为 x86sim 的锁死停止提供支持

支持 AI 引擎跟踪

为 AI 引擎应用提供软件仿真支持

支持 Verilog / System Verilog 环境下的外部流量生成器

扩展剖析监控器插入,以监控内存

- 目前,剖析监控器逻辑可以在内核/CU 端口基础上插入。该特性为用户提供了直接在内存接口上插入监控器逻辑的选项

- 在内存接口上直接实现的内存带宽可视化,可以在配置文件报告中反映出来

- 支持 DDR 内存和 PLRAM

- 支持硬件流程

- 要启用此功能,需要设置链接相位和 XRT

- memory=all

- data_transfer_trace= coarse|fine 或

- opencl_device_counter=true

扩展剖析监控器插入,以监控内存

- 启用内存接口监视的 vadd 示例

- 添加了一个新的“存储体数据传输”表格

Vitis 分析器增强功能

为非 OpenCL 应用生成的通用配置文件摘要报告

- 为 XRT API 和 HAL API 应用提供相同级别的支持。

- 用户选择他们想要创建的报告类型,工具会自动在 Vitis 分析器中生成并显示

将 OpenCL 命令添加到 PL 事件时间轴

- 剖析将增加开销,XRT 提供在不增加开销的情况下,在时间轴跟踪中转储 OpenCL 事件的功能。

- Vitis 分析器可以处理 XRT 输出并在时间轴跟踪视图中显示。

- xocl_debug =true 需要在 xrt.ini 中设置。

在时间轴跟踪报告中扁平化信号层级

- 在默认情况下,时间轴跟踪报告以层级方式显示信号跟踪

- Vitis 分析器提供通过切换“Flatten Signal”符号来扁平化层级的功能

- 为平铺时间轴跟踪提供比较波形的支持

Vitis 分析器 - 数据可视化

- 在 AI 引擎设计中向 AI 引擎内核显示输入/输出数据

- 帮助调试 AI 引擎设计以显示输入/输出数据以及时间轴

- 与 aiesimulator 联合使用

- 支持

- 窗口/流/级联数据类型

- 分组数据流

- 模板化内核

- 数据转储实用工具

Vitis 分析器 - AI 引擎失速分析

- Vitis 分析器提供可视化功能,帮助用户识别失速的根源

- 支持

- 性能指标

- 锁定失速分析

- 数据流停止分析

- 级联失速分析

- 内存失速分析

- 支持流程

- aiesimulator

- 硬件仿真

Xilinx 运行时库 (XRT):

- XRT API

- XRT 本机 API 支持通过 xrt::ip 实现用户托管式内核控制

- XRT 实用工具

- xbutil 和 xbmgmt 工具现在成为默认工具

- 要使用传统实用工具,请将 xbutil --legacy 或 xbmgmt --legacy 与传统子命令一起使用

- 新的实用工具,xball

- 将 xbutil 或 xbmgmt 命令应用于全部已安装数据中心卡或过滤部分。查看 xball --help 了解详情

- 新命令 xbutil configure

- 允许您启用、禁用或配置 PCIe 主机内存和 PCIe 点对点功能。查看 XRT 文档,了解更多详情

- 所有 XRT 实用工具现在都全局支持 --force 选项,以跳过用户交互确认

- xbutil 和 xbmgmt 工具现在成为默认工具

- 剖析

- 启用任何剖析选项时,将生成配置文件摘要报告。

- 所有适用的汇总表及指南都可基于 xrt.ini 文件中启用的剖析选项生成

- 在设计过程中,监控器添加至内存资源时,会提供用于聚合内存资源信息的新数据传输汇总表

- 全新 AIE 剖析度量设置为计算不同 AIE 事件的数量,包括 (1) AIE 中的浮点异常;(2) 处理单元执行计数;以及 (3) 数据流的输出与获取

- 嵌入式

- zocl 内存管理器的改进可支持任何 sptag

面向 AI 引擎多进程的 Vitis XRT 支持

- C 语言和 C++ API 将定义多个进程的访问模式,以共享对相同 AI 引擎阵列及计算图的访问。

- 保护 AI 引擎阵列和计算图免遭不必要的访问。

- 打开 AI 引擎阵列和计算图支持三种模式

- 独占模式(阻止任何其他进程访问)

- 主模式(只允许其他进程进行非破坏性访问)

- 共享模式(只进行非破坏性访问)

- 考虑何时需要提供多进程支持。例如:

- 阻止其他人访问 AI 引擎阵列(独占访问权限)

- 多个用户分别控制不同的计算图(多应用支持)

- 一个主用户控制计算图,允许其他用户探测运行状态(主用户访问和共享访问)

Vitis XRT 提供 AI 引擎支持状态

C 和 C++ API

- C 版 API

- 对于 AI 引擎阵列:

- xrtAIEDeviceOpenExclusive(独占模式)

- xrtAIEDeviceOpen(主要模式)

- xrtAIEDeviceOpenShared(共享模式)

- 对于 AI 引擎计算图:

- xrtGraphOpenExclusive(独占模式)

- xrtGraphOpen(主要模式)

- xrtGraphOpenShared(共享模式)

- 对于 AI 引擎阵列:

- C++ 版 API

- xrt::aie::device 类支持构造函数中的访问模式

- enum 类 access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2 };

- xrt::graph 类支持构造函数中的访问模式

- enum 类 access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2, none = 3 };

- xrt::aie::device 类支持构造函数中的访问模式

AI 引擎 DSP 库 - 新块

- AIE DDS

- AIE 混频器

并行编译

- 与 2021.1 相比,缩短了时间(例如,以下数字主要针对 200MHz TX 链):

- 编译与仿真时间减少了 3 倍

- 编译时间减少了 7 倍

- 仿真后死区时间从 25s 锐降至大约 0s

约束编辑器增强

- 2021.2 改进了导航

针对固定尺寸的改进

针对可变大小块的改进

增强的功能协同仿真能力

- 为 AI 引擎输入导出 Matlab 数据 – xmcVitisWrite

- 将 AI 引擎数据导入 Matlab – xmcVitisRead

- 将 AI 引擎数据导入 Matlab - xmcVitisRead

其他

- 导入没有输入的 AI 引擎或 HLS 内核模块(来源块)

- 全新数据类型支持

- Simulink 原生 int64 和 uint64 用于 AI 引擎开发,而不是 AMD 数据类型 x_sfix64 和 x_ufix64。

- accfloat 和 caccfloat 支持 AI 引擎开发

- 支持 Ubuntu 20.04

- 支持 MATALB 20a、20b、21a(不支持 MATLAB 21b)

- 增加新示例

- 具有 64 个内核的双流 SSR 滤波器示例

- 伪逆矩阵 (64x32) - commslib 示例。

- 使用 xmcLibraryPath 命令指向自定义 DSPLib 位置。

- 大量更多增强功能和漏洞修复

Vitis 软件平台 2021.1 版本亮点:

- 支持 AMD Kria 系统模块 (SOM) KV260 视觉 AI 入门套件。ML(DPU 推断引擎)+ X(RTL 内核和基于 Vitis HLS 的计算机视觉内核)的完整 Vitis 流程。了解更多 >

- 新增对 FPGA 和/或 Versal ACAP 平台上 C/C++ 视觉、DSP、计算图(Louvain 模块化)、图像处理编解码及压缩(GZIP、Facebook ZSTD、ZLIB 全应用加速)性能优化库的支持(相较于 CPU/GPU 方案)

- Versal ACAP 器件上增强的 Vitis™ Core 开发套件设计流程:AI 引擎设计跟踪报告的可视化改进、通过 GMIO 进行的 AI 引擎事件跟踪、增量重新编译、新增启动映像向导并支持加密的 AI 引擎源文件

- 新的 Vitis Model Composer 工具可在 MathWorks MATALB 和 Simulink® 环境中快速进行设计探索和验证,从而实现针对 AI 引擎和可编程逻辑的块的协同仿真、代码生成和测试激励文件创建。

- 使用全新 Vitis HLS Flow Navigator GUI 快速访问流阶段和报告。将综合、分析及调试视图融合在通用默认环境中

注意:Vitis 加速库可单独下载。它们可以从 GitHub 下载,也可以直接从 Vitis IDE 中下载。

AIE DSP

- DSPLib 作为 Github 上的 Vitis 加速库集的一部分发布

- DSPLib 包含许多高级信号处理应用中使用的通用可参数化 DSP 函数。所有函数目前都支持窗口接口和流接口支持。

FIR 滤波器

功能 |

命名空间 |

单速率、非对称 |

dsplib::fir::sr_asym::fir_sr_asym_graph |

单速率、对称 |

dsplib::fir::sr_sym::fir_sr_sym_graph |

插值非对称 |

dsplib::fir::interpolate_asym::fir_interpolate_asym_graph |

抽取、半带 |

dsplib::fir::decimate_hb::fir_decimate_hb_graph |

插值、半带 |

dsplib::fir::interpolate_hb::fir_interpolate_hb_graph |

抽取、非对称 |

dsplib::fir::decimate_asym::fir_decimate_asym_graph |

插值、分数、非对称 |

dsplib::fir::interpolate_fract_asym:: fir_interpolate_fract_asym_graph |

抽取、对称 |

dsplib::fir::decimate_sym::fir_decimate_sym_graph |

FFT/iFFT - DSPLib 包含一个 FFT/iFFT 解决方案。这是一个支持可配置点数、复数数据类型、级联长度以及 FFT/iFFT 功能的单通道单核时域抽取 (DIT) 实现方案。

功能 |

命名空间 |

单通道 FFT/iFFT |

dsplib::fft::fft_ifft_dit_1ch_graph |

矩阵乘法 (GEMM) - DSPLib 包含一个矩阵乘法/GEMM(一般矩阵乘法)解。这支持 2 个矩阵 A 和 B 的矩阵乘法,可配置的输入数据类型可派生出输出数据类型。

功能 |

命名空间 |

矩阵 Mult / GeMM |

dsplib::blas::matrix_mult::matrix_mult_graph |

小部件实用工具 - 这些小部件不仅支持窗口与数据流之间的转换(在 DSPLib 函数输入端)和需要时数据流与窗口之间的转换(在 DSPLib 函数的输出端),而且还支持用于在真实数据类型和复杂数据类型之间进行转换的其他小部件。

功能 |

命名空间 |

数据流至窗口/窗口至数据流 |

dsplib::widget::api_cast::widget_api_cast_graph |

实数到复数/复数到实数 |

dsplib:widget::real2complex::widget_real2complex_graph |

Vitis Model Composer 支持 DSP 库函数,可帮助用户轻松将这些函数插入 Matlab/Simulink 环境,以方便执行 AI 引擎 DSP 库评估和整体 AI 引擎 ADF 计算图开发。

Vitis HPC 库版本引入了 HLS 原语、预构建内核以及用于 FPGA 上 HPC 应用的软件 API。这些应用包括:

2D 声学逆时偏移 (RTM) 时域有限差分 (FDTD) 算法,包括前向内核和后向内核

3D 声学逆时偏移 (RTM) 时域有限差分 (FDTD) 算法,包括前向内核

多层感知器 (MLP) 组件:激活函数和完全连接的网络内核

稠密矩阵和稀疏矩阵的预条件共轭梯度 (PCG) 求解器

- Versal AI Engine 所选视觉函数的首次发布:

可用功能

Filter2D

absdiff

accumulate

accumulate_weighted

addweighted

blobFromImage

colorconversion

convertscaleabs

erode

gaincontrol

gaussian

laplacian

pixelwise_mul

threshold

zero

xfcvDataMovers:实用工具数据转移,以便轻松平铺高分辨率图像并将其传输至 AI 引擎内核的本地内存。两种类型:

- 使用 PL 内核:以更多 PL 资源为代价,提高吞吐量。

- 使用 GMIO:吞吐量低于 PL 内核版本,但使用 Versal 片上网络 (NOC),不耗 PL 资源。

- 新的可编程逻辑 (PL) 功能和特性

- ISP 流水线和功能:

- 更新了 2020.2 非 HDR 流水线

- 支持在运行时更改少量 ISP 参数:红色和蓝色通道的增益参数,AWB 启用/禁用选项,RGB 伽玛表,用以计算 AWB 标准化最小值和最大值的像素百分比。

- 伽马校正和色彩空间转换 (RGB2YUYV) 是流水线的一部分。

- 新的 2021.1 HDR 流水线:2020.2 流水线 + HDR 支持

- 支持短长曝光帧数字重叠传感器的双曝光 HDR 融合技术。

- 支持四种拜耳模式:RGGB、BGGR、GRBG、GBRB

- HDR 融合 + isp 流水线支持运行时配置,其可返回 RGB 输出。

- 提取功能:HDR 提取功能是预处理功能,其可将单个数字重叠流作为输入,返回 2 个输出曝光帧(SEF、LEF)。

- 支持短长曝光帧数字重叠传感器的双曝光 HDR 融合技术。

- 3DLUT:提供输入输出映射来控制复杂的颜色运算符,如色相、饱和度和亮度。

- CLAHE:对比度限制自适应直方图均衡是一种在执行自适应直方图均衡时限制对比度的方法,不会过度放大近恒定区的对比度。这也减少了噪声放大的问题。

- 更新了 2020.2 非 HDR 流水线

- 翻转:沿水平线和垂直线翻转图像。

- 自定义 CCA:用于水果缺陷检测的自定义版本连接成分分析算法。除了计算水果的缺陷部分外,还可计算水果的缺陷像素和水果的总像素

- Canny 更新:Canny 功能现在支持任何图像分辨率。

库相关更改

- 所有测试都已从使用 OpenCV 3.4.2 升级到 OpenCV 4.4

- 增加了对 Versal Edge 系列 (VCK190) 的支持

- 全新基准测试部分,可为发布的选定流水线/功能提供基准测试辅助组件。

2021.1 版提供了二元语法文本分析:

两克谓词 (TGP) 是搜索具有两个字符的反索引。对于建立了反向索引的数据集,它可以在反向索引的每条记录中找到匹配的 ID。

- 社区检测:Louvain 模块化

- 2 跳搜索

不适用

- 新增基于 L2 内核的双精度稀疏矩阵稠密向量乘法 (SpMV) 实现

在 2021.1 版中,GQE 获得了以下特性抢先体验支持

64 位连接支持:现在 gqeJoin 内核及其配套 gqePart 内核已扩展至 64 位密钥及有效负载,可支持更大规模的数据。

支持最初的布隆过滤器:gqeJoin 内核现在提供一种执行布隆过滤器探测的模式。这可提高某些多节点流程的效率,在这些流程中,一定要在早期阶段更大限度减少数据量,这一点非常重要。

这两个特性现在均可作为 L3 纯软件 API 提供,请查看相应的 L3 测试案例。

- GZIP 多核压缩:

- 全新 GZIP 多核压缩流媒体加速器,这是纯数据流专用解决方案(自由运行内核),支持 4KB、8KB、16KB 和 32KB 的大量不同块。

- Facebook ZSTD 压缩核心:

- 新的 Facebook ZSTD 单核压缩加速器,块大小为 32KB。多核 ZSTD 压缩正在进行中(以提高吞吐量)。

- GZIP 低延迟解压缩:

- 新版的 GZIP 解压,降低了每个块的时延,降低了资源(LUT 降低 35%、BRAM 降低 83%)并提高了 FMax。

- ZLIB 使用 U50 的整体应用加速:

- 针对 U50 平台的 L3 GZIP 解决方案,包含 6 个压缩内核,以饱和整个 PCIe 带宽。它附带高效的 GZIP SW 解决方案,为加速 CPU libz.so 库提供加速,针对最终客户软件提供无缝收放 API 级集成,而无需重新编译。

- Versal 平台支持。

- 添加 AIE 支持 - 如上

- 2021.1 版本支持:* RIPEMD160 * 对 BLS 的初始支持(未完成)

- 在 2021.1 版本中,将数据移动器添加至该库。与基于 C++ 的其他 API 不同,这一新增组件主要针对那些在基于 HLS 的内核设计方面缺乏经验、只想测试其基于流媒体的设计的设计人员。数据移动器实际上是一个内核源代码生成器,可创建一系列通用助手内核来驱动或验证设计,跟 AIE 器件上的一样。

- 生成 QoR 指标(Vitis QoR 生成 API)

- 应用内核占用的周期

- 失速周期(从 VCD 文件计算)

- 测量包装器中的开销周期(花在内核之外其他函数上的时间)

- 吞吐量

- 3 个层次的优化 XLOPT=0、1(默认)、2

- xlopt=2 的新功能:

- 循环融合、平展单迭代外部循环、增强循环剥离启发式

- 分析“__restrict”用法并提供指导

- 增量重新编译:计算图没有改变时,只重新编译已经修改过的内核

- 分组交换数据 → 多达 32 个分组(限 4 个)

- 全新 DMA FIFO 位置约束(映射器/路由器在不同版本之间的改变不会影响性能)

- 在新的编译中将映射解决方案用作约束:防止将来的映射变化,其可影响性能

- 将 x86sim 功能支持提升到 aiesim 级别

- 开始在 ADF 图中淘汰 PL 内核(2021.2 中已完全淘汰)

- 图形用户界面中新增的“Flow Navigator”,可快速访问流阶段和报告。 上下文“合成、分析、调试”视图合并到一般默认上下文中

- 为 BIND_OP 和 BIND_STORAGE 指令新增了一个综合报告部分

- 全新的综合后文本报告将反映图形用户界面综合报告中提供的信息

- IP 导出和 Vivado 实现运行小部件使用各种选项进行重新设计,可将设置和约束文件传递给 Vivado

- 全新函数调用图查看器,可直观呈现函数和环路,其可使用可选热图高亮显示,以检查 II、时延或 DSP/BRAM 利用率热点

- Versal 时序校准以及 DSP 块原生浮点运算的全新控制(config_op 的 -precision 选项)

- Vitis HLS 迁移指南(之前的 UG1391)现在是 UG1399 的一个章节

- 用户指南中新增方法部分(UG1399 和网络)

- 备用可冲洗流水线选项已得到改进(自由运行流水线,又称“frp”)

- 在 Vitis 中,顶层端口指针现在可以只映射至 axis -lite 适配器,而不是全局内存

- 聚合指令现在提供了一个“-compact bit”选项来实现极大包装

- 在“帮助”菜单中添加一个“留下反馈意见”条目,其中包含可选调查

- 修复了“帮助页”选项卡在某些 Linux 系统上不显示信息的漏洞

- 在 Vitis 中,重塑 m_axi 接口应该通过 hls::vector 类型完成

- s_axilite 和 m_axi 数据存储的新自定义选项可以是“auto”、“uram”、“bram”或“lutram”,允许您在设计中调整 RAM 利用率

- 在 Vitis 中,为内核引入了一种全新的连续(又称“永不停止”)运行模式

- 已恢复 axi_lite 辅助时钟选项

- 增强对 Vivado IP 封装器中 RTL 内核封装的支持

- 经过完善方法论验证并配备标准化文档的公开产品级功能。

XRT 管理内核是默认流程。

支持加密的 AIE 源文件作为输入

AIE 编译器可以接受加密的 AIE 源文件,v++ 支持其余流程。

- 为 Versal 器件添加“创建启动映像向导”支持

- AI 引擎编程和调试的多项改进

- 能够开启和关闭微代码标签

- 源代码和微代码之间的静态交叉探测

- 微码全视图

- 当流水线视窗更新数据时,将最后一台 PC 带入能够看见的区域

- 在流水线视图中调整指令数据

- 将“单指令模式”操作添加到反汇编视图。

- 能够为平台项目生成默认的 BIF 文件

- SD 和 eMMC 的程序闪存增加了原始模式支持

- 上下文关联的帮助消息添加到 AI 引擎开发流程中

- 将 GCC 工具链版本升级至 10.2

- 用户可通过外部进程(如 Python / C++)来仿真 AXI-MM 的主/从设备。这可帮助用户快速模拟 AXI 主/从设备设计,无需投入资源开发 AXI 主设备或 VIP。AXI-MM 进程间通信还有助于模拟两个 FPGA 之间的芯片到芯片连接。

- 为 VCS 启用 Versal 模型的编译。

- 平台开发者可使用独立应用在平台上运行硬件仿真,以便在早期阶段对平台进行测试。

- 用户覆盖范围分析信息和用户事件信息聚合在配置文件摘要报告中

Vitis 分析器显示了一个关键的时序路径。

Vitis 分析器将显示 Vivado GUI 时序报告的简化版本,无需打开 Vivado 项目或网表。这使用户可以快速导航到故障实现路径。

Vitis 分析器支持多种策略

多种策略运行的结果可以在 Vitis 分析器中查看。

- 最新 xrt.ini 开关用于分析与调试

减少大型应用的内存和加载时间

全新性能分析工具使用更少的资源来处理大型 csv 文件,这可减少加载时间以及崩溃问题的发生。

改进了 PL 连续跟踪分载

使用 DDR 或 HBM 作为内存资源来存储跟踪数据

循环缓冲区支持大型数据分载

跟踪缓冲区大小和分载间隔可以在 xrt.ini 中设置

改进了 AIE 设计跟踪报告的可视化

将显示所有 AIE 输入(窗口、数据流和级联数据流等)

支持所有 IO 数据类型

- 稳定的本地 XRT API,不仅可为 AIE 图形的控制和执行提供 C++ API,而且还支持软件仿真与跟踪。

- XRT 提供全新助手 API,可帮助用户在 $XILINX_XRT/include/CL/cl2xrt.hpp 中将 OpenCL API 升级至 XRT 原生 API。

- XRT 全新 API xrt::device.get_info() 可提取器件属性

- 显著改进的新一代 xbutil 和 xbmgmt 实用工具现在是默认的。

- xbutil 可报告电源状态

- xbmgmt 不仅可支持运行时 clk 扩展,而且还可设置用户电源阈值,从而可保护电路板和服务器。

- sysfs、xbmgmt 和 xbutil 可报告 Alveo 电路板的 MAC 地址

- xocl 中的 KDS 调度器已经进行重构,显著提高了数百个进程(同时在多个器件间执行多个计算单元)的吞吐量。对于原有 shell 而言,您可能会注意到吞吐量下降的百分比很小。请参阅 AR 以获得正确的解决方案。

- 通过 debugfs /sys/kernel/debug/xclmgmt/ and /sys/kernel/debug/xocl/ 支持 XRT 驱动程序调试跟踪

请访问 www.xilinx.com/alveo 获取适用于 Alveo 加速器卡的最新 Vitis 目标平台。请参阅要在其上部署应用的加速器卡的入门 部分。

请参阅 UG1120 - Alveo 数据中心加速器卡平台用户指南,了解更多详细信息,并随时了解最新的 Vitis 目标平台版本。

全新平台

- Alveo U200 Gen3x16 XDMA 1RP

- 名称:xilinx_u200_gen3x16_xdma_1_202110_1

- 游戏特点: Slave Bridge、P2P、GT 内核、DDR 自动刷新

- Alveo U50 Gen3x16 noDMA 1RP

- 名称:xilinx_u50_gen3x16_nodma_1_202110_1

- 游戏特点: Slave Bridge、P2P、GT内核、时钟降频

Vitis 嵌入式平台

- VCK190 基础平台支持 DDR 和 LPDDR 上的 ECC;约束变得很简洁。

- MPSoC 基础平台将 CMA 量增加到了 1536M。所有 Vitis-AI 模型都可按这个 CMA 量运行。

- 简化了嵌入式平台创建流程:设备树生成器可以自动生成 ZOCL 节点;XSCT 可以生成 BIF 文件。减少了基础平台源文件。

- 支持 Kubernetes(K8s) 群集:Xilinx FPGA Resource Manager (XRM) 现在可以与 Kubernetes 一起使用,在连接到服务器的多个 Alveo 加速器卡池中运行和管理计算单元 (CU),并将应用扩展到采用 Alveo 卡的多个服务器。

- 全面的约束编辑器可帮助用户在 Vitis Model Composer 中为 AI 引擎内核指定任何约束。生成的 ADF 计算图将包含这些约束。

- 将 AI 引擎的 FFT 和 IFFT 块添加至库浏览器。

- 用户现在可以使用库浏览器访问大量 AI 引擎 FIR 块变体。

- 能够使用 FIR 滤波器的输入端口指定滤波器系数。

- 增加了两个新的实用工具块“RTP Source”和“To Variable Size”。

- 增强的 AIE 内核导入块现在也支持导入模板化的 AI 引擎功能。

- 能够在 Hub 块中为 AI 引擎设计指定 AMD 平台。

- 用户可通过 Hub 块,在运行 AIE 仿真后随时重启 Vitis 分析器。

- 用户现在可以使用 Simulink 数据检查器绘制周期近似输出,并查看每个输出的估计吞吐量。

- 增强了仅使用计算图头文件将计算图作为块导入的可用性。

- 进度条功能升级,新增取消按钮

- 针对 MATLAB 工作目录与模型目录不一致场景下的 AI 引擎内核导入或设计仿真功能可用性优化。

- 新增 TX 链 200MHz 示例。

- 新增二维 FFT 示例,展示 HLS、HDL及 AI 引擎块的设计。

HDL

- 针对 SSR FIR(改进超过 10 倍)和 SSR FFT 提高了仿真速度。

- 针对 RAM 等内存模块和 FIFO 提高了仿真速度

- 在黑盒导入流程中使用 VHDL 2008 更新了 Questa 仿真器

基本信息

- Vitis Model Composer 现在包含 AMD System Generator for DSP 的功能。 一直使用 AMD System Generator for DSP 的用户可以继续使用 Vitis Model Composer 进行开发。

- MATLAB 支持 - R2020a、R2020b 和 R2021a

Vitis 软件平台 2020.2 版本亮点:

- Vitis 2020.2 支持 Versal ACAP 平台的应用加速与嵌入式软件开发

- Vitis Core 开发套件现在包含 AI 引擎编译器,支持为 Versal AI Engine 编译 C/C++ 应用。AI 引擎是 Versal AI Core 系列的一部分,是计算密集型应用的矢量处理器

- 对于加速内核编译 (Vitis) 和 C/C++ 至 RTL IP 创建流程 (Vivado),默认使用 Vitis HLS

- 提供 600 多个 FPGA 加速功能,遍布 13 大类性能优化库。2020.2 版引入全新 Vitis HPC 库用于加速高性能计算类应用,以及多项增强或补充功能强化数据分析、计算图、BLAS、稀疏矩阵库、安全库和数据库

- 为评估多种实现策略提供支持,充分满足最终 FPGA 二进制的生成,进一步简化 Vitis 应用中 RTL 内核的集成

- 此版本的其他增强功能包括对 AI 引擎应用剖析的支持,对 Vitis 项目的 Git 版本控制,Vitis AI 分析器中的数据集成以及对仿真模式的增强。

- MATLAB® 和 Simulink® 插件:AMD Model Composer 和 System Generator for DSP 融为一体。AI 引擎现已成为 MATLAB 和 Simulink 插件的新功能域。

附注

- 根据 2023 年 8 月 10 日的测试结果,对比 Vitis HLS 2023.2 和 Vitis HLS 2023.1,在 1000 个 Vitis L2/L3 代码库设计上测试。测试期间的系统配置:Intel Xeon E5-2690 v4 @ 2.6GHz CPU,256GB RAM,RedHat Enterprise Linux 8.6.实际性能会有所不同。系统制造商可能会采用不同的配置,因而得到不同的结果。-VGL-04

- 截至 2023 年 2 月 12 日,在所有 1208 个 Vitis L1 库 C 代码设计上完成基准测试。所有设计都使用一个配备 2P Intel Xeon E5-2690 CPU 的系统运行,系统装有 CentOS Linux,启用 SMT 并禁用了 Turbo Boost。预计硬件配置不会影响软件测试结果。结果可能会因软件及固件设置和配置而异 - VGL-03

- 根据 2023 年 8 月 10 日的测试结果,对比 Vitis HLS 2023.2 和 Vitis HLS 2023.1,在 1000 个 Vitis L2/L3 代码库设计上测试。测试期间的系统配置:Intel Xeon E5-2690 v4 @ 2.6GHz CPU,256GB RAM,RedHat Enterprise Linux 8.6.实际性能会有所不同。系统制造商可能会采用不同的配置,因而得到不同的结果。-VGL-04

- 截至 2023 年 2 月 12 日,在所有 1208 个 Vitis L1 库 C 代码设计上完成基准测试。所有设计都使用一个配备 2P Intel Xeon E5-2690 CPU 的系统运行,系统装有 CentOS Linux,启用 SMT 并禁用了 Turbo Boost。预计硬件配置不会影响软件测试结果。结果可能会因软件及固件设置和配置而异 - VGL-03