- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

- 2020.2

- 2020.1

Highlights des Release 2025.2 der AMD Vitis™ Softwareplattform

Verbesserter Design-Flow mit Versal™ AI Engines

- Erweiterungen der KI-Engine-API für Versal AI Edge und Versal AI Edge-Serie der 2. Generation (AIE-ML und AIE-ML v2)

- Neue und erweiterte Datentypen

- Neu: Gleitkomma-Block MX6

- Neu: Gleitkomma-Block MX4

- Neu: cbfloat16 (emuliert)

- Erweitert: cfloat und cbfloat16 (verfügbar in FFT- und Matrixmultiplikation-Funktionen)

- Erweitert: cint16 und cint32 (kann nun Typen zur cint16-Manipulation in FFTs verwenden)

- Neue und erweiterte Datentypen

- Updates des Programmierungsmodells

- Erstellen eines schreibgeschützten gemeinsamen Puffers

- Wiederholter Lesezugriff auf MEM-Kacheln (AIE-ML und AIE-ML v2)

- DMA-FIFO-Unterstützung in AIE-ML und AIE-ML v2

- Ping-Pong-Puffer können sich über zwei benachbarte MEM-Kacheln erstrecken

(AIE-ML und AIE-ML v2) - Gemeinsame Parameter für lokalen Kachelspeicher

- Erweiterungen bei Paketvermittlung für AIE-ML und AIE-ML v2

- Neue und erweiterte DSP-Bibliotheksfunktionen für alle Versal AI Engines

- Neue kumulative Summe

- Neue euklidische Distanz

- Neue Funktionsangleichung (aufgerufen über RTP-Aktualisierung oder LUT)

- Erweiterte TDM-FIR mit Paketvermittlung (spart PLIOs)

- Erweiterte 1D-FFT unter Verwendung von KI-Engine + PL (reduziert erforderliche PL-Ressourcen)

- Erweiterte FIR (Durchsatzoptimierungen)

- Verbesserte KI-Engine-Mapper und -Router – Compiler kann verschiedene Platzbedarfe/Layouts für eine effizientere Implementierung untersuchen

Einfachere Verifizierung von Versal AI Engine Konzepten

- Workflow-Updates für Vitis Functional Simulation mit Unterstützung für C++ (Early Access)

- Hardware-in-the-Loop mit MATLAB® Python Testbench (Early Access)

Verbesserungen an Vitis Model Composer für AIE DSP-Designs

- Benutzerfreundliche Updates für den Super Sample Rate (SSR)-Design-Flow mit KI-Engines (Early Access)

- Zusätzliche Blöcke für KI-Engine und HDL verfügbar:

- AIE, AIE-ML, AIE-ML v2

- Neu: Funktionsangleichung

- Neu: Korrelation/Faltung

- Neu: Kumulative Summe

- HDL-Bibliotheksblöcke

- Erweitert: FFT (native Gleitkomma-SSR = 32, 64 hinzugefügt)

- Erweitert: FIR (Unterstützung von Fractional-Rate-Interpolation mit SSR)

- AIE, AIE-ML, AIE-ML v2

Updates für Vitis IDE für die integrierte Entwicklung

- Python™ API zur Aktualisierung beim Aufbauen der Konfiguration

- Ausführung von Vitis™ API in Python-Umgebung

- PS Trace standardmäßig sichtbar für unterstützte Kerne

- Verbessertes Debugging – aktualisierte Werte werden jetzt in der Ansicht „Watch“ und „Register“ hervorgehoben

- Abbrechen oder Beenden von Backend-Aufgaben

- Unified Platform BSP-Dateipfade (Linux und Windows)

- Theia AI Integration (Early Access) – stellt Infrastruktur für Entwickler bereit, damit sie das LLM und die Code-Assistenten verwenden können, die sie bevorzugen

- DFX-Plattformerstellung mit Python-API

- Sichern der Daten oder Freigeben eines Arbeitsbereichs

- Erweiterte Protokollierung für Konfigurationsdateien

- Neue Komponente „Integrationsprojekt“

Neues bei Vitis nach Kategorie

Erweitern Sie die folgenden Abschnitte, um mehr über die neuen Funktionen und Verbesserungen in Release 2025.2 der AMD Vitis Softwareplattform zu erfahren. Informationen zu unterstützten Plattformen, verändertem Verhalten und bekannten Problemen finden Sie in den Versionshinweisen zu Release 2025.1 der Vitis Softwareplattform für den Flow zur Anwendungsbeschleunigung und den Flow für die Entwicklung von integrierter Software.

Erweiterte DSP-Bibliotheksfunktionen:

- Neue kumulative Summe

- Neue euklidische Distanz

- Neue Funktionsangleichung (aufgerufen über RTP-Aktualisierung oder LUT)

- Erweiterte TDM-FIR mit Paketvermittlung (spart PLIOs)

- Erweiterte 1D-FFT unter Verwendung von AIE + PL (reduziert erforderliche PL-Ressourcen)

- Erweiterte FIR (Durchsatzoptimierungen)

Gilt für:

- Versal™ AI Core mit AIE

- Versal AI Edge mit AIE-ML

- Versal AI Edge-Serie der 2. Generation mit AIE-ML v2:

- Funktionssimulation von Vitis Subsystemen in C++ (Early Access)

- Verbesserte Unterstützung für Latenz- und Durchsatzmessungen in Vitis Analyzer – für KI-Engine-Konzepte

- Laufzeitsteuerung unabhängiger AIE-Partitionen

- Benutzerfreundliche Updates für den Super Sample Rate (SSR)-Design-Flow mit KI-Engines (Early Access)

- Zusätzliche Blöcke für KI-Engine und HDL verfügbar:

- AIE, AIE-ML, AIE-ML v2

- Neu: Funktionsangleichung

- Neu: Korrelation/Faltung

- Neu: Kumulative Summe

- HDL-Bibliotheksblöcke

- Erweitert: FFT (native Gleitkomma-SSR = 32, 64 hinzugefügt)

- Erweitert: FIR (Unterstützung von Fractional-Rate-Interpolation mit SSR)

- Erweiterungen von Performance-Pragma

- Performance-Pragma wird nun basierend auf dem von CSIM berechneten Trip-Count optimiert

- Performance-Pragma-Optimierungen können in Anweisungen in einer Konfigurationsdatei umgewandelt werden

- Bedingte Pragmen-Steuerung, einschließlich Performance-Pragma

- Unterstützung neuer IP

- Fractional-Rate-SSR für FIR und FFT – für FFT bietet SSR in SPFP32 jetzt Unterstützung bis zu SSR=64.

- ECC-Unterstützung für Datenflusspuffer, implementiert mit Block RAM oder UltraRAM

- Benutzerfreundliche Funktionen

- Unterstützung für automatischen Neustart in CSIM und CoSim

- Multi-Port-Cache für M-AXI

- Neue APIs für AXI-Streams mit Seitenbandsignalen

Highlights des Release 2025.1 der AMD Vitis™ Softwareplattform

Verbesserter Konzept-Flow mit Versal AI Engines

- Neue und erweiterte DSP-Bibliotheksfunktionen, KI-Engine-APIs und Unterstützung für neue Datentypen

Versal AI Core-Serie mit AIE:

- Verbessertes GEMV & FFT für KI-Engine mit paralleler 2D-AIE- und PL-Architektur (geeignet für Polyphase Channelizer)

- Vektorisierte bitonische SIMD-Sortierung, -Korrelation, -Convolution

Versal AI Edge-Serie mit AIE-ML:

- FFT für AIE-ML mit paralleler 2D-AIE-ML- und PL-Architektur (geeignet für Polyphase Channelizer)

- Vektorisierte bitonische SIMD-Sortierung, -Korrelation, -Convolution

Versal AI Edge-Serie der 2. Generation mit AIE-ML v2:

- 2D FFT AIE-ML v2 und PL v1 (geeignet für Polyphase Channelizer)

- TDM FIR (geeignet für Polyphase Channelizer)

- GEMM/GEMV

- Einzelraten-FIR

- Halbband-FIR

- Fractional-Resampler-FIR

- Ratenänderungs-FIR

- FFT/iFFT

- DFT

- DDS-Mixer

- Funktionsangleichung

KI-Engine-Programmierungs-Updates:

- Spezifikationen für Tiling-Parameter für lokalen Speicher

- Kürzere Kompilierungszeiten beim Testbench-Wechsel

- Schnelleres Pipelining für das Konzept mit Ping-Pong-Puffern in DDR in AIE-ML

- Weitere Verbesserungen des Speicherzugriffs in AIE-ML

Einfachere Verifizierung von Versal AI Engine Konzepten

- Funktionssimulation von Vitis Subsystemen in MATLAB® und Python™

- Verbesserte Unterstützung für Latenz- und Durchsatzmessungen in Vitis Analyzer – für KI-Engine-Konzepte

- Laufzeitsteuerung unabhängiger AIE-Partitionen

Verbesserungen an Vitis Model Composer für AIE DSP-Designs

- Unterstützung für mehrere KI-Engine-Subsysteme auf oberster Ebene

- Zusätzliche Blöcke für AIE und HDL verfügbar, einschließlich erweitertem FFT mit zusätzlichen SSR-Modi und Complex Multipliers, die weniger DSP58-Ressourcen benötigen

Updates für Vitis IDE für die integrierte Entwicklung

- Vitis Unified IDE (neue GUI) ist die Standardeinstellung – Classic Vitis IDE ist veraltet

- Unterstützung von Werkzeugketten von Drittanbietern wie GCC und ARMClang

- Produktivitätstools von Drittanbietern können jetzt über ein Marktplatz-Dienstprogramm in Vitis IDE installiert und aufgerufen werden

Neues bei Vitis nach Kategorie

Erweitern Sie die folgenden Abschnitte, um mehr über die neuen Funktionen und Verbesserungen in Release 2025.1 der AMD Vitis Softwareplattform zu erfahren. Informationen zu unterstützten Plattformen, verändertem Verhalten und bekannten Problemen finden Sie in den Versionshinweisen zu Release 2025.1 der Vitis Softwareplattform für den Flow zur Anwendungsbeschleunigung und den Flow für die Entwicklung von integrierter Software.

Versal AI Core-Serie mit AIE:

- Verbessertes GEMV & FFT für KI-Engine mit paralleler 2D-AIE- und PL-Architektur (geeignet für Polyphase Channelizer)

- Vektorisierte bitonische SIMD-Sortierung, -Korrelation, -Convolution

Versal AI Edge-Serie mit AIE-ML:

- FFT für AIE-ML mit paralleler 2D-AIE-ML- und PL-Architektur (geeignet für Polyphase Channelizer)

- Vektorisierte bitonische SIMD-Sortierung, -Korrelation, -Convolution

Versal AI Edge-Serie der 2. Generation mit AIE-ML v2:

- 2D FFT AIE-ML v2 und PL v1 (geeignet für Polyphase Channelizer)

- TDM FIR (geeignet für Polyphase Channelizer)

- GEMM/GEMV

- Einzelraten-FIR

- Halbband-FIR

- Fractional-Resampler-FIR

- Ratenänderungs-FIR

- FFT/iFFT

- DFT

- DDS-Mixer

- Funktionsangleichung

- Funktionssimulation von Vitis Subsystemen in MATLAB® und Python™

- Verbesserte Unterstützung für Latenz- und Durchsatzmessungen in Vitis Analyzer – für KI-Engine-Konzepte

- Laufzeitsteuerung unabhängiger AIE-Partitionen

Unterstützung für mehrere KI-Engine-Subsysteme auf oberster Ebene

Zusätzliche Blöcke für KI-Engine und HDL verfügbar

KI-Engine

- Bitonic-Sortierung (Versal AI Core-Serie, Versal AI Edge-Serie, Versal AI Edge-Serie der 2. Generation)

- DFT/FFT (Versal AI Edge-Serie der 2. Generation)

- FIR – Einzelrate, Halbband, Ratenänderung, Fractional-Resampler (Versal AI Edge-Serie der 2. Generation)

- DDS/Mixer (Versal AI Edge-Serie der 2. Generation)

HDL-Bibliothek

- Verbessertes FFT – zusätzliche SSR-Modi

- SSR 8, 16, 32, 64 (natives Gleitkomma)

- SSR 2, 4 (Festkomma)

- Verbesserter Complex Multiplier – weniger DSP58-Ressourcen

- Neue Unterstützung für CFLOAT MAC

- Vector IFFT Float – neuer Block

- Generieren von Vitis HLS-freundlichem C++-Code aus MATLAB (.m)-Konzepten in R2025a

- Neue benutzerfreundliche Funktionen von Vitis HLS

- Modellierung von kabelgebundenen Eingängen und AXI Lite-Eingängen, die sich während der Ausführung ändern (Direct I/O)

- Performance-Pragma für das HLS-Konzept auf oberster Ebene (offener EA)

- Unterstützung des Versal Complex Multipliers über die dedizierte intrinsische Bibliothek

- Verbesserungen der Vitis HLS-GUI

- Anfängliche C++17-Unterstützung über Clang 16

Highlights des Release 2024.2 der AMD Vitis™ Softwareplattform:

Erweiterungen für DSP-Designs der AMD Versal AI Engine

- Latenz- und Durchsatzschätzungen mit Vitis Analyzer

- Markierung nicht verfügbarer PLIOs mit Vitis Analyzer

- Rasche Prototypenerstellung der AMD Versal™ AI Engine-Konzepte

- Heap-Stack- und Programmspeicherberichte

Neue und erweiterte Vitis Bibliotheksfunktionen für alle Versal AI Engines

- Erweiterte DSP-Bibliotheksfunktionen für AIE (verfügbar auf Versal AI Core, Versal Premium-Serie)

- Performance-Verbesserungen der TDM (Time Division Multiplex)-FIR-Filterfunktionen

- Versionen mit höherer Performance von

- General Matrix Vector (GEMV)

- General Matrix Multiply (GEMM)

- 2D-IFFT – partitioniert über AIE + PL für hohe Performance

- Neue DSP-Bibliotheksfunktionen für AIE-ML(verfügbar auf Versal AI Edge)

- Performance-Verbesserungen der TDM-FIR-Filterfunktionen

- Unterstützung für Radix-3/Radix-5 FFTs

- GEMV

- GEMM

Neue benutzerfreundliche Funktionen in der Vitis IDE (neue GUI)

- Neuer serieller Terminal: Überwachung serieller Nachrichten von der Hardware

- Installieren und Erkunden der Erweiterungen von Drittanbietern

- PS Trace-Funktion zum Debuggen und Optimieren der Performance integrierter Systeme

Verbesserungen an Vitis Model Composer für AIE DSP-Designs

- Aktualisierungen der KI-Engine-DSP-Bibliothek

- AIE (verfügbar für Versal AI Core, Versal Premium-Serie)

- FFT mit gemischter Radix

- Stockham FFT Performance-Verbesserungen

- TDM-FIR

- AIE-ML (verfügbar für Versal AI Edge-Serie)

- TDM-FIR

- DDS (Direct Digital Synthesis) – zur Erzeugung von Wellenformen)

- Mixer (für Frequenzverschiebung)

- AIE-MLv2 (verfügbar für Versal AI Edge-Serie der 2. Generation)

- FIR

- DFT

- DDS

- Mixer

- AIE (verfügbar für Versal AI Core, Versal Premium-Serie)

- Zusätzliche Datentypen für Vitis Model Composer

- Unterstützung für cbfloat16

- Unterstützung zusätzlicher Datentypen für kaskadierte Signale

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- Export von AIE/HLS-Kernel-Konzepten aus Vitis Model Composer als Vitis Subsystem (VSS)

- Debugging von AIE/HLS-Kernels, die in Vitis Model Composer mit Vitis Debugger integriert sind

- Aktualisierungen des HDL-Blocksets in Vitis Model Composer

- Weitere Verbesserungen in Vitis Model Composer

- Verbesserte Reaktionszeit für Codegenerierung

- Simulation wird pro Konzept nur einmal ausgeführt

- Speicherung von Hub-Blockkonfigurationen als JSON-Datei (nützlich für rasche Prototypenerstellung oder Batch-Verarbeitung)

- Unterstützung für MATLAB R2024a hinzugefügt

- Unterstützung für Red Hat Enterprise Linux (RHEL) 8.10, 9.4 hinzugefügt

- Verbesserte Reaktionszeit für Codegenerierung

- Entwurfsregelprüfungen (Design Rule Checks, DRC) zum Ersetzen von Designüberlegungen

Neues bei Vitis nach Kategorie

Erweitern Sie die folgenden Abschnitte, um mehr über die neuen Funktionen und Verbesserungen in Release 2024.2 der AMD Vitis Softwareplattform zu erfahren. Informationen zu unterstützten Plattformen, verändertem Verhalten und bekannten Problemen finden Sie in den Versionshinweisen zu Release 2024.2 der Vitis Softwareplattform für den Flow zur Anwendungsbeschleunigung und den Flow für die Entwicklung von Embedded Software.

Erweiterte DSP-Bibliotheksfunktionen für AIE (verfügbar auf Versal AI Core, Versal Premium-Serie)

- Performance-Verbesserungen der TDM (Time Division Multiplex)-FIR-Filterfunktionen

- Versionen mit höherer Performance von

- GEMV (General Matrix Vector)

- GEMM (General Matrix Multiply)

- 2D-IFFT – partitioniert über AIE + PL für hohe Performance

Neue DSP-Bibliotheksfunktionen für AIE-ML(verfügbar auf Versal AI Edge)

- Performance-Verbesserungen der TDM (Time Division Multiplex)-FIR-Filterfunktionen

- Unterstützung für Radix-3/Radix-5 FFTs

- GEMV (General Matrix Vector)

- GEMM (General Matrix Multiply)

- Latenz- und Durchsatzschätzung mit Vitis Analyzer

- Kennzeichnung über Vitis Analyzer, welche PLIOs nicht verfügbar sind

- Aktualisierungen der KI-Engine-DSP-Bibliothek

- AIE (verfügbar für Versal AI Core, Versal Premium-Serie)

- FFT mit gemischter Radix

- Stockham FFT Performance-Verbesserungen

- TDM-FIR

- AIE-ML (verfügbar für Versal AI Edge-Serie)

- TDM-FIR

- DDS (Direct Digital Synthesis – zur Erzeugung von Wellenformen)

- Mixer (für Frequenzverschiebung)

- AIE-MLv2(verfügbar für Versal AI Edge-Serie der 2. Generation)

- FIR

- DFT

- DDS

- Mixer

- AIE (verfügbar für Versal AI Core, Versal Premium-Serie)

- Zusätzliche Datentypen für Vitis Model Composer

- Unterstützung für cbfloat16

- Unterstützung zusätzlicher Datentypen für kaskadierte Signale

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- Export von AIE/HLS-Kernel-Konzepten aus Vitis Model Composer als VSS (Vitis Subsystem)

- Debugging von AIE/HLS-Kernels, die in Vitis Model Composer mit Vitis Debugger integriert sind

- Aktualisierungen des HDL-Blocksets in Vitis Model Composer

- Weitere Verbesserungen in Vitis Model Composer

- Verbesserte Reaktionszeit für Codegenerierung

- Simulation wird pro Konzept nur einmal ausgeführt

- Speicherung von Hub-Blockkonfigurationen als JSON-Datei (nützlich für rasche Prototypenerstellung oder Batch-Verarbeitung)

- Unterstützung für MATLAB R2024a hinzugefügt

- Unterstützung für Red Hat Enterprise Linux (RHEL) 8.10, 9.4 hinzugefügt

- Entwurfsregelprüfungen (Design Rule Checks, DRC) zum Ersetzen von Designüberlegungen

- Modellierung skalarer/kabelgebundener Eingänge, die sich während der Ausführung ändern (Direct I/O)

- Unterstützung für Gleitkomma-Datentypen für Langzahlarithmetik

- Zuordnung von HLS-Code zu DSP-Blöcken

- Benutzerdefinierte Sequenz der Codeausführung

- HLS-Debugger, der Datentypen benutzerfreundlich anzeigt (mit der PrettyPrint-Technologie des GNU-Debuggers)

Highlights des Release 2024.1 der AMD Vitis™ Softwareplattform:

Erweiterungen für DSP-Konzepte der AMD Versal™ AI Engine

- Erweiterte DSP-Bibliotheksfunktionen für AMD Versal AI Core-Serie

- TDM-FIR-Filterfunktionen für SSR > 1

- FFT mit 32-Bit-Manipulation

- Gemischte Radix-3- und Radix-5-FFTs

- Kronecker-Matrix-Produkt

- Householder-basierter QRD-Solver zur Verbesserung der Stabilität

- DFT für SSR > 1

- Neue DSP-Bibliotheksfunktionen für AMD Versal AI Edge-Serie mit AIE-ML

- General Matrix Vector (GEMV) mit SSR-Unterstützung

- General Matrix Multiply (GEMM) mit SSR-Unterstützung

- AIE-API-Erweiterungen

- Unterstützung für Radix-3-/Radix-5-FFTs

- AIE-Simulatorerweiterungen

- Simulationsfunktionen mit Cycle-Approximate-Methode für KI-Engine-Konzepte mit PL ohne erforderlichen CIPS-IP-Kern (Control, Interfaces, and Processing System – Steuerungs-, Schnittstellen- und Verarbeitungssystem)

- Unterstützung von AMD Vitis Analyzer für Hardware-Emulation mit Simulatoren von Drittanbietern wie VCS, Questa, Xcelium und Riviera

Wichtige Verbesserungen an Vitis Unified Software Platform

- Unterstützung für neue Chips: Adaptives AMD Versal™ Premium VP1902 SoC, AMD MicroBlaze™ V Prozessor

- Verbesserte Entwicklung integrierter Anwendungen und BSP-Generierung für Windows®-Umgebung

- Vom Benutzer verwalteter Flow zum Debuggen integrierter Anwendungen, die extern kompiliert wurden

- Neue Bootgen-GUI

- Inkrementelle Builds für Plattformprojekt

Wichtige Verbesserungen für AMD Vitis IDE (neue GUI)

- Unterstützung für hierarchisches Debugging des Verarbeitungssubsystems hinzugefügt

- Unterstützung für Export und Import von Projekten/Arbeitsbereich hinzugefügt

- Unterstützung für Python-Interpreter und API hinzugefügt

- Neue Vorschauseite für Funktionen

- Benachrichtigung über Dateiänderungen für Embedded-, AIE- und Plattformprojekte

Neues bei Vitis nach Kategorie

Erweitern Sie die folgenden Abschnitte, um mehr über die neuen Funktionen und Verbesserungen in Release 2024.1 der AMD Vitis Softwareplattform zu erfahren. Informationen zu unterstützten Plattformen, verändertem Verhalten und bekannten Problemen finden Sie in den Versionshinweisen zu Release 2024.1 der Vitis Softwareplattform für den Flow zur Anwendungsbeschleunigung und den Flow für die Entwicklung von Embedded Software.

Erweiterte DSP-Bibliotheksfunktionen für AMD Versal AI Core-Serie

- TDM-FIR-Filterfunktionen für SSR > 1

- FFT mit 32-Bit-Manipulation

- Gemischte Radix-3- und Radix-5-FFTs

- Kronecker-Matrix-Produkt

- Householder-basierter QRD-Solver zur Verbesserung der Stabilität

- DFT für SSR > 1

Neue DSP-Bibliotheksfunktionen für AMD Versal AI Edge-Serie mit AIE-ML

- General Matrix Vector (GEMV) mit SSR-Unterstützung

- General Matrix Multiply (GEMM) mit SSR-Unterstützung

AIE-API-Erweiterungen

Unterstützung für Radix-3-/Radix-5-FFTs

Verbesserungen im KI-Engine-Simulator

- Simulationsfunktionen mit Cycle-Approximate-Methode für KI-Engine-Konzepte mit PL ohne erforderlichen CIPS-IP-Kern (Control, Interfaces, and Processing System – Steuerungs-, Schnittstellen- und Verarbeitungssystem)

- Unterstützung von Vitis Analyzer für Hardware-Emulation mit Simulatoren von Drittanbietern wie VCS, Questa, Xcelium und Riviera

- Export von Tabellen aus Vitis Analyzer im CSV-Format

- Unterstützung neuer DSP-Funktionen für AIE und AIE-ML in AMD Vitis Model Composer

- Time Division Multiplex (TDM) FIR-Filterfunktionen

- Zur Entwicklung von Polyphase Channelizers mit einem Durchsatz von 1 GSPS und höher

- DFT/IDFT – mit SSR-Unterstützung

- Optimierte Transformationen für Durchsatz/Latenz auf kleinen Größen

- FFT/IFFT – mit erweiterter Unterstützung für CINT32-Bit-Manipulation

- FFT/IFFT mit gemischter Radix – mit AIE-ML-Unterstützung

- Benutzerfreundliche Verbesserungen am Model Composer Hub-Block

- Verbesserungen beim Hardwarevalidierungs-Flow

- Unterstützung von Betriebssystem- und MATLAB®-Versionen mit Release 2024.1 hinzugefügt:

- RHEL 9

- MATLAB R2023a und R2023b

Neue Beispielkonzepte auf GitHub verfügbar.

Ein neues Schablonen-Pragma vereinfacht den HLS C++-Code für Bild- und Videofilter

Neue Assistenten für Bibliotheksfunktionen greifen auf das GitHub-Repository der AMD Vitis Bibliotheken zu

- „Solver“- und „Vision“-IPs (OpenCV-kompatibel) für AMD Vivado Designtoolerstellen

- Verfügbare Bibliotheksbeispiele ausführen

Das Pragma für Memory Interface (ap_memory) kann jetzt Ports für AMD Vivado IP Integratorbündeln

Der neue HLS-Komponentenvergleich zeigt Metriken für mindestens 2 Komponenten nebeneinander an

Unterstützung für vom Benutzer bereitgestellten RTL-Code zum Ersetzen einer C++-Funktion (Black-Box-Flow)

Code Analyzer kann nun Elemente von C++-Konstrukten aufteilen, um die Performance-Analyse zu optimieren

Neue Benutzersteuerung für die globale HLS-FSM-Codierung und Auswahl des Status „Safe“

Zugriff auf Clang Sanitizers während C-Simulation zur Durchführung von Adress- und Initialisierungsprüfungen

Highlights des Release 2023.2 der Vitis™ Softwareplattform:

Erweiterungen für DSP-Designs der Versal™ AI Engine

- Neue DSP-Bibliotheksfunktionen

- Neue API-Unterstützung für DSP-Funktionen

- Neue Funktionen in KI-Engine-Compiler und Simulatoren

Neue eigenständige Vitis Embedded Software

- Ein kleineres eigenständiges Installationsprogramm für Entwickler, die C-Code für das integrierte Arm®-Subsystem schreiben

- Alle integrierten Funktionen, einschließlich Dienstprogramme wie Bootgen und XSCT, werden bereitgestellt

Neue integrierte Vitis Unified-Designumgebung

- Konsistente GUI und CLI in allen Vitis Workflows

- Auf Eclipse Theia basierende GUI der nächsten Generation bietet mehr Flexibilität und benutzerfreundliche Funktionen für verbesserte Arbeitseffizienz

Neues bei Vitis nach Kategorie

Erweitern Sie die folgenden Abschnitte, um mehr über die neuen Funktionen und Verbesserungen in Release 2023.2 der Vitis Softwareplattform zu erfahren. Informationen zu unterstützten Plattformen, verändertem Verhalten und bekannten Problemen finden Sie in den Versionshinweisen zu Release 2023.2 der Vitis Softwareplattform für den Flow zur Anwendungsbeschleunigung und den Flow für die Entwicklung von Embedded Software.

Neue DSP-Bibliotheksfunktionen für KI-Engines

- FFT mit gemischter Radix

- Discrete Fourier Transform (DFT)

- General Matrix-Vector Multiply (GEMV)

Neue API-Unterstützung für DSP-Funktionen

- FFT-IP mit Datentypen zur cint32-Manipulation

- Unterstützung für cint16 für Radix-4-FFT-APIs

- Vektorisierungen von „fix2flt“ und „flt2fix“ in API implementiert

Neue API-Unterstützung für AIE-ML

- APIs unterstützen nun int32/cint32-Datentypen in der Funktion sliding_mul()

- APIs unterstützen jetzt <float>-Datentypen in der Funktion sliding_mul()

- Alle AIE-API-Routinen, die zur Unterstützung der Sparse-Matrixmultiplikation erforderlich sind, werden bereitgestellt

Aktualisierungen der Hauptkomponenten:

- U-Boot 2024.1

- Vertrauenswürdige Arm-Firmware 2.10

- Linux-Kernel 6.6_LTS

- Qemu 8.1

- Xen 4.18

- OpenAMP 2023.10

Sunset BSPs:

- AMD Microblaze™: VCU118, KCU105, KC705, AC701

- Zynq: zc706

- AMD Versal™: VMK180-EMMC, VMK180-OSPI

- Zynq MP: ZCU111

Neue BSPs (XSCT):

- VEK280 Produktions-BSP mit neuem ETH Phy

Neue BSP für System-Device-Tree-Flow (SDT):

- ZCU102, ZCU104, ZCU105, ZCU216

- ZCU208, ZCU208-sdfec, ZCU670

- VCK190

- VMK180

- VPK120

- VPK180

- VEK280

- Der AIE-Compiler unterstützt jetzt 2D- und 3D-Arrays als Eingänge oder Ausgänge

- Vitis Analyzer erstellt jetzt einen Bericht mit Anleitung zur FIFO-Dimensionierung

- Neue Unterstützung für die Beschleunigung von Multi-threaded-Simulator-Kernels und VCD-Analyzer (Value Change Dump)

- Externe Schnittstelle mit MATLAB®-Umgebung und Python Traffic Generators

- Verbessertes AXI-Stream-Modell mit Unterstützung für leere/Wartezyklen bei der PLIO-Ausrichtung

- Erweiterte Entwurfsregelprüfungen

- Auslagerung von KI-Engine-Trace über Hochgeschwindigkeits-Debugging

- Unterstützung von NoC- und Hard-DDRMC-Profilerstellung in der Vitis Umgebung

- Das Vitis Tool unterstützt jetzt AIE-ML-Trace für VEK280 und die Alveo™ V70 AI Inference-Beschleunigerkarte

- KI-Engine-Block-Updates

- Unterstützung für den Import von AIE-ML-Graphen als Blöcke in Vitis Model Composer

- Neue DSPlib-Funktionen für die Implementierung von AIE und AIE-ML in Vitis Model Composer

- Darstellung der AIE-Simulatorausgabe für interne Signale im Simulink® Tool

- HLS-Kernel-Block-Updates

- Automatische Erstellung von Testbenches

- Unterstützung erweiterter Datentypen für HLS-Kernel-Blöcke

- Integration von Vitis Model Composer und Vitis Tool

- Generierung von xo- und libadf.a-Dateien direkt aus Vitis Model Composer

- Weitere Verbesserungen

- Unterstützung der MATLAB® Toolversion: R2021a, R2021b Update 6, R2022a Update 6, R2022b

- Unterstützung zusätzlicher Topologien für den Hardwarevalidierungs-Flow

- Neues Beispielmaterialauf GitHub verfügbar

- Neue Vitis Unified IDE für HLS-Komponenten

- Neue Vitis HLS-Lizenzanforderungen

- Neue Code-Analyzer-Funktion zum Abrufen von Performance-Schätzungen vor der Ausführung der C-Synthese

- Verbesserungen der AXI-Schnittstelle:

- Unterstützung für HLS AXI-Stream-Side-Channels

- Unterstützung für vom Benutzer konfigurierbares AXI-Master-Caching

- Weitere Verbesserungen:

- Neuer Bericht zur Codekomplexität, um Probleme mit der Konzeptgröße während der C-Synthese zu identifizieren

- Verbesserungen der Kompilierungszeit: Durchschnittliche Verbesserung der Kompilierungszeit um 20 % in Release 2023.2 gegenüber 2023.11

Highlights des Release 2023.1 der Vitis Softwareplattform:

Neue Vitis™ Bibliotheksfunktionen für Versal™ AI Engine (AIE)-Arrays

- DSP-Bibliotheksfunktionen – mehr FIR-Filterkonfigurationen

- Funktionen der Solver-Bibliothek – Erweiterungen für höhere Performance

Verbesserungen des Design-Flows für die Versal AI Core- und AI Edge-Serie

- AIE-Compiler-Unterstützung für 2D- und 3D-Arrays als Eingänge/Ausgänge

- Anleitung zur FIFO-Dimensionierung mit AIE-Simulatoren zur Vermeidung von Deadlocks

- Verbesserungen der AIE-Statusmeldungen

- Neue Standard-GUI für den Vitis Analyzer

Unterstützung für den Export der Vitis Umgebung in die Vivado™ Umgebung

- Entwicklungsteams von Vitis und Vivado Tools können parallel an einem gemeinsamen Schnittstellen-Checkpoint arbeiten

Neues bei Vitis nach Kategorie

Erweitern Sie die folgenden Abschnitte, um mehr über die neuen Funktionen und Verbesserungen in Release 2023.1 der AMD Vitis Softwareplattform zu erfahren. Informationen zu unterstützten Plattformen, verändertem Verhalten und bekannten Problemen finden Sie in den Versionshinweisen zu Release 2023.1 der Vitis Softwareplattform für den Flow zur Anwendungsbeschleunigung und den Flow für die Entwicklung von Embedded Software.

DSP-Bibliothek – FIR-Filter

- Erweiterte Fractional-Resampler-FIR, Einzelraten-FIR, Halbband-FIR und Ratenänderungs-FIR, damit Koeffizienten-Bits breiter als Datenbits sein können

- Fractional-Resampler-FIR unterstützt auch SSR-Vorgänge mit mehreren AIE-Kacheln und ermöglicht das erneute Laden des Koeffizienten

Solver-Bibliothek

- Verbesserte API-Performance mit High-Performance-Streaming-Konzepten (ca. 300 Kacheln)

- Unterstützung für QR- und Cholesky-Zerlegung für 4D-Data-Mover-Funktionen zum Lesen oder Schreiben von Daten aus AIE-Arrays

- Der AIE-Compiler unterstützt jetzt neben 1D- auch 2D- und 3D-Arrays als Eingänge oder Ausgänge.

- Der AIE-Compiler unterstützt Graph-in-Graph-Konstrukte (Subgraphen) und bedingte Port-Konstrukte.

- Neue APIs für die AIE CINT-zu-CFLOAT-Datenkonvertierung.

- Verbesserungen der AIE-Statusmeldungen zur Generierung einer Datei, die Informationen über Kacheln, Ereignisse und zusätzliche Register auf AIE-ML- und AIE-Kacheln im Konzept enthält.

- Auslagerung der AIE-Ereignisverfolgung über High-Speed Differential Pairs (HSDPs) anstelle der In-Memory-Speicherung auf Versal Chips.

- Unterstützung von NoC- und Hard-DDR-MC-Profilerstellung in der Vitis Umgebung.

- Ereignisverfolgung in AIE-Fenstern zum Prüfen eines bestimmten Teils einer Anwendung.

- Anleitung zur FIFO-Dimensionierung zur Vermeidung von Deadlocks.

- Möglichkeit, Knoten auszuwählen, die vom AIE-Simulator gemeldet werden, um die Größe der Simulator-VCD-Datei zu verringern und die Simulation zu beschleunigen.

- Der AIE-Simulator generiert jetzt einen Bericht (der im Vitis Analyzer angezeigt werden kann), der zeigt, welche AIE Speicherzugriffsverletzungen aufweist und welchen Zeilen im C-Code des Graphen diese entsprechen.

- Die Visualisierung von Daten aus der Traceansicht unterstützt jetzt auch das AIE-ML-Array.

- Unterstützung neuer Datentypen für FIR-Filterkonfigurationen, die auf Versal AI Engines ausgerichtet sind

- Zwei neue für DSP58 optimierte Gleitkomma-Funktionen in adaptiven Versal SoCs

- Schnellere Reaktionszeit für alle Vitis Model Composer-Bibliotheksfunktionen, die auf Versal AI Engines ausgerichtet sind

- Weitere Verbesserungen:

- Verbesserungen an HLS-Kernel-Blöcken

- Verbesserungen am Vitis Model Composer-Hub

- Unterstützung für MATLAB Toolversionen R2021a, R2021b, R2022a

- Performance-Verbesserungen2: Durchschnittliche Latenzverbesserungen um 5,2 % in Release 2023.1 gegenüber 2022.2

- Einfache Möglichkeit zum Download, Anzeigen und Instanziieren von L1-Bibliotheksfunktionen im Vitis HLS-Tool

- Verbesserte Unterstützung für AXI-Transaktionen und Burst-Berichte im Vitis HLS-Tool

Highlights des Release 2022.2 der Vitis Softwareplattform:

Neue Vitis™ Bibliotheksfunktionen für Versal™ AI Engine (AIE)-Arrays

- DSP-Bibliotheksfunktionen – erweiterte Funktionen

- Funktionen der Solver-Bibliothek

- Funktionen der Vision-Bibliothek

- Funktionen der Ultraschallbibliothek

Verbesserungen des Design-Flows für die Versal AI Core- und AI Edge-Serie

- Steuerung der relativen Platzierung von Kernels im KI-Engine-Array – höhere Performance und bessere Nutzung

- Verbesserungen am AIE x86-Simulator – verbesserte Modellierung von Deadlock-Bedingungen im x86-Simulator

- AIE-API-Erweiterungen – Radix-3/5-FFT und Matrix-„x“ Vektor-APIs hinzugefügt

- Erweiterte Profilerstellungs- und Debugging-Funktionen für Versal Konzepte – Deadlock-Erkennung, umfangreichere Erfassung von Tracedaten, Unterstützung von RTL/Python-Testbench

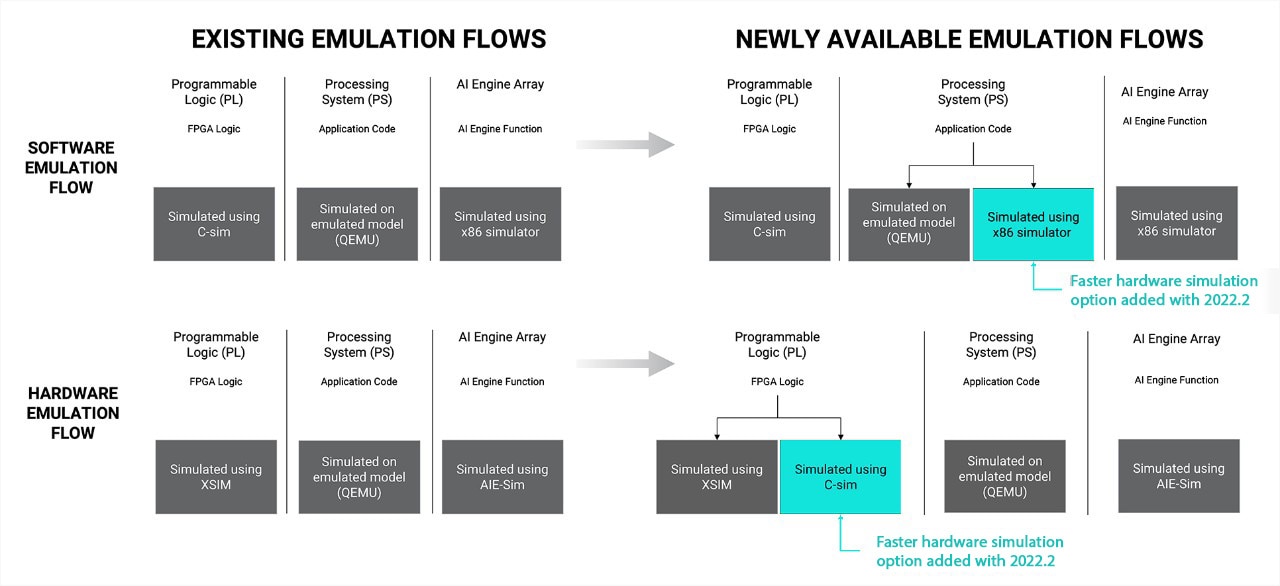

- Neue Simulationsmöglichkeiten für heterogene Konzepte in Vitis

Neues bei Vitis nach Kategorie

Erweitern Sie die folgenden Abschnitte, um mehr über die neuen Funktionen und Verbesserungen in Release 2022.2 der AMD Vitis Softwareplattform zu erfahren. Informationen zu unterstützten Plattformen, verändertem Verhalten und bekannten Problemen finden Sie in den Versionshinweisen zu Release 2022.2 der Vitis Softwareplattform für den Flow zur Anwendungsbeschleunigung und den Flow für die Entwicklung von Embedded Software.

DSP-Bibliotheksfunktionen

- Die Implementierung von Super Sample Rate (SSR)-FIR-Filtern auf der KI-Engine unterstützt jetzt die Funktion zum erneuten Laden des Koeffizienten und die dynamische Punktgröße

- FFT-Fensterelement zur FFT-Funktion hinzugefügt, die auf das KI-Engine-Array abzielt

Funktionen der Solver-Bibliothek

- QR-Zerlegung (Quadrature Rotation)

- Cholesky-Zerlegung

Funktionen der Vision-Bibliothek

- Vier neue Videofunktionen für das KI-Engine-Array

Funktionen der Ultraschallbibliothek

- Verschiedene Funktionen zur Erstellung medizinischer Ultraschallkonzepte

- Möglichkeit, Einschränkungen hinzuzufügen, um die relative Platzierung von Kernels im KI-Engine-Array zu steuern – so erhalten Benutzer eine höhere Performance und eine bessere Nutzung

- Verbesserte Modellierung von AIE-Deadlock-Bedingungen im x86-Simulator

- Neue AIE-API hinzugefügt: Radix-3/5-FFT und Matrix-„x“ Vektor-APIs

- Generierung von KI-Engine-Profilerstellungsberichten in HW-Emulation

- Deadlock-Erkennung mit XSDB (AMD System Debugger) für KI-Engine- und PL-basierte Konzepte

- Mit Xilinx Runtime (XRT) gesteuerte kontinuierliche Auslagerung der KI-Engine-Ereignisverfolgung über PLIO

- Unterstützt PS-Anwendung auf x86-Hostcomputer für SW-Emulation

- Ermöglicht SystemC-Funktionsmodelle für HW-Emulation anstelle von RTL

- So können Benutzern den KI-Engine-Kernel mit einer einfachen RTL-Testbench oder einem Python-Skript-basierten Traffic Generator simulieren

- Der Status der KI-Engine kann während der HW-Emulation mit dem Vitis™ Analyzer analysiert werden

Neue Simulationsoptionen für die Vitis Umgebung in Release 2022.2: x86-Simulation des Prozessorsystems und x86-Simulation der KI-Engine: Die Simulation der programmierbaren Logik kann mit dem x86-Simulator durchgeführt werden.

- Funktionen für Versal AI Engine-Design

- Möglichkeit, Grapheneinschränkungen beim Design von KI-Engine-DSP-Bibliotheksblöcken hinzuzufügen – bessere Nutzung und Performance

- Neue Möglichkeit zur Simulation von KI-Engine-Konzepten mit Cycle-Approximate-Methode

- Der Importblock des KI-Engine-Graphen erkennt automatisch RTP-Ports (Run Time Parameter, Laufzeitparameter)

- Erweiterungen und Ergänzungen der DSP-Bibliotheksblöcke

- Allgemeine Funktionen

- Unterstützung des Hardwarevalidierungs-Flows für heterogene Systemkonzepte, die PL- und AIE-Array verwenden

- Vitis Model Composer-Hub-Block unterstützt jetzt heterogene Konzepte

- Automatische Erkennung gültiger KI-Engine-, HDL- und HLS-Subsysteme

- Der Hardwarevalidierungs-Flow wurde erweitert, um reine HDL-Konzepte und HDL → KI-Engine → HDL-Konzepte für Versal Plattformen zu unterstützen

- Verbesserte Unterstützung des Codierungsstils „Parallelität auf Aufgabenebene“

- Ermöglicht schnellere C-Simulation und bessere QoR

- Zusätzliche Performance- und Timing-Verbesserungen

- Verbesserte Burst-Inferenz

- Automatische Inferenz von Unroll-, Pipeline-, Array_Partition- und Inline-Pragmen für höhere Performance

- Verbesserte Timing-Genauigkeit, was zu einer Timing-Closure-Verbesserung bei höheren Frequenzen führt

- Sonstige Funktionen

- Analyse und Debugging: Einfügen der printf-Funktion in den C-Code wird jetzt auch nach der Synthese in der RTL unterstützt

- Benutzerfreundlichkeit: Neues Performance-Pragma zum automatischen Erzielen eines bestimmten Transaktionsintervalls

- HLS::stream-Schnittstellen werden jetzt von FFT- und FIR-IPunterstützt

Highlights des Release 2022.1 der Vitis Softwareplattform:

Vitis™ Flow-Erweiterung für Versal™ ACAP und AI Engine

- Unterstützt AMD DFX-Plattform mit einer statischen Region und einer DFX-Region

- AIE-Profilerstellung unterstützt die Erkennung von Blockaden/Deadlocks, generiert Anzeigeberichte zum KI-Engine-Status (einschließlich Fehlerereignissen) in Vitis Analyzer

- Externe Traffic Generators in x86sim, AIEsim und SW-Emulation sind viel flexibler und können leicht in Simulations- und Emulations-Flows eingefügt werden

- Vitis Model Composer unterstützt Hardwarevalidierung, Linux und HW-Emulation

Vitis für DC und Vitis HLS

- Vitis bietet zusätzliche Unterstützung für die Berichterstellung beim Generieren dynamischer Regionen. Zu den Verbesserungen der Flow-Berichte zählen 3 neue oder aktualisierte Berichte

- Bei der PL-Profilerstellung in Vitis haben Benutzer jetzt die Wahl zwischen der Trace-Auslagerung an Speicherressourcen (bevorzugt) oder FIFO im PL für höhere Performance

- Neuer Zeitachsentrace-Viewer zeigt das Laufzeitprofil an, sodassder Benutzer nach der Simulation in der Vitis HLS-GUI bleiben kann

- Vitis HLS unterstützt jetzt ein „Smart“-Konstrukt höherer Ebene über das neue Performance-Pragma oder die set_performance_directive

- Vitis Graph-Bibliothek mit L3-API-Verbesserungen (Einsparung von 1 ms für Kernel-Aufruf) für die Performance

Neues bei Vitis nach Kategorie

Erweitern Sie die folgenden Abschnitte, um mehr über die neuen Funktionen und Verbesserungen in Release 2022.1 der AMD Vitis Softwareplattform zu erfahren. Informationen zu unterstützten Plattformen, verändertem Verhalten und bekannten Problemen finden Sie in den Versionshinweisen zu Release 2022.1 der Vitis Softwareplattform für den Flow zur Anwendungsbeschleunigung und den Flow für die Entwicklung von Embedded Software.

- Neue Genomik-Beschleunigerbibliothek hinzugefügt (L1, L2 und L3)

- Graph-Bibliothek, L3-Performance-Verbesserungen

- Vitis Datenbankbibliothek, multifunktionaler GQE-Kernel

- Neue Funktionen in Vision-Bibliothek hinzugefügt

- Neue Funktionen in Vitis AIE Vision-Bibliothek (Zusätze/Erweiterungen)

- Vitis AIE DSP-Bibliothek, FIR-Resampler ersetzt fraktionalen FIR-Interpolator

- Neue APIs in Vitis Codec-Bibliothek: API jxlEnc, API „leptonEnc“, API „resize“, API „WebpEnc“

Vitis Datenkompressionsbibliothek

- ZLIB-Komprimierungsverbesserung, angepasste 8-Kern-Komprimierung für 8-KB-Lösung

- Verbesserung der ZLIB-Dekomprimierung, angepasste IP für 8-KB-Dateigröße

- Verbesserte Abfrage der Plattformfunktionen

- Verbesserte HBM-Benutzerfreundlichkeit. Möglichkeit zur Auswahl eines bestimmten S_AXI-Einstiegspunkts zum HMSS für Kernel-M_AXI, RAMA-Einfügung wird von den Konfigurationsdateien unterstützt

Vitis AI Engine Compiler

- Automatische Erkennung und Analyse von Blockaden/Deadlocks der KI-Engine in der Hardware

- Analyse der automatisierten Statusausgabe

- Analyse der automatisierten Statusausgabe – Puffer

- Analyse der manuellen Statusausgabe in der Hardware

- Analyse der manuellen Statusausgabe

- Verbesserungen der KI-Engine-Ereignisverfolgung

- Externe Traffic Generators AIEsim

- Verbesserungen bei der KI-Engine-Profilerstellung auf HW

- KI-Engine-Unterstützung für Broadcast-Fenster

- Verbessertes Graphen-Programmierungsmodell in Vitis AI Engine Compiler

- Vitis AI Engine Compiler – PLIO/GMIO in ADF-Graphen

Vitis HLS

- Analyseverbesserungen, neuer Zeitachsentrace-Viewer

- Verbesserungen des Codierungsstils, Unterstützung von Array-Partitionen für den Typ „Stream of Blocks“

- Pragmen-Abstraktion, neues Performance-Pragma (mit Anweisung)

- Vitis Core-„Einzeiler“, Vitis HLS – neuer Zeitachsentrace-Viewer, neues PERFORMANCE-Pragma, Unterstützungsfenster für Typ „Stream of Blocks“

- Neuer Viewer eingeführt

- Zeigt das Laufzeitprofil aller noch vorhandenen Funktionen in Ihrem Design an, d. h. der Funktionen, die in Module konvertiert werden

- Besonders nützlich, um das Verhalten von Datenflussbereichen nach der Co-Simulation anzuzeigen

- Nativ für Vitis HLS – der xsim-Wellenform-Viewer muss nicht mehr gestartet werden (externes Tool)

Vitis Analyzer

- Verbesserung von Vitis Analyzer, Anpassungsmöglichkeit für Speichern/Wiederherstellen der Zeitachse

- Erweiterung der Berichterstellung, report_qor_assessment, xclbin-Taktinformationen, Vivado Automatisierungsübersicht

- Verbesserung der Profilerstellung, neue PL-Profilerstellungsinfrastruktur aktiviert, mehrere trace_memory-Optionen können hinzugefügt werden, um mehrere Speichermonitore einzufügen (nur HW), Beispielkonfigurationsdatei für V++ Linker zum Auslagern von Tracedaten für alle CUs in SLR0 nach DDR0 und für alle CUs in SLR1 nach DDR1

Vitis IDE

- Bootgen-GUI für Versal aktualisiert

- Toolchain-Aktualisierung

- XSCT, STAPL-Unterstützung, Skriptgenerierungsbefehl zum Hinzufügen von Linker

- Systemkompilierungs-Flow, siehe Dokument zur Systemkompilierung

Vitis Emulation

- Software-Emulationsunterstützung für automatischen Neustart und Mailbox-Unterstützung für ständig ausgeführte Kernels hinzugefügt

- Free-Running-Kernel benötigt „while(1)“ für SW-Emulation nicht

- Software-Emulationsunterstützung für externen Traffic Generator hinzugefügt

- Die Hardware-Emulation kann das Funktionsmodell des HLS C-Quellcodes für Streaming-IP verwenden.

- API xrt::system zur Ermittlung der Chip-Anzahl hinzugefügt

- API xrt::message für Logging-Nachrichten hinzugefügt

- Hostcode der nativen XRT-API erfordert jetzt:

-std=c++17 oder höher - Experimentelle xrt::queue-APIs für die asynchrone Ausführung synchroner Vorgänge hinzugefügt

- xbutil kann AIE-FIFO-Zähler anzeigen, die beim Debuggen von AIE-Deadlock-Szenarien helfen

- Option xbutil --legacy wurde entfernt.

- xclbinutil --info stellt Taktinformationen für integrierte Plattformen bereit

- xbutil auf ARM kann SOM-Images laden

- Eigenständiges xbtop-Dienstprogramm zur Anzeige einer Ausgabe, die dem top-Befehl von Linux ähnelt (ersetzt das ältere xbutil -top)

- XRT-Dienstprogramme unterstützen die automatische Vervollständigung in Bash mit der Tabulatortaste.

- ALVEO Plattform-Updates, Plattform-Updates für verbesserte Stabilität, Kartenmanagement-Updates, SC-Firmware-Update-Tool

- Embedded Plattform, neue VCK190 DFX-Plattform: xilinx_vck190_base_dfx_202210_1, Embedded Plattformen werden jetzt mit Vitis installiert. Vivado fügt ein neues anpassbares Beispielkonzept hinzu: Vitis Platform for MPSoC

- Umfassende Überarbeitung des Vitis Model Composer-Hub-Blocks für Skalierbarkeit und Benutzerfreundlichkeit

- Der Hardwarevalidierungs-Flow unterstützt nun neben Bare-Metal auch Linux

- Die Blöcke „AIE zu HDL“ und „HDL zu AIE“ enthalten nicht mehr die HDL-Gateway-Blöcke

- 2022.1 wird jetzt mit einem Snapshot der Beispiele für Kunden geliefert, die keinen Internetzugang haben. Das Tool fordert den Benutzer auf, eine neue Version der Beispiele von GitHub herunterzuladen, falls verfügbar

- Aus Gründen der Benutzerfreundlichkeit werden Dienstprogrammblöcke, die nicht Teil der Codegenerierung sind, jetzt mit einem weißen Hintergrund dargestellt

- Bibliotheksbrowser wurde erweitert und benutzerfreundlicher gestaltet

- RHEL 8.x-Unterstützung

- MATLAB-Unterstützung – R2021a und R2021b

Highlights des Release 2021.2 der Vitis Softwareplattform:

- Neue domänenspezifische Entwicklungsumgebungen

- Vitis™ Video Analytics SDK auf Kria™ SOM, Alveo™ U30/U50 und VCK5000 Versal™ Entwicklungskarte: Mehr erfahren >

- Vitis Blockchain-Lösung auf Varium™ C1100-Karte mit Vitis Bibliotheken: Mehr erfahren >

- Unterstützung für den vollen End-to-End-Flow für VCK5000- und Varium C1100-Karten

- Erweiterte Kernfunktionen

- C/C++-Compiler mit High-Level-Abstraktion für Vitis AI Engine, Autom. Pragma-Inferenz, Bereichsgruppeneinschränkungen

- Verbesserungen an Vitis AI Engine x86simulator: Tracebericht, Erkennung von Speicherzugriffverletzungen und Deadlocks

- Vitis HLS-EoU, Verbesserungen bei Timing und QoR, HLS-APIs für benutzergesteuerte Burst-Inferenz

- Vitis Analyzer bietet Verbesserungen bei Zeitachsen-Tracebericht, Datenvisualisierung und Blockaden-Analyse

- Vitis XRT zur Unterstützung für mehrere Prozesse und Threads in KI-Engine für KI-Engine-Graphensteuerung

- Vitis IDE und Emulation unterstützen KI-Engine-Trace, SW-Emulation für KI-Engine-Anwendungen

- 39 neue C/C++-Bibliotheken in verschiedenen Domänen: DSP, Datenanalyse, Vision, Komprimierung, Datenbank, Graph, Sicherheit usw. – insgesamt über 1.000 Bibliotheksfunktionen für Datenbank, Graph, Sicherheit usw.

- Vitis Model Composer

- Reduzierung der Kompilierungs-/Simulationszeit um das 3-Fache, Reduzierung der Kompilierungszeit um das 7-Fache bei paralleler Kompilierung

- Neuer Hardwarevalidierungs-Flow und verbesserte funktionale Co-Simulation

Neues bei Vitis nach Kategorie

Erweitern Sie die folgenden Abschnitte, um mehr über die neuen Funktionen und Verbesserungen in Release 2021.2 der AMD Vitis Softwareplattform zu erfahren. Informationen zu unterstützten Plattformen, verändertem Verhalten und bekannten Problemen finden Sie in den Versionshinweisen zu Release 2021.2 der Vitis Softwareplattform für den Flow zur Anwendungsbeschleunigung und den Flow für die Entwicklung von Embedded Software.

Hinweis: Vitis Accelerated Libraries sind als separater Download verfügbar. Sie können von GitHub oder direkt aus der Vitis IDE heruntergeladen werden.

| Bibliothek | 2021.1 | 2021.2 | Neue Funktionen in 21.2 |

|---|---|---|---|

| xf_blas | 167 | 167 | 0 |

| xf_codec | 3 | 3 | 0 |

| xf_DataAnalytics | 33 | 36 | 3 |

| xf_database | 62 | 65 | 3 |

| xf_compression | 78 | 93 | 15 |

| xf_dsp | 94 | 96 | 2 |

| xf_graph | 53 | 59 | 6 |

| xf_hpc | 37 | 37 | 0 |

| xf_fintech | 116 | 116 | 0 |

| xf_security | 135 | 140 | 5 |

| xf_solver | 11 | 11 | 0 |

| xf_sparse | 11 | 11 | 0 |

| xf_utils_hw | 55 | 57 | 2 |

| xf_opencv | 147 | 150 | 3 |

| Gesamt | 1.002 | 1.041 | 39 |

Hinweis: Für Vision zählen Sie einfach die Anzahl der Unterordner in L*/tests, da jede API mehrere Tests für verschiedene Typen aufweist

Vitis Vision-Bibliothek

- Programmierbare Logik (PL)

- End-to-End-Mono-Bildbearbeitung (ISP) mit CLAHE TMO

- RGB-IR zusammen mit RGB-IR-Bildbearbeitungspipeline (ISP)

- Globale Farbtonzuordnung (Global Tone Mapping, GTM) zusammen mit einer ISP-Pipeline unter Verwendung von GTM

| Neue Features | Kat. | Kunde/Strategie | Segmente | Beschreibung |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | Automobilbereich, ISM | • Unterstützung für 4x4 RGB-IR-Demosaicing • Hauptsächlich für Innenraum-Überwachungssystem • Überwachungskamera bei schwachem Licht |

| Mono (CCCC) | ISP | Strategie | Automobilbereich, ISM, A&D | • Maschinelles Sehen •Anwendungen bei schlechten Lichtverhältnissen |

| Globale Farbtonzuordnung (Global Tone Mapping, GTM) | ISP | Strategie | Automobilbereich, ISM, A&D | • Verbesserter Dynamikbereich und Kontrast • Kostengünstigere Version im Vergleich zur lokalen Farbtonzuordnung (Local Tone Mapping, LTM) |

| Dichter optischer Fluss TV-L1 | CV | NTT | ISM | • Höhere Robustheit (gegen Beleuchtung, Rauschen, Okklusionen) für den optischen Fluss |

KI-Engine (AI Engine, AIE)

- BlobFromImage

- Back-to-Back-filter2D mit Unterstützung von Batchgröße 3

| Neue Features | Kat. | Kunde/Strategie | Segmente | Beschreibung |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | Automobilbereich, ISM | • Unterstützung für 4x4 RGB-IR-Demosaicing • Hauptsächlich für Innenraum-Überwachungssystem • Überwachungskamera bei schwachem Licht |

| ML+X | ISP | Strategie | Automobilbereich, ISM, A&D | • ML-Interferenzvorverarbeitung |

| Gaußsche Pyramide | CV | Strategie | Automobilbereich, ISM, A&D | • Grundlage für die Multi-Scaler-Bildverarbeitung |

| Box-Filter | CV | Strategie | Automobilbereich, ISM, A&D | • Grundlage für Glättung, Tiefpassfilter |

Vitis Datenanalysebibliothek

- Vitis Blockchain-Lösung basierend auf Vitis Bibliotheken

- Gebrauchsfertige Mining-Lösungen für Ethereum

- Open Source und einfache Bedienung und Bereitstellung mit Vitis Bibliotheken über C++

- Flexibel und skalierbar mit Vitis Bibliotheken

- Flexibilität, um mehrere Coins abzubauen

- Anpassung und Kompilierung in Hardware

- Hochgradig optimiertes Konzept

- Hinzufügen von CSV-Parser-API zur Bibliothek

- CSV-Parser kann CSV-Dateien analysieren und Objektstrom generieren, der problemlos mit DataFrame-APIs verbunden werden kann

Vitis Graph-Bibliothek

- Neue L2-Bibliotheken hinzugefügt

- Louvain mit Umnummerierung

- Umnummerierung

- Die Funktion „weight“ wird für Kosinus-Ähnlichkeit unterstützt

Vitis Datenbankbibliothek

- GQE unterstützt die asynchrone Eingabe-/Ausgabefunktion sowie mehrere Karten.

- Dank der asynchronen Unterstützung kann der FPGA-Chip die Verarbeitung starten, sobald ein Teil der Eingabedaten bereit ist.

- Durch die Unterstützung mehrerer Karten können mehrere Alveo Karten ermittelt werden, die für den Einsatz geeignet sind.

Vitis Datenkompressionsbibliothek

- ZSTD Multicore-Komprimierung

- Neue ZSTD Multicore-Architektur und Bereitstellung eines Durchsatzes von >1 GB/s mit Quad-Core.

- Optimierung der ZSTD-Dekomprimierung

- ZSTD-Dekomprimierung optimiert für Performance (Steigerung von 20 %) und Ressourcenverbrauch (Reduzierung von < 30 %)

- Verbesserung der GZIP/ZLIB-Streaming-Kerne für IBM

- Benutzerdefinierte Streaming-IP mit statischer und dynamischer Komprimierung (4 KB und 8 KB)

- Zusätzliche Funktionalität zur Bereitstellung komprimierter Größen im TUSER-Port

- Verbesserung der GZIP/ZLIB-Dekomprimierung für IBM

- Optimierter Huffman-Decoder zur Reduzierung von Latenzzeiten < 1.500 Zyklen

- Deutliche Reduzierung des Ressourcenverbrauchs auf 6.900 (> 9.000 bei älteren Versionen)

- ADLR32-Prüfsummenfunktion hinzugefügt

- GZIP-System-Compiler-PoC

- Erstellung eines System-Compiler-PoC für GZIP-Komprimierungslösung und Benchmarking mit OpenCL-Host.

Vitis DSP-Bibliothek

- DSPLib auf GitHub seit 2021

- Schnelle Fourier-Transformation (FFT/iFFT)

- Erhöhung der Punktgröße auf 32.000 (abhängig vom Datentyp)

- Unterstützung für Stream-API sowie Fenster-API.

- Parallele Leistung (0–4)

- Ermöglicht einen höheren Durchsatz und erweitert den Bereich der unterstützten Punktgrößen

- FIR-Filter

- Anfängliche Streaming-Unterstützung für asymmetrische/symmetrische Einzelraten-FIR

- DDS/Mixer

- Neue Bibliothekseinheit in 2021.2

Vitis Sicherheitsbibliothek

- KECCAK-256 (Hash-Funktion) und CRC32C (Prüfsummenfunktion) veröffentlicht

Vitis Dienstprogrammbibliothek

- Zwei Data-Mover-Implementierungen für das Debuggen von HW-Problemen hinzugefügt.

- LoadDdrToStreamWithCounter: Zum Laden von Daten von PL-DDR in die KI-Engine über AXI-Stream und zum Aufzeichnen der Datenmenge, die an die KI-Engine gesendet wird.

- StoreStreamToMasterWithCounter: Zum Empfangen von Daten von der KI-Engine über AXI-Stream und Speichern in PL-DDR sowie zum Aufzeichnen der Datenmenge, die an DDR gesendet wird.

KI-Engine-API

- Implementiert als reine C++-Header-Bibliothek, die Typen und Vorgänge bereitstellt, die in effiziente KI-Engine-Intrinsics übersetzt werden.

- Stellt parametrisierbare Datentypen bereit, die eine generische Programmierung ermöglichen

- Implementiert die häufigsten Vorgänge auf einheitliche Weise für verschiedene Datentypen

- Allgemeinere Primitive werden transparent in optimierte KI-Engine-Intrinsics übersetzt

- Verbessert die Portabilität über KI-Engine-Architekturen hinweg

KI-Engine-API wird zur Hauptmethode für die Programmierung des KI-Engine-Kernels

Allgemeine Optimierungen

Optimierungsoptionen für den KI-Engine-Compiler

- --xlopt=0, keine Optimierung angewendet.

- --xlopt=1, automatische Berechnung der Heap-Größe, Leitliniengenerierung aus LLVM-IR-Analyse.

- --xlopt=2, automatisches Inlining, Loop Peeling für „Unrolled“-Schleifen, Pragma-Einfügung.

Neu: --xlopt=2 zur Verbesserung der Performance, Standard weiterhin: --xlopt=1

- Automatisches Inlining

- Integriert Funktionen automatisch inline, wenn dies praktikabel und möglich ist, auch wenn die Funktionen nicht als „__inline“ oder „inline“ deklariert sind

- Automatische Pragma-Einfügung

- Fügt Pragmen automatisch in Kernel-Code ein. (Weitere Informationen weiter unten)

Pragma-Inferenz

Notwendig für die Optimierung der Kernel

- Verringert die Verantwortung des Benutzers, effektive und korrekte Schachpragmen hinzuzufügen

Unterstützung für die automatische Inferenz von fünf Pragmen in 2021.2

- Für Performance:

- chess_prepare_for_pipelining für innerste Schleife und äußere Schleifen mit bekanntem Trip-Count

- chess_loop_range für Schleifen mit bekanntem Trip-Count

- chess_unroll_loop/chess_flatten_loop für innerste Schleifen mit bekanntem Trip-Count

- Für Korrektheit:

- chess_unroll_loop_preamble, wenn Trip-Count kein Vielfaches des Unroll-Faktors ist

Aktualisiertes Graphen-Programmierungsmodell PLIO und GMIO

Die Modelländerungen umfassen:

- Änderungen bei der Verwendung von „simulation::platform“

- Interaktion mit PLIO/GMIO-Objekten im Graphen, Position bestimmt Eingabe/Ausgabe.

- Änderungen globaler PLIO/GMIO-Objekte im Graphen.

- Änderungen bei connect<>-Anweisungen des Graphen.

PLIO/GMIO in ADF-Graphen

Derzeit

- PLIO, GMIO, simulation::platform und Verbindungen im globalen Geltungsbereich schreiben

GMIO gm0(“GMIO_In0”, 64, 1);

GMIO gm1(“GMIO_In1”, 64, 1);

…

GMIO gm7(“GMIO_In7”, 64, 1);

PLIO pl0(“PLIO_Out0”, plio_32_bits, “data/output0.txt”, 250.0);

PLIO pl1(“PLIO_Out1”, plio_32_bits, “data/output1.txt”, 250.0);

…

PLIO pl7(“PLIO_Out7”, plio_32_bits, “data/output7.txt”, 250.0);

simulation::platform<8,8> plat(&gm0, &gm1,…, &gm7, &pl0, &pl1,…, &pl7,);

subgraph g;

connect<> net0(plat.src[0], g.in[0]);

connect<> net1(plat.src[1], g.in[1]);

…

connect<> net7(plat.src[7], g.in[7]);

connect<> net8(g.out[0], plat.sink[0]);

connect<> net9(g.out[1], plat.sink[1]);

…

connect<> net15(g.out[7], plat.sink[7]);

Alternative Methode

- Graphen der obersten Ebene erstellen und PLIO, GMIO und Verbindungen hineinverschieben

- Verwaltung von Verbindungen darin für Schleife zulassen

class topgraph

{

input_gmio gm[8];

output_plio pl[8];

subgraph sg;

topgraph()

{

for (i=0; i<8; i++)

{

gm[i] = input_gmio::create(“GMIO_In”+std::to_string(i), 64, 1);

pl[i] = output_plio::create(“PLIO_Out”+std::to_string(i), plio_32_bits, “data/output”+std::to_string(i)+”.txt”, 250.0);

connect<>(gm[i].out[0], sg.in[i]);

connect<>(sg.out[i], pl[i].in[0]);

}

}

};

topgraph g;

Verbesserungen bei Bereichsgruppeneinschränkungen

Möglichkeit zur Verwendung von Flags im ADF-Graphen oder in der Constraints-Datei zur Steuerung von Mapper und Router

- -contain_routing – wenn TRUE angegeben ist, wird sichergestellt, dass das gesamte Routing (einschließlich der Netze zwischen Knoten in der nodeGroup) in der Bereichsgruppe enthalten ist.

- -exclusive_routing – wenn TRUE angegeben ist, wird sichergestellt, dass das gesamte Routing (Netze zwischen Knoten in der nodeGroup ausgenommen) von der Bereichsgruppe ausgeschlossen wird.

- -exclusive_placement – wenn TRUE angegeben ist, werden alle Knoten, die nicht in der nodeGroup enthalten sind, nicht innerhalb des Begrenzungsrahmens der Bereichsgruppe platziert.

Snapshots

Snapshots sind Textdateien, die Kommentare und Daten zu allen Kernel-Ports enthalten

- Streams, Paketstreams, kaskadierende Streams

- Fenster, Puffer

- RTP

Umfasst auch alle Plattform-Ports

- PLIO, GMIO, RTP

Ermöglicht es Benutzern, den Datenverkehr an Kernel-Ports zu überprüfen, ohne den Debugger zu verwenden und ohne Kernel-Code-Instrumentierung zu benötigen

Deadlock-Erkennung

- Erkennt Deadlocks in x86-Simulationen, unabhängig davon, ob diese auf unzureichende Eingabedaten oder eine unausgeglichene FIFO-Tiefe auf einem rekonvergenten Pfad zurückzuführen sind

- Die Funktion Stop-on-Deadlock muss während der x86-Simulation durch Angabe der Option --stop-on-deadlock aktiviert werden

- Wenn die Simulation aufgrund eines Deadlocks gestoppt wird, weist die Fehlermeldung darauf hin, dass Sie sie mit der Option -trace --timeout erneut ausführen sollten

Erkennung von Speicherzugriffsverletzungen

Integration mit Valgrind zur Erkennung von Speicherzugriffsverletzungen

- Erkennung

- Lese- und Schreibvorgänge außerhalb des zulässigen Bereichs

- Lesen von nicht initialisiertem Speicher

- Für die Kompilierung ist kein spezifisches Flag erforderlich

- Simulationsflags sind entweder:

- --valgrind: Simulation läuft wie gewohnt und valgrind zeigt einen Bericht an

- --valgrind-gdb: Wie oben, aber mit gleichzeitigem GDB-Debugging

Tracebericht

Deadlock führt zu einer schlechten Simulationsausgabe und Schwierigkeiten bei der Analyse der Fehlerursache

Mit der Traceoption bei der x86-Simulation kann der Simulator verschiedene Zeitstempelinformationen protokollieren:

- Start/Ende der Kernel-Iterationen

- Start/Ende der Stream-Blockaden

- Start/Ende der Sperr-Blockade

Zeitstempel sind in x86-Simulation und KI-Engine-Simulation unterschiedlich

Vom Benutzer gesteuerte Burst-Inferenz

- Bei Anwendungsfällen, die die automatische Burst-Inferenz durch Vitis HLS-Tool nicht erfüllen, können Benutzer die neu eingeführte manuelle Burst-Optimierung einsetzen

- Die neue Klasse „hls::burst_maxi“ unterstützt die manuelle Steuerung des Burst-Verhaltens. Neue HLS-APIs werden zur Verwendung mit der neuen Klasse bereitgestellt

- Benutzer müssen mit dem AXI-AMBA-Protokoll und der Modellierung auf Hardware-Transaktionsebene im HLS-Konzept vertraut sein

Verbesserungen bei Timing und QoR

- Unterstützung für Benutzer bei der Eingabe von Einschränkungen des Durchsatzes auf hoher Ebene

- Verbesserte Genauigkeit der HLS-Zeitabschätzung. Wenn HLS eine Timing-Closure meldet, sollte auch die RTL-Synthese in Vivado erwartungsgemäß die Timing-Anforderungen erfüllen

EoU-Verbesserungen

Schnittstellenadapter-Bericht in C-Syntheseberichten hinzufügen

- Benutzer müssen wissen, welche Auswirkungen Schnittstellenadapter auf ihr Konzept haben

- Schnittstellenadapter haben variable Eigenschaften, die sich auf die Ergebnisqualität des Konzepts auswirken

- Einige dieser Eigenschaften haben verknüpfte Benutzersteuerungen, die Benutzern gemeldet werden sollten

- Die Textversion der Berichte bind_op und bind_storage wird bereitgestellt

Neuen Abschnitt im Synthesebericht hinzufügen, um eine Liste der Pragmen und Warnungen zu Pragmen anzuzeigen

- Übersichtliche Anzeige, bei welchen der hinzugefügten Pragmen Probleme auftreten.

Verbesserungen bei Analyse und Berichterstellung

Die Graph-Anzeige für Funktionsaufrufe verfügt über einige neue Funktionen

- Neue Möglichkeit zum Vergrößern und Verkleinern der Ansicht durch Ziehen der Maus

- Neue Übersichtsfunktion, die den vollständigen Graphen anzeigt und dem Benutzer ermöglicht, Teile des Gesamtgraphen zu vergrößern

- Alle Funktionen und Schleifen werden zusammen mit ihren Simulationsdaten angezeigt

Nach der Simulation ist jetzt ein neuer Zeitachsentrace-Viewer verfügbar. Dieser Viewer zeigt das Laufzeitprofil Ihres Konzepts an, sodass derErmöglicht es den Benutzer in der Vitis HLS-GUI bleiben kann.

Erweiterung der Link-Zusammenfassung

- Bereitstellung von Taktfrequenzinformationen für die KI-Engine, die Plattform und die Recheneinheiten

- Bereitstellung einer neuen Tabelle namens Clocks im Systemdiagramm und Plattformdiagramm

Erweiterung des Plattformexports

- Beim XSA-Export aus Vivado sind keine Quelldateien erforderlich, um lokal für das Projekt zu sein

- Beim XSA-Export aus Vivado keine Änderung an der Projektstruktur

- Verpackung der IPs, die im Hardware-Plattformprojekt verwendet werden, anstatt Verpackung des gesamten IP-Repositorys

Erweiterungen der KI-Engine-Anwendungsemulation

- Unterstützung für die Integration externer Testbenches mit aiesimulation

- Unterstützung für die Integration externer Testbenches mit x86simulation

- Unterstützung für GDB-Debugging mit x86simulation

- Unterstützung für Snapshots der Daten zwischen Kernels in einem Graphen für x86simulation

- Unterstützung für Zugriffsverletzungsprüfungen für x86sim

- Unterstützung für Stop on Deadlock für x86sim

Unterstützung für KI-Engine-Trace

Unterstützung der SW-Emulation für KI-Engine-Anwendungen

Unterstützung des externen Traffic Generators in Verilog/System Verilog

Erweitertes Einfügen der Profilerstellungsüberwachung in Speicherüberwachung

- Derzeit kann die Logik der Profilerstellungsüberwachungslogik auf Kernel-/CU-Port-Basis eingefügt werden. Diese Funktion bietet Benutzern die Möglichkeit, die Überwachungslogik direkt in das Memory Interface einzufügen

- Die Visualisierung der Speicherbandbreite, die direkt auf den Memory Interfaces erreicht wird, kann in der Profilzusammenfassung widergespiegelt werden

- DDR-Speicher und PLRAM werden unterstützt

- Hardware-Flow wird unterstützt

- Um diese Funktion zu aktivieren, müssen sowohl die Verbindungsphase als auch XRT eingerichtet werden

- memory=all

- data_transfer_trace= coarse|fine oder

- opencl_device_counter=true

Erweitertes Einfügen der Profilerstellungsüberwachung in Speicherüberwachung

- Ein VADD-Beispiel, das die Memory-Interface-Überwachung ermöglicht

- Die neue Tabelle „Memory Bank Data Transfer“ ist enthalten

Verbesserungen von Vitis Analyzer

Generischer Profilzusammenfassungsbericht für Nicht-OpenCL-Anwendungen

- Bereitstellung des gleichen Unterstützungsniveaus für XRT-API- und HAL-API-Anwendungen.

- Benutzer wählen aus, welche Berichtstypen sie erstellen möchten. Das Tool generiert sie automatisch und stellt sie in Vitis Analyzer grafisch dar.

OpenCL-Befehle zur PL-Ereigniszeitleiste hinzufügen

- Die Profilerstellung erhöht den Overhead. XRT bietet die Möglichkeit, OpenCL-Ereignisse ohne Overhead im Zeitachsentrace auszugeben.

- Vitis Analyzer kann die XRT-Ausgabe verarbeiten und sie im Zeitachsentrace-Viewer anzeigen.

- xocl_debug=true muss in der xrt.ini festgelegt werden.

Abflachung der Signalhierarchie im Zeitachsen-Tracebericht

- Standardmäßig wird der Signaltrace im Zeitachsen-Tracebericht hierarchisch angezeigt

- Vitis Analyzer bietet die Möglichkeit, die Hierarchie durch Umschalten des Symbols „Signal abflachen“ abzuflachen

- Der Wellenform-Vergleich wird für einen abgeflachten Zeitachsentrace unterstützt

Vitis Analyzer – Datenvisualisierung

- Anzeige von Eingabe-/Ausgabedaten für KI-Engine-Kernels in einem KI-Engine-Konzept

- Unterstützt das Debuggen von KI-Engine-Konzepten, um Eingabe-/Ausgabedaten zusammen mit der Zeitachse anzuzeigen

- Funktioniert mit aiesimulator

- Unterstützt:

- Datentypen für Fenster/Stream/Kaskadierung

- Paketstreams

- Vorlagenbasierte Kernels

- Dienstprogramm zum Auslesen von Daten

Vitis Analyzer – KI-Engine-Blockadenanalyse

- Vitis Analyzer bietet Visualisierungsfunktionen, mit denen Benutzer die Ursache von Blockaden identifizieren können

- Support

- Performance-Metriken

- Sperr-Blockadenanalyse

- Stream-Blockadenanalyse

- Kaskadierende Blockadenanalyse

- Speicher-Blockadenanalyse

- Unterstützungs-Flow

- aiesimulator

- HW-Emulation

Xilinx Runtime Bibliothek (XRT):

- XRT-API

- Die native XRT-API unterstützt benutzerverwaltete Kernel-Steuerung mit xrt::ip

- XRT-Dienstprogramme

- Die Werkzeuge xbutil und xbmgmt werden jetzt standardmäßig verwendet

- Um die Legacy-Dienstprogramme zu nutzen, müssen Sie xbutil --legacy oder xbmgmt --legacy mit Legacy-Unterbefehlen verwenden

- Neues Dienstprogramm: xball

- Wenden Sie xbutil- oder xbmgmt-Befehle auf alle oder einen gefilterten Teil der installierten Rechenzentrumskarten an. Weitere Informationen finden Sie in xball --help

- Neuer Befehl: xbutil configure

- Hiermit können Sie den PCIe-Hostspeicher- und PCIe-Peer-to-Peer-Funktionen aktivieren, deaktivieren oder konfigurieren. Weitere Einzelheiten finden Sie in der XRT-Dokumentation

- Alle XRT-Dienstprogramme unterstützen jetzt global die Option --force, um die interaktive Benutzerbestätigung zu überspringen

- Die Werkzeuge xbutil und xbmgmt werden jetzt standardmäßig verwendet

- Profilerstellung

- Wenn eine Profilerstellungsoption aktiviert ist, wird ein Profilzusammenfassungsbericht erstellt.

- Alle anwendbaren Übersichtstabellen und Anleitungen werden basierend auf den Profilerstellungsoptionen generiert, die in der Datei xrt.ini aktiviert sind

- Neue Übersichtstabelle für die Datenübertragung für aggregierte Informationen zu einer Speicherressource, wenn Monitore zu Speicherressourcen im Konzept hinzugefügt werden

- Neue AIE-Profilerstellungsmetriken zur Zählung verschiedener AIE-Ereignisse, einschließlich (1) Gleitkommaausnahmen in AIE, (2) Anzahl der Kachel-Ausführungen und (3) Stream-Put- und -Get-Vorgänge

- Embedded

- Verbesserungen im Zocl-Speicher-Manager zur Unterstützung von sptag

Vitis XRT zur Unterstützung mehrerer KI-Engine-Prozesse

- Mit C- und C++-APIs können Zugriffsmodi für mehrere Prozesse definiert werden, um den Zugriff auf dasselbe KI-Engine-Array und dieselben Graphen freizugeben.

- Schutz der KI-Engine-Arrays und Graphen vor unerwünschtem Zugriff.

- Drei Modi werden zum Öffnen von KI-Engine-Arrays und Graphen unterstützt

- Exklusiver Modus (Zugriff auf andere Prozesse verhindern)

- Primärer Modus (andere Prozesse dürfen nur zerstörungsfreien Zugriff erhalten)

- Freigabemodus (nur zerstörungsfreier Zugriff)

- Es sind einige Dinge zu berücksichtigen, wenn Unterstützung mehrerer Prozesse erforderlich ist. Zum Beispiel:

- Andere am Zugriff auf das KI-Engine-Array hindern (exklusiver Zugriff)

- Mehrere Benutzer können verschiedene Graphen separat steuern (Unterstützung mehrerer Anwendungen)

- Ein primärer Benutzer steuert den Graphen, sodass andere Benutzer den Ausführungsstatus prüfen können (primärer und Freigabezugriff).

Vitis XRT für KI-Engine-Unterstützungsstatus

C- und C++-APIs

- C-Versions-API

- Für KI-Engine-Array:

- xrtAIEDeviceOpenExclusive (exklusiver Modus)

- xrtAIEDeviceOpen (primärer Modus)

- xrtAIEDeviceOpenShared (Freigabemodus)

- Für KI-Engine-Graph:

- xrtGraphOpenExclusive (exklusiver Modus)

- xrtGraphOpen (primärer Modus)

- xrtGraphOpenShared (Freigabemodus)

- Für KI-Engine-Array:

- C++-Versions-API

- Zugriffsmodus zur Unterstützung der xrt::aie::device-Klasse im Konstruktor

- enum class access_mode: uint8_t { exclusive = 0, primary = 1, shared = 2 };

- Zugriffsmodus zur Unterstützung der xrt::graph-Klasse im Konstruktor

- enum class access_mode: uint8_t { exclusive = 0, primary = 1, shared = 2, none = 3 };

- Zugriffsmodus zur Unterstützung der xrt::aie::device-Klasse im Konstruktor

- Greifen Sie auf die neuesten Vitis Zielplattformen für Alveo-Karten zu, und machen Sie sich mit dem Abschnitt zu den ersten Schritten mit der Beschleunigerkarte vertraut.

- Vitis herunterladen und Abschnitt zu Alveo-Paketen prüfen

KI-Engine-DSP-Bibliothek – neue Blöcke

- AIE-DDS

- AIE-Mixer

Parallele Kompilierung

- Zeiteinsparung im Vergleich zu 2021.1 (die folgenden Zahlen gelten beispielsweise für die 200-MHz-TX-Kette):

- Kompilierungs- und Simulationszeit um den Faktor 3 verkürzt

- Kompilierungszeiten um den Faktor 7 verkürzt

- Die Totzeit nach der Simulation wurde von 25 Sek. auf ca. 0 Sek. verkürzt

Constraint-Editor-Verbesserungen

- Verbesserte Navigation in 2021.2

Verbesserungen bei Blöcken mit fester Größe

Verbesserungen bei Blöcken mit variabler Größe

Erweiterte Funktionen zur Co-Simulation

- Export von Matlab-Daten für KI-Engine-Eingabe – xmcVitisWrite

- Import von KI-Engine-Daten in Matlab – xmcVitisRead

- Import von KI-Engine-Daten in Matlab – xmcVitisRead

Sonstiges

- Import eines KI-Engine- oder HLS-Kernel-Blocks ohne Eingabedaten (Quellblock)

- Unterstützung für neuen Datentyp

- Native Simulink-Typen int64 und uint64 für die KI-Engine-Entwicklung anstelle der AMD Datentypen x_sfix64 und x_ufix64.

- accfloat und caccfloat für die KI-Engine-Entwicklung

- Unterstützung für Ubuntu 20.04

- Unterstützung für MATLAB 20a, 20b, 21a (keine Unterstützung für MATLAB 21b)

- Neue Beispiele hinzugefügt

- Beispiel für Dual-Stream-SSR-Filter mit 64 Kernels

- Pseudoinverse (64x32) – Beispiel für commslib.

- Verwendung des Befehls xmcLibraryPath zum Verweis auf einen benutzerdefinierten DSPLib-Speicherort.

- Viele weitere Verbesserungen und Fehlerbehebungen

Highlights des Release 2021.1 der Vitis Softwareplattform:

- Unterstützung für AMD Kria System-on-Modules (SOMs) KV260 Vision AI-Starterkit. Der vollständige Vitis Flow für ML (DPU-Inferenz-Engine) + X (RTL-Kernel und Vitis HLS-basierte Computer-Vision-Kernels). Mehr erfahren >

- Unterstützung für neue C/C++ Vision, DSP, Graph (Louvain-Modularität), Codec in der Bildverarbeitung, Komprimierung (GZIP, Facebook ZSTD, ZLIB-Beschleunigung der gesamten Anwendung), Performance-optimierte Bibliotheken auf FPGA und/oder Versal ACAP über CPU/GPUs

- Erweiterter Design-Flow für Vitis™ Core-Entwicklungskits auf Versal ACAP-Chips: verbesserte Visualisierung von Traceberichten für KI-Engine-Konzepte, KI-Engine-Ereignisverfolgung über GMIO, inkrementelle Neukompilierung, Assistent für neue Boot-Images und Unterstützung verschlüsselter KI-Engine-Quelldateien

- Das neue Vitis Model Composer-Tool ermöglicht eine rasche Konzeptuntersuchung und -verifizierung innerhalb der MathWorks MATLAB- und Simulink®-Umgebung. Es ermöglicht die Co-Simulation von Blöcken, die auf KI-Engines und programmierbare Logik ausgerichtet sind, Codegenerierung und Erstellung von Testbenches.

- Neue Vitis HLS Flow Navigator-GUI für schnellen Zugriff auf Flow-Phasen und Berichte. Zusammenführung von Synthese-, Analyse- und Debug-Ansichten in einen allgemeinen Standardkontext

Neues bei Vitis nach Kategorie

Erweitern Sie die folgenden Abschnitte, um mehr über die neuen Funktionen und Verbesserungen in Release 2021.1 der AMD Vitis Softwareplattform zu erfahren. Informationen zu unterstützten Plattformen, verändertem Verhalten und bekannten Problemen finden Sie in den Versionshinweisen zu Release 2021.1 der Vitis Softwareplattform für den Flow zur Anwendungsbeschleunigung und den Flow für die Entwicklung von Embedded Software.

Hinweis: Vitis Accelerated Libraries sind als separater Download verfügbar. Sie können von GitHub oder direkt aus der Vitis IDE heruntergeladen werden.

AIE-DSP

- DSPLib wurde als Teil der Vitis Accelerated Libraries auf GitHub veröffentlicht

- DSPLib enthält allgemeine parametrisierbare DSP-Funktionen, die in vielen fortschrittlichen Signalverarbeitungsanwendungen zum Einsatz kommen. Alle Funktionen unterstützen derzeit Fensterschnittstellen mit Streaming-Schnittstelle.

FIR-Filter

Funktion |

Namespace |

Einzelrate, asymmetrisch |

dsplib::fir::sr_asym::fir_sr_asym_graph |

Einzelrate, symmetrisch |

dsplib::fir::sr_sym::fir_sr_sym_graph |

Interpolation, asymmetrisch |

dsplib::fir::interpolate_asym::fir_interpolate_asym_graph |

Dezimierung, Halbband |

dsplib::fir::decimate_hb::fir_decimate_hb_graph |

Interpolation, Halbband |

dsplib::fir::interpolate_hb::fir_interpolate_hb_graph |

Dezimierung, asymmetrisch |

dsplib::fir::decimate_asym::fir_decimate_asym_graph |

Interpolation, fraktional, asymmetrisch |

dsplib::fir::interpolate_fract_asym:: fir_interpolate_fract_asym_graph |

Dezimierung, symmetrisch |

dsplib::fir::decimate_sym::fir_decimate_sym_graph |

FFT/iFFT – die DSPLib enthält eine FFT/iFFT-Lösung. Hierbei handelt es sich um eine Einzelkanal-Implementierung mit Decimation in Time (DIT) und einem einzelnen Kernel sowie mit konfigurierbarer Punktgröße, komplexen Datentypen, Kaskadenlänge und FFT/iFFT-Funktion.

Funktion |

Namespace |

Einzelkanal-FFT/iFFT |

dsplib::fft::fft_ifft_dit_1ch_graph |

Matrixmultiplikation (GEMM) – die DSPLib enthält eine Lösung zur Matrixmultiplikation/GEMM (General Matrix Multiply). Sie bietet Unterstützung für die Matrixmultiplikation von 2 Matrizen A und B mit konfigurierbaren Eingabedatentypen, was zu einem abgeleiteten Ausgabedatentyp führt.

Funktion |

Namespace |

Matrixmultiplikation/GEMM |

dsplib::blas::matrix_mult::matrix_mult_graph |

Widget-Dienstprogramme – diese Widgets unterstützen die Konvertierung zwischen Fenster und Streams bei der Eingabe in die DSPLib-Funktion sowie zwischen Streams und Fenstern bei der Ausgabe der DSPLib-Funktion, wo gewünscht. Außerdem wird ein zusätzliches Widget zur Konvertierung zwischen realen und komplexen Datentypen bereitgestellt.

Funktion |

Namespace |

Stream zu Fenster/Fenster zu Stream |

dsplib::widget::api_cast::widget_api_cast_graph |

Real zu komplex/komplex zu real |

dsplib:widget::real2complex::widget_real2complex_graph |

DSP-Bibliotheksfunktionen werden in Vitis Model Composer unterstützt, sodass Benutzer diese Funktionen problemlos in die Matlab/Simulink-Umgebung integrieren können. Dies vereinfacht die Evaluierung der KI-Engine-DSP-Bibliothek und die allgemeine Entwicklung von ADF-Graphen der KI-Engine.

Dieses Release der Vitis HPC-Bibliothek führt HLS-Primitive, vordefinierte Kernels und Software-APIs für HPC-Anwendungen auf FPGAs ein. Anwendungen:

Akustische 2D-RTM (Reverse Time Migration), FDTD-Algorithmus (Finite Difference Time Domain), einschließlich Forward Kernel und Backward Kernel

Akustische 3D-RTM (Reverse Time Migration) FDTD-Algorithmus (Finite Difference Time Domain), einschließlich Forward Kernel

MLP-Komponenten (Multi-Layer Perceptron): Aktivierungsfunktionen und vollständig verbundene Netzwerk-Kernels

PCG-Solver (Preconditioned Conjugate Gradient) für Dense- und Sparse-Matrizen

- Erstes Release ausgewählter Bildverarbeitungsfunktionen für Versal AI Engines:

Verfügbare Funktionen

Filter2D

absdiff

accumulate

accumulate_weighted

addweighted

blobFromImage

colorconversion

convertscaleabs

erode

gaincontrol

gaussian

laplacian

pixelwise_mul

threshold

zero

xfcvDataMovers: Data-Mover-Dienstprogramm zum einfachen Tiling hochauflösender Bilder und zur Übertragung in den lokalen Speicher von KI-Engine-Kernen. Zwei Arten:

- Verwendung des PL-Kernels: höherer Durchsatz auf Kosten zusätzlicher PL-Ressourcen.

- Verwendung von GMIO: geringerer Durchsatz als mit der PL-Kernel-Version, verwendet aber Versal NOC (Network on Chip) und keine PL-Ressourcen.

- Neue Funktionen für programmierbare Logik (PL)

- ISP-Pipeline und -Funktionen:

- Aktualisierung der Nicht-HDR-Pipeline aus 2020.2

- Einige ISP-Parameter können zur Laufzeit geändert werden: Verstärkungsparameter für rote und blaue Kanäle, AWB-Aktivierungs-/Deaktivierungsoption, Gammatabellen für R/G/B, Pixelprozentsatz zur Berechnung von Min./Max. für AWB-Normalisierung.

- Gamma Correction und Farbbereichskonvertierung (RGB2YUYV) wurde Teil der Pipeline.

- Neue HDR-Pipeline in 2021.1: Unterstützung für 2020.2-Pipeline + HDR

- HDR-Zusammenführung für 2 Belichtungen, die Sensoren mit digitaler Überlappung zwischen Kurzbelichtungs-Frame und Langbelichtungs-Frame unterstützt.

- Vier Bayer-Muster unterstützt: RGGB, BGGR, GRBG, GBRB

- HDR-Zusammenführung + ISP-Pipeline mit Laufzeitkonfigurationen, was zu einer RGB-Ausgabe führt.

- Extraktionsfunktion: Die HDR-Extraktionsfunktion ist eine Vorverarbeitungsfunktion, die einen digitalen überlappenden Stream als Eingabe verwendet und 2 Belichtungs-Frames (SEF, LEF) als Ausgabe zurückgibt.

- HDR-Zusammenführung für 2 Belichtungen, die Sensoren mit digitaler Überlappung zwischen Kurzbelichtungs-Frame und Langbelichtungs-Frame unterstützt.

- 3DLUT: Bietet Eingabe-/Ausgabezuordnung zur Steuerung komplexer Farboperatoren wie Farbton, Sättigung und Luminanz.

- CLAHE: Die CLAHE-Methode (Contrast Limited Adaptive Histogram Equalization: kontrastbegrenzte adaptive Histogrammausgleichung) ist eine Methode, die während des adaptiven Histogrammausgleichs den Kontrast begrenzt, damit dieser in nahezu konstanten Bereichen nicht übermäßig verstärkt wird. Dadurch wird auch das Problem der Rauschverstärkung reduziert.

- Aktualisierung der Nicht-HDR-Pipeline aus 2020.2

- Flip: Kippt das Bild entlang der horizontalen und vertikalen Linie.