- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

- 2020.2

- 2020.1

AMD Vitis™ 軟體平台 2025.2 版本重點

增強 Versal™ AI Engine 的設計流程

- 增強 Versal AI Edge 與第 2 代 Versal AI Edge 系列(AIE-ML 與 AIE-ML v2)的 AI 引擎 API

- 新增並增強資料類型

- 新增:區塊浮點 MX6

- 新增:區塊浮點 MX4

- 新增:cbfloat16(模擬)

- 增強:cfloat 和 cbfloat16(適用於 FFT 與矩陣乘法函數)

- 增強:cint16 和 cint32(現在可在 FFT 使用 cint16 轉動係數類型)

- 新增並增強資料類型

- 程式設計模型更新

- 建立唯讀的共用緩衝區

- 重複的 MEM 磚讀取存取(AIE-ML 與 AIE-ML v2)

- AIE-ML 與 AIE-ML v2 現在支援 DMA-FIFO

- 雙緩衝區可以跨越兩個相鄰的 MEM 磚

(AIE-ML 與 AIE-ML v2) - 本地磚記憶體共用參數

- 增強 AIE-ML 與 AIE-ML v2 的封包交換功能

- 新增並增強適用於 Versal AI Engine 的 DSP 程式庫函數

- 新增累積總和

- 新增歐氏距離

- 新增函數逼近(透過 RTP 更新或 LUT 呼叫)

- 以封包交換增強 TDM FIR(節省 PLIO)

- 增強使用 AI Engine + PL 的 1D FFT(減少所需 PL 資源)

- 增強 FIR(輸送量最佳化)

- 改善 AI 引擎對映工具與路由器 - 編譯器將探索各種佔用空間/佈局,以提供更有效率的實作

更簡易的 Versal AI Engine 設計驗證

- 更新 Vitis 功能模擬工作流程,使其支援 C++(搶先體驗)

- 提供採用 MATLAB® 與 Python™ 測試平台的硬體迴路測試法(搶先體驗)

針對 AIE DSP 設計強化 Vitis 模型編輯器的功能

- 針對 AI 引擎超取樣率 (SSR) 設計流程的易用性更新(搶先體驗)

- 新增其他同時適用於 AI 引擎及 HDL 的區塊:

- AIE、AIE-ML、AIE-ML v2

- 新增:函數逼近

- 新增:相關性/卷積

- 新增:累積總和

- HDL 程式庫區塊

- 增強:FFT(新增原生浮點 SSR = 32、64)

- 增強:FIR(以 SSR 支援分數比率插補)

- AIE、AIE-ML、AIE-ML v2

適用於嵌入式開發的 Vitis IDE 更新

- 用來更新建構組態的 Python™ API

- 可在 Python 環境中執行 Vitis™ API

- 支援的核心預設顯示 PS Trace

- 增強除錯功能 – 更新的值現在會在「監看」視景和「暫存器」視景中醒目顯示

- 支援取消或終止後端工作

- 統一平台 BSP 檔案路徑(Linux 和 Windows)

- Theia AI 整合(搶先體驗)– 提供基礎架構,讓開發人員可以使用其偏好的 LLM 和程式碼助理

- 支援以 Python API 建立 DFX 平台

- 備份或共用工作空間

- 增強設定檔的記錄功能

- 新增「整合專案」元件

按類別列出 Vitis 的最新功能

展開以下部分,瞭解更多有關 AMD Vitis 軟體平台 2025.2 新功能和增強功能的資訊。如需支援平台、行為變更與已知問題的更多資訊,請參閱 Vitis 軟體平台 2025.2 發行說明,以瞭解應用程式加速流程及嵌入式軟體開發流程。

增強 DSP 程式庫函數:

- 新增累積總和

- 新增歐氏距離

- 新增函數逼近(透過 RTP 更新 LUT 呼叫)

- 以封包交換增強 TDM FIR(節省 PLIO)

- 增強使用 AIE + PL 的 1D FFT(減少所需 PL 資源)

- 增強 FIR(輸送量最佳化)

適用於:

- 具備 AIE 的 Versal™ AI Core

- 具備 AIE-ML 的 Versal AI Edge

- 具備 AIE-ML v2 的第 2 代 Versal AI Edge 系列

- 以 C++ 進行 Vitis 子系統的功能模擬(搶先體驗)

- 強化 Vitis Analyzer 對於延遲測量及輸送量測量的支援性 – 適用於 AI 引擎設計

- 獨立 AIE 分區的執行階段控制

- 針對 AI Engine 超取樣率 (SSR) 之設計流程的易用性更新(搶先體驗)

- 新增其他同時適用於 AI 引擎及 HDL 的區塊:

- AIE、AIE-ML、AIE-ML v2

- 新增:函數逼近

- 新增:關聯性/卷積

- 新增:累積總和

- HDL 程式庫區塊

- 增強:FFT(新增原生浮點 SSR = 32、64)

- 增強:FIR(以 SSR 支援分數比率插補)

- 效能標註增強功能

- 效能標註現在將根據 CSIM 計算的行程計數進行最佳化

- 效能標註最佳化可在組態檔中轉換為指示

- 條件式控制標註,包括效能標註

- 新 IP 支援

- 提供適用於 FIR 和 FFT 的分數取樣率 SSR。就 FFT 而言,使用 SPFP32 時的 SSR 現在最高可支援到 SSR=64。

- 針對以區塊 RAM 或 UltraRAM 實作的資料流緩衝區,新增對 ECC 的支援

- 易於使用的功能

- CSIM 與 CoSim 支援自動重新啟動

- 提供適用於 M-AXI 的多連接埠快取

- 針對具有邊帶訊號的 AXI 串流新增新的 API

AMD Vitis™ 軟體平台 2025.1 版本重點

增強 Versal AI Engine 的設計流程

- 新增或強化 DSP 程式庫函數、AI 引擎 API,以及對新資料類型的支援

具備 AIE 的 Versal AI Core 系列:

- 針對使用 2D 平行 AIE + 可程式化邏輯 (PL) 架構的 AI 引擎,增強其 GEMV 與 FFT 功能(適合多相通道分離器)

- 向量化 Bitonic SIMD 排序、關聯性、卷積

具備 AIE-ML 的Versal AI Edge 系列:

- 針對使用 2D 平行 AIE-ML + PL 架構之 AIE-ML 提供 FFT 支援(適合多相通道分離器)

- 向量化 Bitonic SIMD 排序、關聯性、卷積

具備 AIE-ML v2 的第 2 代 Versal AI Edge 系列:

- 2D FFT AIE-ML v2 + PL v1(適合多相通道分離器)

- TDM FIR(適合多相通道分離器)

- GEMM/GEMV

- 單取樣率 FIR

- 半頻帶 FIR

- 分數重新取樣器 FIR

- 取樣率改變 FIR

- FFT/iFFT

- DFT

- DDS 混頻器

- 函數逼近

AI 引擎程式設計更新:

- 本地記憶體的分塊參數規格

- 減少變更測試平台時所所需要的編譯時間

- 加速在 AIE-ML 使用 DDR 雙緩衝區的設計管道化

- AIE-ML 中的其他記憶體存取增強功能

更簡易的 Versal AI Engine 設計驗證

- 支援在 MATLAB® 與 Python™ 中進行 Vitis 子系統的功能模擬

- 強化 Vitis Analyzer 對於延遲測量及輸送量測量的支援性 – 適用於 AI 引擎設計

- 獨立 AIE 分區的執行階段控制

針對 AIE DSP 設計強化 Vitis 模型編輯器的功能

- 支援多個頂層 AI 引擎子系統

- 新增其他同時適用於 AIE 及 HDL 的區塊,包括含有額外 SSR 模式的增強型 FFT和可減少使用 DSP58 資源之 Complex Multiplier

適用於嵌入式開發的 Vitis IDE 更新

- Vitis 統一 IDE(新 GUI)將為預設環境 - 傳統 Vitis IDE 已棄用

- 第三方工具鏈支援,例如 GCC 和 ARMClang

- 現在可透過 Vitis IDE 內的市集公用程式來安裝與存取第三方生產力工具

按類別列出 Vitis 的最新功能

展開以下部分,瞭解更多有關 AMD Vitis 軟體平台 2025.1 新功能和增強功能的資訊。如需支援平台、行為變更與已知問題的更多資訊,請參閱 Vitis 軟體平台 2025.1 發行說明,以瞭解應用程式加速流程及嵌入式軟體開發流程。

具備 AIE 的 Versal AI Core 系列:

- 針對使用 2D 平行 AIE + 可程式化邏輯 (PL) 架構的 AI 引擎,增強其 GEMV 與 FFT 功能(適合多相通道分離器)

- 向量化 Bitonic SIMD 排序、關聯性、卷積

具備 AIE-ML 的 Versal AI Edge 系列:

- 針對使用 2D 平行 AIE-ML + PL 架構之 AIE-ML 提供 FFT 支援(適合多相通道分離器)

- 向量化 Bitonic SIMD 排序、關聯性、卷積

具備 AIE-ML v2 的第 2 代 Versal AI Edge 系列

- 2D FFT AIE-ML v2 + PL v1(適合多相通道分離器)

- TDM FIR(適合多相通道分離器)

- GEMM/GEMV

- 單取樣率 FIR

- 半頻帶 FIR

- 分數重新取樣器 FIR

- 取樣率改變 FIR

- FFT/iFFT

- DFT

- DDS 混頻器

- 函數逼近

- 支援在 MATLAB® 與 Python™ 中進行 Vitis 子系統的功能模擬

- 強化 Vitis Analyzer 對於延遲測量及輸送量測量的支援性 – 適用於 AI 引擎設計

- 獨立 AIE 分區的執行階段控制

支援多個頂層 AI 引擎子系統

新增其他同時適用於 AI 引擎及 HDL 的區塊

AI 引擎

- Bitonic 排序(Versal AI Core 系列、Versal AI Edge 系列、第 2 代 Versal AI Edge 系列)

- DFT/FFT(第 2 代 Versal AI Edge 系列)

- FIR – 單取樣率、半頻帶、取樣率改變、分數重新取樣器(第 2 代 Versal AI Edge 系列)

- DDS/混頻器(第 2 代 Versal AI Edge 系列)

HDL 程式庫

- 增強型 FFT – 額外 SSR 模式

- SSR 8、16、32、64(原生浮點)

- SSR 2、4(固定點)

- 增強複數乘法器 – 減少使用 DSP58 資源

- 新增對 CFLOAT MAC 的支援

- 向量 IFFT 浮點 – 新區塊

- 從 R2025a 版的 MATLAB (.m) 設計產生 Vitis HLS 易於解讀的 C++ 程式碼

- 全新 Vitis HLS 易用性功能

- 模擬會在執行期間變動之線路輸入與 AXI Lite 輸入(直接 I/O)

- 適用於頂層 HLS 設計的效能標註(開放搶先體驗功能)

- 透過專屬內在函數庫支援 Versal 複數成法器

- Vitis HLS GUI 改善

- 透過 Clang 16 對 C++17 提供初期支援

AMD Vitis™ 軟體平台 2024.2 版本重點:

針對 AMD Versal AI Engine DSP 設計的增強功能

- 使用 Vitis Analyzer 預估延遲與輸送量

- 使用 Vitis Analyzer 標記無法利用的 PLIO

- 快速建立 AMD Versal™ AI 引擎的設計原型

- 堆疊、堆積和程式記憶體報告

適用 Versal AI Engine 的全新增強 Vitis 程式庫功能

- 適用於 AIE 的增強 DSP 程式庫功能(在 Versal AI Core、Versal Premium 系列提供)

- 強化分時多工 (Time Division Multiplexed, TDM) 有限脈衝響應 (finite impulse response, FIR) 濾波器功能效能

- 推出下列運算的更高效能版本

- 一般矩陣向量 (GEMV)

- 一般矩陣乘法 (GEMM)

- 2D IFFT - AIE + PL 分區以獲得更高效能

- 適用於 AIE-ML 的全新 DSP 程式庫功能(在 Versal AI Edge 提供)

- 強化 TDM FIR 濾波器功能效能

- 支援 Radix-3/Radix-5 FFT

- GEMV

- GEMM

Vitis IDE 提供全新易用的功能(新 GUI)

- 新的序列終端台:監測來自硬體的序列訊息

- 安裝和探索第三方延伸模組

- PS Trace - 用於除錯和最佳化嵌入式系統效能的功能

針對 AIE DSP 設計強化 Vitis 模型編輯器的功能

- AI 引擎 DSP 程式庫更新

- AIE(適用於 Versal AI Core 和 Versal Premium 系列)

- 混合 Radix FFT

- Stockham FFT 效能增強

- TDM 有限脈衝響應 (finite impulse response, FIR)

- AIE-ML(適用於 Versal AI Edge 系列)

- TDM 有限脈衝響應 (finite impulse response, FIR)

- 直接數位合成 (Direct Digital Synthesis, DDS)(用於波型生成)

- 混頻器(用於變更頻率)

- AIE-MLv2(適用於第 2 代 Versal AI Edge 系列)

- FIR

- DFT

- DDS

- 混頻器

- AIE(適用於 Versal AI Core 和 Versal Premium 系列)

- Vitis 模型編輯器的新增資料類型

- 支援 cbfloat16

- 支援新的串聯訊號資料類型

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- 將 AIE/HLS 內核設計從 Vitis 模型編輯器以 Vitis 子系統 (VSS) 之形式匯出到 Vitis

- 使用 Vitis 除錯器為在 Vitis 模型編輯器中建立的 AIE/HLS 內核進行除錯

- Vitis 模型編輯器中的 HDL 區塊組更新

- Vitis 模型編輯器的其他增強功能

- 改善代碼生成的回應時間

- 任何設計只會執行一次模擬

- 將中控台區塊配置另存為 JSON 檔案(利於快速原型設計或批次處理)

- 新增 MATLAB R2024a 支援

- 新增 Red Hat Enterprise Linux (RHEL) 8.10、9.4 支援

- 改善代碼生成的回應時間

- 以設計規則檢查 (DRC) 取代設計考量

適用於 AIE 的增強 DSP 程式庫功能(在 Versal AI Core、Versal Premium 系列提供)

- 強化分時多工 (TDM) 有限脈衝響應 (FIR) 濾波器功能效能

- 推出下列運算的更高效能版本

- GEMV(一般矩陣向量)

- GEMM(一般矩陣乘法)

- 2D IFFT - AIE + PL 分區以獲得更高效能

適用於 AIE-ML 的全新 DSP 程式庫功能(在 Versal AI Edge 提供)

- 強化分時多工 (TDM) 有限脈衝響應 (FIR) 濾波器功能效能

- 支援 Radix-3/Radix-5 FFT

- GEMV(一般矩陣向量)

- GEMM(一般矩陣乘法)

- 使用 Vitis Analyzer 預估延遲與輸送量

- 使用 Vitis Analyzer 標示哪些 PLIO 不可用

- AI 引擎 DSP 程式庫更新

- AIE(適用於 Versal AI Core、Versal Premium 系列)

- 混合 Radix FFT

- Stockham FFT 效能增強

- TDM 有限脈衝響應 (finite impulse response, FIR)

- AIE-ML(適用於 Versal AI Edge 系列)

- TDM 有限脈衝響應 (finite impulse response, FIR)

- DDS(直接數位合成,用於產生波形)

- 混頻器(用於變更頻率)

- AIE-MLv2(適用於第 2 代 Versal AI Edge 系列)

- FIR

- DFT

- DDS

- 混頻器

- AIE(適用於 Versal AI Core、Versal Premium 系列)

- Vitis 模型編輯器的新增資料類型

- 支援 cbfloat16

- 支援新的串聯訊號資料類型

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- 將 AIE/HLS 內核設計從 Vitis 模型編輯器以 VSS(Vitis 子系統)之形式匯出到 Vitis

- 使用 Vitis 除錯器為在 Vitis 模型編輯器中建立的 AIE/HLS 內核進行除錯

- Vitis 模型編輯器中的 HDL 區塊組更新

- Vitis 模型編輯器的其他增強功能

- 改善代碼生成的回應時間

- 任何設計只會執行一次模擬

- 將中控台區塊配置另存為 JSON 檔案(利於快速原型設計或批次處理)

- 新增 MATLAB R2024a 支援

- 新增 Red Hat Enterprise Linux (RHEL) 8.10、9.4 支援

- 以設計規則檢查 (DRC) 取代設計考量

- 模擬會在執行期間變動的純量/線路輸入(直接 I/O)

- 支援任意精度浮點類型

- 將 HLS 程式碼對映至 DSP 區塊

- 使用者決定程式碼的執行順序

- HLS 除錯器以清晰易懂的方式顯示資料類型(使用 GNU 除錯器的 pretty print 技術)

AMD Vitis™ 軟體平台 2024.1 版本重點:

針對 AMD Versal™ AI 引擎 DSP 設計的增強功能

- 針對 AMD Versal AI Core 系列強化 DSP 程式庫功能

- 適用於 SSR > 1 的分時多工 (TDM) FIR 濾波器功能

- 搭配 32 位元轉動係數的 FFT

- 混合 Radix 3 和混合 Radix 5 FFT

- Kronecker 矩陣積

- 基於 Householder 的 QRD 求解器,以改善穩定性

- DFT,適用於 SSR > 1 的情況

- 全新 DSP 程式庫功能,適用於執行 AIE-ML 的 AMD Versal AI Edge 系列

- 支援 SSR 的一般矩陣向量 (GEMV)

- 支援 SSR 的一般矩陣乘法 (GEMM)

- AIE API 增強功能

- 支援 Radix-3/Radix-5 FFT

- AIE 模擬器增強功能

- 針對與 PL 互動的 AI 引擎設計,提供週期近似模擬功能,無需透過控制、介面與處理系統 (CIPS) IP 核心

- AMD Vitis Analyzer 支援使用第三方模擬器進行硬體模擬,例如 VCS、Questa、Xcelium 和 Riviera

Vitis 統一軟體平台的關鍵改良

- 支援新器件:AMD Versal™ Premium VP1902 自適應 SoC、AMD MicroBlaze™ V 處理器

- 強化用於 Windows® 環境的嵌入式應用程式開發與板卡支援套件 (Board Support Package, BSP) 生成功能

- 針對外部編譯的嵌入式應用程式,提供使用者管理的除錯流程

- 全新 Bootgen GUI

- 支援平台專案漸進式建構

AMD Vitis IDE 的關鍵改良(新 GUI)

- 新增處理子系統的階層式除錯支援

- 新增專案/工作空間匯出和匯入功能支援

- 新增 Python 直譯器和 API 支援

- 全新功能預覽頁面

- 嵌入式、AIE 和平台專案的全新檔案異動通知

針對 AMD Versal AI Core 系列強化 DSP 程式庫功能

- 適用於 SSR > 1 的分時多工 (TDM) FIR 濾波器功能

- 搭配 32 位元轉動係數的 FFT

- 混合 Radix 3 和混合 Radix 5 FFT

- Kronecker 矩陣積

- 基於 Householder 的 QRD 求解器,以改善穩定性

- DFT,適用於 SSR > 1 的情況

全新 DSP 程式庫功能,適用於執行 AIE-ML 的 AMD Versal AI Edge 系列

- 支援 SSR 的一般矩陣向量 (GEMV)

- 支援 SSR 的一般矩陣乘法 (GEMM)

AIE API 增強功能

支援 Radix-3/Radix-5 FFT

AI 引擎模擬器增強功能

- 針對與 PL 互動的 AI 引擎設計,提供週期近似模擬功能,無需透過 CIPS(控制、介面與處理系統 IP 核心)。

- Vitis Analyzer 支援使用第三方模擬器進行硬體模擬,例如 VCS、Questa、Xcelium 和 Riviera

- 從 Vitis Analyzer 將表格匯出為 CSV 格式

- AMD Vitis 模型編輯器中針對 AIE 和 AIE-ML 的全新 DSP 函數支援

- 分時多工 (Time Division Multiplexed, TDM) FIR 濾波器函數

- 用於建構 1 GSPS 及更高輸送量的多相通道分離器

- DFT/IDFT - 支援 SSR

- 最佳化轉換,在較小尺寸上實現輸送量/延遲

- FFT/IFFT - 擴展至支援 CINT32 位元轉動係數

- 混合 Radix FFT/IFFT - 支援 AIE-ML

- 提升模型編輯器中控台區塊易用性

- 強化硬體驗證流程

- 2024.1 版新增的 OS 和 MATLAB® 版本支援

- RHEL 9

- MATLAB R2023a 和 R2023b

Github 提供新範例設計。

全新模板標註,簡化影像和視訊濾波器的 HLS C++ 程式碼

全新程式庫函數精靈,運用 AMD Vitis 程式庫的 GitHub 儲存庫

- 為 AMD Vivado 設計工具建立「求解器」和「視覺」(相容於 OpenCV)IP

- 執行可用的程式庫範例

記憶體介面標註 (ap_memory) 現在可將連接埠群組化,以利在 AMD Vivado IP Integrator 的運用

全新 HLS 元件比較功能,可並排顯示 2 個以上元件的指標

支援以使用者供應商提供的 RTL 程式碼取代 C++ 函數(黑箱流程)

代碼分析器現在可解構 C++ 結構的成員,藉此微調效能分析

全新使用者控制項,用於控制 HLS 全域 FSM 編碼,並可選擇安全狀態

支援在 C 模擬期間存取 Clang 檢測工具,以執行位址與初始化檢查

Vitis™ 軟體平台 2023.2 版本重點:

針對 Versal™ AI 引擎 DSP 設計的增強功能

- 全新 DSP 程式庫功能

- 為 DSP 功能提供全新 API 支援

- AI 引擎編譯器和模擬器的新功能

全新獨立 Vitis 嵌入式軟體

- 小型獨立安裝程式,適合為 Arm® 嵌入式子系統編寫 C 程式碼的設計人員使用

- 提供所有嵌入式功能,包括 Bootgen 和 XSCT 等公用程式

全新 Vitis 統一整合設計環境

- 在所有 Vitis 工作流程提供一致的 GUI 和 CLI

- 採用新一代 Eclipse Theia GUI,提供更高靈活度和易用性功能,工作效率獲得提升

適用於 AI 引擎的全新 DSP 程式庫功能

- 混合 Radix FFT

- 離散傅立葉轉換 (DFT)

- 一般矩陣向量乘法 (GEMV)

為 DSP 功能提供全新 API 支援

- FFT IP,支援 cint32 轉動係數資料類型

- 支援用於 Radix-4 FFT API 的 cint16

- 在 API 實作的向量化「fix2flt」和「flt2fix」

為 AIE-ML 提供全新 API 支援

- API 現在支援於 sliding_mul() 函數中,使用 int32/cint32 資料類型

- API 現在支援於 sliding_mul() 函數中,使用 <float> 資料類型

- 提供支援稀疏矩陣乘法所需之所有 AIE API 程式

主要元件更新:

- U-boot 2024.1

- Arm Trusted Firmware 2.10

- Linux Kernel 6.6_LTS

- Qemu 8.1

- Xen 4.18

- OpenAMP 2023.10

淘汰 BSP:

- AMD Microblaze™:VCU118、KCU105、KC705、AC701

- Zynq:ZC706

- AMD Versal™:VMK180-EMMC、VMK180-OSPI

- Zynq MP:ZCU111

新 BSP (XSCT):

- VEK280 投產級 BSP,搭配全新 ETH Phy

新系統裝置樹流程 (SDT) BSP:

- ZCU102、ZCU104、ZCU105、ZCU216

- ZCU208、ZCU208-sdfec、ZCU670

- VCK190

- VMK180

- VPK120

- VPK180

- VEK280

- AIE 編譯器現在支援作為輸入或輸出的 2D 和 3D 陣列

- Vitis Analyzer 現在會產生指引報告,以調整先進先出 (First-In First-Out, FIFO) 的容量

- 新增多執行緒模擬器內核支援,並加速 Value Change Dump (VCD) 分析器

- 支援向外介接至 MATLAB® 環境與 Python 流量生成器

- 增強 AXI Stream 模型,支援 PLIO 對齊的空白/等待週期

- 增強設計規則檢查

- 支援透過高速除錯卸載 AI 引擎追蹤資料

- 支援在 Vitis 環境中進行晶片上網路 (Network on Chip, NoC) 和硬體 DDRMC 分析

- Vitis 工具現在支援 VEK280 和 Alveo™ V70 AI 推論加速卡的 AIE-ML 追蹤

- AI 引擎區塊更新

- 支援匯入 AIE-ML 圖形,作為 Vitis 模型編輯器的區塊

- 為 Vitis 模型編輯器中的 AIE 和 AIE-ML 實作,提供全新 DSPlib 函數

- 支援在 Simulink® 工具內繪製 AIE 模擬器的內部訊號輸出結果

- HLS 內核區塊更新

- 自動產生測試平台

- 擴大 HLS 內核區塊的資料類型支援

- 整合 Vitis 模型編輯器和 Vitis 工具

- 直接從 Vitis 模型編輯器產生 .xo 和 libadf.a 檔案

- 其他增強功能

- 支援 MATLAB® 工具版本:R2021a、R2021b Update 6、R2022a Update 6、R2022b

- 為硬體驗證流程新增其他拓撲法支援

- GitHub 提供新範例文件

- 適用於 HLS 元件的全新 Vitis 統一 IDE

- 全新 Vitis HLS 授權要求

- 全新代碼分析器功能,可在執行 C 語言合成前,取得效能評估

- 增強 AXI 介面功能:

- 支援 HLS AXI 串流側通道

- 支援使用者可設定的 AXI 主快取

- 其他增強功能:

- 全新程式碼複雜性報告,用於在 C 語言合成過程中,識別設計大小問題

- 改善編譯時間:相較於 2023.1 版,2023.2 版的平均編譯時間提升了 20%1

Vitis 軟體平台 2023.1 版本重點:

適用於 Versal™ AI 引擎 (AIE) 陣列的全新 Vitis™ 程式庫功能

- DSP 程式庫功能 - 更多 FIR 濾波器配置

- 求解器程式庫函數 - 增強功能以提升效能

增強 Versal AI Core 和 AI Edge 系列設計流程

- AIE 編譯器支援作為輸入或輸出的 2D 和 3D 陣列

- AIE 模擬器指引支援調整 FIFO 大小,以避免產生死結

- 增強 AIE 狀態報告功能

- 為 Vitis Analyzer 提供全新預設 GUI

支援從 Vitis 環境匯出至 Vivado™ 環境

- 讓 Vitis 和 Vivado 工具開發團隊,能透過通用介面檢查點並行工作

DSP 程式庫 - FIR 濾波器

- 增強分數重新取樣器 FIR、單取樣率 FIR、半頻帶 FIR 和取樣率改變 FIR,以支援係數位元寬度大於資料位元寬度的情況

- 分數重新取樣器 FIR 亦支援使用多重 AIE 磚執行 SSR 操作,並納入係數重新載入功能

求解器函數庫

- 透過高效能串流設計(約 300 個磚)增強 API 效能

- 針對 4D 資料移動器函數,新增 QR 和 Cholesky 分解法支援,協助從 AIE 陣列讀取或寫入資料

- AIE 編譯器除了 1D 以外,現在還支援作為輸入或輸出的 2D 和 3D 陣列

- AIE 編譯器支援圖形內圖形結構(子圖)和條件式連接埠結構。

- 全新 AIE CINT-轉-CFLOAT 資料轉換 API。

- 增強 AIE 狀態報告功能,使 AIE 狀態報告納入與設計中的 AIE-ML 磚、AIE 磚、事件,以及磚上其他暫存器相關的資訊。

- 支援透過高速差分對 (HSDP),卸載 AIE 事件追蹤資料,而不是將其儲存在 Versal 器件記憶體。

- 支援在 Vitis 環境進行晶片上網路 (Network on Chip, NoC) 和硬體 DDR MC 分析。

- 支援鎖定特定範圍的 AIE 事件追蹤,以利檢查應用程式的特定部分。

- 提供 FIFO 容量調整指引以避免死結。

- 支援選取 AIE 模擬器所報告的節點,以降低模擬器 VCD 檔案的大小且加速模擬。

- AIE 模擬器現在會產生報告(可在 Vitis Analyzer 檢視),顯示哪些 AIE 發生記憶體存取違規,以及這些違規如何與 Graph C 程式碼的行數相對應。

- 追蹤檢視資料視覺化功能,現在也支援 AIE-ML 陣列。

- 針對 Versal AI Engine 的 FIR 濾波器配置新增資料類型支援

- 新增兩個針對 Versal 自適應 SoC 的 DSP58 最佳化的浮點函數

- 加快 Versal AI Engine 所有 Vitis 模型編輯器程式庫函數的回應速度

- 其他增強功能:

- 增強 HLS 內核區塊

- 增強 Vitis 模型編輯器中控台

- 支援 MATLAB 工具版本 R2021a、R2021b 和 R2022a

- 效能提升2:相較於 2022.2 版,2023.1 版的平均延遲時間減少了 5.2%

- 提供在 Vitis HLS 工具中輕鬆下載、檢視和實例化 L1 程式庫函數的方式

- 增強 Vitis HLS工具對於 AXI 交易和叢發報告的支援性

Vitis 軟體平台 2022.2 版本重點:

適用於 Versal™ AI 引擎 (AIE) 陣列的全新 Vitis™ 程式庫功能

- DSP 程式庫函數 – 增強功能

- 求解器程式庫函數

- 視覺程式庫函數

- 超音波程式庫函數

增強 Versal AI Core 和 AI Edge 系列設計流程

- 控制內核在 AI 引擎陣列中的相對位置 - 更高效能,使用率更優異

- AIE x86 模擬器增強功能 - 改善 x86 模擬器死結條件建模

- AIE API 增強功能 - 新增 Radix 3/5 FFT 和矩陣「x」向量 API

- 增強 Versal 設計的分析與除錯功能 - 死結偵測、更大量的追蹤資料收集、RTL/Python 測試平台支援

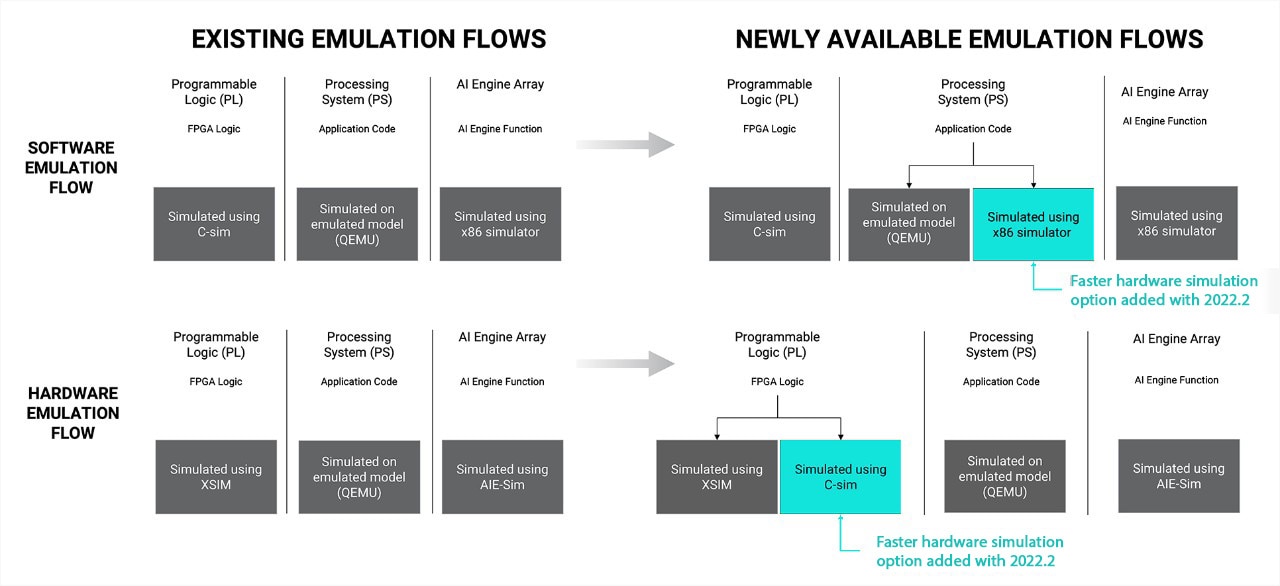

- 為 Vitis 的異構設計提供全新模擬選項

DSP 程式庫功能

- AI 引擎上的超取樣率 (SSR) FIR 濾波器實作,現在支援係數重新載入功能和動態點尺寸

- 針對 AI 引擎陣列的 FFT 函數新增 FFT 分窗元素

求解器程式庫函數

- 正交旋轉 (QR) 分解

- Cholesky 分解

視覺程式庫函數

- 針對 AI 引擎陣列提供四種新的視訊函數

超音波程式庫函數

- 新增多種函數,協助建構醫療超音波設計

- 支援使用者新增限制,以控制內核在 AI 引擎陣列中的相對位置,讓使用者獲得更高效能,使用率更優異

- 改善 x86 模擬器中的 AIE 死結條件建模

- 新增 AIE API - 追加 Radix 3/5 FFT 和矩陣「x」向量 API

- 支援在硬體模擬中產生 AI 引擎分析報告

- 針對以 AI 引擎和 PL 為核心的設計,新增使用 XSDB(AMD 系統除錯器)進行死結偵測的功能

- 支援以賽靈思執行階段套件 (XRT) 控制,持續透過 PLIO 卸載 AI 引擎事件追蹤資料

- Versal AI Engine 設計功能

- 支援將圖形限制新增至 AI 引擎 DSP 程式庫區塊設計,取得更優異的使用率與效能

- 新增 AI 引擎設計的週期近似模擬功能

- AI 引擎圖形匯入區塊,會自動偵測執行階段參數 (RTP) 連接埠

- 增強且新增 DSP 程式庫區塊

- 一般功能

- 為使用 PL 和 AIE 陣列的異構系統設計,支援硬體驗證流程

- 更新 Vitis 模型編輯器中控台區塊,以支援異構設計

- 自動偵測有效的 AI 引擎、HDL 和 HLS 子系統

- 針對僅有 HDL 的設計,以及 HDL → AI 引擎 → HDL 的設計,增強 Versal 平台的硬體驗證流程

- 強化「任務層級平行化」編碼風格的支援性

- 提升 C 模擬速度及成果品質

- 新增效能與時序增強功能

- 改善叢發推論

- 自動推論展開、管道、Array_Partition 和內嵌標註,以獲得更好的效能

- 改善時序準確度,實現更優異的時序收斂,並達到更高的時脈頻率

- 其他功能

- 分析和除錯:現在支援在 C 程式碼插入 printf,即使在 RTL 合成後亦可

- 易用性:全新效能標註,自動實現指定交易間隔

- FFT 和 FIR IP 現在支援 HLS::stream 介面

Vitis 軟體平台 2022.1 版本重點:

改善針對 Versal™ ACAP 和 AI 引擎的 Vitis™ 流程

- 支援 AMD 基礎 DFX 平台,含一個靜態區域與一個 DFX 區域

- AIE 分析支援停滯/死結偵測,在 Vitis Analyzer 中產生 AI 引擎狀態(包括錯誤事件)檢視報告

- x86sim、AIEsim 和軟體模擬中的外部流量生成器,不僅靈活度更高,並可輕鬆插入模擬流程

- Vitis 模型編輯器支援硬體驗證、Linux 和硬體模擬

Vitis for DC 和 Vitis HLS

- Vitis 為動態區域產生流程,提供額外的報告支援,並加強流程報告,包含 3 個新報告或更新報告

- Vitis 改善 PL 分析,並可選擇卸載追蹤資料至記憶體資源(偏好),或是 PL 中的 FIFO,以獲得更佳效能

- 支援全新 Timeline Trace Viewer,可在模擬後使用,以顯示執行期間的分析資料,並讓使用者留在 Vitis HLS GUI 內

- Vitis HLS 現在透過全新效能標註或 set_performance_directive,支援更高階層類型的「智慧」架構

- 增強 Vitis 圖形程式庫的 L3 API 效能表現(內核呼叫時間節省了 1 mS)

- 新增基因組學加速器程式庫(L1、L2 和 L3)

- 增強圖形程式庫 L3 功能,以提供更高效能

- Vitis 資料庫程式庫、GQE 多功能內核

- 視覺程式庫增加新函數

- Vitis AIE 視覺程式庫增加新函數/增強功能

- Vitis AIE DSP 程式庫,以 FIR 重新取樣器取代 FIR 分數插值器

- Vitis 編碼程式庫新增 API:API jxlEnc、API「leptonEnc」、API「resize」、API「WebpEnc」

Vitis 資料壓縮庫

- 提升 ZLIB 壓縮功能,為 8KB 解決方案提供客製化八核心壓縮

- 提升 ZLIB 解壓縮功能,針對 8KB 檔案大小提供客製化 IP

- 平台功能查詢改進

- 改善 HBM 易用性,支援為內核 M_AXI 選擇特定的 S_AXI 進入點,支援透過配置檔插入 RAMA

Vitis AI 引擎編譯器

- AI 引擎自動停滯/死結偵測與硬體分析

- 分析自動狀態輸出

- 分析自動狀態輸出 - 緩衝

- 分析硬體的手動狀態輸出

- 分析手動狀態輸出

- 增強 AI 引擎事件追蹤功能

- 外部流量生成器 AIEsim

- 提升硬體上的 AI 引擎分析

- AI 引擎支援廣播分窗

- Vitis AI 引擎編譯器強化圖形程式設計模型

- Vitis AI 引擎編譯器 - ADF 圖中的 PLIO/GMIO

Vitis HLS

- 加強分析功能,全新 Timeline Trace Viewer

- 增強編碼風格,針對「區塊流」類型新增「陣列分區」支援

- 標註抽象化、新效能標註(與指示)

- Vitis Core「one liner」指令、Vitis HLS - 全新 Timeline Trace Viewer、新效能標註、區塊流支援分窗

- 推出新檢視器

- 顯示設計中所有存續函數在執行期間的特性分析資料,也就是成功轉換為模組的那些函數

- 對於在共同模擬後查看資料流區域的行為而言尤其實用。

- Vitis HLS 原生 - 不再需要啟動 xsim 波形檢視器(外部工具)

Vitis Analyzer

- 增進 Vitis Analyzer 的功能,儲存/恢復 Timeline 自訂

- 增強報告功能,report_qor_assessment、xclbin 時脈資訊、Vivado 自動化摘要

- 增強分析功能,引進全新 PL 分析架構,支援透過新增多重 trace_memory 選項以插入多個記憶體監測器(僅限硬體),適用於 v++ 連結器的範例配置檔,可將位於 SLR0 的所有 CU 追蹤資料卸載至 DDR0,同樣將位於 SLR1 的所有 CU 追蹤資料卸載至 DDR1

Vitis IDE

- 更新 Versal 的 Bootgen GUI

- 工具鏈更新

- XSCT,支援 STAPL,新增連結器腳本生成指令

- 系統編譯流程,請參閱系統編譯文件

Vitis 模擬

- 新增軟體模擬支援,為永遠執行內核,提供自動重啟與信箱支援

- 自由執行內核,不再需要為了sw-emu 而使用 while(1)

- 為外部流量生成器,新增軟體模擬支援

- 硬體模擬現可將 HLS C 原始碼功能模型用在串流 IP 上。

- 新增 API xrt::system 以探測裝置數量

- 新增 API xrt::message,供訊息記錄使用

- XRT 原生 API 主機程式碼現在需要用到

-std=c++17 或更高標準 - 新增實驗性 xrt::queue API,支援非同步執行同步操作

- xbutil 可顯示 AIE FIFO 計數器,協助在 AIE 死結情況下進行除錯

- 移除 xbutil --legacy 選項。

- xclbinutil --info 提供嵌入式平台的時脈資訊

- xbutil 在 ARM 上可載入 SOM 映像

- xbtop 獨立公用程式,可顯示類似 Linux top 的指令輸出(取代之前的 xbutil -top)

- XRT 公用程式支援在 Bash 中使用 Tab 鍵進行自動完成。

- Alveo 平台更新:提升穩定性的平台更新、加速卡管理更新、SC 韌體更新工具

- 嵌入式平台,新增 VCK190 DFX 平台:xilinx_vck190_base_dfx_202210_1,嵌入式平台現在隨 Vitis 同時安裝,Vivado 新增可客製化的範例設計:適用於 MPSoC 的 Vitis 平台

- 大幅修改 Vitis 模型編輯器中控台區塊,改善擴充性和易用性

- 除了裸機外,硬體驗證流程現在亦支援 Linux

- 「AIE 至 HDL」和「HDL 至 AIE」區塊不再包含 HDL 閘道區塊

- 2022.1 現在出貨時會隨附範例快照,便於無法存取網際網路的客戶使用。若有更新版本,工具會提示使用者從 GitHub 下載新範例版本

- 為了易於使用起見,不屬於產生程式碼的公用程式區塊,現在改以白色背景呈現

- 增強並重新規劃程式庫瀏覽器以提高易用性

- 支援 RHEL 8.x

- 支援 MATLAB R2021a 和 R2021b

Vitis 軟體平台 2021.2 版本重點:

- 全新特定領域專用開發環境

- 針對 VCK5000 和 Varium C1100 卡,支援完整的端對端流程

- 增強核心工具功能

- Vitis AI 引擎編譯器 C/C++ 高階抽象 API、自動標註推論、區域群組限制

- Vitis AI Engine x86 模擬器增強功能:追蹤報告、記憶體存取違規和死結偵測

- 增強 Vitis HLS EoU、時序和 QoR;新 HLS API,供使用者進行由其控制的叢發推論

- 增強 Vitis Analyzer 功能,提供更優異的時間軸追蹤報告、資料視覺化與停滯分析

- Vitis XRT 現在針對 AI 引擎提供 AI 引擎圖形控制方面的多程序與多執行緒支援。

- Vitis IDE 和模擬支援 AI 引擎追蹤、AI 引擎應用軟體模擬

- 39 個不同領域的全新 C/C++ 程式庫,包括 DSP、資料分析、視覺、壓縮、資料庫、圖形、安全性等,共有逾 1000 個程式庫函數

- Vitis 模型編輯器

- 編譯/模擬速度加快 3 倍,平行編譯時的編譯時間縮短 7 倍

- 新增硬體驗證流程,並強化功能共同模擬功能

附註:Vitis 加速程式庫現提供單獨下載。可從 GitHub 下載,亦可直接在 Vitis IDE 內取得。

| 程式庫 | 2021.1 | 2021.2 | 21.2 新函數 |

|---|---|---|---|

| xf_blas | 167 | 167 | 0 |

| xf_codec | 3 | 3 | 0 |

| xf_DataAnalytics | 33 | 36 | 3 |

| xf_database | 62 | 65 | 3 |

| xf_compression | 78 | 93 | 15 |

| xf_dsp | 94 | 96 | 2 |

| xf_graph | 53 | 59 | 6 |

| xf_hpc | 37 | 37 | 0 |

| xf_fintech | 116 | 116 | 0 |

| xf_security | 135 | 140 | 5 |

| xf_solver | 11 | 11 | 0 |

| xf_sparse | 11 | 11 | 0 |

| xf_utils_hw | 55 | 57 | 2 |

| xf_opencv | 147 | 150 | 3 |

| 總計 | 1002 | 1041 | 39 |

附註:就視覺資料庫的部分,由於每個 API 針對不同類型都有多項測試,所以只需計算 L*/tests 中的子資料夾數量即可

Vitis視覺程式庫

- 可程式化邏輯 (PL)

- 端對端單色影像處理 (ISP),搭配 CLAHE TMO

- RGB-IR 與 RGB-IR 影像處理 (ISP) 管道

- 全域色調對應 (GTM),搭配使用 GTM 的 ISP 管道

| 新功能 | 類別 | 客戶/策略性 | 領域 | 描述 |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | 汽車、ISM | •支援 4x4 RGB-IR 去馬賽克 •主要用於車艙監控系統 •低光源監視攝影機 |

| 單色 (CCCC) | ISP | 策略性 | 汽車、ISM、A&D | •機器視覺 •低光源應用 |

| 全域色調對應 (GTM) | ISP | 策略性 | 汽車、ISM、A&D | •提升動態範圍和對比度 •相較於區域色調對應 (LTM),為成本較低的版本 |

| 密集光流法 TV-L1 | CV | NTT | ISM | •提升光流強固性(抗光照、雜訊與遮蔽) |

AI 引擎 (AIE)

- BlobFromImage

- 支援批次大小為三的接連 filter2D 處理

| 新功能 | 類別 | 客戶/策略性 | 領域 | 描述 |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | 汽車、ISM | •支援 4x4 RGB-IR 去馬賽克 •主要用於車艙監控系統 •低光源監視攝影機 |

| ML+X | ISP | 策略性 | 汽車、ISM、A&D | •ML 干擾預處理 |

| 高斯金字塔 (Gaussian Pyramid) | CV | 策略性 | 汽車、ISM、A&D | •多尺度影像處理的基礎 |

| 箱形濾波器 | CV | 策略性 | 汽車、ISM、A&D | •流暢低通濾波器的基礎 |

Vitis 資料分析程式庫

- 根據 Vitis 程式庫的 Vitis 區塊鏈解決方案

- 立即可用於 Ethereum 的挖礦解決方案

- 開放原始碼,使用與部署極為簡便,以 C++ 搭配 Vitis 程式庫即可部署

- Vitis 程式庫提供靈活度與可擴充性

- 靈活開採多種幣別

- 客製化且編譯至硬體

- 高度最佳化設計

- 在程式庫加入 CSV 剖析器 API

- CSV 剖析器可剖析以逗號分隔值的檔案,並產生物件串流,可輕易連接至 DataFrame API

Vitis 圖形程式庫

- 新增 L2 程式庫

- Louvain 重新編號

- 重新編號

- 餘弦相似度支援「權重」功能

Vitis 資料庫程式庫

- GQE 開始支援非同步輸入/輸出功能,並提供多卡支援。

- 非同步支援可讓 FPGA 在部分輸入資料就緒後,隨即可以開始處理。

- 多卡支援可識別適合工作的多塊 Alveo 加速卡。

Vitis 資料壓縮庫

- ZSTD 多核心壓縮

- 建立全新 ZSTD 多核心架構,使用四核心時,可提供 >1GB/s 的輸送量。

- ZSTD 解壓縮最佳化

- ZSTD 解壓縮法針對效能(增加 20%)和資源(降低 30%)進行最佳化

- 針對 IBM 改良 GZIP/ZLIB 串流核心

- 客製化靜態與動態壓縮串流 IP(4KB 與 8KB)

- 新增功能,以便在 TUSER 連接埠提供壓縮後的大小

- 針對 IBM 改良 GZIP/ZLIB 解壓縮法

- 最佳化 Huffman 解碼器,將延遲減少至 < 1.5K 個週期

- 使用資源大幅減少至 6.9K 個單位(之前為 > 9K)

- 新增 ADLR32 檢查總和功能

- GZIP 系統編譯器 PoC

- 為 GZIP 壓縮解決方案建立系統編譯器 PoC,並以 OpenCL 主機作為基準測試的比較對象。

Vitis DSP 程式庫

- DSPLib 自 2021 起於 Github 提供

- 快速傅立葉轉換 (FFT/iFFT)

- 點大小增加至 32k(取決於資料類型)

- 支援串流 API 和分窗 API。

- 平行等級 (0-4)

- 可達到更高的輸送量,並擴大點大小的支援範圍

- FIR 濾波器

- 針對單取樣率非對稱/對稱 FIR,提供早期串流支援

- DDS/混頻器

- 2021.2 提供新程式庫單元

Vitis Security 程式庫

- 推出 KECCAK-256(雜湊函數)和 CRC32C(檢查總和函數)

Vitis 公用程式庫

- 新增兩個資料移動器實作,供硬體問題除錯使用。

- LoadDdrToStreamWithCounter:透過 AXI 串流,將資料從 PL 的 DDR 載入至 AI 引擎,並記錄發送至 AI 引擎的資料數量。

- StoreStreamToMasterWithCounter:透過 AXI 串流接收來自 AI 引擎的資料,並儲存到 PL 的 DDR,同時記錄發送至 DDR 的資料數量。

AI 引擎 API

- 以純標頭檔 C++ 程式庫的形式實作,提供可轉換為高效 AI 引擎內在函數的類型與運算。

- 提供可參數化的資料類型,以進行泛型程式設計

- 以統一一貫的方式,為不同資料類型執行最常見的運算

- 以公開透明的方式,將較高階的基元轉換為最佳化 AI 引擎內在函數

- 提高 AI 引擎架構間的可攜性

AI 引擎 API 將成為 AI 引擎內核程式設計的主要方式

高階最佳化

AI 引擎編譯器最佳化選項

- --xlopt=0,不套用最佳化。

- --xlopt=1,自動運算堆疊大小,根據 LLVM IR 分析產生指引。

- --xlopt=2,自動內嵌,針對未展開迴圈執行迴圈剝離 (loop peeling),插入標註。

引進 --xlopt=2 以提升效能,預設維持為 --xlopt=1

- 自動內嵌

- 在可行且可能的情況下自動內嵌函數,即使函數未宣告為 __inline 或 inline 亦然

- 自動插入標註

- 自動將標註插入內核程式碼。(更多詳細資訊,請參閱下節)

標註推論

內核最佳化的必要功能

- 減輕使用者手動增添有效且正確之 chess 標註的負擔

2021.2 支援自動推論五種標註

- 針對效能:

- chess_prepare_for_pipelining:適用於最內側的迴圈,以及已知跳脫計數的外側迴圈

- chess_loop_range:適用於已知跳脫計數的迴圈

- chess_unroll_loop/chess_flatten_loop:適用於已知跳脫計數的最內側迴圈

- 針對正確性:

- chess_unroll_loop_preamble:適用於跳脫計數並非展開係數之倍數時

更新圖形程式設計模型 PLIO 和 GMIO

模型之變更項目包括:

- 變更「simulation::platform」的使用方式

- 與圖中的 PLIO/GMIO 物件互動,依位置決定輸入/輸出。

- 變更圖中的全域 PLIO/GMIO 物件。

- 與 graph connect<> 敘述相關的變更。

ADF 圖中的 PLIO/GMIO

目前

- 以全域規模編寫 PLIO、GMIO、simulation::platform 和連線

GMIO gm0(“GMIO_In0”, 64, 1);

GMIO gm1(“GMIO_In1”, 64, 1);

…

GMIO gm7(“GMIO_In7”, 64, 1);

PLIO pl0(“PLIO_Out0”, plio_32_bits, “data/output0.txt”, 250.0);

PLIO pl1(“PLIO_Out1”, plio_32_bits, “data/output1.txt”, 250.0);

…

PLIO pl7(“PLIO_Out7”, plio_32_bits, “data/output7.txt”, 250.0);

simulation::platform<8,8> plat(&gm0, &gm1,…, &gm7, &pl0, &pl1,…, &pl7,);

subgraph g;

connect<> net0(plat.src[0], g.in[0]);

connect<> net1(plat.src[1], g.in[1]);

…

connect<> net7(plat.src[7], g.in[7]);

connect<> net8(g.out[0], plat.sink[0]);

connect<> net9(g.out[1], plat.sink[1]);

…

connect<> net15(g.out[7], plat.sink[7]);

替代方法

- 建立上層圖,然後將 PLIO、GMIO 和連線移動至上層圖裡

- 允許管理在 for 迴圈 (for loop) 內的連線

class topgraph

{

input_gmio gm[8];

output_plio pl[8];

subgraph sg;

topgraph()

{

for (i=0; i<8; i++)

{

gm[i] = input_gmio::create(“GMIO_In”+std::to_string(i), 64, 1);

pl[i] = output_plio::create(“PLIO_Out”+std::to_string(i), plio_32_bits, “data/output”+std::to_string(i)+”.txt”, 250.0);

connect<>(gm[i].out[0], sg.in[i]);

connect<>(sg.out[i], pl[i].in[0]);

}

}

};

topgraph g;

改善區域群組限制功能

支援在 ADF 圖或限制檔案中,使用旗標控制對映工具與路由器

- -contain_routing – 指定為 true 時,所有路由都會限制在區域群組內,且包含 nodeGroup 節點之間的網路。

- -exclusive_routing - 指定為 true 時,所有路由都會限制在區域群組外,但不含 nodeGroup 節點之間的網路。

- -exclusive_placement - 指定為 true 時,會禁止對映工具及路由器將任何 nodeGroup 以外的節點,放入區域群組的邊界方框內。

快照

快照是針對每一個內核連接埠記錄相關註解和資料的文字檔案

- 串流、封包串流、串聯串流

- 分窗、緩衝

- RTP

亦包括所有平台連接埠

- PLIO、GMIO、RTP

允許使用者在內核連接埠上檢查資料流量,不必使用除錯器,也無需安插儀表碼到內核程式碼中

死結偵測

- 偵測 x86 模擬的死結狀況,無論是因為輸入資料不足,或是重新收斂路徑上的 FIFO 深度不平均

- 「死結時停止」功能必須透過指定選項 --stop-on-deadlock,才能在 x86 模擬中啟用

- 模擬作業由於死結而停止時,錯誤訊息會提示您重新執行,其選項為 -trace --timeout

記憶體存取違規偵測

整合 Valgrind 以偵測記憶體存取違規

- 偵測

- 讀取和寫入超出範圍

- 讀取未初始化的記憶體

- 編譯不需要使用特定旗標

- 模擬旗標可以是

- --valgrind:模擬如常運作,由 valgrind 顯示報告

- --valgrind-gdb:相同動作,但同時會以 gdb 進行除錯

追蹤報告

死結情況會導致模擬輸出不佳,難以分析錯誤根源

X86 模擬追蹤選項讓模擬器可以記錄各種時間戳記資訊:

- 內核迭代開始/結束

- 串流停滯開始/結束

- 同步鎖停滯開始/結束

x86 模擬和 AI 引擎模擬器的時間戳記不同

使用者控制的叢發推論

- 使用者若不滿意由 Vitis HLS 工具自動進行的叢發推論,可採用新推出的手動叢發最佳化

- 新類別「hls::burst_maxi」,支援手動控制叢發行為。提供新的 HLS API 以搭配新類別使用

- 使用者需要瞭解 HLS 設計中的 AXI AMBA 通訊協定,以及硬體交易層級建模

增強時序和結果品質功能

- 支援使用者輸入高階輸送量限制

- 提高 HLS 時序估計準確度。當 HLS 報告時序收斂時,Vivado 中的 RTL 合成也應達成時序

EoU 增強功能

在 C 語言合成報告中,新增介面配接器報告

- 使用者需要瞭解介面配接器對其設計的資源影響

- 介面配接器具有可變屬性,可能影響到設計成果品質

- 其中一些屬性具有相關聯的使用者控制項,應向使用者報告這些控制項

- 提供 bind_op 和 bind_storage 報告的文字版本

在合成報告中增加新區塊,以顯示標註和警告清單

- 使用者很容易就能瞭解新增的哪一個標註有問題。

增強分析和報告功能

Function Call Graph Viewer 引進了一些新功能

- 新增滑鼠拖曳縮放功能

- 全新「概覽」功能可呈現完整圖形,且支援使用者放大整體圖形的特定部分

- 所有函數和迴圈都會連同其模擬資料顯示

釋出新的 Timeline Trace Viewer,可在模擬後使用。此檢視器會顯示設計的執行時間設定檔,並可讓使用者在 Vitis HLS GUI 中保留該設定檔。

增強連接摘要功能

- 提供 AI 引擎、平台和運算單元的時脈頻率資訊

- 在系統圖表和平台圖表中,提供一個名為「時脈」的新表格

增強平台匯出功能

- 從 Vivado 匯出 XSA 時,任何來源檔案即使不在專案的本地位置中,也能進行。

- 從 Vivado 匯出 XSA 時,專案結構不會改變

- 僅打包用於硬體平台專案的 IP,而不是打包整個 IP 儲存庫

增強 AI 引擎應用模擬功能

- 針對 aiesimulation 提供外部測試平台整合支援

- 針對 x86simulation 提供外部測試平台整合支援

- 支援在 x86simulation 進行 GDB 除錯

- 支援在 x86simulation 中,針對圖中內核間的資料製作快照

- 支援 x86sim 的存取違規檢查

- 支援 x86sim 的死結時停止

支援 AI 引擎追蹤

支援 AI 引擎應用軟體模擬

支援 Verilog/System Verilog 的外部流量生成器

將分析監測器的功能,延伸安插至監測記憶體

- 現在分析監測邏輯,能夠以內核/CU 連接埠為單位進行安插。此功能為使用者提供了直接在記憶體介面插入監測邏輯的選項

- 直接在記憶體介面達成的記憶體頻寬視覺化成果,可反映在設定檔摘要報告上

- 支援 DDR 記憶體和 PLRAM

- 支援硬體流程

- 若要啟用此功能,需要設定連接階段和 XRT

- memory=all

- data_transfer_trace= coarse|fine 或

- opencl_device_counter=true

將分析監測器的功能,延伸安插至監測記憶體

- 實現記憶體介面監測的 vadd 範例

- 新增「記憶體庫資料傳輸」表格

增強 Vitis Analyzer 功能

為非 OpenCL 應用產生一般分析摘要報告

- 為 XRT API 和 HAL API 應用提供相同水準的支援。

- 使用者可選擇要建立的報告類型,工具會自動產生,並在 Vitis Analyzer 以視覺化顯示

為 PL 事件時間軸新增 OpenCL 指令

- 分析會增加額外負載,XRT 提供將 OpenCL 事件資料傾印在時間軸追蹤視景上的功能,且不會增加負載。

- Vitis Analyzer 可處理 XRT 輸出,並顯示在時間軸追蹤視景。

- 需要在 xrt.ini 中設定 xocl_debug=true。

支援將時間軸追蹤報告中的訊號階層扁平化

- 在預設情況下,時間軸追蹤報告會以階層化方式顯示訊號追蹤狀況

- Vitis Analyzer 提供階層扁平化功能,只要切換「扁平化訊號」圖示即可

- 扁平化時間軸支援波形比較功能

Vitis Analyzer - 資料視覺化

- 顯示 AI 引擎設計中的 AI 引擎內核輸入/輸出資料

- 這有助於進行 AI 引擎設計除錯,並以時間軸顯示輸入/輸出資料

- 可搭配 aiesimulator 使用

- 支援

- 分窗/串流/串聯資料類型

- 封包串流

- 範本內核

- 資料傾印公用程式

Vitis Analyzer - AI 引擎停滯分析

- Vitis Analyzer 提供視覺化功能,讓使用者能夠識別停滯的根本原因

- 支援

- 效能指標

- 同步鎖停滯分析

- 串流停滯分析

- 串聯停滯分析

- 記憶體停滯分析

- 支援流程

- aiesimulator

- 硬體模擬

賽靈思執行階段程式庫 (XRT):

- XRT API

- XRT 原生 API 支援使用者透過 xrt::ip 管理內核控制機制

- XRT 公用程式

- xbutil 和 xbmgmt 現在轉為預設工具

- 若要使用舊版公用程式,請使用 xbutil --legacy 或 xbmgmt --legacy,並搭配舊版子指令

- 新公用程式 xball

- 將 xbutil 或 xbmgmt 指令,套用到安裝後的資料中心卡之全部或篩選出來的一部分。查看 xball --help 以取得詳細資料

- 新指令 xbutil configure

- 可啟用、停用或配置 PCIe 主機記憶體和 PCIe 對等功能。如需詳細資料,請參閱 XRT 說明文件

- 現在,所有 XRT 公用程式全面支援跳過互動式確認步驟的 --force 選項

- xbutil 和 xbmgmt 現在轉為預設工具

- 分析

- 啟用分析選項時,會產生分析摘要報告。

- 所有適用的摘要表和指引,都是根據 xrt.ini 檔案啟用的分析選項所產生

- 全新資料傳輸摘要表,可在將監測器新增至設計中的記憶體資源時,彙整記憶體資源的相關資訊

- 全新 AIE 分析指標集,可計算不同的 AIE 事件,包括 (1) AIE 中的浮點例外狀況、(2) 磚執行數量,以及 (3) 串流寫入與讀取數

- 嵌入式

- 增強 zocl 記憶體管理員功能,以支援所有 sptag

Vitis XRT 提供 AI 引擎多程序支援

- 可使用 C 和 C++ API 定義存取模式,讓多個程序共同存取相同的 AI 引擎陣列和圖形。

- ¬保護 AI 引擎陣列與圖形,避免遭到意外存取。

- 支援三種開啟 AI 引擎陣列與圖形的模式

- 獨占模式(防止任何其他程序存取)

- 優先模式(僅允許其他流程進行非破壞性存取)

- 共用模式(僅限非破壞性存取)

- 需要進行多程序支援時的考量。例如:

- 防止他人存取 AI 引擎陣列(專屬存取)

- 數名使用者需分別控制不同圖形(支援多重應用)

- 由一名主要使用者控制圖形,並允許其他使用者查詢執行狀態(優先與共用存取)

Vitis XRT 對於 AI 引擎的支援狀況

C 和 C++ API

- C 版本 API

- 適用於 AI 引擎陣列:

- xrtAIEDeviceOpenExclusive(獨占模式)

- xrtAIEDeviceOpen(優先模式)

- xrtAIEDeviceOpenShared(共用模式)

- 適用於 AI 引擎圖形:

- xrtGraphOpenExclusive(獨占模式)

- xrtGraphOpen(優先模式)

- xrtGraphOpenShared(共用模式)

- 適用於 AI 引擎陣列:

- C++ 版本 API

- xrt::aie::device 類別支援建構子中的存取模式

- enum class access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2 };

- xrt::graph 類別支援建構子中的存取模式

- enum class access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2, none = 3 };

- xrt::aie::device 類別支援建構子中的存取模式

AI 引擎 DSP 程式庫 – 新區塊

- AIE DDS

- AIE 混頻器

平行編譯

- 時間短於 2021.1 版(為供參考,以下以 200 MHz TX Chain 的數據為例):

- 編譯和模擬時間縮短了 3 倍

- 編譯時間縮短了 7 倍

- 模擬後的空檔時間從 25 秒減少到約 0 秒

增強限制編輯器功能

- 本次 2021.2 版改善了瀏覽介面

改良「轉變為固定大小」區塊

改良「轉變為可變大小」區塊

增強功能共同模擬功能

- 匯出 Matlab 資料,以作為 AI 引擎輸入內容 – xmcVitisWrite

- 匯入 AI 引擎資料至 Matlab – xmcVitisRead

- 匯入 AI 引擎資料至 Matlab - xmcVitisRead

其他

- 匯入沒有輸入的 AI 引擎或 HLS 內核區塊(來源區塊)

- 支援新資料類型

- 支援用 Simulink 原生 int64 和 uint64 開發 AI 引擎,以取代 AMD 資料類型 x_sfix64 和 x_ufix64。

- 新增 accfloat 和 caccfloat 作為 AI 引擎開發的資料類型

- 支援 Ubuntu 20.04

- 支援 MATALB 20a、20b、21a(不支援 MATLAB 21b)

- 新增範例

- 具備 64 內核的雙串流 SSR 濾波器範例

- 擬反矩陣(64x32) – commslib 範例。

- 使用 xmcLibraryPath 指令指定自訂 DSPLib 位置。

- 還有更多功能增強和錯誤修復

Vitis 軟體平台 2021.1 版本重點:

- 支援 AMD Kria 系統模組 (System-on-Module, SOM) KV260 視覺 AI 入門套件。為 ML(DPU 推論引擎)+ X(RTL 內核和以 Vitis HLS 為基礎的電腦視覺內核)提供完整 Vitis 流程。瞭解更多 >

- 支援在 FPGA 和/或 Versal 自適應 SoC 上,使用全新 C/C++ 視覺、DSP、圖形(Louvain 模組化)、影像處理編解碼器、壓縮(GZIP、Facebook ZSTD、ZLIB 全應用加速)最佳化程式庫,效能表現勝過在處理器/顯示卡上運行的版本

- 增強 Versal ACAP 器件上的 Vitis™ 核心開發套件設計流程:AI 引擎設計追蹤報告視覺化改善功能、透過 GMIO 追蹤 AI 引擎事件、漸進式重新編譯、全新開機映像精靈,並且支援加密的 AI 引擎來源檔案

- 全新的 Vitis 模型編輯器工具,實現在 MathWorks MATALB 和 Simulink® 環境中進行快速設計探索即驗證,支援 AI 引擎和可程式化邏輯區塊共同模擬、程式碼生成,及測試平台生成。

- GUI 中新增 Vitis HLS 流程導覽選單,用以快速存取流程階段和報告。將合成、分析和除錯視景,合併至一般預設介面

附註:Vitis 加速程式庫現提供單獨下載。可從 GitHub 下載,亦可直接在 Vitis IDE 內取得。

AIE DSP

- DSPLib 是作為 Github 上 Vitis 加速程式庫套件的一部分發行

- DSPLib 收錄了許多進階訊號處理應用常用到的可參數化 DSP 函數。目前所有函數都支援串流介面,也支援分窗介面。

FIR 濾波器

功能 |

命名空間 |

單取樣率、非對稱 |

dsplib::fir::sr_asym::fir_sr_asym_graph |

單取樣率、對稱 |

dsplib::fir::sr_sym::fir_sr_sym_graph |

插值、非對稱 |

dsplib::fir::interpolate_asym::fir_interpolate_asym_graph |

降頻、半頻帶 |

dsplib::fir::decimate_hb::fir_decimate_hb_graph |

插值、半頻帶 |

dsplib::fir::interpolate_hb::fir_interpolate_hb_graph |

降頻、非對稱 |

dsplib::fir::decimate_asym::fir_decimate_asym_graph |

插值、分數、非對稱 |

dsplib::fir::interpolate_fract_asym:: fir_interpolate_fract_asym_graph |

降頻、對稱 |

dsplib::fir::decimate_sym::fir_decimate_sym_graph |

FFT/iFFT - DSPLib 包含一項 FFT/iFFT 解決方案。這是一個單通道、單內核的分時法 (decimation in time, DIT) 實作,由可配置點大小、複數資料類型、串聯長度和 FFT/iFFT 函數所組成。

功能 |

命名空間 |

單通道 FFT/iFFT |

dsplib::fft::fft_ifft_dit_1ch_graph |

矩陣乘法 (GeMM) - DSPLib 包含一個矩陣乘法/GEMM(一般矩陣乘法)解決方案,支援兩個矩陣 A 和 B 的矩陣乘法,其輸入資料類型可供配置,並產生衍生性輸出資料類型。

功能 |

命名空間 |

矩陣乘法/GeMM |

dsplib::blas::matrix_mult::matrix_mult_graph |

小工具公用程式 - 這些小工具支援在 DSPLib 函數的輸入端進行分窗與串流之間的轉換,如有需要,也可支援在 DSPLib 函數的輸出端將串流轉換成分窗,亦有其他小工具支援在實數和複數資料類型之間轉換。

功能 |

命名空間 |

串流至分窗/分窗至串流 |

dsplib::widget::api_cast::widget_api_cast_graph |

實數轉複數/複數轉實數 |

dsplib:widget::real2complex::widget_real2complex_graph |

Vitis 模型編輯器支援 DSP 程式庫函數,讓使用者能夠簡單地將函數插入 Matlab/Simulink 環境,簡化 AI 引擎 DSP 程式庫評估,以及 AI 引擎 ADF 圖的整體開發工作。

此次 Vitis HPC 程式庫釋出,引進了針對 FPGA HPC 應用的 HLS 基元、預先建構內核與軟體 API。此類應用包括:

2D 聲學 RTM(逆時移位)FDTD(時域有限差分)演算法,包括正向內核和反向內核

3D 聲學 RTM(逆時移位)FDTD(時域有限差分)演算法,包括正向內核

MLP(多層感知器)元件:活化函數與完整連接的網路內核

PCG(預處理共軛梯度)求解器,適用於稠密矩陣與稀疏矩陣

- 首度為 Versal AI Engine 推出多種特選視覺函數:

可用函數

Filter2D

absdiff

accumulate

accumulate_weighted

addweighted

blobFromImage

colorconversion

convertscaleabs

erode

gaincontrol

gaussian

laplacian

pixelwise_mul

threshold

zero

xfcvDataMovers:資料移動公用程式可輕鬆地將高解析度影像分塊 (tiling),並傳輸至 AI 引擎核心本地的記憶體。兩種版本

- 使用 PL 內核:輸送量較高,卻會犧牲額外的 PL 資源。

- 使用 GMIO:輸送量低於 PL 內核的版本,但使用的是 Versal NoC(晶片上網路),不需要用到 PL 資源。

- 全新可程式化邏輯 (PL) 函數與功能

- ISP 管道與函數:

- 更新 2020.2 非 HDR 管道

- 支援在執行期間變更幾個 ISP 參數:紅色與藍色通道的增益參數、AWB 啟用/停用選項、RGB Gamma 表、用於計算 AWB 正規化最小值與最大值的像素百分比 (%pixel)。

- Gamma Correction 和色彩空間轉換 (RGB2YUYV),如今成為管道的一部分。

- 2021.1 HDR 新管道:2020.2 管道 + HDR 支援

- 2 次曝光 HDR 合併,支援具備數位重疊功能的感測器,亦即能同時捕捉短曝光影格及長曝光影格的感測器。

- 支援四種 Bayer 模式:RGGB、BGGR、GRBG、GBRB

- 支援執行期間配置的 HDR 合併 + ISP 管道,管道傳回的是 RGB 輸出。

- 擷取函數:HDR 擷取函數屬於預處理函數,是將單一數位重疊串流當作輸入,並傳回 2 個輸出曝光影格(SEF、LEF)。

- 2 次曝光 HDR 合併,支援具備數位重疊功能的感測器,亦即能同時捕捉短曝光影格及長曝光影格的感測器。

- 3DLUT:提供輸入-輸出對映,控制複雜的色彩運算子,例如色相、飽和度和亮度等。

- CLAHE:限制對比度自適應直方圖均衡化 (Contrast Limited Adaptive Histogram Equalization) 是一種在執行自適應直方圖均衡化時,著手限制對比度的方法,以此避免在接近恆定區域時過度放大對比度。此方法也減少了放大雜訊的問題。

- 更新 2020.2 非 HDR 管道

- 翻轉:以水平線和垂直線為軸翻轉影像。

- 客製 CCA:客製版本的連通元件分析演算法 (Connected Component Analysis),用於偵測果面的缺陷。除了計算果面缺陷部分外,也會運算缺陷像素和果面總像素

- 更新 Canny:Canny 函數現在支援所有影像解析度。

程式庫相關變更

- 所有測試都從 OpenCV 3.4.2 升級到 OpenCV 4.4

- 新增 Versal Edge 系列 (VCK190) 支援

- 新的基準測試區塊,此外也發佈了針對特定管道/函數的基準測試資料。

本次 2021.1 版提供雙元 (Two-Gram) 文字分析:

雙元述詞 (Two Gram Predicate, TGP) 是指使用 2 個字元的詞彙,進行反向索引搜尋。凡建立了反向索引的資料集,TGP 即可在反向索引中找到每筆記錄的配對 ID。

- 社群偵測:Louvain 模組化

- 2-Hop 搜尋

不適用

- 新增用於 L2 內核的雙精度 SpMV(稀疏矩陣稠密向量乘法)實作

在 2021.1 版中,GQE 獲得以下功能的搶先體驗支援

支援 64 位元 join:現在 gqeJoin 內核及其成對的 gqePart 內核,已延伸到 64 位元金鑰與酬載,所以可支援為數更龐大的資料。

初期支援 Bloom-filter:gqeJoin 內核現在出貨時,會搭載可執行 Bloom-filter 探測的模式。此模式可提高部分多節點流程的效率,對於在初期階段最小化資料大小非常重要。

這兩種功能現在都以 L3 純軟體 API 的形式提供,請查看相應的 L3 測試案例。

- GZIP 多核心壓縮:

- 全新 GZIP 多核心壓縮串流加速器,是不折不扣的純串流解決方案(自由執行內核),支援多種不同大小的區塊:4KB、8KB、16KB 和 32KB。

- Facebook ZSTD 壓縮核心:

- 全新 Facebook ZSTD 單核心壓縮加速器,支援 32KB 區塊。ZSTD 壓縮的多核心版本正在開發中(提供更高輸送量)。

- GZIP 低延遲解壓縮:

- 新版本的 GZIP 解壓縮法,在每個區塊的延遲都有所改善,使用的資源更少(LUT 降低 35%,BRAM 降低 83%),同時改善 FMax。

- 針對 U50 的 ZLIB 全應用加速:

- 適用於 U50 平台的 L3 GZIP 解決方案,結合 6 個壓縮核心,能徹底用滿 PCIe 頻寬。它提供了高效率的 GZIP 軟體解決方案,可加速處理器 libz.so 程式庫,無需重新編譯,即可與最終客戶的軟體進行壓縮/解壓縮 API 層級的流暢整合。

- 支援 Versal 平台。

- 新增 AIE 支援 - 請見上文

- 2021.1 版提供以下支援:BLS 的 * RIPEMD160 * 初期支援(尚不完整)

- 在 2021.1 版中,此程式庫新增了資料移動器。不同於其他以 C++ 語言為基礎的 API,這個新功能是為了 HLS 內核設計經驗較少,但想要測試串流設計的使用者所設計。資料移動器實際上是一種內核原始碼生成器,會建立一系列驅動或驗證設計的常用輔助內核,類似 AIE 裝置上的內核。

- 產生 QoR 指標(Vitis QoR 生成 API)

- 應用程式內核所用週期

- 停滯週期(根據 VCD 檔案計算得出)

- 測量包裝函數 (wrapper) 額外使用的週期數(耗費在其他函數而非內核本身的時間)

- 輸送量

- 3 種最佳化等級 XLOPT=0、1(預設)、2

- xlopt=2 的新功能:

- 迴圈融合、扁平化單次迭代外側迴圈、增強迴圈剝離啟發法 (loop peeling heuristics)

- 分析「__restrict」使用量並提供指引

- 漸進式重新編譯:在不變更圖形的情況下,僅重新編譯經過修改的內核

- 封包交換資料 → 最多 32 路(之前限制為 4 路)

- 新增 DMA FIFO 位置限制(不同版本的對映器/路由器更動不影響效能)

- 使用對映解決方案作為新編譯的限制:避免未來的對映變化影響效能

- 讓 aiesim 層級支援 x86sim 功能

- 逐步停止支援 ADF 圖中的 PL 內核(至 2021.2 版完全停止支援)

- GUI 中新增流程導覽選單,用以快速存取流程階段和報告。 情境關係的「合成、分析、除錯」視景,合併至一般預設介面

- 為 BIND_OP 和 BIND_STORAGE 指示提供新的合成報告區塊

- 新的合成後文字報告,反映出 GUI 合成報告中提供的資訊

- 重新設計 IP 匯出和 Vivado 實作執行小工具,現在可選擇將設定及限制檔案傳遞至 Vivado

- 全新函數呼叫圖形檢視器,可視覺化呈現並凸顯強調函數與迴圈,另有偵測 II、延遲或 DSP/BRAM 使用率熱點之熱圖可供選用

- 適用 DSP 區塊原生浮點運算的 Versal 時序校準和全新控制項(config_op 的 -precision 選項)

- Vitis HLS 移轉指南(前身為 UG1391)現在是 UG1399 中的一章

- 收錄新方法章節於使用者指南(UG1399 和網頁)

- 改善替代性的可清除管道選項:無載運行管道(free-running pipeline,又稱「frp」)

- 在 Vitis 中,頂層連接埠指標現在可簡單對映至 axi-lite 轉接器上,而不是全域記憶體

- aggregate 指示現在提供「-compact bit」選項,以達成最大程度的封裝

- 「說明」選單加回「提供意見」欄位,並附上選用調查問卷

- 修正「手冊頁面」索引標籤在部分 Linux 系統不會顯示資訊的問題

- 在 Vitis 中的 m_axi 介面重塑工作,應透過 hls::vector 類型完成

- 為 s_axilite 和 m_axi 資料儲存提供全新客製化選項,以利調整設計中的 RAM 資源規劃,您可以選擇「auto」、「uram」、「bram」或「lutram」

- 在 Vitis 引入新式內核連續(又稱「無止盡」)執行模式

- 恢復 axi_lite 次要時脈選項

- 增強 Vivado IP 打包工具對於 RTL 內核打包的支援性

- 已公開且產品化的功能,附以適當方法和文件。

XRT 管理內核為預設流程。

支援以加密 AIE 來源檔案作為輸入

AIE 編譯器可接受加密 AIE 來源檔案,v++ 亦支援其餘流程。

- 為 Versal 器件新增「建立開機映像精靈」的支援

- 多項 AI 引擎程式設計與除錯改善

- 支援開啟和關閉微碼標籤

- 原始碼和微碼之間的靜態交互定位

- 微碼的完整視景

- 每當管道視景更新資料時,最後的 PC 都一律都會被帶到可見區域

- 在管道視景中對齊指令資料

- 在分解視景中新增「單指令模式」。

- 支援為平台專案產生預設 BIF 檔案

- SD 和 eMMC 的程式燒錄,新增原始模式支援

- AI 引擎開發流程新增介面內說明訊息

- GCC 工具鏈升級至版本 10.2

- 使用者可透過 Python/C++ 等外部程序,模擬 AXI-MM 主/從。這樣可協助使用者快速設計 AXI 主/從且開始模擬,無須投入資源開發 AXI 主器件或 VIP。AXI-MM 跨程序通訊功能,亦有助於模擬兩個 FPGA 之間的晶片對晶片連線。

- 支援將 Versal 模型編譯為 VCS 可模擬的格式。

- 平台開發人員可透過獨立應用程式,在平台上執行硬體模擬,有利於在初期階段測試平台。

- 使用者範圍分析資訊和使用者事件資訊,會彙整至分析摘要報告中

Vitis Analyzer 顯示關鍵時序路徑。

Vitis Analyzer 會顯示簡化版本的 Vivado GUI 時序報告,無須開啟 Vivado 專案或網路連線表。這可讓使用者快速移動定位到失敗的時序路徑。

Vitis Analyzer 多策略支援

Vitis Analyzer 能以視覺化方式,呈現執行多重策略的結果。

- 用於分析與除錯的新 xrt.ini 開關

減少大型應用消耗的記憶體和載入時間

新分析工具在處理大型 csv 檔時,使用的資源較少,進而縮短載入時間與減少發生崩潰問題。

提升 PL 連續追蹤資料卸載能力

使用 DDR 或 HBM 作為儲存追蹤資料的記憶體資源

循環緩衝區支援大量資料卸載

可在 xrt.ini 設定追蹤緩衝區大小和卸載間隔

改善 AIE 設計追蹤報告的視覺呈現

顯示所有 AIE 輸入(分窗、串流、串聯等)

支援所有 IO 資料類型

- 穩定的原生 XRT API,供使用者以 C++ API 處理 AIE 圖形控制與執行、軟體模擬和支援追蹤。

- XRT 提供新的輔助 API,協助使用者從 OpenCL API 移轉至 XRT 原生 API,位置為 $XILINX_XRT/include/CL/cl2xrt.hpp。

- 全新 XRT API xrt::device.get_info() 可擷取器件屬性

- 新一代 xbutil、xbmgmt 公用程式獲得顯著改善,現在改為預設。

- xbutil 可報告電源狀態

- xbmgmt 可支援執行期間的 clk 頻率調節,以及設定使用者的功率上限,以利保護板卡與伺服器。

- sysfs、xbmgmt 和 xbutil 可報告 Alveo 加速卡的 MAC 位址

- 重構 xocl 中的 KDS 排程器後,同時在多個器件上執行多個運算單元時,數百個程序所達到的輸送量獲得了顯著提升。若仍使用舊款殼層,或許會發現輸送量有微幅減少幾個百分比。請參閱 AR 以取得合適解決方案。

- 透過 debugfs /sys/kernel/debug/xclmgmt/ 和 /sys/kernel/debug/xocl/,支援 XRT 驅動程式除錯追蹤

請在以下網址取得適合 Alveo 加速器卡的最新 Vitis 目標平台:www.xilinx.com/alveo。請針對您想要部署應用程式的加速器卡,參閱其開始使用節。

請參閱 UG1120 - Alveo 資料中心加速器卡平台使用者指南,以瞭解詳細資料,並於新版釋出時隨即掌握最新 Vitis 目標平台的相關資訊。

全新平台

- Alveo U200 Gen3x16 XDMA 1RP

- 名稱:xilinx_u200_gen3x16_xdma_1_202110_1

- 特點:從橋、P2P、GT 內核、DDR 自行更新

- Alveo U50 Gen3x16 noDMA 1RP

- 名稱:xilinx_u50_gen3x16_nodma_1_202110_1

- 特點:從橋、P2P、GT 內核、時脈調節

Vitis 嵌入式平台

- VCK190 基礎平台支援 DDR 和 LPDDR 上的 ECC,限制更簡潔。

- MPSoC 基礎平台的 CMA 大小增加至 1536M。所有 Vitis-AI 模型都可使用此 CMA 大小執行。

- 簡化嵌入式平台建立流程:裝置樹生成器可自動產生 ZOCL 節點;XSCT 可產生 BIF 檔案。減少基礎平台來源檔案。

- 支援 Kubernetes (K8s) 叢集:Xilinx FPGA Resource Manager (XRM) 現在可搭配 Kubernetes 使用,對於連接至伺服器的一整群 Alveo 加速器卡,執行和管理其運算單元 (CU),並使用 Alveo 加速器卡,將應用程式擴充至多部伺服器。

- 功能完備的限制編輯器,讓使用者能在 Vitis 模型編輯器中針對 AI 引擎內核指定任何限制。產生的 ADF 圖將包含這些限制。

- 在程式庫瀏覽器新增 AI 引擎 FFT 和 IFFT 區塊。

- 使用者現在可以在程式庫瀏覽器,存取各種不同版本的 AI 引擎 FIR 區塊。

- 支援透過使用輸入連接埠,為 FIR 濾波器指定濾波器係數。

- 新增兩個公用程式區塊「RTP 來源」和「轉變為可變大小」。

- 增強 AIE 內核匯入區塊,現在支援匯入範本化 AI 引擎函數。

- 支援在中控台區塊指定 AI 引擎設計所用的 AMD 平台。

- 使用者可透過中控台區塊,在執行 AIE 模擬後,隨時重啟 Vitis Analyzer。

- 使用者現在可使用 Simulink Data Inspector,繪製週期近似輸出結果,並檢視每個輸出的估計輸送量。

- 增強僅使用圖形標頭檔,將圖形以區塊之形式匯入的可用性。

- 重新設計進度條,現在備有「取消」按鈕

- 提高當 MATLAB 工作目錄不同於模型目錄時,匯入 AI 引擎內核或模擬設計的可用性。

- 新增 TX Chain 200MHz 範例。

- 新增二維 FFT 範例,展示 HLS、HDL 和 AI 引擎區塊的設計。

HDL

- SSR FIR(改善超過 10 倍)和 SSR FFT 模擬速度提升。

- 提升 RAM 和 FIFO 等記憶體區塊的模擬速度

- 更新 Questa Simulator 的黑箱匯入流程,以支援 VHDL 2008

綜述

- Vitis 模型編輯器現已含括 AMD System Generator for DSP 的功能。 曾使用 AMD System Generator for DSP 的使用者,可採用 Vitis 模型編輯器繼續進行開發。

- 支援 MATLAB R2020a、R2020b 和 R2021a

Vitis 軟體平台 2020.2 版本重點:

- Vitis 2020.2 支援 Versal ACAP 平台應用加速和嵌入式軟體開發

- Vitis 核心開發套件現在納入了 AI 引擎編譯器,用於編譯 Versal AI Engine 的 C/C++ 應用程式。AI 引擎為 Versal AI Core 系列一部分,為適用於運算密集型應用的向量處理器

- 加速內核編譯 (Vitis),以及 C/C++ 轉 RTL IP 建立流程 (Vivado),兩者的預設工具皆為 Vitis HLS

- 13 個效能最佳化程式庫,提供逾 600 個 FPGA 加速函數。2020.2 引入了可加速高效能運算應用的全新 Vitis HPC 程式庫,還有多種針對資料分析、圖形、BLAS、稀疏、安全性與資料庫程式庫的增強及新功能

- 針對最終 FPGA 二進碼的生成,新增評估多種實作策略的支援,並提供增強功能,簡化在 Vitis 應用程式中整合 RTL 內核的過程

- 此版本的其他增強功能,包括 AI 引擎應用分析支援、Vitis 專案 Git 版本控制、Vitis Analyzer 內的 Vitis AI 分析資料整合,以及模擬模式的功能強化。

- MATLAB® 和 Simulink® 附加元件:將 AMD 模型編輯器與 DSP 系統生成器合而為一。AI 引擎是 MATLAB 和 Simulink 附加元件的新領域。

尾註

- 根據 2023 年 8 月 10 日的測試,本測試使用了 1000 項 Vitis L2/L3 代碼程式庫設計,以比較 Vitis HLS 2023.2 版和 Vitis HLS 2023.1 版之間的差異。測試期間的系統配置:Intel Xeon E5-2690 v4 @ 2.6GHz 處理器、256GB RAM、RedHat Enterprise Linux 8.6。實際效能會有所不同。系統製造商可能改變配置,而產生不同的結果。-VGL-04

- 這批基準測試是在 2023 年 2 月 12 日進行,使用了 Vitis L1 程式庫所有的 C 程式碼設計,共 1208 項。每項設計都是在搭載雙路 Intel Xeon E5-2690 處理器的系統上運行,作業系統為 CentOS Linux,啟用 SMT,停用渦輪加速。硬體配置預期不會影響軟體測試結果。結果可能會因軟體及韌體設定和配置而異 - VGL-03

- 根據 2023 年 8 月 10 日的測試,本測試使用了 1000 項 Vitis L2/L3 代碼程式庫設計,以比較 Vitis HLS 2023.2 版和 Vitis HLS 2023.1 版之間的差異。測試期間的系統配置:Intel Xeon E5-2690 v4 @ 2.6GHz 處理器、256GB RAM、RedHat Enterprise Linux 8.6。實際效能會有所不同。系統製造商可能改變配置,而產生不同的結果。-VGL-04

- 這批基準測試是在 2023 年 2 月 12 日進行,使用了 Vitis L1 程式庫所有的 C 程式碼設計,共 1208 項。每項設計都是在搭載雙路 Intel Xeon E5-2690 處理器的系統上運行,作業系統為 CentOS Linux,啟用 SMT,停用渦輪加速。硬體配置預期不會影響軟體測試結果。結果可能會因軟體及韌體設定和配置而異 - VGL-03