- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

- 2020.2

- 2020.1

Destaques da versão 2025.2 da Plataforma de software AMD Vitis™

Fluxo de projeto avançado com mecanismos de IA Versal™

- Melhorias na API do mecanismo de IA para Versal AI Edge e Versal AI Série Edge de 2ª geração (AIE-ML e AIE-ML v2)

- Tipos de dados novos e aprimorados

- Novo: MX6 com ponto flutuante em bloco

- Novo: MX4 com ponto flutuante em bloco

- Novo: cbfloat16 (emulado)

- Aprimorado: Cfloat e cbfloat16 (disponíveis nas funções de FFT e de multiplicação de matrizes)

- Aprimorado: cint16 e cint32 (agora podem usar tipos twiddle cint16 em FFTs)

- Tipos de dados novos e aprimorados

- Atualizações do modelo de programação

- Criar buffer compartilhado somente leitura

- Acesso repetido à leitura de blocos MEM (AIE-ML e AIE-ML v2)

- Suporte a DMA-FIFO em AIE-ML e AIE-ML v2

- Os buffers ping-pong podem abranger dois blocos MEM adjacentes

(AIE-ML e AIE-ML v2) - Parâmetros compartilhados para a memória do bloco local

- Aprimoramentos de comutação de pacotes para AIE-ML e AIE-ML v2

- Funções de biblioteca DSP novas e aprimoradas para mecanismos de IA Versal

- Nova soma cumulativa

- Nova distância euclidiana

- Nova aproximação de função (chamada via atualização RTP ou LUT)

- FIR TDM aprimorado com comutação de pacotes (salva os PLIOs)

- 1D FFT aprimorado usando mecanismo de IA e PL (reduz os recursos de PL necessários)

- FIR aprimorado (otimizações de produtividade)

- Mapeador e roteador do mecanismo de IA aprimorado - O compilador pode explorar diferentes footprints/layouts para uma implementação mais eficiente

Verificação mais fácil dos projetos Versal AI Engine

- Atualizações no fluxo de trabalho da Simulação funcional do Vitis com suporte para C++ (acesso antecipado)

- Hardware em loop usando test bench em MATLAB® e Python (acesso antecipado)

Aprimoramentos no Vitis Model Composer para projetos de DSP de AIE

- Atualizações fáceis de usar para fluxo de projeto de SSR (super sample rate, taxa de superamostragem) com mecanismos de IA (acesso antecipado)

- Blocos adicionais disponíveis para mecanismos de IA e HDL:

- AIE, AIE-ML, AIE-ML v2

- Novo: aproximação de função

- Novo: Correlação/convolução

- Novo: Soma cumulativa

- Blocos de biblioteca HDL

- Aprimorado: FFT (adição de SSR nativa de ponto flutuante = 32, 64)

- Aprimorado: FIR (suporta interpolação de taxa fracionária com SSR)

- AIE, AIE-ML, AIE-ML v2

Atualizações para o Vitis IDE para desenvolvimento incorporado

- API Python™ para atualizar a configuração de compilação

- Execute a API do Vitis™ em ambiente Python

- PS Trace visível por padrão para núcleos compatíveis

- Melhoria de depuração – os valores atualizados agora estão destacados na visualização de Assistir e na visualização de Inscrever-se

- Cancelar ou encerrar tarefas de back-end

- Caminhos de arquivos BSP da plataforma unificada (Linux e Windows)

- Theia AI Integration (Acesso antecipado) – fornece a infraestrutura para que o desenvolvedor use seu LLM e assistentes de código preferidos

- Criação de plataforma DFX com API Python

- Fazer backup ou compartilhar uma área de trabalho

- Registro aprimorado para arquivos de configuração

- Novo componente do "Projeto de integração"

Novidades no Vitis por categoria

Expanda as seções abaixo para saber mais sobre os novos recursos e aprimoramentos da plataforma de software AMD Vitis 2025.2. Para obter informações sobre plataformas compatíveis, comportamento alterado e problemas conhecidos, consulte as Notas da versão 2025.2 da plataforma de software Vitis para o Fluxo de aceleração de aplicativos e o Fluxo de desenvolvimento de software incorporado.

Funções aprimoradas da biblioteca de DSP:

- Nova soma cumulativa

- Nova distância euclidiana

- Nova aproximação de função (chamada via atualização RTP ou LUT)

- FIR TDM aprimorado com comutação de pacotes (salva os PLIOs)

- FFT 1D aprimorado usando AIE e PL (reduz os recursos de PL necessários)

- FIR aprimorado (otimizações de produtividade)

Aplica-se a:

- Versal™ AI Core com AIE

- Versal AI Edge com AIE-ML

- Versal AI Série Edge de 2ª geração com AIE-ML v2

- Simulação funcional dos subsistemas do Vitis em C++ (acesso antecipado)

- Suporte avançado para medição de latência e produtividade no Vitis Analyzer — para projetos do mecanismo de IA

- Controle de tempo de execução de partições de AIE independentes

- Atualizações fáceis de usar para fluxo de projeto de SSR (super sample rate, taxa de superamostragem) com mecanismos de IA (acesso antecipado)

- Blocos adicionais disponíveis para mecanismos de IA e HDL:

- AIE, AIE-ML, AIE-ML v2

- Novo: aproximação de função

- Novo: Correlação/convolução

- Novo: Soma cumulativa

- Blocos de biblioteca HDL

- Aprimorado: FFT (adição de SSR nativa de ponto flutuante = 32, 64)

- Aprimorado: FIR (suporta interpolação de taxa fracionária com SSR)

- Melhorias no Pragma de desempenho

- O pragma de desempenho agora será otimizado com base na contagem de viagens calculada pelo CSIM

- As otimizações do pragma de desempenho podem ser convertidas em diretivas em um arquivo de configuração

- Controle condicional de pragmas, incluindo o pragma de desempenho

- Novo suporte de IP

- Taxa fracionária SSR para FIR e FFT - para FFT, a SSR em SPFP32 suporta agora até SSR=64.

- Suporte ECC para buffers de fluxo de dados implementados com Block RAM ou UltraRAM

- Recursos fáceis de usar

- Suporte à reinicialização automática no CSIM e no CoSim

- Cache multiporta para M-AXI

- Novas APIs para transmissões AXI com sinais de bandas laterais

Destaques da versão 2025.1 da plataforma de software AMD Vitis™

Fluxo de projeto avançado com Versal AI Engines

- Funções de biblioteca de DSP novas e avançadas, APIs do mecanismo de IA e suporte para novos tipos de dados

Versal Série AI Core com AIE:

- GEMV e FFT avançados para mecanismo de IA usando arquitetura de lógica programável (PL) + AIE paralelo 2D (adequada para canalizador polifásico)

- Classificação SIMD bitonic vetorizada, correlação, convolução

Versal Série AI Edge com AIE-ML:

- FFT para AIE-ML usando arquitetura PL + AIE-ML paralelo 2D (adequada para canalizador polifásico)

- Classificação SIMD bitonic vetorizada, correlação, convolução

Versal AI Série Edge de 2ª geração com AIE-ML v2:

- FFT 2D AIE-ML v2 + PL v1 (adequada para canalizadores polifásicos)

- FIR TDM (adequada para canalizadores polifásicos)

- GEMM/GEMV

- FIR de taxa única

- FIR de meia-banda

- FIR do reamostrador fracionário

- FIR de alteração de taxa

- FFT/iFFT

- DFT

- Mixer de DDS

- Aproximação de função

Atualizações de programação do mecanismo de IA:

- Especificações de parâmetros de exibição em bloco para memória local

- Redução dos tempos de compilação ao alterar o test bench

- Pipeline mais rápido para o projeto usando buffers ping-pong na DDR em AIE-ML

- Outros aprimoramentos de acesso à memória no AIE-ML

Verificação mais fácil dos projetos Versal AI Engine

- Simulação funcional dos subsistemas do Vitis no MATLAB® e Python™

- Suporte avançado para medição de latência e produtividade no Vitis Analyzer — para projetos do mecanismo de IA

- Controle de tempo de execução de partições de AIE independentes

Aprimoramentos no Vitis Model Composer para projetos de DSP de AIE

- Suporte para vários subsistemas de mecanismo de IA de nível superior

- Blocos adicionais disponíveis para AIE e HDL, incluindo FFT avançado com modos SSR adicionais e complex multipliers que podem usar menos recursos de DSP58

Atualizações para o Vitis IDE para desenvolvimento incorporado

- O Vitis Unified IDE (nova GUI) será o padrão — o Vitis IDE clássico está obsoleto

- Suporte ao conjunto de ferramentas de terceiros, como GCC e ARMClang

- As ferramentas de produtividade de terceiros agora podem ser instaladas e acessadas por meio de um utilitário de mercado no Vitis IDE

Novidades no Vitis por categoria

Expanda as seções abaixo para saber mais sobre os novos recursos e aprimoramentos da plataforma de software AMD Vitis 2025.1. Para obter informações sobre plataformas compatíveis, comportamento alterado e problemas conhecidos, consulte as Notas da versão 2025.1 da plataforma de software Vitis para o Fluxo de aceleração de aplicativos e Fluxo de desenvolvimento de software incorporado.

Versal Série AI Core com AIE:

- GEMV e FFT avançados para mecanismo de IA usando arquitetura de lógica programável (PL) + AIE paralelo 2D (adequada para canalizador polifásico)

- Classificação SIMD bitonic vetorizada, correlação, convolução

Versal AI Série Edge com AIE-ML:

- FFT para AIE-ML usando arquitetura PL + AIE-ML paralelo 2D (adequada para canalizador polifásico)

- Classificação SIMD bitonic vetorizada, correlação, convolução

Versal AI Série Edge de 2ª geração com AIE-ML v2

- FFT 2D AIE-ML v2 + PL v1 (adequada para canalizadores polifásicos)

- FIR TDM (adequada para canalizadores polifásicos)

- GEMM/GEMV

- FIR de taxa única

- FIR de meia-banda

- FIR do reamostrador fracionário

- FIR de alteração de taxa

- FFT/iFFT

- DFT

- Mixer de DDS

- Aproximação de função

- Simulação funcional dos subsistemas do Vitis no MATLAB® e Python™

- Suporte avançado para medição de latência e produtividade no Vitis Analyzer — para projetos do mecanismo de IA

- Controle de tempo de execução de partições de AIE independentes

Suporte para vários subsistemas de mecanismo de IA de nível superior

Blocos adicionais disponíveis para mecanismo de IA e HDL

Mecanismo de IA

- Classificação Bitonic (Versal Série AI Core, Versal AI Série Edge, Versal AI Série Edge de 2ª geração)

- DFT/FFT (Versal AI Série Edge de 2ª geração)

- FIR — taxa única, meia-banda, alteração de taxa, reamostrador fracionário (Versal AI Série Edge de 2ª geração)

- DDS/mixer (Versal AI Série Edge de 2ª geração)

Biblioteca HDL

- FFT avançado — Modos SSR adicionais

- SSR 8, 16, 32, 64 (ponto de flutuação nativo)

- SSR 2, 4 (ponto fixo)

- Complex Multiplier avançado — Menos recursos DSP58

- Novo suporte para CFLOAT MAC

- Flutuação em IFFT de vetor — novo bloco

- Gere o código C++ compatível com Vitis HLS a partir de projetos MATLAB (.m) em R2025a

- Novos recursos de facilidade de uso do Vitis HLS

- Modelagem de entradas de fios e entradas AXI Lite que mudam durante a execução (E/S direta)

- Pragma de desempenho para o projeto HLS de nível superior (EA aberto)

- Suporte para complex multiplier Versal por meio da biblioteca intrínseca dedicada

- Melhorias na GUI do Vitis HLS

- Suporte inicial C++17 via Clang 16

Destaques da versão 2024.2 da plataforma de software AMD Vitis™:

Aprimoramentos nos projetos AMD Versal AI Engine para DSP

- Estimativas de latência e produtividade usando o Vitis Analyzer

- Marcação dos PLIOs indisponíveis usando o Vitis Analyzer

- Rápida prototipagem dos projetos com AMD Versal™ AI Engine

- Heap, pilha e relatório de memória do programa

Funções de biblioteca do Vitis novas e aprimoradas para Versal AI Engines

- Funções avançadas da Biblioteca de DSP para AIE (Disponível no Versal AI Core, Versal Série Premium)

- Funções de filtro FIR TDM (Time Division Multiplexed) com desempenho aprimorado

- Versões de maior desempenho de

- Vetor de matriz geral (GEMV)

- Multiplicação geral da matriz (GEMM)

- 2D IFFT — particionado em AIE + PL para desempenho elevado

- Novas funções da biblioteca de DSP para AIE-ML (disponível no Versal AI Edge)

- Funções de filtro FIR TDM com desempenho aprimorado

- Suporte para FFTs Radix-3/Radix-5

- GEMV

- GEMM

Novos recursos fáceis de usar no IDE Vitis (nova GUI)

- Novo terminal serial: Monitore mensagens seriais a partir do hardware

- Instale e explore extensões de terceiros

- Recurso PS Trace para depuração e otimização do desempenho de sistemas incorporados

Aprimoramentos no Vitis Model Composer para projetos de DSP de AIE

- Atualizações da biblioteca de DSP do mecanismo de IA

- AIE (Disponível no Versal AI Core, Versal Série Premium)

- FFT radix misto

- Aprimoramentos do desempenho de FFT Stockham

- FIR TDM

- AIE-ML (Disponível no Versal Série AI Edge)

- FIR TDM

- Síntese digital direta (DDS — usada para geração de formas de onda)

- Mixer (usado para mudança de frequência)

- AIE-MLv2 (Disponível no Versal Série AI Edge de 2ª geração)

- FIR

- DFT

- DDS

- Mixer

- AIE (Disponível no Versal AI Core, Versal Série Premium)

- Tipos de dados adicionais para o Compositor de modelos Vitis

- Suporte para cbfloat16

- Suporte adicional ao tipo de dados para sinais em cascata

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- Exporte projetos de kernel de AIE/HLS do Vitis Model Composer para o Vitis como um Subsistema Vitis (VSS)

- Depurar kernels de AIE/HLS incorporados no Vitis Model Composer usando o Vitis Debugger

- Atualizações dos conjuntos de blocos de HDL no Vitis Model Composer

- Outros aprimoramentos no Compositor de modelos Vitis

- Tempo de resposta aprimorado para geração de código

- A simulação é executada apenas uma vez para qualquer projeto

- Salve as configurações do bloco do Hub como um arquivo JSON (útil para prototipagem rápida ou processamento em lote)

- Suporte adicionado para MATLAB R2024a

- Suporte adicionado para Red Hat Enterprise Linux (RHEL) 8.10, 9.4

- Tempo de resposta aprimorado para geração de código

- Verificações de regras de projeto (DRCs) para substituir considerações de projeto

Novidades no Vitis por categoria

Expanda as seções abaixo para saber mais sobre os novos recursos e aprimoramentos da plataforma de software AMD Vitis 2024.2. Para obter informações sobre plataformas compatíveis, comportamento alterado e problemas conhecidos, consulte as Notas da versão 2024.2 da plataforma de software Vitis para o Fluxo de aceleração de aplicativos e Fluxo de desenvolvimento de software incorporado.

Funções de biblioteca de DSP aprimoradas para AIE (disponível no Versal AI Core, Versal Série Premium)

- Funções de filtro FIR TDM (Time Division Multiplexed) com desempenho aprimorado

- Versões de maior desempenho de

- GEMV (Vetor geral da matriz)

- GEMM (Multiplicação geral da matriz)

- 2D IFFT — particionado em AIE + PL para desempenho elevado

Novas funções da biblioteca de DSP para AIE-ML (disponível no Versal AI Edge)

- Funções de filtro FIR TDM (Time Division Multiplexed) com desempenho aprimorado

- Suporte para FFTs Radix-3/Radix-5

- GEMV (Vetor geral da matriz)

- GEMM (Multiplicação geral da matriz)

- Estimativa de latência e produtividade com o Vitis Analyzer

- Marcação de quais PLIOs estão indisponíveis usando o Vitis Analyzer

- Atualizações da biblioteca de DSP do mecanismo de IA

- AIE (Disponível no Versal AI Core, Versal Série Premium)

- FFT radix misto

- Aprimoramentos do desempenho de FFT Stockham

- FIR TDM

- AIE-ML (Disponível no Versal Série AI Edge)

- FIR TDM

- DDS (Síntese digital direta — usada para geração de formas de onda)

- Mixer (usado para mudança de frequência)

- AIE-MLv2 (Disponível no Versal Série AI Edge de 2ª geração)

- FIR

- DFT

- DDS

- Mixer

- AIE (Disponível no Versal AI Core, Versal Série Premium)

- Tipos de dados adicionais para o Compositor de modelos Vitis

- Suporte para cbfloat16

- Suporte adicional ao tipo de dados para sinais em cascata

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- Exporte projetos de kernel de AIE/HLS do Compositor de modelos Vitis para o Vitis como um VSS (Subsistema Vitis)

- Depurar kernels de AIE/HLS incorporados no Vitis Model Composer usando o Vitis Debugger

- Atualizações dos conjuntos de blocos de HDL no Vitis Model Composer

- Outros aprimoramentos no Compositor de modelos Vitis

- Tempo de resposta aprimorado para geração de código

- A simulação é executada apenas uma vez para qualquer projeto

- Salve as configurações do bloco do Hub como um arquivo JSON (útil para prototipagem rápida ou processamento em lote)

- Suporte adicionado para MATLAB R2024a

- Suporte adicionado para Red Hat Enterprise Linux (RHEL) 8.10, 9.4

- Verificações de regras de projeto (DRCs) para substituir considerações de projeto

- Modelagem de entradas escalares/de fios que mudam durante a execução (E/S direta)

- Suporte para tipos de ponto flutuação de precisão arbitrária

- Mapeamento do código HLS para blocos de DSP

- Sequência determinada pelo usuário da execução do código

- Depurador HLS que mostra tipos de dados de maneira amigável (usando a tecnologia de prettyprint do depurador GNU)

Destaques da versão 2024.1 da plataforma de software AMD Vitis™:

Aprimoramentos nos projetos do AMD Versal™ AI Engine para DSP

- Funções aprimoradas da biblioteca de DSP para AMD Versal Série AI Core

- Funções de filtro FIR TDM (Time Division Multiplexed) para SSR > 1

- FFT com fator twiddle de 32 bits

- FFTs radix misto 3 e radix misto 5

- Matriz de produto de Kronecker

- Solver QRD baseado em uso doméstico para estabilidade melhorada

- DFT para SSR > 1

- Novas funções da biblioteca de DSP para AMD Versal Série AI Edge com AIE-ML

- Vetor geral da matriz (GEMV) com suporte para SSR

- Multiplicação geral da matriz (GEMM) com suporte para SSR

- Aprimoramentos de API AIE

- Compatível com FFTs Radix-3/Radix-5

- Aprimoramentos do Simulador AIE

- Capacidades de simulação aproximada de ciclo para projetos de mecanismo de IA com PL, sem a necessidade de núcleo de IP de sistema de controle, interfaces e processamento (CIPS)

- Suporte ao analisador AMD Vitis para emulação de hardware com simuladores de terceiros, como VCS, Questa, Xcelium e Riviera

Aprimoramentos importantes na Plataforma de software unificada Vitis

- Suporte a novos dispositivos: AMD Versal™ Premium VP1902 SoC adaptativo, processador AMD MicroBlaze™ V

- Desenvolvimento aprimorado de aplicativos incorporados e geração de BSP para ambiente Windows®

- Fluxo gerenciado pelo usuário para depurar aplicativos incorporados compilados externamente

- Nova GUI Bootgen

- Habilite criações incrementais para projeto de plataforma

Principais aprimoramentos no AMD Vitis IDE (Nova GUI)

- Suporte adicionado para depuração hierárquica do subsistema de processamento

- Suporte adicionado para exportação e importação de projetos/espaço de trabalho

- Suporte adicionado para interpretador Python e API

- Nova página de visualização de recursos

- Nova notificação de alteração de arquivo para projetos de plataforma incorporados, AIE

Novidades no Vitis por categoria

Expanda as seções abaixo para saber mais sobre os novos recursos e aprimoramentos da plataforma de software AMD Vitis 2024.1. Para obter informações sobre plataformas compatíveis, comportamento alterado e problemas conhecidos, consulte as Notas da versão 2024.1 da plataforma de software Vitis para o Fluxo de aceleração de aplicativos e Fluxo de desenvolvimento de software incorporado.

Funções avançadas da Biblioteca de DSP para AMD Versal Série AI Core

- Funções de filtro FIR TDM (Time Division Multiplexed) para SSR > 1

- FFT com fator twiddle de 32 bits

- FFTs radix misto 3 e radix misto 5

- Matriz de produto de Kronecker

- Solver QRD baseado em uso doméstico para estabilidade melhorada

- DFT para SSR > 1

Novas funções da biblioteca de DSP para AMD Versal Série AI Edge com AIE-ML

- Vetor geral da matriz (GEMV) com suporte para SSR

- Multiplicação geral da matriz (GEMM) com suporte para SSR

Aprimoramentos de API AIE

Compatível com FFTs Radix-3/Radix-5

Aprimoramentos do simulador do mecanismo de IA

- Capacidades de simulação aproximada de ciclo para projetos de mecanismo de IA com PL, sem a necessidade de CIPS (núcleo de IP de sistema de controle, interfaces e processamento).

- Suporte ao analisador do Vitis para emulação de hardware com simuladores de terceiros, como VCS, Questa, Xcelium e Riviera

- Exporte tabelas do analisador do Vitis para o formato CSV

- Novas funções de DSP compatíveis com AIE e AIE-ML no Compositor de modelos do AMD Vitis

- Funções de filtro FIR TDM (Time Division Multiplexed)

- Para criação de canalizadores polifásicos a 1 GSPS e maior produtividade

- DFT/IDFT — com suporte para SSR

- Transformações otimizadas para produtividade/latência em tamanhos pequenos

- FFT/IFFT — com suporte estendido para fator twiddle CINT32 bits

- FFT/IFFT radix misto — com suporte para AIE-ML

- Aprimoramentos fáceis de usar no bloco do Hub do Compositor de modelos

- Aprimoramentos no fluxo de validação de hardware

- Suporte para versão do sistema operacional e MATLAB® adicionado à versão 2024.1:

- RHEL 9

- MATLAB R2023a e R2023b

Novos exemplos de projetos disponíveis no Github.

Um novo pragma de estêncil simplifica o código HLS em C++ para imagens e vídeos

Novos assistentes de função de biblioteca aproveitam o repositório GitHub das bibliotecas do AMD Vitis

- Crie IPs "Solver" e "Vision" (compatível com OpenCV) para a ferramenta de projetos do AMD Vivado

- Execute os exemplos de biblioteca disponíveis

Agora, o pragma para interface de memória (ap_memory) pode agrupar portas para o AMD Vivado IP Integrator

A nova comparação de componentes HLS exibe métricas lado a lado para 2 ou mais componentes

Suporte para código RTL do provedor de usuário para substituir uma função do C++ (fluxo de black-box)

Agora, o Analisador de código pode desagregar membros de C analysis struct para ajustar o desempenho

Novo controle de usuário para codificação de FSM global de HLS e seleção de estado seguro

Acesso a limpadores de clang durante a C-Simulation para realizar verificações de endereço e de inicialização

Destaques da versão 2023.2 da plataforma de software Vitis™:

Aprimoramentos nos projetos AMD Versal™ AI Engine para DSP

- Novas funções da biblioteca de DSP

- Novo suporte de API para funções de DSP

- Novos recursos do compilador e simuladores do mecanismo de IA

Novo software independente Vitis Embedded

- Um instalador independente menor para projetistas que escrevem código C para o subsistema incorporado Arm®

- Todos os recursos incorporados são fornecidos, incluindo utilitários como Bootgen e XSCT

Novo ambiente de projeto integrado e unificado do Vitis

- GUI e CLI consistentes em todos os fluxos de trabalho do Vitis

- A GUI baseada em Eclipse Theia de última geração oferece mais flexibilidade e recursos fáceis de usar para melhorar a eficiência do trabalho

Novidades no Vitis por categoria

Expanda as seções abaixo para saber mais sobre os novos recursos e aprimoramentos da plataforma de software Vitis 2023.2. Para obter informações sobre plataformas compatíveis, comportamento alterado e problemas conhecidos, consulte as Notas da versão 2023.2 da plataforma de software Vitis para o Fluxo de aceleração de aplicativos e Fluxo de desenvolvimento de software incorporado.

Novas funções de biblioteca de DSP para mecanismos de IA

- FFT radix misto

- Discrete Fourier Transform (DFT)

- Multiplicador de matriz-vetor geral (GEMV)

Novo suporte de API para funções de DSP

- FFT IP com tipos de dados de fator twiddle cint32

- Suporte para cint16 para APIs FFT Radix-4

- "fix2flt" e "flt2fix" vetorizados e implementados na API

Novo suporte de API para funções de AIE

- Agora, as APIs suportam tipos de dados int32/cint32 na função sliding_mul()

- Agora, as APIs suportam tipos de dados <float> na função sliding_mul()

- Todas as rotinas de API AIE necessárias para suportar a multiplicação de matriz esparsa são fornecidas

Principais atualizações de componentes:

- U-boot 2024.1

- Arm Trusted Firmware 2.10

- Kernel do Linux 6.6_LTS

- Qemu 8.1

- Xen 4.18

- OpenAMP 2023.10

Sunset BSPs:

- AMD Microblaze™: VCU118, KCU105, KC705, AC701

- Zynq: zc706

- AMD Versal™: VMK180-EMMC, VMK180-OSPI

- Zynq MP: ZCU111

Novos BSPs (XSCT):

- BSP de produção VEK280 com o novo Ethernet PHY

Novo sistema BSP Device Tree Flow (SDT):

- ZCU102, ZCU104, ZCU105, ZCU216

- ZCU208, ZCU208-sdfec, ZCU670

- VCK190

- VMK180

- VPK120

- VPK180

- VEK280

- Agora, o compilador AIE pode suportar matrizes 2D e 3D como entradas ou saídas

- O Vitis Analyzer agora gera um relatório de orientação para ajustar o tamanho de FIFO

- Nova compatibilidade para aceleração do analisador de kernel do simulador com vários threads e de despejo de alteração de valor (VCD)

- Interface externa com o ambiente MATLAB® e geradores de tráfego Python

- Modelo de fluxo AXI aprimorado com suporte para ciclos de espera/vazio no alinhamento do PLIO

- Verificação avançada de regras de projeto

- Descarregamento do rastreamento do mecanismo de IA via depuração de alta velocidade

- Suporte a perfil NOC e DDRMC rígido no ambiente do Vitis

- A ferramenta Vitis agora suporta o rastreamento AIE-ML para a placa aceleradora AI Inference VEK280 e Alveo™ V70

- Atualizações do bloco de mecanismo de IA

- Suporte para importação de grafos AIE-ML como blocos para o Compositor de modelos Vitis Model Composer

- Novas funções de DSPlib para implementação de AIE e AIE-ML no Compositor de modelos Vitis

- Plotagem da saída do simulador AIE para sinais internos na ferramenta Simulink®

- Atualizações do bloco do kernel HLS

- Geração automática de testbench

- Suporte expandido ao tipo de dados para blocos de kernel de HLS

- Integração do Compositor de modelos Vitis e da ferramenta Vitis

- Geração de arquivos .xo and libadf.a diretamente do compositor de modelos Vitis

- Outros aprimoramentos

- Suporte para versão da ferramenta MATLAB®: R2021a, R2021b Atualização 6, R2022a Atualização 6, R2022b

- Topologias adicionais suportadas para o fluxo de validação de hardware

- Novos exemplos de materiais de apoio disponíveis no GitHub

- Novo IDE unificado do Vitis para componentes HLS

- Novos requisitos de licença do Vitis HLS

- Novo recurso do analisador de código para obter estimativas de desempenho antes de executar a síntese em C

- Aprimoramentos na interface AXI:

- Suporte para canais laterais de transmissão AXI de HLS

- Suporte para cache principal AXI configurável pelo usuário

- Outros aprimoramentos:

- Novo relatório de complexidade de código para possibilitar a identificação de problemas de tamanho de projeto durante a síntese em C

- Aprimoramentos no tempo de compilação: Aprimoramento médio no tempo de compilação de 20% na versão 2023.2 em comparação com a versão 2023.11

Destaques da versão 2023.1 da plataforma de software Vitis:

Novas funções de biblioteca do Vitis™ para matrizes do mecanismo de IA (AIE) Versal™

- Funções da biblioteca de DSP — mais configurações de filtro FIR

- Funções da biblioteca Solver — aprimoramentos para um desempenho mais elevado

Aprimoramentos no fluxo de projeto para o Versal das séries AI Core e AI Edge

- Suporte do compilador AIE para matrizes 2D e 3D como entradas/saídas

- Suporte de orientação do simulador AIE para dimensionamento FIFO para evitar condições de deadlock

- Melhorias no relatório de status de AIE

- Nova GUI padrão para o Vitis Analyzer

Suporte para exportação de ambiente do Vitis para o ambiente do Vivado™

- Possibilita que as equipes de desenvolvimento de ferramentas Vitis e Vivado trabalhem em paralelo com base em um ponto de verificação de interface comum

Novidades no Vitis por categoria

Expanda as seções abaixo para saber mais sobre os novos recursos e aprimoramentos da plataforma de software AMD Vitis 2023.1. Para obter informações sobre plataformas compatíveis, comportamento alterado e problemas conhecidos, consulte as Notas da versão 2023.1 da plataforma de software Vitis para o Fluxo de aceleração de aplicativos e Fluxo de desenvolvimento de software incorporado.

Biblioteca de DSP — Filtros FIR

- FIR do reamostrador fracionário aprimorado, FIR de taxa única, FIR de meia banda e FIR de alteração de taxa para suportar larguras de bits de coeficiente maiores que a as larguras de bits de dados

- O FIR do reamostrador fracionário também suporta a operação SSR usando vários blocos AIE e incorpora um recurso de recarga de coeficiente

Biblioteca Solver

- Desempenho de API aprimorado com projetos de streaming de alto desempenho (aproximadamente 300 blocos)

- Suporte de decomposição QR e Cholesky para funções de movimentador de dados 4D para ajudar a ler ou gravar dados de matrizes de AIE

- Agora, o compilador AIE pode suportar matrizes 2D e 3D como entradas ou saídas, além de 1D.

- O compilador AIE suporta construções de grafo dentro de grafo (subgrafos) e construções de porta condicional.

- APIs de conversão de dados do novo AIE CINT para CFLOAT.

- Aprimoramento do relatório de status de AIE para gerar um arquivo que inclui informações sobre blocos, eventos e registros adicionais nos blocos AIE-ML e AIE no projeto.

- Descarregamento do rastreamento de eventos AIE em pares diferenciais de alta velocidade (HSDPs) em vez de armazená-lo na memória em dispositivos Versal.

- Suporte a perfil NOC e DDR MC rígido no ambiente do Vitis.

- Rastreamento de evento com janela de AIE para inspecionar uma parte específica de um aplicativo.

- Orientação com dimensionamento FIFO para evitar deadlocks.

- Capacidade de selecionar nós que são relatados pelo simulador AIE para reduzir o tamanho do arquivo VCD do simulador e acelerar a simulação.

- O simulador AIE agora gera um relatório (que pode ser visualizado no Vitis Analyzer) que mostra qual AIE tem violações de acesso à memória e como elas correspondem às linhas no grafo em código C.

- A visualização de dados da visualização de rastreamento agora também é compatível com a matriz de AIE-ML.

- Suporte a um novo tipo de dados para configurações de filtro FIR que visam mecanismos do Versal AI Engine

- Duas novas funções de ponto de flutuação otimizadas para DSP58s nos SoCs adaptativos Versal

- Tempo de resposta mais rápido para todas as funções da biblioteca do Vitis Model Composer direcionadas aos mecanismos de IA do Versal

- Outros aprimoramentos:

- Aprimoramentos nos blocos do kernel de HLS

- Aprimoramentos no Hub do Vitis Model Composer

- Suporte para a ferramenta MATLAB versões R2021a, R2021b, R2022a

- Aprimoramentos de desempenho2: Aprimoramentos médios de latência de 5,2% na versão 2023.1 em comparação com a versão 2022.2

- Maneira fácil de baixar, visualizar e instanciar funções de bibliotecas de L1 na ferramenta Vitis HLS

- Suporte avançado para transações de AXI e relatórios de bursts na ferramenta Vitis HLS

Destaques da versão 2022.2 da plataforma de software Vitis:

Novas funções de biblioteca do Vitis™ para matrizes do mecanismo de IA (AIE) Versal™

- Funções da biblioteca de DSP — recursos aprimorados

- Funções da biblioteca do Solver

- Funções da biblioteca Vision

- Funções da biblioteca Ultrasound

Aprimoramentos no fluxo de projeto para o Versal das séries AI Core e AI Edge

- Controle a colocação relativa de kernels na matriz do mecanismo de IA — desempenho mais elevado e melhor utilização

- Melhorias no simulador AIE x86 — modelagem aprimorada de condições de deadlock no simulador x86

- Melhorias na API de AIE — APIs de vetor Radix 3/5 FFT e Matrix "x" adicionadas

- Capacidades avançadas de criação de perfis e depuração para projetos Versal — detecção de deadlock, coleta de dados de rastreamento maiores, suporte a testbench de RTL/Python

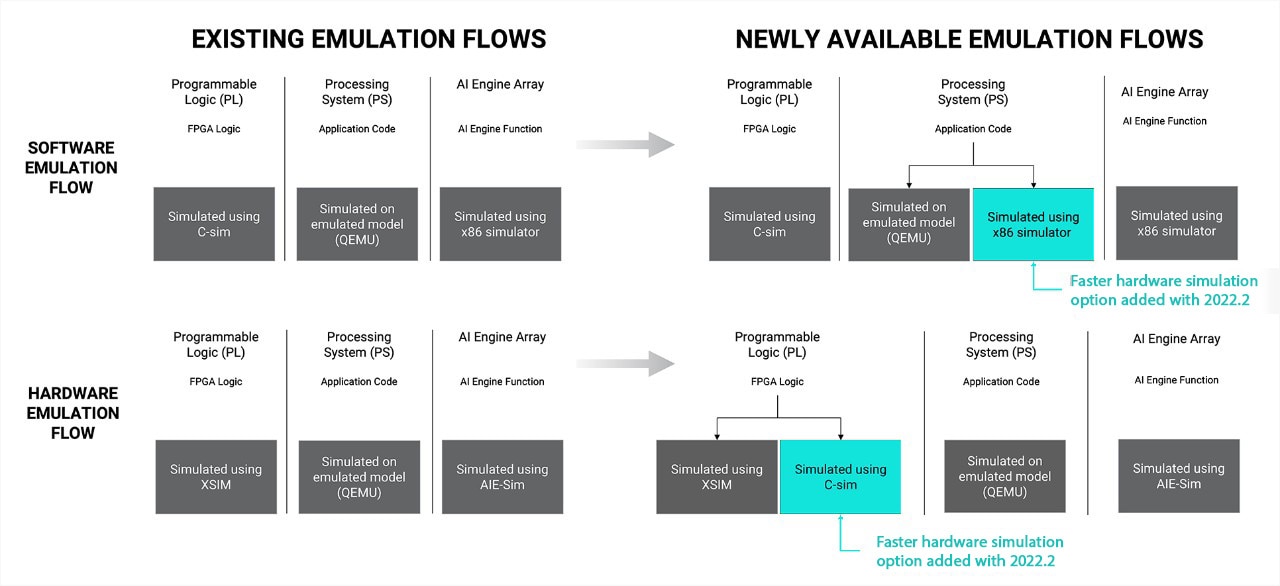

- Novas opções de simulação para projetos heterogêneos no Vitis

Novidades no Vitis por categoria

Expanda as seções abaixo para saber mais sobre os novos recursos e aprimoramentos da plataforma de software AMD Vitis 2022.2. Para obter informações sobre plataformas compatíveis, comportamento alterado e problemas conhecidos, consulte as Notas da versão 2022.2 da plataforma de software Vitis para o Fluxo de aceleração de aplicativos e Fluxo de desenvolvimento de software incorporado.

Funções da biblioteca de DSP

- A implementação do filtro FIR de taxa de superamostra (SSR) no mecanismo de IA agora suporta o recurso de recarga de coeficiente e o tamanho de ponto dinâmico

- Adicionado o elemento de janela de FFT à função FFT que visa a matriz do mecanismo de IA

Funções da biblioteca do Solver

- Decomposição da rotação de quadratura (QR)

- Decomposição de Cholesky

Funções da biblioteca Vision

- Quatro novas funções de vídeo direcionadas à matriz do mecanismo de IA

Funções da biblioteca Ultrasound

- Várias funções para ajudar a criar projetos de ultrassom médico

- Capacidade de adicionar restrições para controlar a colocação relativa de kernels na matriz do mecanismo de IA, isso permite que os usuários obtenham desempenho mais elevado e melhor utilização

- Modelagem aprimorada das condições de deadlock de AIE no simulador de x86

- Nova API de AIE adicionada — APIs de vetor Radix 3/5 FFT e Matrix "x" adicionadas

- Geração de relatórios de criação de perfis do mecanismo de IA em emulação de HW

- Detecção de deadlock usando o XSDB (AMD System Debugger) para projetos baseados em PL e mecanismo de IA

- Descarregamento contínuo controlado por Xilinx Runtime (XRT) do rastreamento de evento do mecanismo AI pelo PLIO

- Suporta o aplicativo PS na máquina host x86 para emulação de SW

- Permite modelos funcionais SystemC para emulação de HW em vez de RTL

- Permite que os usuários simulem o kernel do mecanismo de IA com um simples testbench RTL ou um gerador de tráfego baseado em script Python

- O status do mecanismo de IA pode ser analisado durante a emulação de HW com o analisador do Vitis™

Novas opções de simulação do ambiente do Vitis 2022.2: Simulação do sistema de processador x86 e simulação do mecanismo de IA x86: A simulação lógica programável pode ser realizada usando o simulador x86.

- Recursos para o projeto Versal AI Engine

- A capacidade de adicionar restrições de grafos à biblioteca de DSP do mecanismo de IA bloqueia projetos — melhor utilização e desempenho

- Nova capacidade para simulação de ciclo aproximado para projetos de mecanismo de IA

- O bloco de importação de grafo do mecanismo de IA detecta automaticamente as portas do parâmetro de tempo de execução (RTP)

- Aprimoramentos e adições aos blocos da biblioteca de DSP

- Recursos gerais

- Fluxo de validação de hardware compatível com projetos de sistema heterogêneos que usam matriz PL e AIE

- Bloco de Hub do Vitis Model Composer atualizado para dar suporte ao projeto heterogêneo

- Detecção automática de subsistemas de mecanismo de IA, HDL e HLS válidos

- Fluxo de validação de hardware avançado para projetos somente HDL e HDL → AI Engine → projetos HDL para plataformas Versal

- Suporte aprimorado ao estilo de codificação do "paralelismo no nível da tarefa"

- Possibilita uma simulação C mais rápida e uma melhor qualidade dos resultados

- Aprimoramentos de desempenho e tempo adicionais

- Inferência de burst aprimorado

- Inferência automática de Unroll, Pipeline, Array_Partition e pragmas em linha para um melhor desempenho

- Maior precisão de tempo, resultando em melhor fechamento de tempo e em frequências mais altas

- Outros recursos

- Análise e depuração: printf inserido no código C agora é suportado mesmo após a síntese de RTL

- Facilidade de uso: novo pragma de desempenho para atingir automaticamente um determinado intervalo de transação

- As interfaces HLS::stream agora são compatíveis para IPs FFT e FIR

Destaques da versão 2022.1 da plataforma de software Vitis:

Aprimoramento de fluxo do Vitis™ para ACAP Versal™ e mecanismo de AI

- Suporta a plataforma DFX base da AMD com uma região estática e uma região de DFX

- O perfil de AIE suporta a detecção de paralisação/deadlock, gera relatórios de visualização do status do mecanismo de AI (incluindo eventos de erro) no Vitis Analyzer

- Geradores de tráfego externo em x86sim, AIEsim e emulação de SW são muito mais flexíveis e podem ser inseridos com muita facilidade em fluxos de simulação e emulação

- O Vitis Model Composer é compatível com validação de hardware, Linux e emulação de hardware

Vitis para DC e Vitis HLS

- O Vitis fornece suporte adicional a relatórios para o processo de geração de região dinâmica e os aprimoramentos de relatórios de fluxo incluem 3 relatórios novos ou atualizados

- O Vitis melhora o perfil de PL com a opção de descarregar o rastreamento para recursos de memória (preferencial) ou FIFO de PL para melhor desempenho

- Um novo Visualizador de rastreamento de linha de tempo para mostrar o perfil de tempo de execução e permitir que o usuário permaneça na GUI do Vitis HLS agora está disponível após a simulação

- Agora, o Vitis HLS suporta um tipo de construção "inteligente" de nível mais elevado através do novo pragma de desempenho ou do set_performance_directive

- Biblioteca de grafos do Vitis com melhorias de API L3 (tempo de 1 ms economizado para chamada de kernel) para desempenho

Novidades no Vitis por categoria

Expanda as seções abaixo para saber mais sobre os novos recursos e aprimoramentos da plataforma de software AMD Vitis 2022.1. Para obter informações sobre plataformas compatíveis, comportamento alterado e problemas conhecidos, consulte as Notas da versão 2022.1 da plataforma de software Vitis para o Fluxo de aceleração de aplicativos e Fluxo de desenvolvimento de software incorporado.

- Nova biblioteca de aceleradores genômicos adicionada (L1 e L2 e L3)

- Biblioteca de grafos, aprimoramentos de L3 para desempenho

- Biblioteca de banco de dados do Vitis, kernel multifuncional GQE

- Novas funções adicionadas à biblioteca Vision

- Novas funções nas adições/melhorias da biblioteca AIE Vitis Vision

- Biblioteca de DSP do AIE do Vitis, o reamostrador FIR substitui o interpolador fracional FIR

- Novas APIs, API jxlEnc, API "leptonEnc", API "resize" e API "WebpEnc" da biblioteca de codecs do Vitis

Biblioteca de compactação de dados do Vitis

- Melhora da compressão de ZLIB, compressão Octa-Core personalizada para solução 8KB

- Aprimoramento na descompactação do ZLIB, IP personalizado para tamanho de arquivo 8KB

- Aprimoramento da consulta de capacidade da plataforma

- Aprimoramento na HBM fácil de usar, capacidade de escolher um ponto de entrada específico S_AXI para o HMSS para um kernel M_AXI, inserção RAMA suportada a partir dos arquivos de configuração

Compilador de mecanismo de IA do Vitis

- Detecção e análise automatizada em hardware de paralisação/deadlock por mecanismo de IA

- Analisando a saída de status automatizada

- Analisando a saída de status automatizada — buffers

- Analisando a saída de status manual em hardware

- Analisando a saída de status manual

- Melhorias no rastreamento de eventos do mecanismo de IA

- Geradores de tráfego externo AIEsim

- Aprimoramentos no HW com perfil do mecanismo de IA

- Suporte ao mecanismo de IA para janelas de transmissão

- Modelo de programação avançada de grafos do compilador do mecanismo de IA do Vitis

- Compilador do mecanismo de IA do Vitis — PLIO/GMIO em grafos ADF

Vitis HLS

- Aprimoramentos de análise e novo visualizador de rastreamento de linha de tempo

- Aprimoramentos de estilo de codificação e suporte à partição de matriz para o tipo fluxo de blocos

- Abstração de pragma e novo pragma de desempenho (e diretiva)

- Vitis Core "one liner", Vitis HLS — Novo visualizador de rastreamento de linha de tempo, novo pragma de desempenho, janelas de suporte de fluxo de blocos

- Novo visualizador introduzido

- Mostra o perfil de tempo de execução de todas as funções sobreviventes em seu projeto, ou seja, aquelas que são convertidas em módulos

- Especialmente útil para ver o comportamento das regiões de fluxo de dados após a cossimulação

- Nativo para Vitis HLS — não é mais necessário iniciar o visualizador de forma de onda xsim (ferramenta externa)

Vitis Analyzer

- Aprimoramento do Vitis Analyzer e salvar/restaurar a personalização da linha do tempo

- Aprimoramento de relatórios, report_qor_assessment, informação de clocking xclbin, resumo de automação do Vivado

- Aprimoramento de perfil, nova infraestrutura de criação de perfil PL habilitada, várias opções de trace_memory podem ser adicionadas para inserir vários monitores de memória (somente HW), arquivo de configuração de amostra para mais de um linker para descarregar dados de rastreamento de todos os CUS em SLR0 a DDR0 e o mesmo para todos os CUS em SLR1 a DDR1

Vitis IDE

- GUI Bootgen atualizada para Versal

- Atualização da cadeia de ferramentas

- XSCT, suporte a STAPL e adição de comando de geração de script Linker

- Fluxo de compilação do sistema, consulte o documento de compilação do sistema

Vitis Emulation

- Adição de suporte de emulação de software para reinicialização automática e suporte de caixa de correio para kernels sempre em execução

- O kernel de execução livre não precisa de while(1) para sw-emu

- Adição de suporte de emulação de software para gerador de tráfego externo

- A emulação de hardware pode usar o modelo de função de código-fonte C HLS para Streaming IP.

- Adicione a API xrt::system para sondar o número de dispositivos

- Adicione a API xrt::message para mensagens de registro

- O código de host da API nativa do XRT agora requer

-std=c++17 ou superior - Adicione APIs experimentais xrt::queue para execução assíncrona de operações síncronas

- O xbutil pode mostrar contadores AIE FIFO que ajudam a depurar cenários de deadlock do AIE

- A opção xbutil --legacy foi removida.

- A opção xclbinutil --info fornece informações de clock para plataformas incorporadas

- O xbutil em ARM pode carregar imagens de SOM

- O utilitário autônomo xbtop mostra a saída semelhante ao Linux top (substituindo o legado xbutil -top)

- O XRT Utilities suporta preenchimento automático em Bash com a tecla tab.

- Atualizações da plataforma Alveo, atualizações da plataforma para estabilidade aprimorada, atualizações do gerenciamento de placa, ferramenta de atualização de firmware SC

- Plataforma incorporada, nova plataforma DFX VCK190: xilinx_vck190_base_dfx_202210_1, plataformas incorporadas agora são instaladas com o Vitis, o Vivado adiciona um novo exemplo de projeto personalizável: Plataforma Vitis para MPSoC

- Revisão geral do bloco de hub do Vitis Model Composer para escalabilidade e facilidade de uso

- O fluxo de validação de hardware agora oferece suporte ao Linux, além do bare metal

- Os blocos "AIE to HDL" e "HDL to AIE" não incluem mais os blocos de gateway HDL

- A versão 2022.1 agora é enviada com um snapshot dos exemplos para clientes que não têm acesso à internet. A ferramenta solicitará que o usuário faça download de uma nova revisão dos exemplos do GitHub, se disponível

- Para facilitar o uso, os blocos de utilitários que não fazem parte da geração de código agora são apresentados com uma cor de fundo branca

- Navegador de biblioteca aprimorado e reorganizado para facilitar o uso

- Suporte a RHEL 8.x

- Suporte para MATLAB — R2021a e R2021b

Destaques da versão 2021.2 da plataforma de software Vitis:

- Novos ambientes de desenvolvimento específicos de domínio

- Vitis™ Video Analytics SDK no SOM Kria™, Alveo™ U30/U50 e placa de desenvolvimento VCK5000 Versal™: Saiba mais >

- Solução Vitis Blockchain na placa Varium™ C1100 com bibliotecas do Vitis: Saiba mais >

- Suporte de fluxo de ponta a ponta completo para placas VCK5000 e Varium C1100

- Recursos aprimorados da ferramenta principal

- API de abstração de alto nível em C/C++ do compilador de mecanismo de IA do Vitis, inferência automática de pragma, restrições do grupo de área

- Aprimoramentos do x86simulator do Vitis AI Engine: Relatório de rastreamento, violação de acesso à memória e detecção de deadlock

- Aprimoramento de qualidade dos resultados, temporização e EoU do Vitis HLS, APIs do HLS para inferência de burst controlada pelo usuário

- Vitis Analyzer aprimorado para melhor relatório de rastreamento de linha de tempo, visualização de dados, análise de parada

- Vitis XRT para múltiplos processos de mecanismo de IA e suporte a vários threads para controle de grafos do mecanismo de IA

- Vitis IDE e rastreamento de mecanismo de IA para suporte de emulação, emulação de SW para aplicativos de mecanismo de IA

- 39 novas bibliotecas de C/C++ em diversos domínios, abrangendo DSP, análise de dados, visão, compactação, banco de dados, grafos, segurança, com um total de mais de 1.000 funções de biblioteca, banco de dados, grafos, segurança, …

- Compositor de modelos Vitis

- 3 vezes o tempo de compilação/simulação, 7 vezes de redução no tempo de compilação com compilação paralela

- Novo fluxo de validação de hardware e cosimulação funcional aprimorada

Novidades no Vitis por categoria

Expanda as seções abaixo para saber mais sobre os novos recursos e aprimoramentos da plataforma de software AMD Vitis 2021.2. Para obter informações sobre plataformas compatíveis, comportamento alterado e problemas conhecidos, consulte as Notas da versão 2021.2 da plataforma de software Vitis para o Fluxo de aceleração de aplicativos e Fluxo de desenvolvimento de software incorporado.

Nota: As bibliotecas aceleradas do Vitis estão disponíveis como download separado. Elas podem ser baixadas do GitHub ou diretamente do Vitis IDE.

| Biblioteca | 2021.1 | 2021.2 | Novas funções em 21.2 |

|---|---|---|---|

| xf_blas | 167 | 167 | 0 |

| xf_codec | 3 | 3 | 0 |

| xf_DataAnalytics | 33 | 36 | 3 |

| xf_database | 62 | 65 | 3 |

| xf_compression | 78 | 93 | 15 |

| xf_dsp | 94 | 96 | 2 |

| xf_graph | 53 | 59 | 6 |

| xf_hpc | 37 | 37 | 0 |

| xf_fintech | 116 | 116 | 0 |

| xf_security | 135 | 140 | 5 |

| xf_solver | 11 | 11 | 0 |

| xf_sparse | 11 | 11 | 0 |

| xf_utils_hw | 55 | 57 | 2 |

| xf_opencv | 147 | 150 | 3 |

| total | 1002 | 1041 | 39 |

Nota: Para visão, basta contar o número de subpastas em L*/tests, porque cada API tem vários testes para diferentes tipos

Biblioteca Vitis Vision

- Lógica programável (PL)

- Processamento de imagens monocromáticas de ponta a ponta (ISP) com CLAHE TMO

- RGB-IR juntamente com o pipeline de processamento de imagem (ISP) RGB-IR

- Mapeamento global de tons (GTM) juntamente com um canal ISP usando GTM

| Novos recursos | Cat | Cliente/Estratégico | Segmentos | Descrição |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | Automotivo, ISM | •Suporte para demosaicking RGB-IR 4x4 •Principalmente para o sistema de monitoramento dentro da cabine •Câmera de vigilância com pouca luz |

| Mono (CCCC) | ISP | Estratégico | Automotivo, ISM, A&D | •Visão de máquina •Aplicações com pouca luz |

| Mapeamento global de tons (GTM) | ISP | Estratégico | Automotivo, ISM, A&D | •Melhor faixa dinâmica e contraste •Versão de custo mais baixo em comparação com mapeamento local de tons (LTM) |

| Fluxo óptico denso TV-L1 | CV | NTT | ISM | •Maior robustez (contra iluminação, ruído, oclusões) para fluxo óptico |

Mecanismo de IA (AIE)

- BlobFromImage

- Filtro back to back 2D com suporte a três tamanhos de lote

| Novos recursos | Cat | Cliente/Estratégico | Segmentos | Descrição |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | Automotivo, ISM | •Suporte para demosaicking RGB-IR 4x4 •Principalmente para o sistema de monitoramento dentro da cabine •Câmera de vigilância com pouca luz |

| ML+X | ISP | Estratégico | Automotivo, ISM, A&D | •Pré-processamento de interferência ML |

| Pirâmide gaussiana | CV | Estratégico | Automotivo, ISM, A&D | •Fundamental para o processamento de imagens em várias escalas |

| Filtro de caixa | CV | Estratégico | Automotivo, ISM, A&D | •Fundamental para suavização, filtro de baixa passagem |

Biblioteca de análise de dados do Vitis

- Solução de blockchain do Vitis baseada em bibliotecas do Vitis

- Soluções de mineração prontas para uso para Ethereum

- Código-fonte aberto e fácil de usar e implantar com as bibliotecas do Vitis usando C++

- Flexível e dimensionável com as bibliotecas do Vitis

- Seja flexível para minerar várias moedas

- Personalize e compile em hardware

- Projeto altamente otimizado

- Adicionando a API do analisador CSV à biblioteca

- O analisador CSV pode analisar arquivos de valor separados por vírgula e gerar fluxo de objetos que pode ser facilmente conectado com as APIs do DataFrame

Biblioteca de grafos do Vitis

- Novas bibliotecas L2 adicionadas

- Louvain com renumeração

- Renumeração

- O recurso "peso" é compatível com Cosine Similarity

Biblioteca de banco de dados do Vitis

- O GQE começa a suportar o recurso de entrada/saída assíncrona, juntamente com o suporte a várias placas.

- O suporte assíncrono permitirá que a FPGA comece a processar assim que parte dos dados de entrada estiver pronta.

- O suporte para várias placas permite identificar várias placas Alveo adequadas para o trabalho.

Biblioteca de compactação de dados do Vitis

- Compactação ZSTD multinúcleo

- Foi criada uma nova arquitetura ZSTD multinúcleo e foi fornecido uma produtividade >1 GB/s usando quad-core.

- Otimização da descompactação ZSTD

- Descompactação ZSTD otimizada para desempenho (aumentada em 20%) e recursos (reduzida < 30%)

- Aprimoramento do núcleo de fluxo do GZIP/ZLIB para IBM

- IP de transmissão de compactação estática e dinâmica personalizada (4 KB e 8 KB)

- Funcionalidade adicionada para fornecer tamanho compactado na porta TUSER

- Aprimoramento na descompactação do GZIP/ZLIB para IBM

- Decodificador huffman otimizado para reduzir a latência para < 1,5K ciclos

- Redução significativa dos recursos para 6,9K (antigo > 9K)

- Adicionada a funcionalidade Checksum ADLR32

- Compilador de sistema GZIP PoC

- Foi criado um PoC de compilador de sistema para solução GZIP Compress e comparado com o host OpenCL.

Biblioteca de DSP do Vitis

- DSPLib no GitHub desde 2021

- Fast Fourier Transform (FFT/iFFT)

- O tamanho do ponto aumenta para 32k (dependendo do tipo dos dados)

- Suporte para API de fluxo, bem como API de janela.

- Alimentação paralela (0-4)

- Permite uma maior produtividade e estende a faixa de tamanhos de pontos suportados

- Filtros FIR

- Suporte a fluxo inicial para FIR assimétrico/simétrico de taxa única

- DDS/Mixer

- Nova unidade de biblioteca em 2021.2

Biblioteca de segurança do Vitis

- KECCAK-256 (função hash) e CRC32C (função de soma de verificação) são lançados

Biblioteca de utilitários do Vitis

- Implementação de dois movimentadores de dados adicionada para depurar problemas de hardware.

- LoadDdrToStreamWithCounter: Para carregar dados DDR da PL para o mecanismo de IA por meio de AXI-stream e registrar o envio de contagem de dados para o mecanismo de IA.

- StoreStreamToMasterWithCounter: Para receber dados do mecanismo de IA por meio de AXI-stream e salvá-los na DDR da PL, bem como gravar o envio de contagem de dados para DDR.

API do mecanismo de IA

- Implementada como uma biblioteca somente de cabeçalho C++ que fornece tipos e operações que são traduzidos em intrínsecos eficientes do mecanismo de IA.

- Fornece tipos de dados parametrizáveis que possibilitam a programação genérica

- Implementa as operações mais comuns de maneira uniforme para diferentes tipos de dados

- Traduz de forma transparente primitivas de nível superior em intrínsecos otimizados do mecanismo de IA

- Melhora a portabilidade entre arquiteturas do mecanismo de IA

A API do mecanismo de IA será o método principal para a programação do kernel do mecanismo de IA

Otimizações de alto nível

Opções de otimização do compilador do mecanismo de IA

- --xlopt=0, nenhuma otimização aplicada.

- --xlopt=1, computação automática do tamanho do heap, geração de orientação da análise de IR LLVM.

- --xlopt=2, inlining automático, loop peeling para loops desenrolados, inserção de pragma.

Apresentamos o --xlopt=2 para melhorar o desempenho, o padrão permanece --xlopt=1

- Inline automático

- Os inlines automáticos funcionam se for prático e possível fazê-los, mesmo que as funções não sejam declaradas como __inline ou inline

- Inserção automática de pragma

- Insira pragmas para o código do kernel automaticamente. (consulte o próximo slide para obter mais detalhes)

Inferência de pragma

Necessário para otimizar os kernels

- Alivie a responsabilidade do usuário de adicionar pragmas de xadrez eficazes e corretos

Suporte para inferir automaticamente cinco pragmas em 2021.2

- para desempenho:

- chess_prepare_for_pipelining para loop mais interno e loops externos com contagem de viagens conhecida

- chess_loop_range para loops com contagem de viagens conhecida

- chess_unroll_loop/chess_planate_loop para loops mais internos com contagem de viagens conhecida

- para correção:

- chess_unroll_loop_preamble quando a contagem de viagens não é um múltiplo do fator unroll

Atualização de OPIO e GMIO do modelo de programação de grafos

As alterações de modelo incluem:

- Alterações no uso de "simulation::platform"

- Interação com objetos OPIO/GMIO no grafo, a posição determina a entrada/saída.

- Alterações de objetos OPIO/GMIO globais no grafo.

- Alterações em torno das instruções de conexão do grafo<>.

PLIO/GMIO em grafos ADF

Atual

- Escreva PLIO, GMIO, simulation::platform e conexões no escopo global

GMIO gm0(“GMIO_In0”, 64, 1);

GMIO gm1(“GMIO_In1”, 64, 1);

…

GMIO gm7(“GMIO_In7”, 64, 1);

PLIO pl0(“PLIO_Out0”, plio_32_bits, “data/output0.txt”, 250.0);

PLIO pl1(“PLIO_Out1”, plio_32_bits, “data/output1.txt”, 250.0);

…

PLIO pl7(“PLIO_Out7”, plio_32_bits, “data/output7.txt”, 250.0);

simulation::platform<8,8> plat(&gm0, &gm1,…, &gm7, &pl0, &pl1,…, &pl7,);

subgraph g;

connect<> net0(plat.src[0], g.in[0]);

connect<> net1(plat.src[1], g.in[1]);

…

connect<> net7(plat.src[7], g.in[7]);

connect<> net8(g.out[0], plat.sink[0]);

connect<> net9(g.out[1], plat.sink[1]);

…

connect<> net15(g.out[7], plat.sink[7]);

Método alternativo

- Crie um grafo de nível superior e mova OPIO, GMIO e conexões para dentro

- Permita o gerenciamento de conexões para loop

class topgraph

{

input_gmio gm[8];

output_plio pl[8];

subgraph sg;

topgraph()

{

for (i=0; i<8; i++)

{

gm[i] = input_gmio::create(“GMIO_In”+std::to_string(i), 64, 1);

pl[i] = output_plio::create(“PLIO_Out”+std::to_string(i), plio_32_bits, “data/output”+std::to_string(i)+”.txt”, 250.0);

connect<>(gm[i].out[0], sg.in[i]);

connect<>(sg.out[i], pl[i].in[0]);

}

}

};

topgraph g;

Aprimoramentos nas restrições do grupo de área

Capacidade de usar sinalizadores no grafo ADF ou no arquivo de restrições para controlar o mapeador e o roteador

- -contain_routing — quando especificado como verdadeiro, garante que todo o roteamento, incluindo redes entre nós contidos no nodeGroup, esteja contido no grupo de área.

- -exclusive_routing — quando especificado como verdadeiro, garante que todo o roteamento, excluindo redes entre nós do nodeGroup, seja excluído do grupo de área.

- -exclusive_placement — quando especificado como verdadeiro impede que todos os nós não incluídos no nodeGroup sejam colocados dentro da caixa delimitadora do grupo de área.

Snapshots

Snapshots são arquivos de texto que contêm comentários e dados relativos a todas as portas do kernel

- fluxos, fluxos de pacotes, fluxos em cascata

- janelas, buffer

- RTP

Inclui também todas as portas de plataforma

- PLIO, GMIO, RTP

Permite que os usuários inspecionem o tráfego de dados nas portas do kernel sem usar o depurador e sem exigir a instrumentação do código do kernel

Detecção de deadlock

- Detecta deadlocks em simulações x86, seja porque essa situação surge de dados de entrada insuficientes ou de uma profundidade FIFO desequilibrada em um caminho reconvergente

- O recurso stop-on-deadlock deve ser ativado durante a simulação x86 especificando a opção --stop-on-deadlock

- Se a simulação for interrompida devido a um deadlock, a mensagem de erro indica que você deve executar novamente com a opção -trace --timeout

Detecção de violação de acesso à memória

Integração com Valgrind para detecção de violação de acesso à memória

- Detecta

- leitura e gravação fora dos limites

- leitura de memória não inicializada

- Nenhum sinalizador específico é necessário para a compilação

- Os sinalizadores de simulação podem ser

- --valgrind : a simulação é executada normalmente e valgrind exibe um relatório

- --valgrind-gdb : a mesma coisa, mas com depuração gdb ao mesmo tempo

Relatório de rastreamento

A situação de deadlock resulta em saída de simulação ruim e dificuldades para analisar a origem do bug

A opção de rastreamento de simulação x86 permite que o simulador registre várias informações com carimbo de data/hora:

- Início/fim das iterações do kernel

- Início/fim das paralisações de fluxo

- Início/fim da paralisação de bloqueio

Os carimbos de data e hora são diferentes entre a simulação do x86 e a simulação do mecanismo de IA

Inferência de burst controlada pelo usuário

- Para casos de uso que não satisfazem a inferência de burst automática pela ferramenta Vitis HLS, o usuário pode adotar a otimização de burst manual recém-introduzida

- Uma nova classe "hls::burst_maxi" para suportar o controle manual do comportamento de burst. Novas APIs de HLS são fornecidas para uso com a nova classe

- O usuário precisa entender o protocolo AXI AMBA e a modelagem em nível de transação de hardware no projeto de HLS

Aprimoramentos de temporização e de Qualidade dos resultados

- Fornece suporte para usuário inserir restrições de produtividade de alto nível

- Melhora a precisão da estimativa de temporização de HLS. Quando a HLS relata o encerramento de temporização, a síntese de RTL no Vivado também deve esperar cumprir a temporização

Aprimoramentos de EoU

Adicione o relatório de adaptadores de interface nos relatórios de Síntese em C

- Os usuários precisam saber o impacto dos recursos que os adaptadores de interface têm em seu projeto

- Os adaptadores de interface têm propriedades variáveis que afetam a QoR do projeto

- Algumas dessas propriedades têm controles de usuário associados que devem ser relatados aos usuários

- A versão em texto dos relatórios bind_op e bind_storage é fornecida

Adicione uma nova seção ao relatório de síntese para mostrar a lista de pragmas e advertências sobre pragmas

- O usuário pode entender facilmente quais dos pragmas adicionados apresentam problemas.

Aprimoramentos de análise e geração de relatórios

O Function Call Graph Viewer tem alguns recursos novos

- Nova capacidade de aumentar e diminuir o zoom baseada em arrastar do mouse

- Novo recurso de visão geral que mostra o gráfico completo e permite que o usuário aumente o zoom em partes do gráfico geral

- Todas as funções e loops são mostrados junto com seus dados de simulação

Um novo Timeline Trace Viewer agora está disponível após a simulação. Este visualizador mostra o perfil de tempo de execução do seu projeto e permite que o usuário permaneça na GUI do Vitis HLS.

Aprimoramento do resumo do link

- Fornece informações sobre a frequência do clock para o mecanismo de IA, plataforma e unidades de computação

- Fornece uma nova tabela chamada Clocks no diagrama do sistema e no diagrama da plataforma

Aprimoramento de exportação de plataforma

- Exportação XSA do Vivado, sem necessidade de ter arquivos gravados localmente no projeto

- Exportação XSA do Vivado sem alteração na estrutura do projeto

- Empacote os IPs que são usados no projeto da plataforma de hardware em vez de empacotar todo o repositório de IP

Aprimoramentos na emulação de aplicativos do mecanismo de IA

- Fornece suporte para integração de testbench externo com simulação AIE

- Fornece suporte para integração de testbench externo com simulação do x86

- Suporte para depuração GDB com simulação do x86

- Fornece suporte para instantâneos dos dados entre kernels em um grafo para simulação do x86

- Fornece suporte para verificação de violação de acesso para simulação do x86

- Fornece suporte para parada em deadlock para x86sim

Suporte para rastreamento do mecanismo de IA

Suporte à emulação de software para aplicativos do mecanismo de IA

Suporte para gerador de tráfego externo no Verilog/System Verilog

Estenda a inserção do monitor de perfil para a memória do monitor

- Atualmente, a lógica do monitor de criação de perfil pode ser inserida na base da porta CU/kernel. Esse recurso fornece ao usuário a opção de inserir a lógica do monitor diretamente na interface de memória

- A visualização da largura de banda de memória obtida diretamente nas interfaces de memória pode ser refletida no relatório de resumo de perfil

- Há suporte para memória DDR e PLRAM

- O fluxo de hardware é permitido

- Para ativar esse recurso, tanto a fase de vinculação quanto o xrt precisam ser configurados

- memory=all

- data_transfer_trace= coarse|fine ou

- opencl_device_counter=true

Estenda a inserção do monitor de perfil para a memória do monitor

- Um exemplo vadd que possibilita o monitoramento da interface de memória

- Uma nova tabela "Transferência de dados do banco de memória" foi incluída

Aprimoramentos no Vitis Analyzer

Relatório de resumo de perfil genérico gerado para aplicativos não OpenCL

- Fornece o mesmo nível de suporte para aplicativos API XRT e API HAL.

- Os usuários selecionam os tipos de relatórios que desejam criar, a ferramenta gera e visualiza automaticamente os relatórios no Vitis Analyzer

Adicione comandos OpenCL à linha do tempo do evento PL

- A criação de perfil adicionará sobrecarga, enquanto o XRT possibilita despejar os eventos do OpenCL no rastreamento da linha do tempo sem sobrecarga.

- O Vitis Analyzer pode processar a saída do XRT e mostrá-la na visualização do rastreamento da linha do tempo.

- xocl_debug=verdadeiro, precisa ser definido no xrt.ini.

Nivelar hierarquia de sinal no relatório de rastreamento da linha do tempo

- Por padrão, o relatório de rastreamento de linha do tempo exibe o rastreamento de sinal de forma hierárquica

- O Vitis Analyzer fornece a capacidade de nivelar a hierarquia, alternando o símbolo "Nivelar sinal"

- A comparação da forma de onda é compatível com o rastreamento nivelado de linha do tempo

Vitis Analyzer — Visualização de dados

- Exibe dados de entrada/saída para os kernels do mecanismo de IA em um projeto do mecanismo de IA

- Ajuda a depurar os projetos do mecanismo de IA para mostrar dados de entrada/saída junto com a linha do tempo

- Funciona com o aiesimulator

- Compatível com

- Tipos de dados de janela/fluxo/cascata

- Fluxos de pacotes

- Kernels padronizados

- utilitário de despejo de dados

Vitis Analyzer — Análise de paralisação do mecanismo de IA

- O Vitis Analyzer oferece recursos de visualização para que os usuários identifiquem a causa principal das paralisações

- Suporte

- Métricas de desempenho

- Análise de paralisação de bloqueio

- Análise de paralisação de fluxo

- Análise de paralisação de cascata

- Análise de paralisação de memória

- Fluxo de suporte

- aiesimulator

- Emulação de HW

Biblioteca de tempo de execução Xilinx (XRT):

- API XRT

- A API nativa do XRT oferece suporte ao controle do kernel gerenciado pelo usuário com xrt::ip

- Utilitários do XRT

- As ferramentas xbutil e xbmgmt agora se tornam padrão

- Para usar os utilitários legados, use xbutil --legacy ou xbmgmt --legacy com subcomandos legados

- Novo utilitário, xball

- Aplique os comandos xbutil ou xbmgmt a todas ou a uma parte filtrada das placas de data center instaladas. Consulte xball --help para obter detalhes

- Um novo comando, xbutil configure

- Permite habilitar, desabilitar ou configurar os recursos PCIe Host Memory e PCIe Peer to Peer. Ver a documentação do XRT para obter mais detalhes

- Todos os utilitários do XRT agora oferecem suporte global à opção --force para pular a confirmação interativa do usuário

- As ferramentas xbutil e xbmgmt agora se tornam padrão

- Criação de perfis

- Um relatório de resumo do perfil é gerado quando qualquer opção de criação de perfil é ativada.

- Todas as tabelas de resumo e orientações aplicáveis são geradas com base nas opções de criação de perfil ativadas no arquivo xrt.ini

- Nova tabela de resumo de transferência de dados para informações agregadas em um recurso de memória quando monitores são adicionados a recursos de memória no projeto

- Novos conjuntos de métricas de criação de perfil AIE para contar diferentes eventos do AIE, incluindo (1) exceções de ponto de flutuação no AIE, (2) contagens de execução de blocos e (3) puts e gets de fluxo

- Incorporado

- aprimoramentos no gerenciador de memória zocl para oferecer suporte a qualquer sptag

Suporte Vitis XRT para mecanismo de IA de vários processos

- APIs C e C++ para definir modos de acesso para vários processos para compartilhar o acesso à mesma matriz e grafos do mecanismo de IA.

- ¬Proteja os grafos e matriz do mecanismo de IA contra acesso indesejado.

- Três modos são compatíveis para abrir grafos e matriz do mecanismo de IA

- Modo exclusivo (impede que outros processos acessem)

- Modo primário (permite que apenas outros processos façam acesso não destrutivo)

- Modo compartilhado (faz apenas acesso não destrutivo)

- Leve em consideração quando é necessário suporte a vários processos. Por exemplo:

- Impedir que outros acessem a matriz do mecanismo de IA (acesso exclusivo)

- Vários usuários para controlar diferentes grafos separadamente (suporte a vários aplicativos)

- Um usuário principal para controlar o grafo e permitir que outros investiguem o status de execução (acesso primário e compartilhado)

Status do suporte do Vitis XRT para mecanismo de IA

APIs C e C++

- API da versão C

- Para matriz do mecanismo de IA:

- xrtAIEDeviceOpenExclusive (Modo exclusivo)

- xrtAIEDeviceOpen (Modo primário)

- xrtAIEDeviceOpenShared (Modo compartilhado)

- Para grafo do mecanismo de IA:

- xrtGraphOpenExclusive (Modo exclusivo)

- xrtGraphOpen (Modo primário)

- xrtGraphOpenShared (Modo compartilhado)

- Para matriz do mecanismo de IA:

- API da versão C++

- Modo de acesso ao suporte de classe xrt::aie::device no construtor

- enum class access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2 };

- Modo de acesso ao suporte de classe xrt::graph no construtor

- enum class access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2, none = 3 };

- Modo de acesso ao suporte de classe xrt::aie::device no construtor

- Acesse as Plataformas de destino mais recentes do Vitis para Placas Alveo e consulte a seção Introdução da placa aceleradora.

- Baixe o Vitis e consulte a seção Pacotes Alveo

Biblioteca de DSP de AI Engine — Novo blocos

- DDS AIE

- Mixer AIE

Compilação paralela

- Tempos reduzidos em comparação com a versão 2021.1 (Por exemplo, os seguintes números são para a Cadeia TX de 200 MHz):

- Tempo para compilação e simulação reduzido pelo fator 3

- Tempos de compilação reduzidos por um fator de 7

- Tempo morto após simulação reduzido de 25 s para ~0 s

Aprimoramento do editor de restrições

- Navegação aprimorada na versão 2021.2

Para aprimoramentos de tamanho fixo

Para aprimoramentos de bloco de tamanho variável

Capacidades avançadas de co-simulação funcional

- Exportar dados do Matlab para entrada do mecanismo de IA — xmcVitisWrite

- Importar dados do mecanismo de IA para Matlab — xmcVitisRead

- Importar dados do mecanismo de IA para Matlab — xmcVitisRead

Outros

- Importar um mecanismo de IA ou bloco do kernel de HLS sem entrada (bloco de origem)

- Novo suporte para tipos de dados

- o Simulink nativo int64 e uint64 para desenvolvimento do mecanismo de IA em vez de tipos de dados AMD, x_sfix64 e x_ufix64.

- accfloat e caccfloat para desenvolvimento do mecanismo de IA

- Suporte para Ubuntu 20.04

- Suporte para MATALB 20a, 20b, 21a (Sem suporte para MATLAB 21b)

- Adição de novos exemplos

- Exemplo de filtro SSR de fluxo duplo com 64 kernels

- Pseudo-inverso(64x32) — exemplo commslib.

- Use o comando xmcLibraryPath para apontar para um local DSPLib personalizado.

- Muitos outros aprimoramentos e correções de bug

Destaques da versão 2021.1 da plataforma de software Vitis:

- Suporte ao kit inicial do Vision AI KV260 dos Sistemas nos módulos (SOMs) Kria da AMD. O fluxo completo do Vitis para ML (mecanismo de inferência DPU) + X (kernel RTL e kernels de visão computacional baseados em Vitis HLS). Saiba mais >

- Suporte para nova C/C++ Vision, DSP, Grafo (Louvain Modularity), Codec em processamento de imagem, compactação (GZIP, Facebook ZSTD, toda a aceleração de aplicativos ZLIB) bibliotecas otimizadas para desempenho na FPGA e/ou ACAP Versal em CPU/GPUs

- Fluxo de projeto avançado do kit de desenvolvimento básico do Vitis™ em dispositivos ACAP Versal: aprimoramentos de visualização para relatório de rastreamento de projeto do mecanismo de IA, rastreamento de eventos do mecanismo de IA via GMIO, recompilação incremental, novo assistente de imagem de inicialização e suporte ao arquivo de origem do mecanismo de IA criptografado

- A nova ferramenta Vitis Model Composer permite a rápida exploração e verificação de projetos no ambiente MathWorks MATALB e Simulink®, permitindo a cossimulação de blocos direcionados a mecanismos de IA e lógica programável, geração de código e criação de testbench.

- Nova GUI do Navegador de fluxo do Vitis HLS para acesso rápido às fases de fluxo e relatórios. Mesclar visualizações de síntese, análise e depuração em um contexto padrão geral

Novidades no Vitis por categoria

Expanda as seções abaixo para saber mais sobre os novos recursos e aprimoramentos da plataforma de software AMD Vitis 2021.1. Para obter informações sobre plataformas compatíveis, comportamento alterado e problemas conhecidos, consulte as Notas da versão 2021.1 da plataforma de software Vitis para o Fluxo de aceleração de aplicativos e Fluxo de desenvolvimento de software incorporado.

Nota: As bibliotecas aceleradas do Vitis estão disponíveis como download separado. Elas podem ser baixadas do GitHub ou diretamente do Vitis IDE.

DSP AIE

- DSPLib publicado como parte do conjunto de Bibliotecas de aceleração do Vitis no GitHub

- O DSPLib contém funções de DSP parametrizáveis comuns usadas em muitas aplicações avançadas de processamento de sinal. Todas as funções atualmente oferecem suporte a interfaces de janela com suporte a interface de streaming.

Filtros FIR

Função |

Namespace |

Taxa única, assimétrica |

dsplib::fir::sr_asym::fir_sr_asym_graph |

Taxa única, simétrica |

dsplib::fir::sr_sym::fir_sr_sym_graph |

Interpolação assimétrica |

dsplib::fir::interpolate_asym::fir_interpolate_asym_graph |

Decimação, meia-banda |

dsplib::fir::decimate_hb::fir_decimate_hb_graph |

Interpolação, meia-banda |

dsplib::fir::interpolate_hb::fir_interpolate_hb_graph |

Decimação, assimétrica |

dsplib::fir::decimate_asym::fir_decimate_asym_graph |

Interpolação, fracionária, assimétrica |

dsplib::fir::interpolate_fract_asym:: fir_interpolate_fract_asym_graph |

Decimação, simétrica |

dsplib::fir::decimate_sym::fir_decimate_sym_graph |

FFT/iFFT — O DSPLib contém uma solução FFT/iFFT. Esta é uma implementação de um único canal, decimação no tempo (DIT) de kernel único, com tamanho de ponto configurável, tipos de dados complexos, comprimento em cascata e função FFT/iFFT.

Função |

Namespace |

FFT/iFFT de canal único |

dsplib::fft::fft_ifft_dit_1ch_graph |

Multiplicação de matriz (GeMM) - O DSPLib contém uma solução de Multiplicação de matriz/GEMM (Multiplicação geral da matriz). Isso atende à Multiplicação de matriz de 2 matrizes A e B com tipos de dados de entrada configuráveis, resultando em um tipo de dados de saída derivado.

Função |

Namespace |

Mult. de matrix/GeMM |

dsplib::blas::matrix_mult::matrix_mult_graph |

Utilitários de widget — Esses widgets permitem a conversão entre janela e fluxos na entrada para a função DSPLib e entre fluxos para janelas na saída da função DSPLib, onde desejado, e widget adicional para conversão entre tipos de dados reais e complexos.

Função |

Namespace |

Fluxo para janela/janela para fluxo |

dsplib::widget::api_cast::widget_api_cast_graph |

Real para complexo/complexo para real |

dsplib:widget::real2complex::widget_real2complex_graph |

As funções da biblioteca de DSP são compatíveis com o Vitis Model Composer, permitindo que os usuários conectem facilmente essas funções ao ambiente Matlab/Simulink para facilitar a avaliação da Biblioteca DSP do mecanismo de IA e o desenvolvimento geral do grafo ADF do mecanismo de IA.

O lançamento da Biblioteca Vitis HPC apresenta primitivas de HLS, kernles pré-criados e APIs de software para aplicativos de HPC nas FPGAs. Esses aplicativos são:

Algoritmo FDTD (Domínio de tempo de diferença finita) RTM (Migração reversa de tempo) acústico 2D, incluindo kernel forward e kernel backward

Algoritmo FDTD (Domínio de tempo de diferença finita) RTM (Migração reversa de tempo) acústico 3D, incluindo kernel forward

Componentes MLP (Perceptron de múltiplas camadas): funções de ativação e kernels de rede totalmente conectados

Solvers PCG (Gradiente conjugado pré-condicionado) para matriz densa e matriz esparsa

- Primeira versão das funções de visão selecionadas para mecanismos de IA do Versal:

Funções disponíveis

Filter2D

absdiff

accumulate

accumulate_weighted

addweighted

blobFromImage

colorconversion

convertscaleabs

erode

gaincontrol

gaussian

laplacian

pixelwise_mul

threshold

zero

xfcvDataMovers: Datamovers de utilitários para facilitar a exibição em bloco de imagens de alta resolução e a transferência para a memória local dos núcleos dos mecanismos de IA. Dois tipos

- Usando o kernel de PL: maior produtividade à custa de recursos de PL adicionais.

- Usando GMIO: menor produtividade do que a versão do kernel de PL, mas usa NoC (Rede em chip) Versal e nenhum recurso de PL.

- Novos recursos e funções de lógica programável (PL)

- Funções e pipeline do ISP:

- Pipeline não HDR atualizado em 2020.2

- Suporte para alterar alguns dos parâmetros do ISP no tempo de execução: parâmetros de ganho para canais vermelho e azul, opção de ativação/desativação de AWB, tabelas gama para R,G,B, %pixels para calcular mín. e máx. para normalização de awb.

- Gamma Correction e conversão do espaço de cores (RGB2YUYV) fizeram parte do pipeline.

- Novo pipeline HDR 2021.1: Suporte a Pipeline + HDR 2020.2

- Mesclagem HDR para 2 exposições que suporta sensores com sobreposição digital entre frame de exposição curta e frame de exposição longa.

- Quatro padrões Bayer compatíveis: RGGB,BGGR,GRBG,GBRB

- Mesclagem HDR + pipeline isp com configurações de tempo de execução, que retorna a saída RGB.

- Função de extração: A função de extração HDR é a função de pré-processamento, que utiliza um único fluxo digital sobreposto como entrada e retorna os 2 frames de exposição de saída (SEF, LEF).

- Mesclagem HDR para 2 exposições que suporta sensores com sobreposição digital entre frame de exposição curta e frame de exposição longa.