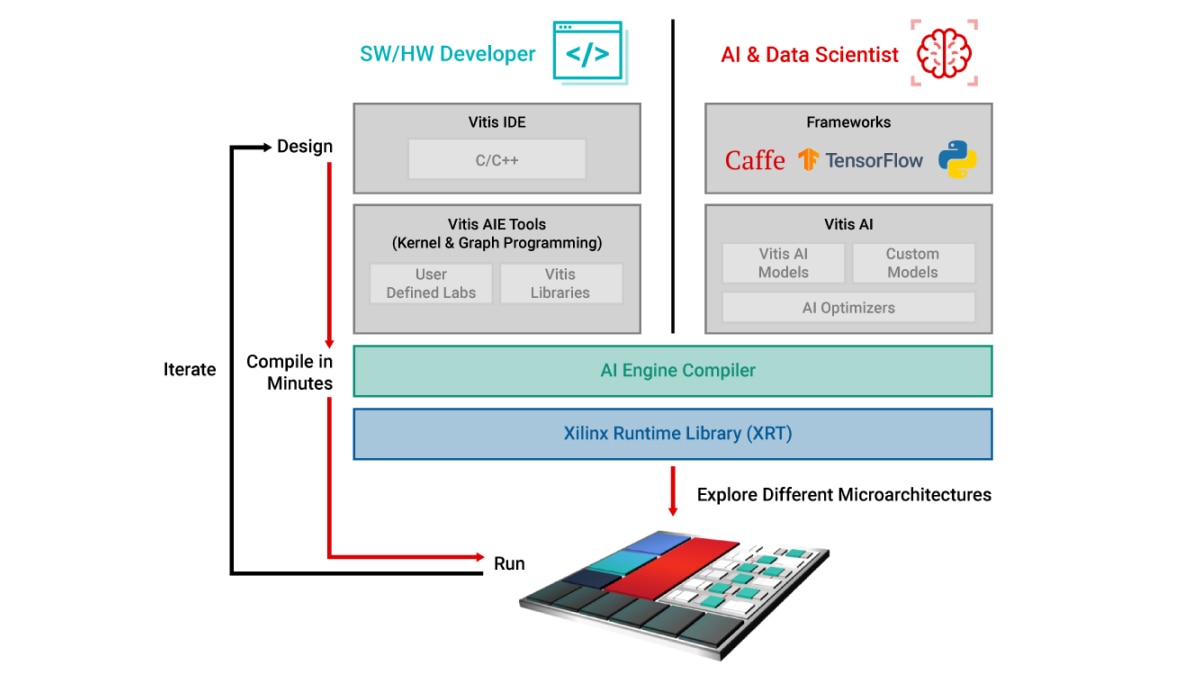

Programação do fluxo de dados para o desenvolvedor de software/hardware

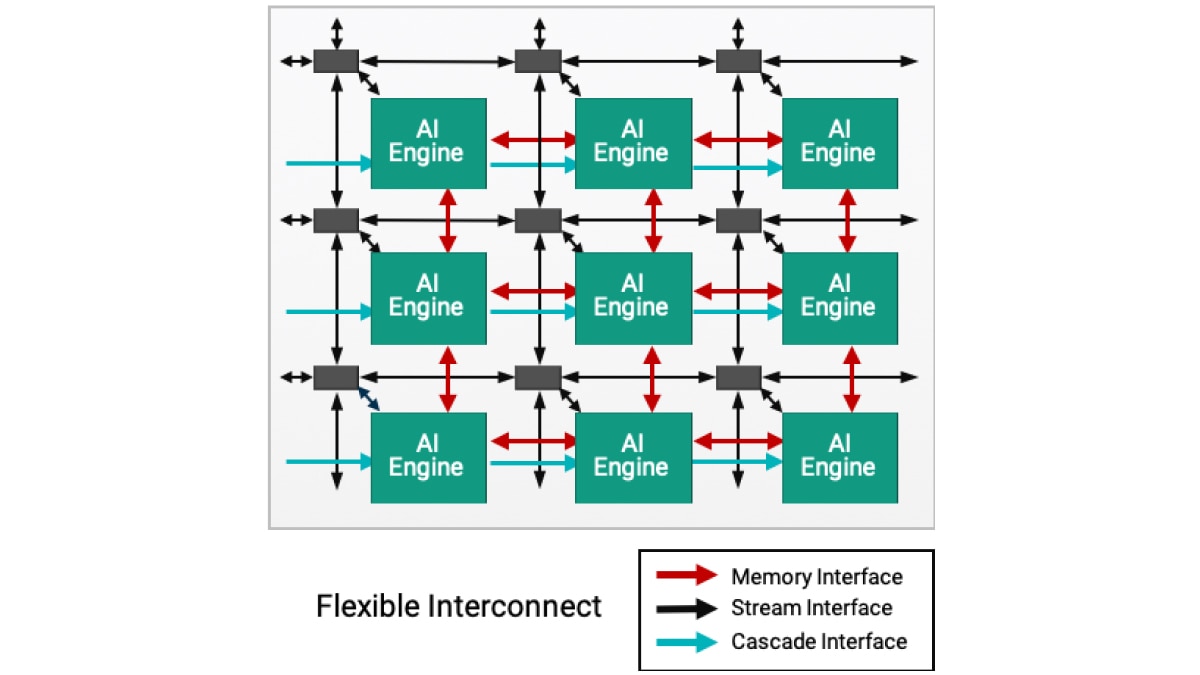

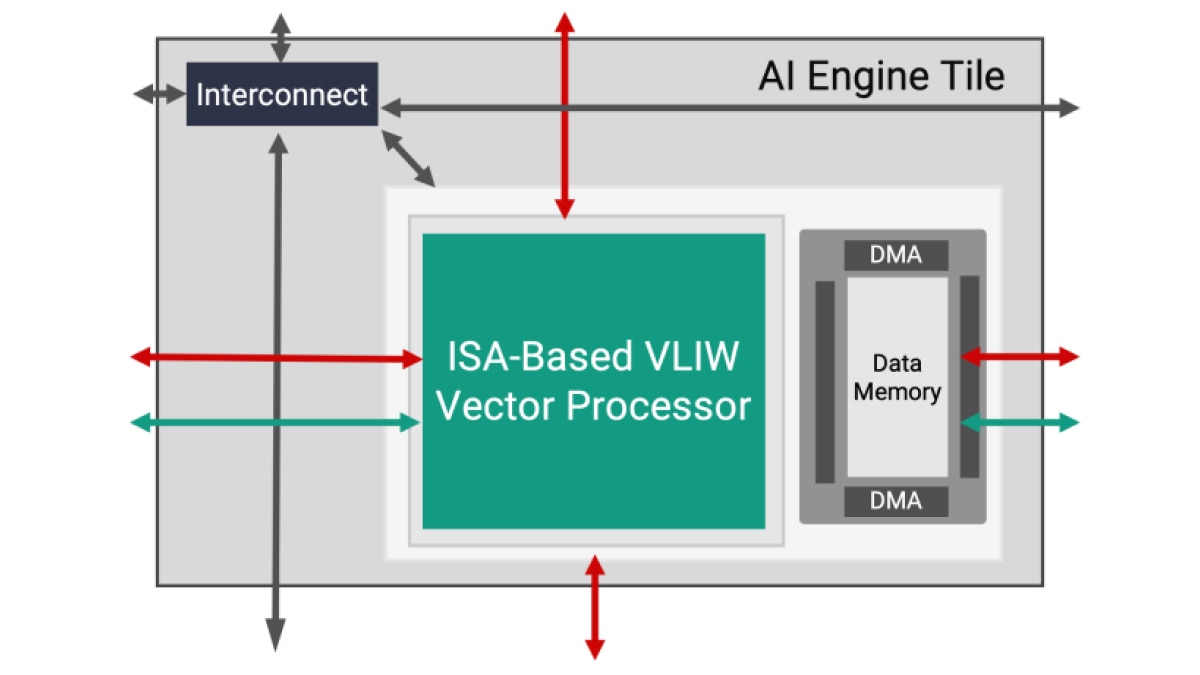

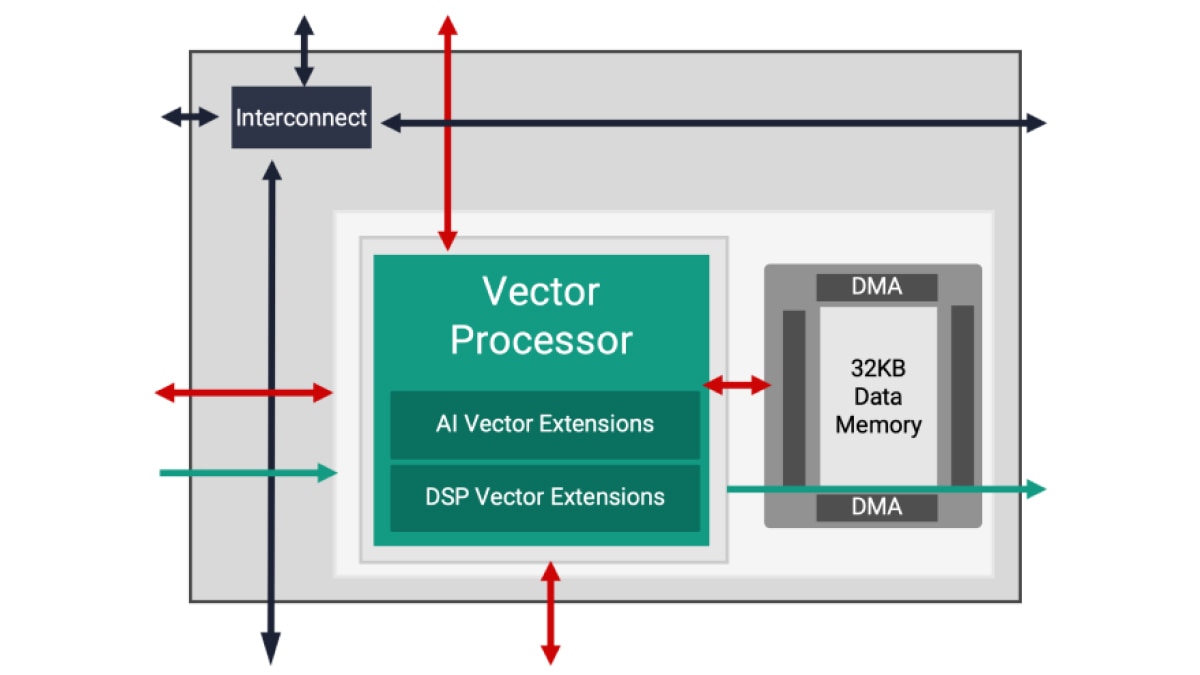

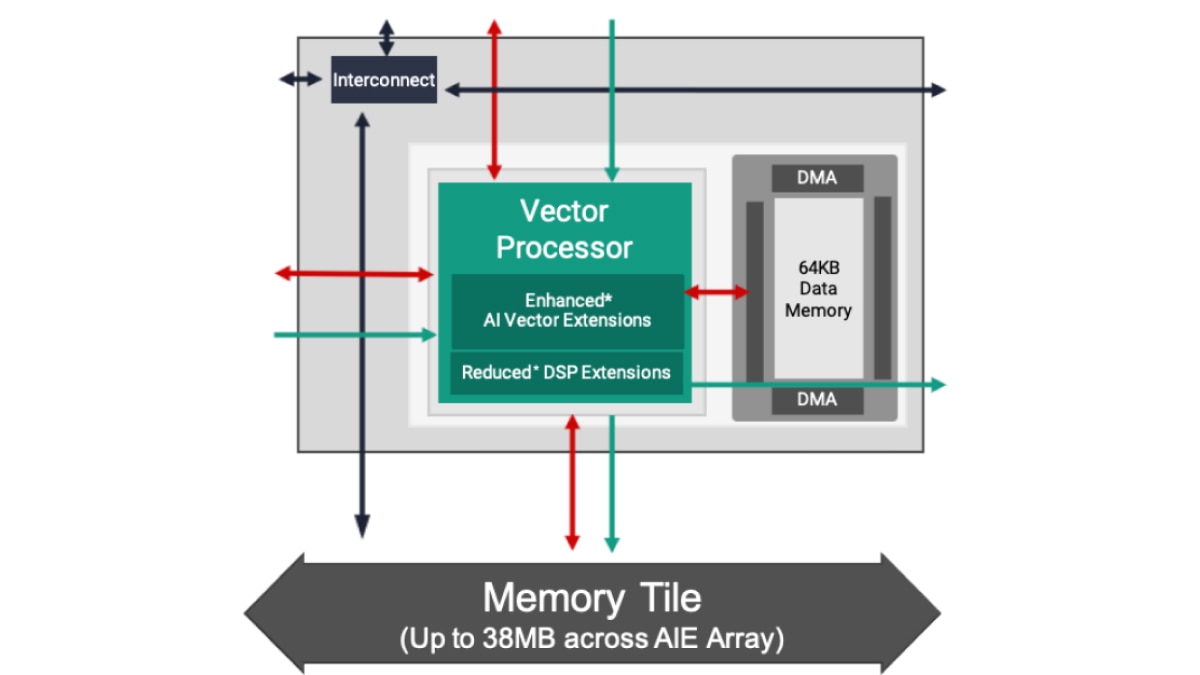

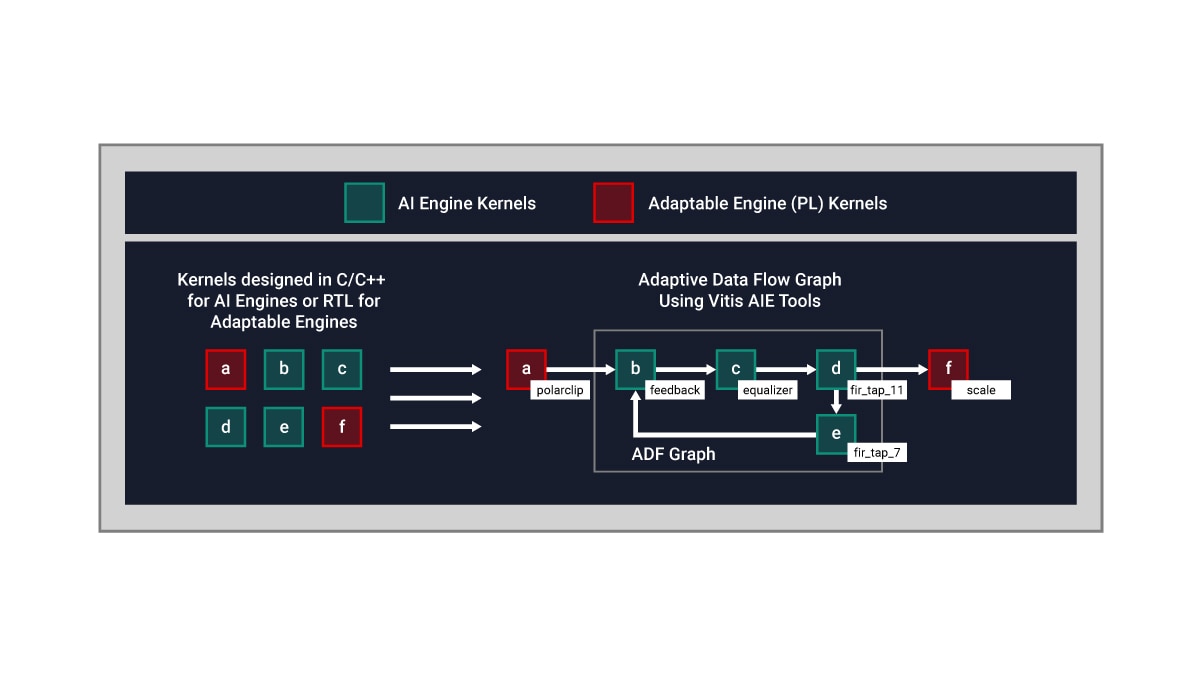

A arquitetura do mecanismo de IA é baseada em uma tecnologia de fluxo de dados. Os elementos de processamento são fornecidos em matrizes de 10 a 100 blocos, criando um único programa em todas as unidades de computação. Para um projetista, incorporar diretivas para especificar o paralelismo entre esses blocos seria um processo tedioso e quase impossível. Para superar essa dificuldade, o projeto do mecanismo de IA é realizado em duas etapas: o desenvolvimento de um único kernel, seguido pela criação do gráfico de ADF (Adaptive Data Flow, Fluxo de dados adaptativo), que conecta múltiplos kernels em uma aplicação geral.

O Vitis Unified IDE oferece um único cockpit de IDE que permite o desenvolvimento de kernels do mecanismo de IA usando código de programação C/C++ e projeto de gráficos de ADF. Especificamente, os projetistas podem:

- Desenvolver kernels em C/C++ e descrever funções de computação específicas usando as bibliotecas Vitis

- Conectar kernels por meio de gráficos de ADF usando as ferramentas de mecanismo de IA Vitis

Por padrão, um único kernel é executado em um único bloco do mecanismo de IA. No entanto, vários kernels podem ser executados no mesmo bloco do mecanismo de IA, compartilhando o tempo de processamento que a aplicação permite.

Abaixo, um exemplo conceitual:

- Os kernels do mecanismo de IA são desenvolvidos em C/C++

- Os kernels em PL (Programmable Logic, Lógica programável) são escritos em RTL ou Vitis HLS (High Level Synthesis, Síntese de alto nível)

- O fluxo de dados entre kernels nos mecanismos de PL e IA é realizado por meio de um gráfico de ADF