Datenflussprogrammierung für den Software-/Hardwareentwickler

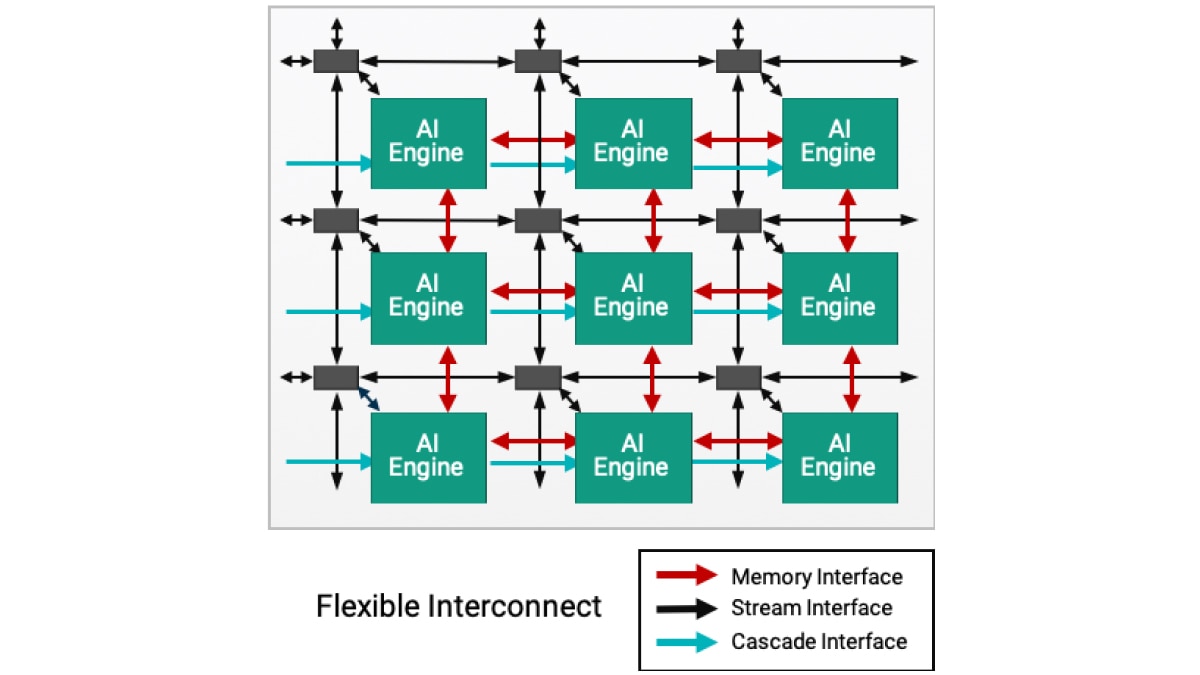

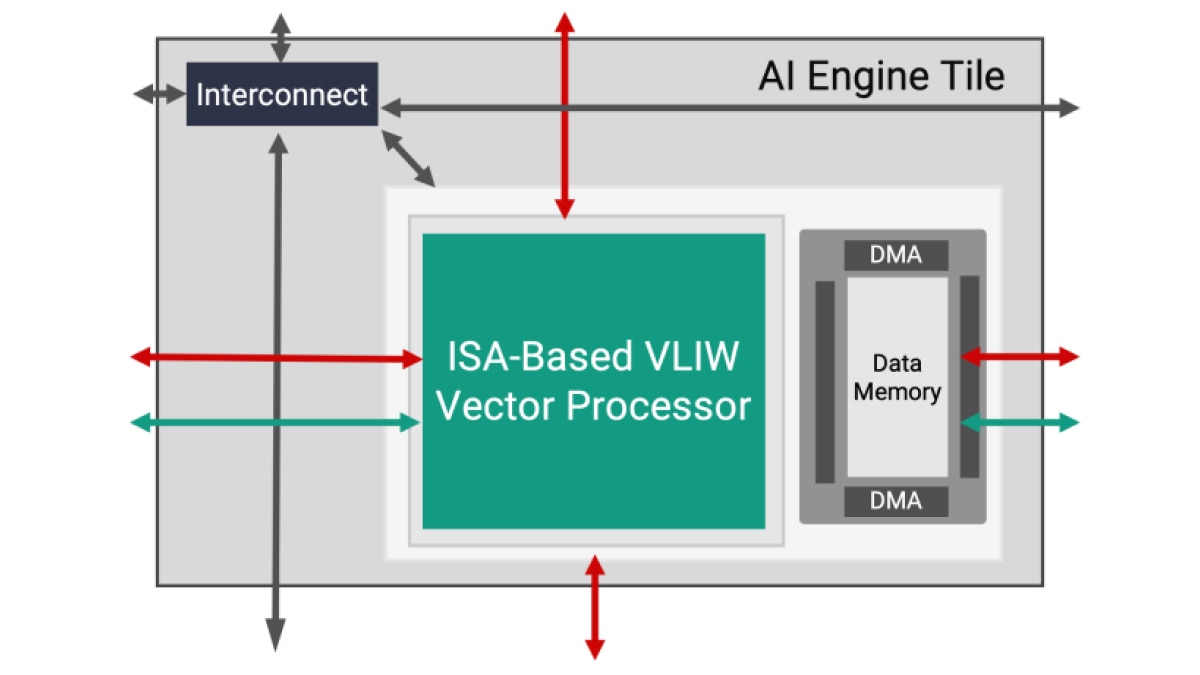

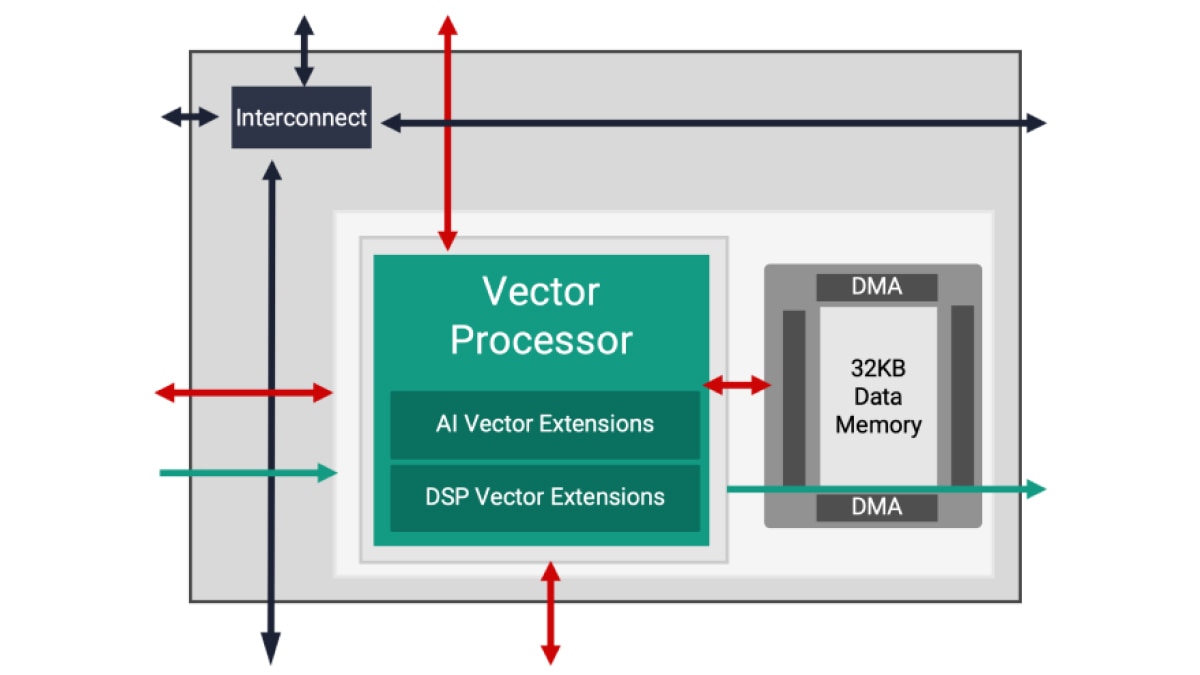

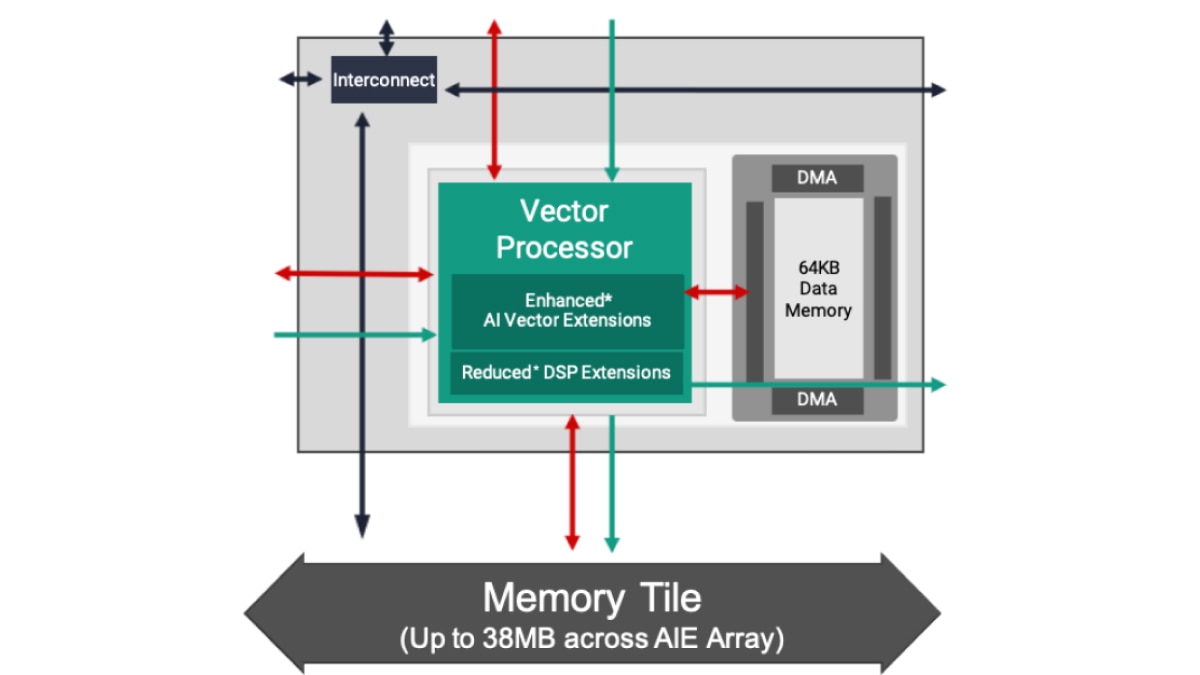

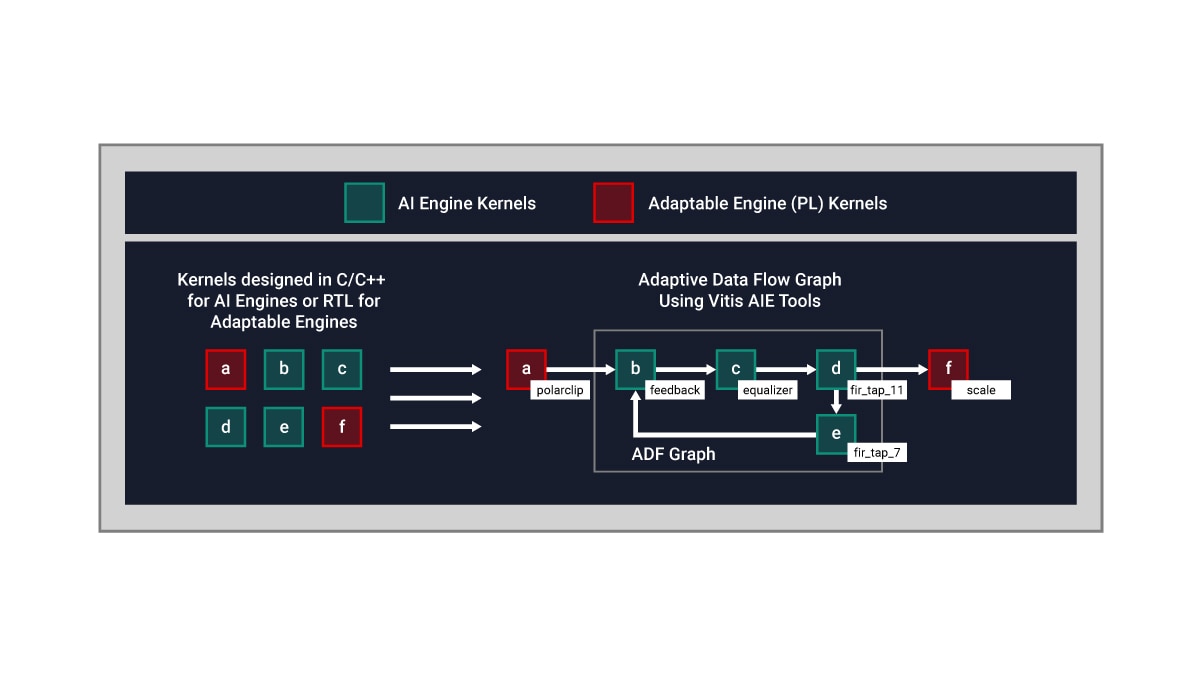

Die Architektur der KI-Engine basiert auf einer Datenflusstechnologie. Verarbeitungselemente sind in Arrays von 10 bis 100 Kacheln angeordnet und erstellen damit ein einziges, mehrere Recheneinheiten übergreifendes Programm. Wenn ein Designer Anweisungen zum Spezifizieren der Parallelität für alle diese Kacheln integrieren müsste, dann wäre das sehr mühsam, wenn nicht gar unmöglich. Um diese Schwierigkeit zu überwinden, wird das KI-Engine-Design in zwei Stufen durchgeführt: Auf die Entwicklung eines einzelnen Kernels folgt die Erstellung eines Adaptive Data Flow (ADF)-Graphen, bei dem mehrere Kernels zu einer Gesamtanwendung verbunden werden.

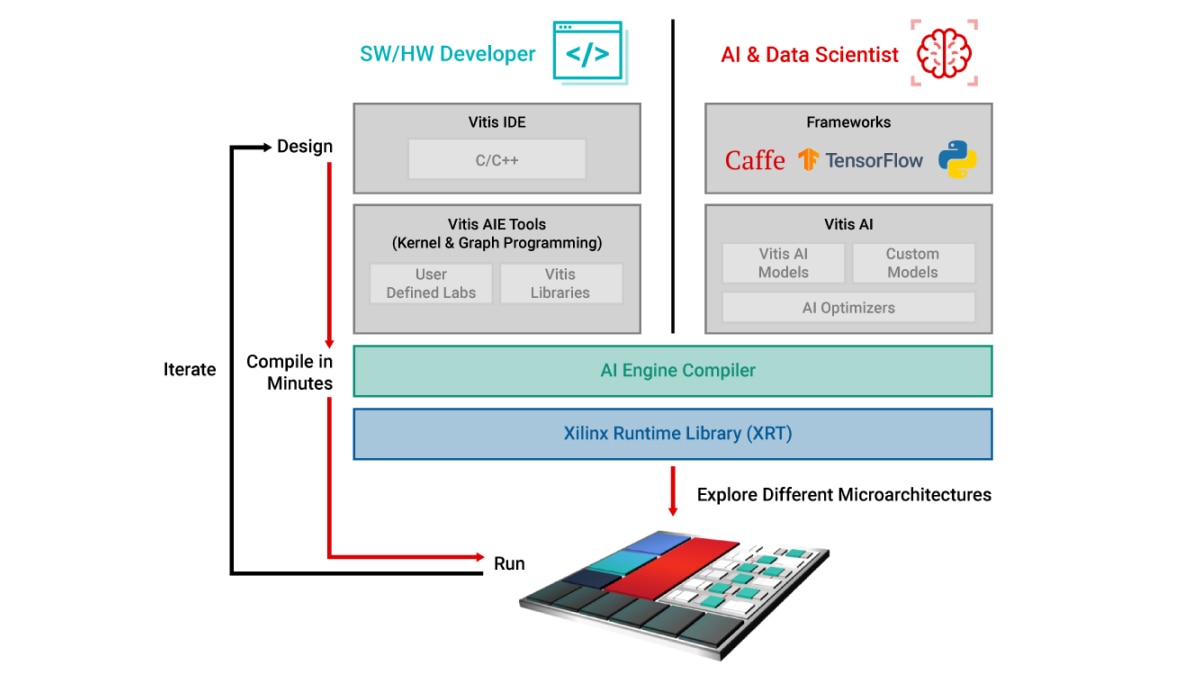

Vitis Unified IDE stellt ein einheitliches IDE-Cockpit bereit, das die Entwicklung des KI-Engine-Kernels mithilfe von C/C++-Programmiercode und Design von ADF-Graphen ermöglicht. Designer können insbesondere:

- Kernels in C/C++ entwickeln und spezifische Rechenfunktionen mithilfe von Vitis Bibliotheken beschreiben

- Kernels über ADF-Graphen mit den Tools der Vitis AI Engine verbinden

Standardmäßig wird jeweils ein Kernel auf einer KI-Engine-Kachel ausgeführt. Es ist jedoch auch möglich, mehrere Kernels auf derselben KI-Engine-Kachel auszuführen und die Verarbeitungszeit gemeinsam zu nutzen, sofern die Anwendung dies zulässt.

Nachfolgend wird ein Beispiel dieses Konzepts gezeigt:

- KI-Engine-Kernels werden in C/C++ entwickelt.

- Kernels in programmierbarer Logik (PL) werden in RTL oder Vitis HLS (High-Level-Synthese) geschrieben.

- Der Datenfluss zwischen Kernels in den PL- und KI-Engines erfolgt über einen ADF-Graphen.