Vitis Embedded

Vitis Embedded

Vitis™ Embedded ist ein eigenständiges integriertes Softwareentwicklungspaket zur Entwicklung von Host-Anwendungen, die auf integrierten Arm Prozessoren ausgeführt werden.

Version 2025.2 jetzt verfügbar

Die AMD Vitis™ Softwareplattform ist eine Entwicklungsumgebung für Designs, die auf FPGA-Fabric, Arm® Prozessoren und KI-Engines ausgerichtet sind. Sie arbeitet mit der AMD Vivado™ Design Suite zusammen, um eine höhere Abstraktionsstufe zu erreichen.

Vitis Software umfasst Vitis Embedded für C/C++ Anwendungsentwicklung auf Arm Prozessoren, KI-Engine-Compiler und Simulatoren, Vitis HLS für C/C++-basiertes FPGA IP, Vitis Model Composer für modellbasiertes Design in Simulink® und Performance-optimierte Bibliotheken wie DSP, Vision, Solver, Ultrasound und BLAS für die Bereitstellung von FPGA oder KI-Engine.

Erfahren Sie, wie Sie mithilfe des heterogenen System-Flows von Vitis Unified eine integrierte Systemlösung erstellen.

(Traditionell bezeichnet als Embedded SDK bei vorherigen FPGA Familien)

Designer, die C/C++-Code für das integrierte Arm® Prozessor-Subsystem in adaptiven SoCs von AMD entwickeln, verwenden in der Regel diesen Flow.

Entwickler können die gesamte Verifizierung auf Systemebene innerhalb der Vitis Embedded Software durchführen und Boot-Images zum Start der Anwendung generieren.

(Hardware und Software)

Systementwickler, die sowohl die Software- als auch die Hardwarebestandteile ihres Designs in adaptive SoCs von AMD integrieren, verwenden in der Regel diesen Flow.

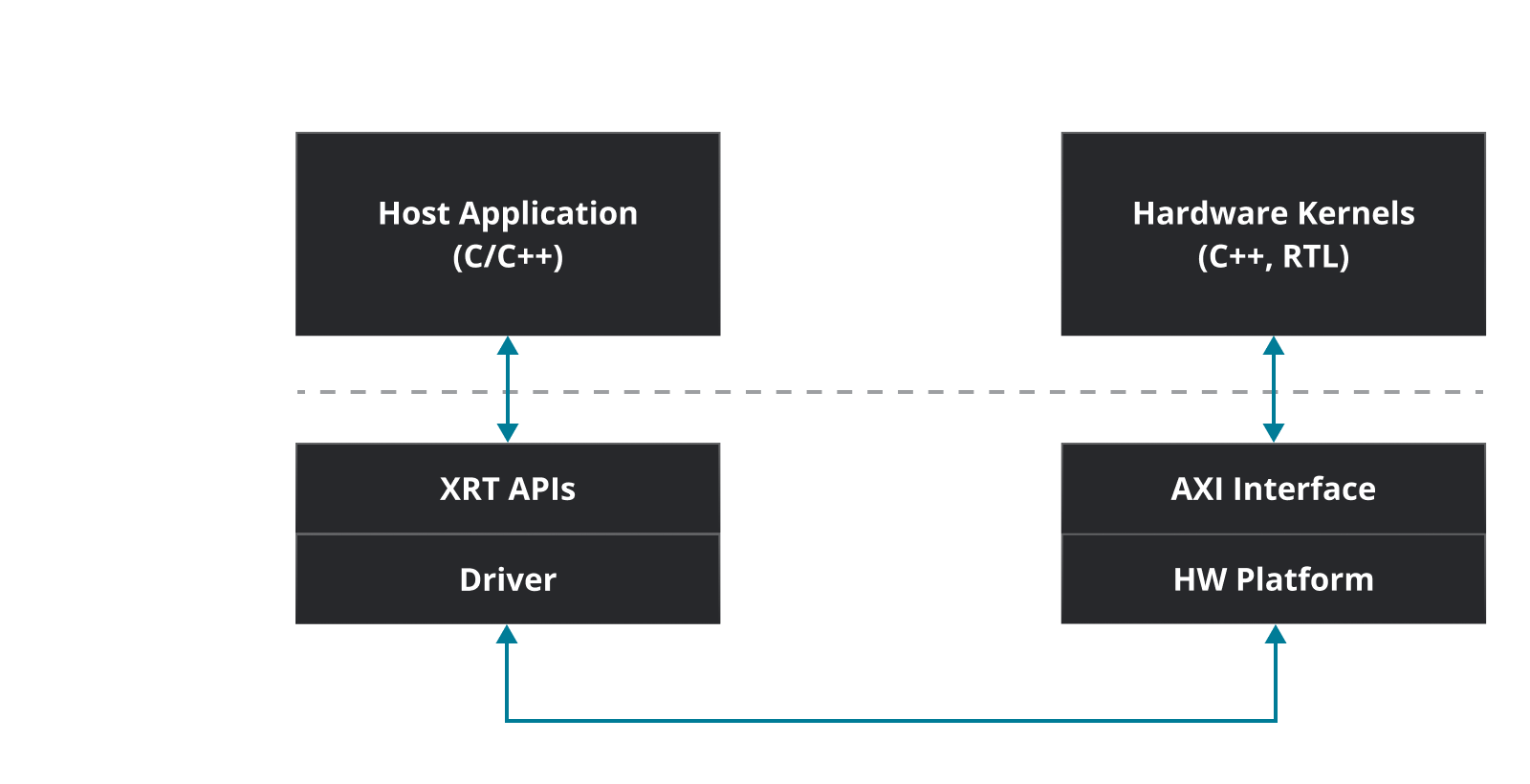

Dieser Flow wird verwendet, um heterogene integrierte Systemdesigns zu entwickeln, die aus Softwareanwendungen mit integrierten Arm® Prozessoren und Computing-Kernels bestehen, die auf programmierbarer Logik (PL) und/oder Versal™ AI Engine Arrays ausgeführt werden.

Dieser Flow umfasst:

Weitere Informationen im Abschnitt zu Vitis Tools für das heterogene Systemdesign in UG1393 >

AMD Alveo™ Beschleunigerkarten für Rechenzentren nutzen denselben Systemdesign-Flow – das Softwareprogramm wird auf einem x86-Host und die Kernels auf dem FPGA auf einer PCIe®-gebundenen Beschleunigerkarte ausgeführt.

In den bevorzugten Tools simulieren

• Verwenden vorhandener MATLAB®-, Python™-, C++- oder HDL-Testbenches

• Umschreiben von Testbenches oder Erlernen neuer Workflows nicht erforderlich

• Beschleunigen der Iteration von Algorithmus zu Hardware

Einheitliche KI-Engine- + PL-Simulation (Vitis Subsystem)

• Gemeinsames Simulieren von KI-Engine und PL

• Ersetzen fragmentierter Flows durch eine einheitliche Methodik

• Frühzeitiges Erkennen von Integrationsproblemen

Hardware-in-the-Loop (HIL)-Validierung

• Verkürzen der Validierungszeit auf Systemebene

• Streamen echter E/A über den Chip für schnelleres Debugging

• Prüfen des durchgängigen Durchsatzes vor der endgültigen Hardware