Vitis Embedded

Vitis Embedded

Vitis™ Embedded est un package de développement software embarqué autonome, destiné au développement d'applications hôtes s'exécutant sur des processeurs Arm intégrés.

Version 2025.2 désormais disponible

La plateforme software AMD Vitis™ est un environnement de développement pour les conceptions ciblant la structure FPGA, les processeurs ARM® et les moteurs AI Engine, en collaboration avec la suite AMD Vivado™ Design pour fournir un niveau d'abstraction supérieur.

La suite software Vitis comprend notamment Vitis Embedded pour le développement d'applications C/C++ sur les processeurs Arm, les compilateurs et simulateurs AI Engine, Vitis HLS pour la création d'IP FPGA en C/C++, Vitis Model Composer pour la conception basée sur modèle sous Simulink® et des bibliothèques optimisées pour les performances telles que DSP, Vision, Solver, Ultrasound et BLAS pour le déploiement FPGA ou AI Engine.

Apprenez à créer une solution de système embarqué à l'aide du flux de système hétérogène Vitis Unified.

(généralement appelé SDK embarqué pour les familles FPGA précédentes)

Les concepteurs qui codent en C/C++ pour le sous-système de processeur embarqué Arm® dans les SoC adaptatifs AMD utiliseront généralement ce flux.

Les développeurs peuvent effectuer toutes les vérifications au niveau du système dans le software Vitis Embedded et générer des images de démarrage pour lancer l'application.

(hardware et software)

Les concepteurs de systèmes qui intègrent à la fois les parties software et hardware de leurs conceptions dans les SoC adaptatifs AMD utiliseront généralement ce flux.

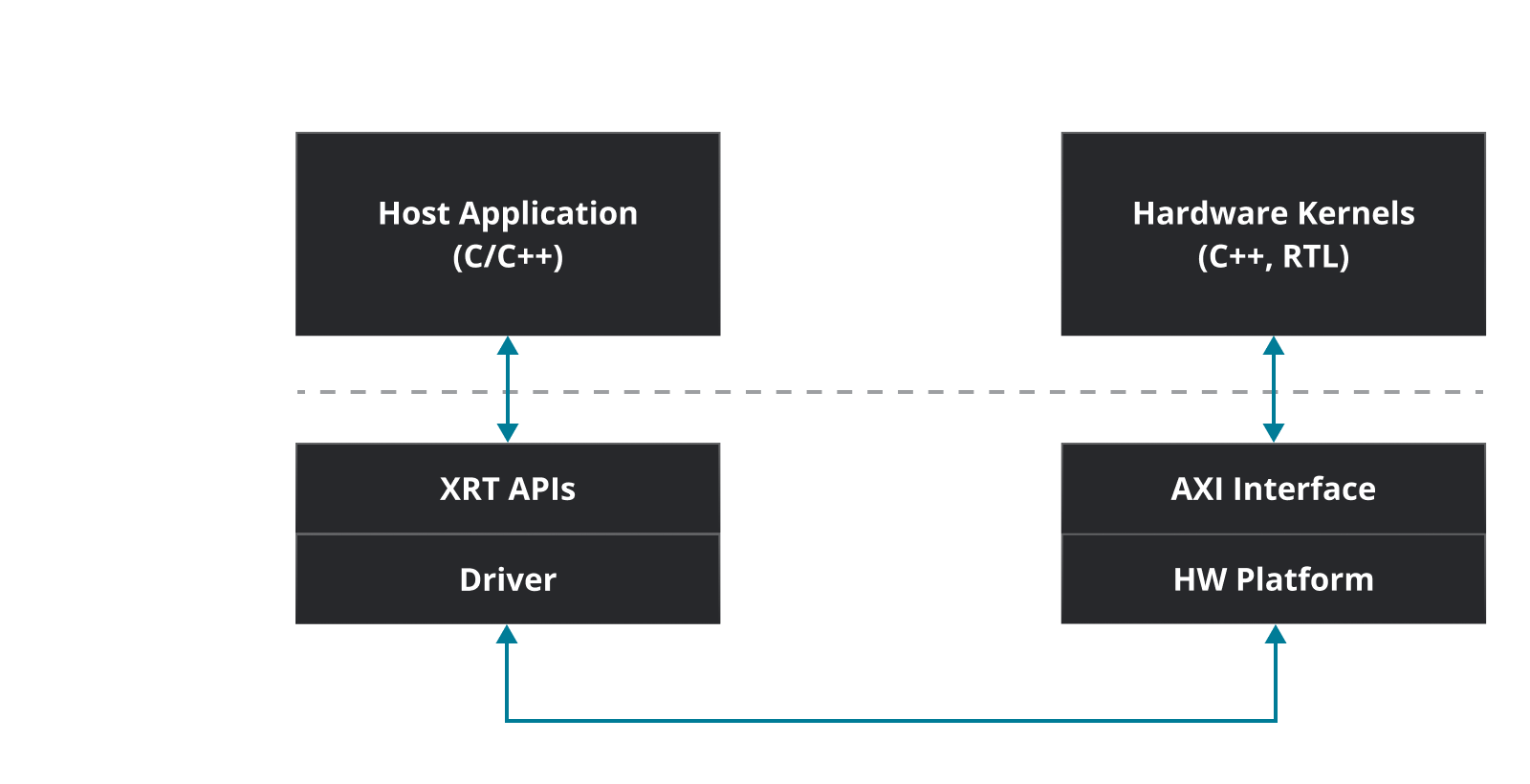

Ce flux permet de développer des conceptions de systèmes embarqués hétérogènes, notamment des applications software exécutées sur des processeurs intégrés Arm® et des noyaux de calcul s'exécutant sur des matrices à logique programmable (PL) et/ou sur des matrices AI Engine Versal™.

Ce flux comprend :

Les cartes d'accélération pour centres de données AMD Alveo™ utilisent ce même flux de conception de systèmes : le programme software s'exécute sur un hôte x86 et les noyaux s'exécutent dans le FPGA sur une carte d'accélération PCIe®.

Simulation dans vos outils préférés

• Utilisez les bancs d'essai MATLAB®, Python™, C++ ou HDL existants

• Éliminez le besoin de réécrire les bancs d'essai ou d'apprendre de nouveaux flux de travail

• Accélérez l'itération entre l'algorithme et le hardware

Simulation AI Engine + PL unifiée (sous-système Vitis)

• Réalisez des simulations AI Engine et PL conjointement

• Remplacez les flux fragmentés par une méthodologie cohérente

• Détectez les problèmes d'intégration en amont

Validation hardware dans la boucle (HIL)

• Raccourcissez le temps de validation au niveau du système

• Faites transiter des E/S réelles via la puce pour un débogage plus rapide

• Vérifiez le débit de bout en bout avant la mise en place du hardware final