Télécharger

Télécharger XRT pour les plateformes Alveo >

Remarque : Lors du téléchargement du programme d'installation XRT, sélectionnez la même version de XRT que la version de votre plateforme.

Hôte

(x86, Power PC ou CPU ARM)

Accélérateur

(FPGA, AI Engine)

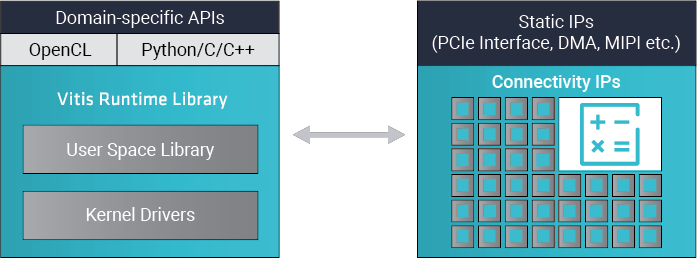

AMD Runtime Library est un composant clé de Vitis™ Unified Software Platform et de Vitis AI Development Environment, qui permet aux développeurs de déployer leurs conceptions sur des plateformes adaptables AMD, tout en continuant à utiliser des langages de programmation familiers tels que C/C++, Python et des architectures spécifiques au domaine de haut niveau tels que TensorFlow et Caffe.

AMD Runtime Library est une interface software standardisée open source qui facilite la communication entre le code d'application et les noyaux accélérés déployés sur la partie reconfigurable des cartes d'accélération Alveo basées sur PCIe, Zynq™ 7000, les plateformes intégrées Zynq UltraScale+™ MPSoC ou les plateformes d'accélération de calcul adaptatif Versal™.

AMD Runtime Library s'exécute sur le CPU hôte. Dans le cas des plateformes intégrées, l'hôte fait référence au processeur ARM sur la plateforme AMD et, dans le cas des cartes d'accélération Alveo™, il fait référence au CPU basé sur x86 ou au CPU PowerPC sur le serveur.