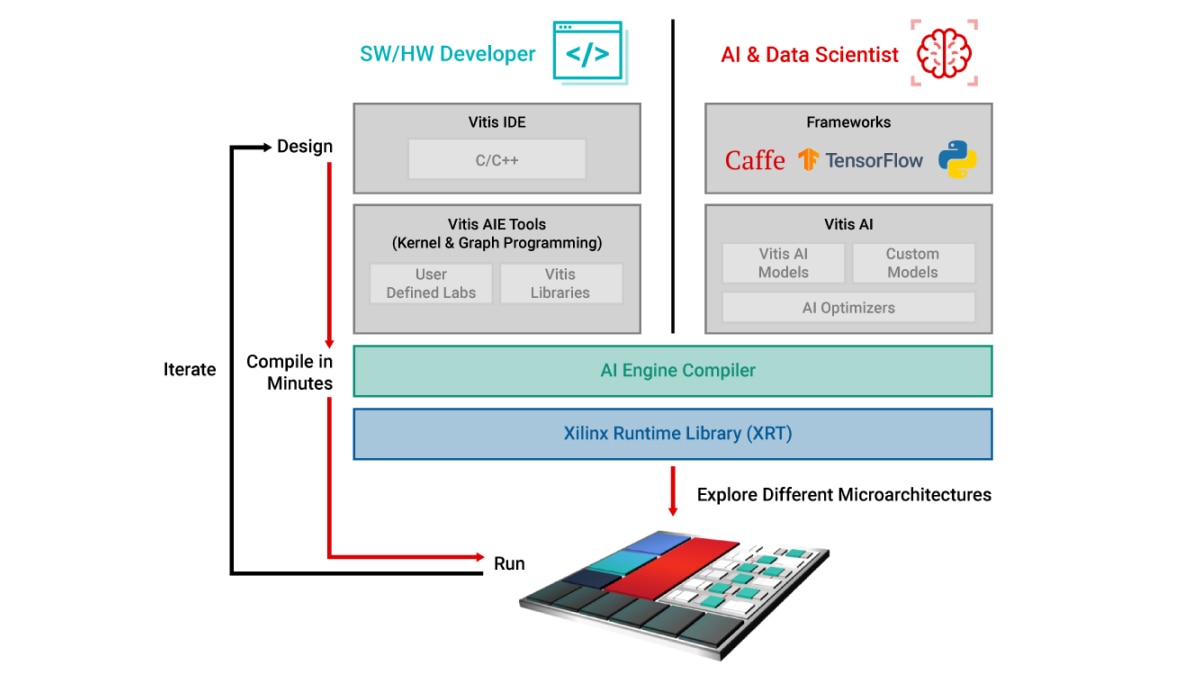

Programación de flujo de datos para desarrollador de software/hardware

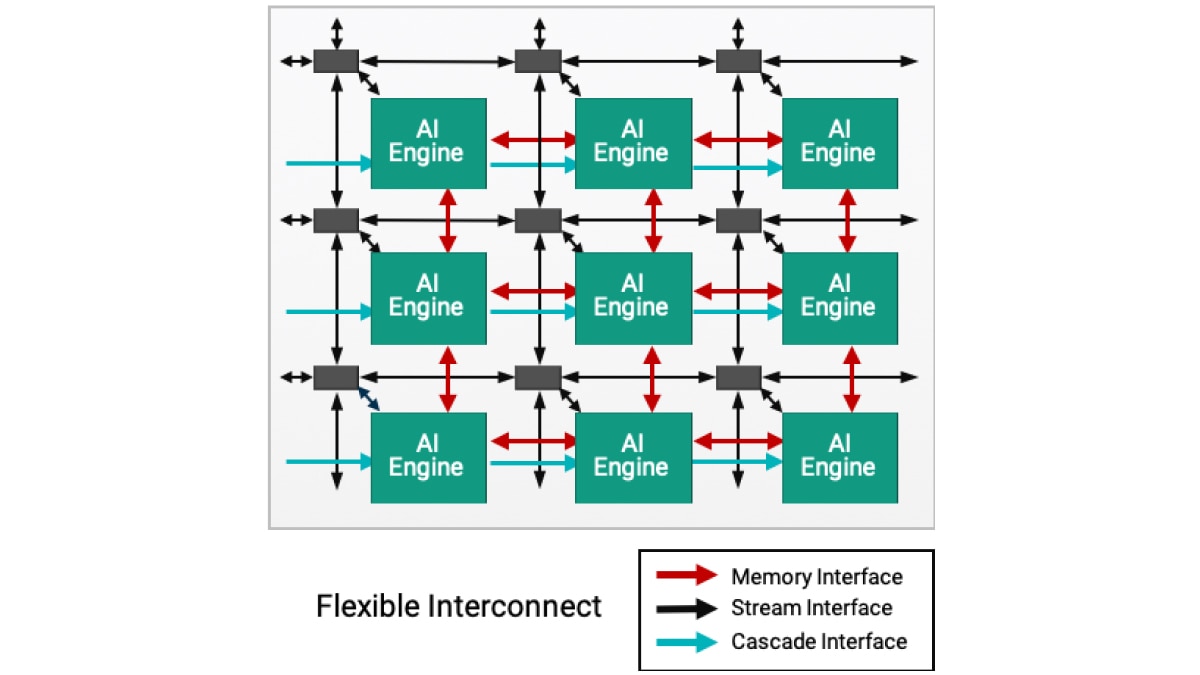

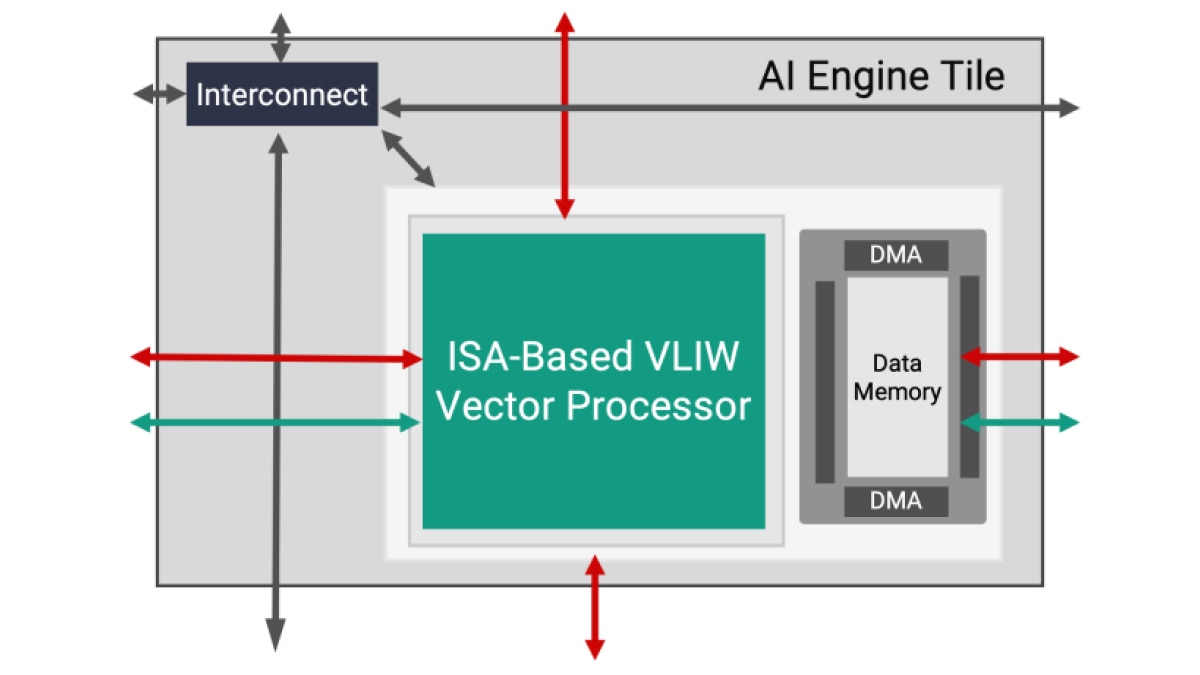

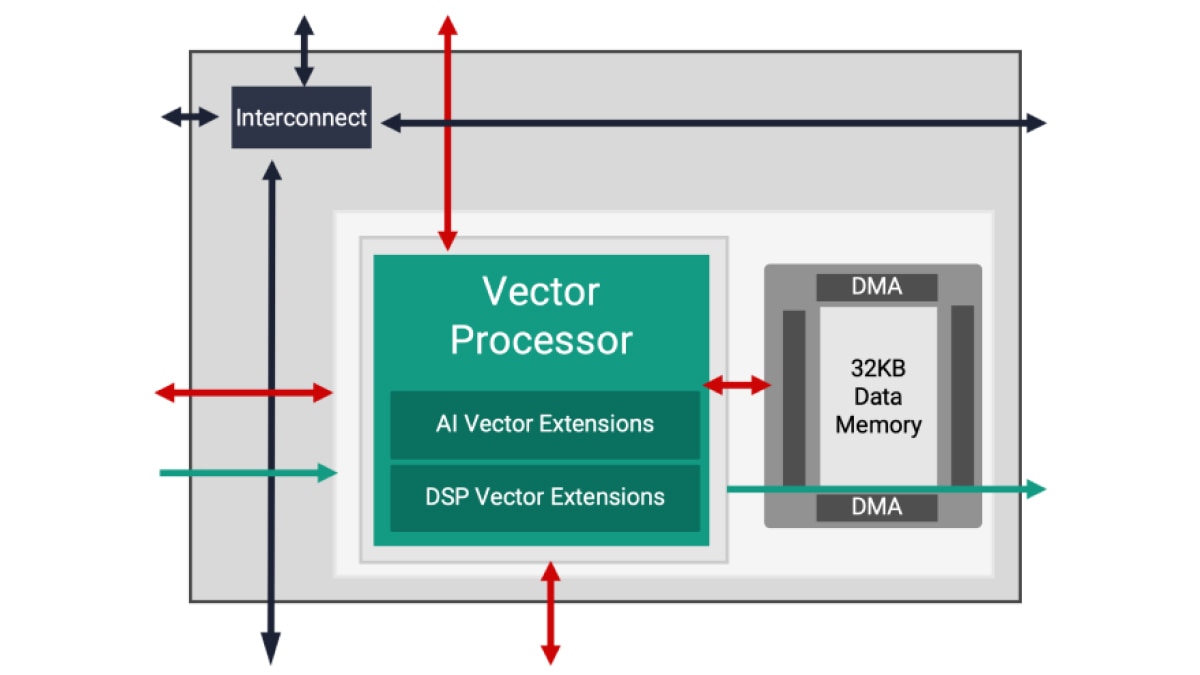

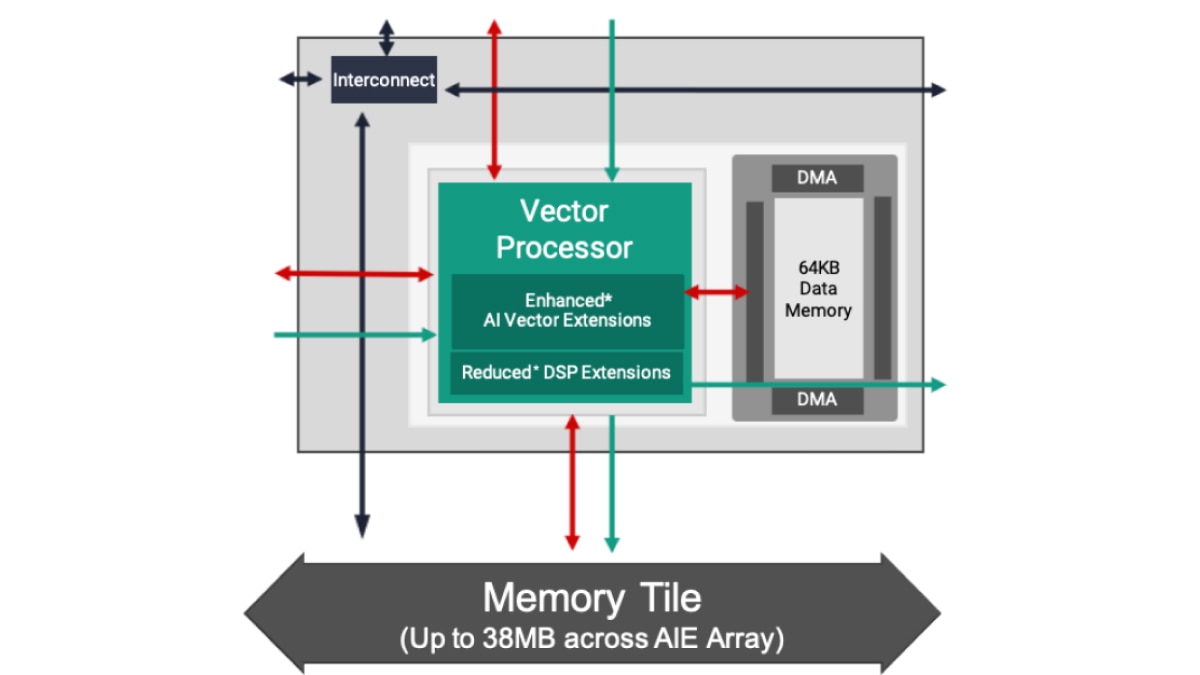

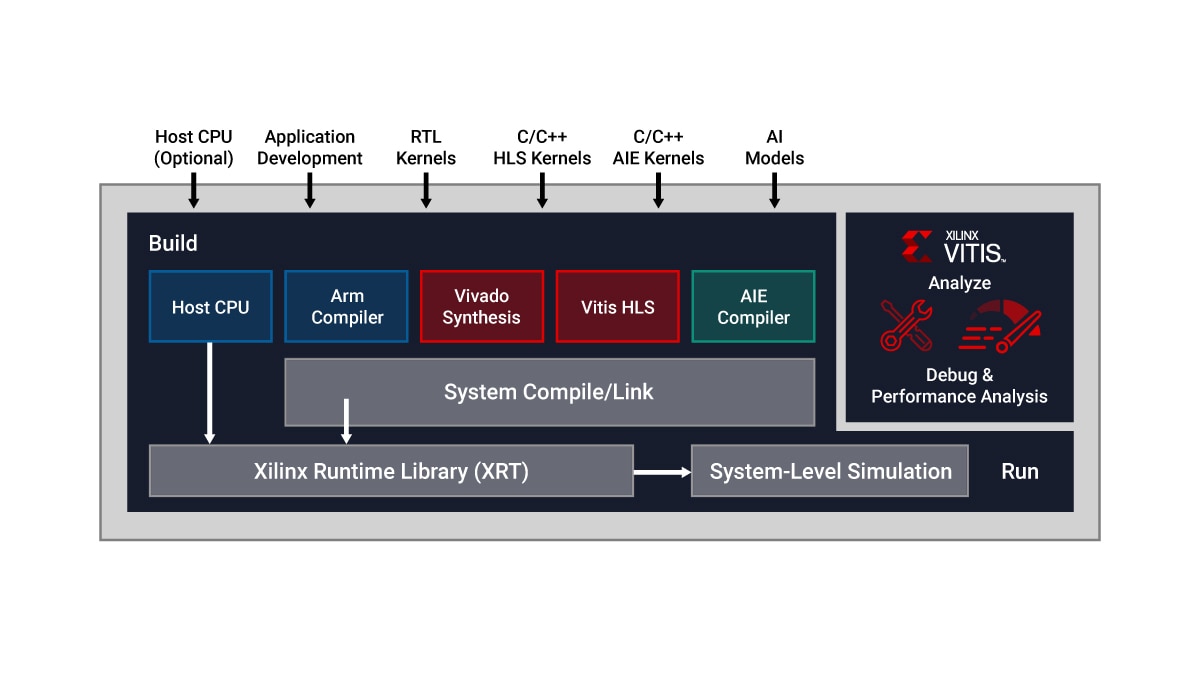

La arquitectura de motor de IA se basa en una tecnología de flujo de datos. Los elementos de procesamiento vienen en matrices de 10 a 100 mosaicos, creando un solo programa a través de las unidades de procesamiento. Para un diseñador, integrar directivas en un paralelismo específico en estos mosaicos sería tedioso y casi imposible. Para superar esta dificultad, el diseño de motor de IA se realiza en dos etapas: desarrollo de kernel único seguido de creación de gráficos ADF (Adaptive Data Flow, flujo de datos adaptable), que conecta varios kernels en una aplicación general.

El IDE unificado de Vitis proporciona una única cabina de IDE que permite el desarrollo del kernel de motor de IA utilizando código de programación C/C++ y diseño de gráficos ADF. Específicamente, los diseñadores pueden:

- Desarrollar kernels en C/C++ y describir funciones de procesamiento específicas usando bibliotecas de Vitis

- Conectar kernels a través de gráficos ADF utilizando las herramientas de Vitis AI Engine

Se ejecuta un solo kernel en un único mosaico de motor de IA de manera predeterminada. Sin embargo, pueden ejecutarse varios kernels en el mismo mosaico de motor de IA, compartiendo el tiempo de procesamiento cuando la aplicación lo permita.

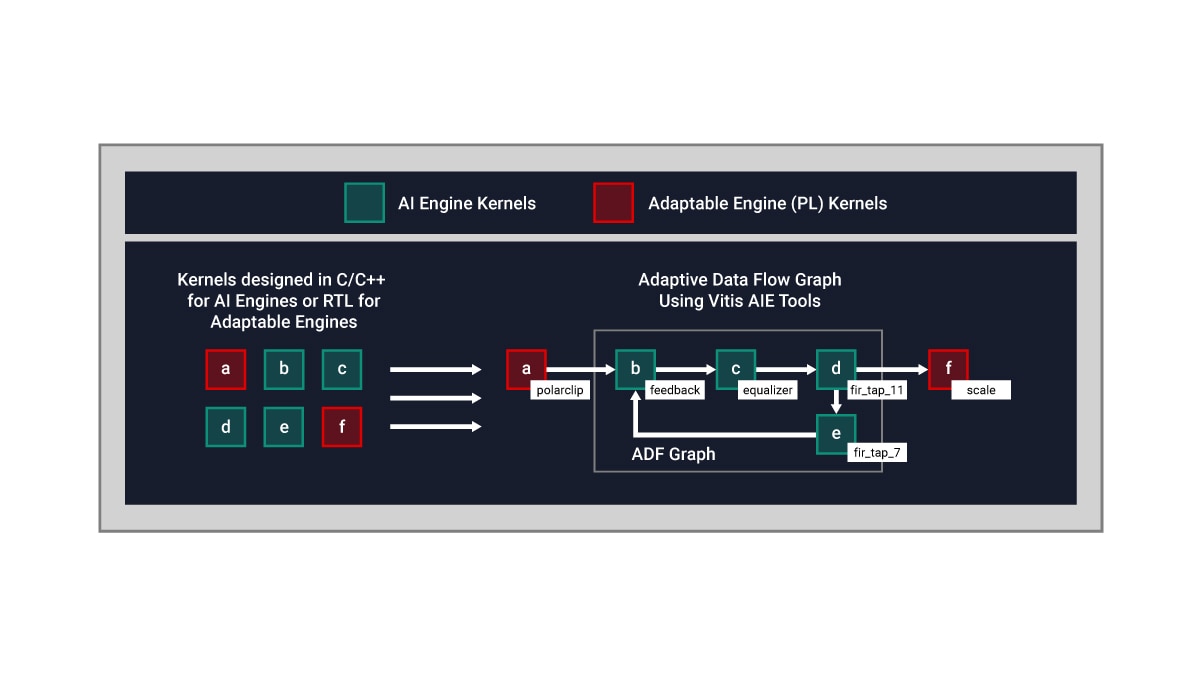

A continuación, se muestra un ejemplo conceptual:

- Los kernels de motor de IA se desarrollan en C/C++

- Los kernels en PL (programmable logic, lógica programable) se escriben en RTL o Vitis HLS (high level synthesis, síntesis de alto nivel)

- El flujo de datos entre kernels en los motores de PL e IA se realiza a través de un gráfico ADF