- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

- 2020.2

- 2020.1

AMD Vitis™ 소프트웨어 플랫폼 2025.2 릴리스 하이라이트

Versal™ AI 엔진을 통한 설계 흐름 개선

- Versal AI Edge 및 Versal AI Edge 시리즈 2세대(AIE-ML 및 AIE-ML v2)를 위한 AI 엔진 API 향상

- 새로운 데이터 형식 및 향상된 데이터 형식

- 새로운 사항: 블록 부동 소수점 MX6

- 새로운 사항: 블록 부동 소수점 MX4

- 새로운 사항: cbfloat16(에뮬레이트됨)

- 향상된 기능: cfloat 및 cbfloat16(FFT 및 행렬 곱셈 기능에서 사용 가능)

- 향상된 기능: cint16 및 cint32(이제 FFT에서 cint16 트위들 유형을 사용할 수 있음)

- 새로운 데이터 형식 및 향상된 데이터 형식

- 프로그래밍 모델 업데이트

- 읽기 전용 공유 버퍼 만들기

- 반복 MEM 타일 읽기 액세스(AIE-ML 및 AIE-ML v2)

- AIE-ML 및 AIE-ML v2에서 DMA-FIFO 지원

- 핑퐁 버퍼를 두 개의 인접한 MEM 타일에 포괄 가능

(AIE-ML 및 AIE-ML v2) - 로컬 타일 메모리에 대한 공유 매개변수

- AIE-ML 및 AIE-ML v2에 대한 패킷 스위칭 향상

- Versal AI Engine을 위한 새로운 DSP 라이브러리 함수와 개선된 DSP 라이브러리 함수

- 새 누적 합계

- 새 유클리드 거리

- 새 함수 근사화(RTP 업데이트 또는 LUT를 통해 호출됨)

- 패킷 스위칭을 통해 향상된 TDM FIR(PLIO 저장)

- AI 엔진 + PL을 사용한 향상된 1D FFT(필요한 PL 리소스 감소)

- 향상된 FIR(처리량 최적화)

- 향상된 AI 엔진 매퍼 및 라우터 - 컴파일러로 보다 효율적인 구현을 위해 다양한 풋프린트/레이아웃 탐색 가능

Versal AI Engine 설계의 손쉬운 검증

- C++(얼리 액세스)를 지원하는 Vitis Functional Simulation 워크플로 업데이트

- MATLAB® 및 Python 테스트 벤치를 사용하는 하드웨어 인 더 루프(얼리 액세스)

AIE DSP 설계용 Vitis 모델 컴포저의 개선 사항

- AI 엔진을 통한 슈퍼 샘플링 속도(SSR) 설계 흐름에 대한 간편한 업데이트(얼리 액세스)

- AI 엔진과 HDL 모두에 사용할 수 있는 추가 블록:

- AIE, AIE-ML, AIE-ML v2

- 새로운 사항: 함수 근사화

- 새로운 사항: 상관/중첩

- 새로운 사항: 누적 합계

- HDL 라이브러리 블록

- 향상된 기능: FFT(네이티브 부동 소수점 SSR=32, 64 추가)

- 향상된 기능: FIR(SSR을 사용한 분수 속도 보간 지원)

- AIE, AIE-ML, AIE-ML v2

임베디드 개발을 위한 Vitis IDE 업데이트

- 구성 빌드 업데이트를 위한 Python™ API

- Python 환경에서 Vitis™ API 실행

- 지원되는 코어에서 PS 추적 기능 기본 활성화

- 디버그 향상 - 이제 감시 보기 및 등록 보기에서 업데이트된 값 강조 표시

- 백엔드 작업 취소 또는 종료

- 통합 플랫폼 BSP 파일 경로(Linux 및 Windows)

- Theia AI Integration(얼리 액세스) - 개발자가 선호하는 LLM 및 코드 어시스턴트를 사용할 수 있는 인프라 제공

- Python API를 사용한 DFX 플랫폼 생성

- 작업 영역 백업 또는 공유

- 구성 파일에 대한 향상된 로깅

- 새로운 ‘통합 프로젝트’ 구성 요소

Vitis의 범주별 새로워진 사항

아래 섹션을 확장하여 AMD Vitis 소프트웨어 플랫폼 2025.2의 새로운 기능과 개선 사항에 대해 자세히 알아보세요. 지원되는 플랫폼, 변경된 동작 및 알려진 문제에 대한 자세한 내용은 애플리케이션 가속 흐름 및 임베디드 소프트웨어 개발 흐름에 대한 Vitis 소프트웨어 플랫폼 2025.2 릴리스 노트를 참조하세요.

향상된 DSP 라이브러리 함수:

- 새 누적 합계

- 새 유클리드 거리

- 새 함수 근사화(RTP 업데이트 또는 LUT를 통해 호출됨)

- 패킷 스위칭을 통해 향상된 TDM FIR(PLIO 저장)

- AIE + PL을 사용한 향상된 1D FFT(필요한 PL 리소스 감소)

- 향상된 FIR(처리량 최적화)

적용 대상:

- Versa™ AI Core(AIE 탑재)

- Versal AI Edge(AIE-ML 탑재)

- Versal AI Edge 시리즈 Gen 2 및 AIE-ML v2

- C++에서 Vitis 하위 시스템의 함수 시뮬레이션(얼리 액세스)

- AI 엔진 설계용 Vitis Analyzer의 향상된 지연율 및 처리율 측정 지원

- 독립적인 AIE 파티션의 런타임 제어

- AI 엔진을 통한 슈퍼 샘플링 속도(SSR) 설계 흐름에 대한 간편한 업데이트(얼리 액세스)

- AI 엔진과 HDL 모두에 사용할 수 있는 추가 블록:

- AIE, AIE-ML, AIE-ML v2

- 새로운 사항: 함수 근사화

- 새로운 사항: 상관/중첩

- 새로운 사항: 누적 합계

- HDL 라이브러리 블록

- 향상된 기능: FFT(네이티브 부동 소수점 SSR=32, 64 추가)

- 향상된 기능: FIR(SSR을 사용한 분수 속도 보간 지원)

- 성능 Pragma 개선 사항

- 이제 성능 Pragma를 CSIM이 계산한 트립 수를 기준으로 최적화

- 성능 Pragma 최적화를 구성 파일의 지시어로 변환 가능

- 성능 Pragma를 포함한 Pragma에 대한 조건부 제어

- 새로운 IP 지원

- FIR 및 FFT에 대한 분수 속도 SSR - FFT의 경우 SPFP32의 SSR이 이제 SSR=64까지 지원합니다.

- 블록 RAM 또는 UltraRAM으로 구현된 데이터 흐름 버퍼에 대한 ECC 지원

- 사용 편의성 기능

- CSIM 및 CoSim에서 자동 재시작 지원

- M-AXI용 멀티 포트 캐시

- 사이드밴드 신호를 사용하는 AXI 스트림을 위한 새로운 API

AMD Vitis™ 소프트웨어 플랫폼 2025.1 릴리스 하이라이트

Versal AI 엔진을 통한 설계 흐름 개선

- 새롭게 향상된 DSP 라이브러리 기능, AI 엔진 API, 새로운 데이터 유형 지원

AIE가 제공되는 Versal AI Core 시리즈:

- 2D 병렬 AIE + 프로그래밍 가능 로직(PL) 아키텍처를 사용하는 향상된 AI 엔진용 GEMV 및 FFT(다상 채널라이저에 적합)

- 벡터화된 바이토닉 SIMD 정렬, 상관관계, 컨볼루션

AIE-ML이 제공되는 Versal AI Edge 시리즈:

- 2D 병렬 AIE-ML + PL 아키텍처를 사용하는 AIE-ML용 FFT(다상 채널라이저에 적합)

- 벡터화된 바이토닉 SIMD 정렬, 상관관계, 컨볼루션

AIE-ML v2가 제공되는 Versal AI Edge 시리즈 Gen 2:

- 2D FFT AIE-ML v2 + PL v1(다상 채널라이저에 적합)

- TDM FIR(다상 채널라이저에 적합)

- GEMM/GEMV

- 단일 속도 FIR

- 반대역 FIR

- 분수 리샘플러 FIR

- 속도 변경 FIR

- FFT/iFFT

- DFT

- DDS 믹서

- 함수 근사화

AI 엔진 프로그래밍 업데이트:

- 로컬 메모리에 대한 타일링 파라미터 사양

- 테스트 벤치 변경 시 컴파일 시간 단축

- AIE-ML의 DDR에서 핑퐁 버퍼를 사용한 보다 빠른 설계 파이프라이닝

- AIE-ML의 기타 메모리 액세스 기능 향상

Versal AI Engine 설계의 손쉬운 검증

- MATLAB® 및 Python™에서 Vitis 하위 시스템의 기능 시뮬레이션

- AI 엔진 설계용 Vitis Analyzer의 향상된 지연율 및 처리율 측정 지원

- 독립적인 AIE 파티션의 런타임 제어

AIE DSP 설계용 Vitis 모델 컴포저의 개선 사항

- 여러 최상위 AI 엔진 하위 시스템 지원

- 추가 SSR 모드가 있는 향상된 FFT와 더 적은 DSP58 리소스를 사용할 수 있는 Complex Multiplier를 포함하여 AIE 및 HDL에 사용 가능한 추가 블록

임베디드 개발을 위한 Vitis IDE 업데이트

- Vitis Unified IDE(새 GUI)를 기본값으로 사용 - Classic Vitis IDE는 제공 중단

- GCC 및 ARMClang과 같은 타사 툴 체인 지원

- 이제 타사 생산성 도구에서 Vitis IDE 내의 마켓플레이스 유틸리티를 통해 설치 및 액세스 가능

Vitis의 범주별 새로워진 사항

아래 섹션을 확장하여 AMD Vitis 소프트웨어 플랫폼 2025.1의 새로운 기능과 개선 사항에 대해 자세히 알아보세요. 지원되는 플랫폼, 변경된 동작 및 알려진 문제에 대한 자세한 내용은 애플리케이션 가속 흐름 및 임베디드 소프트웨어 개발 흐름에 대한 Vitis 소프트웨어 플랫폼 2025.1 릴리스 노트를 참조하세요.

AIE가 제공되는 Versal AI Core 시리즈:

- 2D 병렬 AIE + 프로그래밍 가능 로직(PL) 아키텍처를 사용하는 향상된 AI 엔진용 GEMV 및 FFT(다상 채널라이저에 적합)

- 벡터화된 바이토닉 SIMD 정렬, 상관관계, 컨볼루션

AIE-ML이 제공되는 Versal AI Edge 시리즈:

- 2D 병렬 AIE-ML + PL 아키텍처를 사용하는 AIE-ML용 FFT(다상 채널라이저에 적합)

- 벡터화된 바이토닉 SIMD 정렬, 상관관계, 컨볼루션

Versal AI Edge 시리즈 Gen 2 및 AIE-ML v2

- 2D FFT AIE-ML v2 + PL v1(다상 채널라이저에 적합)

- TDM FIR(다상 채널라이저에 적합)

- GEMM/GEMV

- 단일 속도 FIR

- 반대역 FIR

- 분수 리샘플러 FIR

- 속도 변경 FIR

- FFT/iFFT

- DFT

- DDS 믹서

- 함수 근사화

- MATLAB® 및 Python™에서 Vitis 하위 시스템의 기능 시뮬레이션

- AI 엔진 설계용 Vitis Analyzer의 향상된 지연율 및 처리율 측정 지원

- 독립적인 AIE 파티션의 런타임 제어

여러 최상위 AI 엔진 하위 시스템 지원

AI 엔진과 HDL 모두에 사용할 수 있는 추가 블록

AI 엔진

- Bitonic Sort(Versal AI Core 시리즈, Versal AI Edge 시리즈, Versal AI Edge 시리즈 Gen2)

- DFT/ FFT(Versal AI Edge 시리즈 Gen2)

- FIR - 단일 속도, 반대역, 속도 변경, 분수 리샘플러(Versal AI Edge 시리즈 Gen2)

- DDS/믹서(Versal AI Edge 시리즈 Gen2)

HDL 라이브러리

- 향상된 FFT - 추가 SSR 모드

- SSR 8, 16, 32, 64(네이티브 부동 소수점)

- SSR 2, 4(고정점)

- 향상된 복합 승수 - 더 적은 DSP58 리소스

- CFLOAT MAC에 대한 새로운 지원

- 벡터 IFFT 부동 - 새로운 블록

- R2025a의 MATLAB(.m) 설계에서 Vitis HLS 친화적 C++ 코드 생성

- 새로운 Vitis HLS 사용 편의성 기능

- 실행 중 변경되는 와이어 입력 및 AXI Lite 입력 모델링(직접 I/O)

- 최상위 HLS 설계를 위한 성능 pragma(공개 EA)

- 전용 내장 라이브러리를 통한 Versal Complex Multiplier 지원

- Vitis HLS GUI 개선 사항

- Clang 16을 통한 초기 C++ 17 지원

AMD Vitis™ 소프트웨어 플랫폼 2024.2 릴리스 하이라이트:

AMD Versal AI Engine DSP 설계를 위한 개선 사항

- Vitis Analyzer를 사용한 지연율 및 처리율 추산

- Vitis Analyzer를 사용하여 사용할 수 없는 PLIO 표시

- AMD Versal™ AI Engine 설계의 신속한 프로토타이핑

- 힙 스택 및 프로그램 메모리 보고

Versal AI Engine을 위한 새로운 Vitis 라이브러리 함수와 개선된 Vitis 라이브러리 함수

- AIE를 위한 개선된 DSP 라이브러리 함수(Versal AI Core, Versal Premium 시리즈에서 사용 가능)

- 성능 강화된 TDM(시분할 다중화) FIR 필터 함수

- 성능 강화 버전

- GEMV(일반 행렬 벡터)

- GEMM(일반 행렬곱)

- 2D IFFT - 고성능을 위해 AIE + PL로 분할

- AIE-ML을 위한 새로운 DSP 라이브러리 함수(Versal AI Edge에서 사용 가능)

- 성능 강화된 TDM FIR 필터 함수

- 기수 3/기수 5 FFT 지원

- GEMV

- GEMM

Vitis IDE의 새로운 사용 편의성 기능(새로운 GUI)

- 새 직렬 터미널: 하드웨어의 직렬 메시지 모니터링

- 타사 확장 기능 설치 및 탐색

- 임베디드 시스템의 성능을 디버깅하고 최적화하기 위한 PS 트레이스 기능

AIE DSP 설계용 Vitis 모델 컴포저의 개선 사항

- AI 엔진 DSP 라이브러리 업데이트

- AIE(Versal AI Core, Versal Premium 시리즈에서 사용 가능)

- 혼합 기수 FFT

- Stockham FFT 성능 개선 사항

- TDM FIR

- AIE-ML(Versal AI Edge 시리즈에서 사용 가능)

- TDM FIR

- 직접 디지털 합성(DDS - 파형 생성에 사용)

- 믹서(주파수 변환에 사용)

- AIE-MLv2(Versal AI Edge Gen 2 시리즈에서 사용 가능)

- FIR

- DFT

- DDS

- 믹서

- AIE(Versal AI Core, Versal Premium 시리즈에서 사용 가능)

- Vitis 모델 컴포저의 추가 데이터 형식

- cbfloat16 지원

- 캐스케이드 신호에 대한 추가 데이터 형식 지원

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- Vitis 모델 컴포저에서 VSS(Vitis 하위 시스템)로 Vitis에 AIE/HLS 커널 설계 내보내기

- Vitis Debugger를 사용하여 Vitis 모델 컴포저에 내장된 AIE/HLS 커널 디버깅

- Vitis 모델 컴포저의 HDL 블록 세트 업데이트

- Vitis 모델 컴포저의 기타 개선 사항

- 코드 생성에 대한 반응 시간 개선

- 모든 설계에 대해 한 번만 시뮬레이션 실행

- 허브 블록 구성을 JSON 파일로 저장(신속한 프로토타이핑 또는 일괄 처리에 유용)

- MATLAB R2024a지원 추가

- Red Hat Enterprise Linux(RHEL) 8.10, 9.4 지원 추가

- 코드 생성에 대한 반응 시간 개선

- 설계 고려 사항을 대체할 DRC(Design Rule Check)

Vitis의 범주별 새로워진 사항

아래 섹션을 확장하여 AMD Vitis 소프트웨어 플랫폼 2024.2의 새로운 기능과 개선 사항에 대해 자세히 알아보세요. 지원되는 플랫폼, 변경된 동작 및 알려진 문제에 대한 자세한 내용은 애플리케이션 가속 흐름 및 임베디드 소프트웨어 개발 흐름에 대한 Vitis 소프트웨어 플랫폼 2024.2 릴리스 노트를 참조하세요.

AIE를 위한 개선된 DSP 라이브러리 함수(Versal AI Core, Versal Premium 시리즈에서 사용 가능)

- 성능 강화된 TDM(시분할 다중화) FIR 필터 함수

- 성능 강화 버전

- GEMV(일반 행렬 벡터)

- GEMM(일반 행렬곱)

- 2D IFFT - 고성능을 위해 AIE + PL로 분할

AIE-ML을 위한 새로운 DSP 라이브러리 함수(Versal AI Edge에서 사용 가능)

- 성능 강화된 TDM(시분할 다중화) FIR 필터 함수

- 기수 3/기수 5 FFT 지원

- GEMV(일반 행렬 벡터)

- GEMM(일반 행렬곱)

- Vitis Analyzer를 사용한 지연율 및 처리율 추산

- Vitis Analyzer를 사용하여 사용할 수 없는 PLIO 표시

- AI 엔진 DSP 라이브러리 업데이트

- AIE(Versal AI Core, Versal Premium 시리즈에서 사용 가능)

- 혼합 기수 FFT

- Stockham FFT 성능 개선 사항

- TDM FIR

- AIE-ML(Versal AI Edge 시리즈에서 사용 가능)

- TDM FIR

- DDS(직접 디지털 합성 - 파형 생성에 사용)

- 믹서(주파수 변환에 사용)

- AIE-MLv2(Versal AI Edge Gen 2 시리즈에서 사용 가능)

- FIR

- DFT

- DDS

- 믹서

- AIE(Versal AI Core, Versal Premium 시리즈에서 사용 가능)

- Vitis 모델 컴포저의 추가 데이터 형식

- cbfloat16 지원

- 캐스케이드 신호에 대한 추가 데이터 형식 지원

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- Vitis 모델 컴포저에서 VSS(Vitis 하위 시스템)로 Vitis에 AIE/HLS 커널 설계 내보내기

- Vitis Debugger를 사용하여 Vitis 모델 컴포저에 내장된 AIE/HLS 커널 디버깅

- Vitis 모델 컴포저의 HDL 블록 세트 업데이트

- Vitis 모델 컴포저의 기타 개선 사항

- 코드 생성에 대한 반응 시간 개선

- 모든 설계에 대해 한 번만 시뮬레이션 실행

- 허브 블록 구성을 JSON 파일로 저장(신속한 프로토타이핑 또는 일괄 처리에 유용)

- MATLAB R2024a지원 추가

- Red Hat Enterprise Linux(RHEL) 8.10, 9.4 지원 추가

- 설계 고려 사항을 대체할 DRC(Design Rule Check)

- 실행 중 변경되는 스칼라/와이어 입력 모델링(직접 I/O)

- 임의 정밀도 부동 소수점 유형 지원

- DSP 블록에 HLS 코드 매핑

- 사용자가 결정하는 코드 실행 순서

- 사용자 친화적인 방식으로 데이터 형식을 보여 주는 HLS 디버거(GNU 디버거의 자동 서식 지정 기술 사용)

AMD Vitis™ 소프트웨어 플랫폼 2024.1 릴리스 하이라이트:

AMD Versal™ AI Engine DSP 설계를 위한 개선 사항

- AMD Versal AI Core 시리즈를 위한 개선된 DSP 라이브러리 함수

- SSR >1에 대한 TDM(시분할 다중화) FIR 필터 함수

- 32비트 트위들을 사용한 FFT

- 혼합 기수 3 및 혼합 기수 5 FFT

- 크로네커 행렬곱

- 안정성 향상을 위한 하우스홀더 기반 QRD 솔버

- SSR >1에 대한 DFT

- AIE-ML을 사용하는 AMD Versal AI Edge 시리즈를 위한 새로운 DSP 라이브러리 함수

- GEMV(일반 행렬 벡터), SSR 지원

- GEMM(일반 행렬곱), SSR 지원

- AIE API 개선 사항

- Radix-3/Radix-5 FFT 지원

- AIE 시뮬레이터 개선 사항

- CIPS(Control, Interfaces, and Processing System) IP 코어가 필요 없이 PL을 사용하는 AI 엔진 설계를 위한 주기 근사 시뮬레이션 기능

- VCS, Questa, Xcelium 및 Riviera와 같은 타사 시뮬레이터를 사용한 하드웨어 에뮬레이션을 위한 AMD Vitis Analyzer 지원

Vitis 통합 소프트웨어 플랫폼의 주요 개선 사항

- 새로운 디바이스 지원: AMD Versal™ Premium VP1902 Adaptive SoC, AMD MicroBlaze™ V 프로세서

- Windows® 환경을 위한 개선된 임베디드 애플리케이션 개발 및 BSP 생성

- 외부에서 컴파일된 임베디드 애플리케이션을 디버깅하기 위한 사용자 관리 흐름

- 새로운 Bootgen GUI

- 플랫폼 프로젝트에 대한 증분 빌드 활성화

AMD Vitis IDE의 주요 개선 사항(새로운 GUI)

- 처리 하위 시스템의 계층적 디버깅 지원 추가

- 프로젝트/작업 공간 내보내기 및 가져오기 지원 추가

- Python 인터프리터 및 API 지원 추가

- 새로운 기능 미리보기 페이지

- 임베디드, AIE, 플랫폼 프로젝트에 대한 새로운 파일 변경 알림

Vitis의 범주별 새로워진 사항

아래 섹션을 확장하여 AMD Vitis 소프트웨어 플랫폼 2024.1의 새로운 기능과 개선 사항에 대해 자세히 알아보세요. 지원되는 플랫폼, 변경된 동작 및 알려진 문제에 대한 자세한 내용은 애플리케이션 가속 흐름 및 임베디드 소프트웨어 개발 흐름에 대한 Vitis 소프트웨어 플랫폼 2024.1 릴리스 노트를 참조하세요.

AMD Versal AI Core 시리즈를 위한 개선된 DSP 라이브러리 함수

- SSR >1에 대한 TDM(시분할 다중화) FIR 필터 함수

- 32비트 트위들을 사용한 FFT

- 혼합 기수 3 및 혼합 기수 5 FFT

- 크로네커 행렬곱

- 안정성 향상을 위한 하우스홀더 기반 QRD 솔버

- SSR >1에 대한 DFT

AIE-ML을 사용하는 AMD Versal AI Edge 시리즈를 위한 새로운 DSP 라이브러리 함수

- GEMV(일반 행렬 벡터), SSR 지원

- GEMM(일반 행렬곱), SSR 지원

AIE API 개선 사항

Radix-3/Radix-5 FFT 지원

AI Engine 시뮬레이터 개선 사항

- CIPS(Control, Interfaces, and Processing System) IP 코어가 필요 없이 PL을 사용하는 AI 엔진 설계를 위한 주기 근사 시뮬레이션 기능

- VCS, Questa, Xcelium 및 Riviera와 같은 타사 시뮬레이터를 사용한 하드웨어 에뮬레이션을 위한 Vitis Analyzer 지원

- Vitis Analyzer에서 CSV 형식으로 테이블 내보내기

- AMD Vitis 모델 컴포저 내에서 AIE 및 AIE-ML에 지원되는 새로운 DSP 함수

- TDM(시분할 다중화) FIR 필터 함수

- 1GSPS 이상의 처리율에서 다상 채널라이저 구축

- DFT/IDFT - SSR 지원

- 작은 크기에서의 처리율/지연율을 위한 최적화된 변환

- FFT/IFFT - CINT32비트 트위들에 대한 확장 지원

- 혼합 기수 FFT/IFFT - AIE-ML 지원

- 모델 컴포저 허브 블록의 사용 편의성 개선 사항

- 하드웨어 검증 흐름 개선 사항

- v 2024.1에 추가된 OS 및 MATLAB® 버전 지원:

- RHEL 9

- MATLAB R2023a 및 R2023b

GitHub에서 새로운 예제 설계 사용 가능

새로운 스텐실 pragma가 이미지 및 비디오 필터용 HLS C++ 코드를 단순화

새로운 라이브러리 함수 마법사가 AMD Vitis 라이브러리 Github 리포지토리 활용

- AMD Vivado 설계 도구용 "Solver" 및 "Vision"(OpenCV 호환) IP 생성

- 사용 가능한 라이브러리 예제 실행

메모리 인터페이스용 pragma(ap_memory)가 이제 AMD Vivado IP Integrator용 포트를 번들로 구성 가능

새로운 HLS 구성 요소 비교에서는 2개 이상의 구성 요소에 대한 지표가 나란히 표시됨

C++ 함수를 대체하는 사용자-공급자 RTL 코드 지원(블랙박스 흐름)

코드 분석기가 이제 C++ 구조체 멤버를 분해하여 성능 분석을 미세 조정 가능

HLS 전역 FSM 인코딩 및 안전 상태 선택을 위한 새로운 사용자 컨트롤

C 시뮬레이션 중 Clang 새니타이저에 액세스하여 주소 및 초기화 검사 수행

Vitis™ 소프트웨어 플랫폼 2023.2 릴리스 하이라이트:

Versal™ AI Engine DSP 설계를 위한 개선 사항

- 새로운 DSP 라이브러리 함수

- DSP 함수를 위한 새로운 API 지원

- AI 엔진 컴파일러 및 시뮬레이터의 새로운 기능

새로운 독립형 Vitis Embedded 소프트웨어

- Arm® 임베디드 하위 시스템용 C 코드를 작성하는 설계자를 위한 더 작은 독립형 설치 프로그램

- Bootgen 및 XSCT와 같은 유틸리티를 포함한 모든 임베디드 기능 제공

새로운 Vitis 통합 설계 환경

- 모든 Vitis 워크플로에서 일관된 GUI 및 CLI

- 차세대 Eclipse Theia 기반 GUI는 작업 효율성 강화를 위해 향상된 유연성과 사용자 친화적인 기능을 제공

Vitis의 범주별 새로워진 사항

아래 섹션을 확장하여 Vitis 소프트웨어 플랫폼 2023.2의 새로운 기능과 개선 사항에 대해 자세히 알아보세요. 지원되는 플랫폼, 변경된 동작 및 알려진 문제에 대한 자세한 내용은 애플리케이션 가속 흐름 및 임베디드 소프트웨어 개발 흐름에 대한 Vitis 소프트웨어 플랫폼 2023.2 릴리스 노트를 참조하세요.

AI 엔진을 위한 새로운 DSP 라이브러리 함수

- 혼합 기수 FFT

- Discrete Fourier Transform (DFT)

- GEMV(일반 행렬-벡터 곱셈)

DSP 함수를 위한 새로운 API 지원

- cint32 트위들 데이터 형식을 사용하는 FFT IP

- 기수 4 FFT API에 대한 cint16 지원

- API에서 구현된 벡터화된 "fix2flt" 및 "flt2fix"

AIE-ML을 위한 새로운 API 지원

- API가 이제 sliding_mul() 함수에서 int32/cint32 데이터 형식 지원

- API가 이제 sliding_mul() 함수에서 <float> 데이터 형식 지원

- 희소 행렬 곱셈을 지원하는 데 필요한 모든 AIE API 루틴 제공

주요 구성 요소 업데이트:

- U-boot 2024.1

- Arm Trusted Firmware 2.10

- Linux Kernel 6.6_LTS

- Qemu 8.1

- Xen 4.18

- OpenAMP 2023.10

Sunset BSP:

- AMD Microblaze™: VCU118, KCU105, KC705, AC701

- Zynq: zc706

- AMD Versal™: VMK180-EMMC, VMK180-OSPI

- Zynq MP: ZCU111

새로운 BSP(XSCT):

- 새로운 ETH Phy가 포함된 VEK280 프로덕션 BSP

새로운 시스템 디바이스 트리 흐름(SDT) BSP:

- ZCU102, ZCU104, ZCU105, ZCU216

- ZCU208, ZCU208-sdfec, ZCU670

- VCK190

- VMK180

- VPK120

- VPK180

- VEK280

- AIE 컴파일러가 이제 입력 또는 출력으로 2D 및 3D 어레이 지원 가능

- Vitis Analyzer가 이제 FIFO 크기를 조정하기 위한 안내 보고서 생성

- 멀티스레드 시뮬레이터 커널 및 VCD(값 변경 덤프) 분석기 가속을 위한 새로운 지원

- MATLAB® 환경 및 Python 트래픽 발생기와의 외부 인터페이싱

- PLIO 정렬에서 공백/대기 주기를 지원하는 개선된 AXI 스트림 모델

- 강화된 설계 규칙 검사

- 고속 디버그를 통한 AI 엔진 추적 오프로드

- Vitis 환경의 NoC 및 하드 DDRMC 프로파일링 지원

- Vitis 도구가 이제 VEK280 및 Alveo™ V70 AI 추론 가속기 카드에 대한 AIE-ML 추적 지원

- AI 엔진 블록 업데이트

- AIE-ML 그래프를 블록으로 Vitis 모델 컴포저에 가져올 수 있도록 지원

- Vitis 모델 컴포저에서 AIE 및 AIE-ML 구현을 위한 새로운 DSPlib 함수

- Simulink® 도구에서 내부 신호에 대한 AIE 시뮬레이터 출력 플로팅

- HLS 커널 블록 업데이트

- 자동 테스트 벤치 생성

- HLS 커널 블록에 대한 확장된 데이터 형식 지원

- Vitis 모델 컴포저와 Vitis 도구의 통합

- Vitis 모델 컴포저에서 직접 .xo 및 libadf.a 파일 생성

- 기타 개선 사항

- MATLAB® 도구 버전 지원: R2021a, R2021b 업데이트 6, R2022a 업데이트 6, R2022b

- 하드웨어 검증 흐름에 대해 지원되는 추가 토폴로지

- GitHub에서 제공되는 새로운 예제 자료

- HLS 구성 요소를 위한 새로운 Vitis 통합 IDE

- 새로운 Vitis HLS 라이선스 요구 사항

- C 합성을 실행하기 전에 성능 추정치를 얻기 위한 새로운 코드 분석기 기능

- AXI 인터페이스 개선 사항:

- HLS AXI 스트림 사이드 채널 지원

- 사용자 구성 가능 AXI 마스터 캐싱 지원

- 기타 개선 사항:

- C 합성 중에 설계 크기 문제를 식별할 수 있는 새로운 코드 복잡성 보고서

- 컴파일 시간 개선: 2023.1에 비해 2023.2에서 평균 컴파일 시간 20% 개선1

Vitis 소프트웨어 플랫폼 2023.1 릴리스 하이라이트:

Versal™ AIE(AI Engine) 어레이를 위한 새로운 Vitis™ 라이브러리 함수

- DSP 라이브러리 함수 - FIR 필터 구성 추가

- Solver 라이브러리 함수 - 성능 향상을 위한 기능 개선

Versal AI Core 및 AI Edge 시리즈의 설계 흐름 개선 사항

- 입력/출력으로서의 2D 및 3D 어레이에 대한 AIE 컴파일러 지원

- 교착 상태 조건을 피하기 위한 FIFO 크기 조정에 대한 AIE 시뮬레이터 안내 지원

- AIE 상태 보고 개선 사항

- Vitis Analyzer의 새로운 기본 GUI

Vivado™ 환경으로 Vitis 환경 내보내기 지원

- Vitis 및 Vivado 도구 개발 팀이 공통 인터페이스 체크포인트를 기반으로 병렬 작업 가능

Vitis의 범주별 새로워진 사항

아래 섹션을 확장하여 AMD Vitis 소프트웨어 플랫폼 2023.1의 새로운 기능과 개선 사항에 대해 자세히 알아보세요. 지원되는 플랫폼, 변경된 동작 및 알려진 문제에 대한 자세한 내용은 애플리케이션 가속 흐름 및 임베디드 소프트웨어 개발 흐름에 대한 Vitis 소프트웨어 플랫폼 2023.1 릴리스 노트를 참조하세요.

DSP 라이브러리 - FIR 필터

- 계수 비트 폭이 데이터 비트 폭보다 클 수 있도록 지원하기 위해 분수 리샘플러 FIR, 단일 속도 FIR, 반대역 FIR, 속도 변경 FIR 개선

- 분수 리샘플러 FIR은 또한 다수의 AIE 타일을 사용하여 SSR 작동을 지원하고 계수 재로드 기능을 통합

Solver 라이브러리

- 고성능 스트리밍 설계로 API 성능 향상(약 300개 타일)

- AIE 어레이의 데이터를 읽거나 쓰는 데 도움이 되는 4D 데이터 무버 기능에 대한 QR 및 숄레스키 분해 지원

- AIE 컴파일러가 이제 입력 또는 출력으로 1D 외에도 2D 및 3D 어레이 지원 가능

- AIE 컴파일러가 그래프 내의 그래프 구조(하위 그래프)와 조건부 포트 구조 지원

- 새로운 AIE CINT-CFLOAT 데이터 변환 API

- 설계의 AIE-ML 및 AIE 타일에 대한 타일, 이벤트 및 추가 레지스터 관련 정보를 포함하는 파일을 생성하기 위한 AIE 상태 보고 개선 사항

- Versal 디바이스의 메모리에 저장하는 대신 HSDP(고속 차동 쌍)를 통해 AIE 이벤트 추적 오프로드

- Vitis 환경의 NoC 및 하드 DDR MC 프로파일링 지원

- 애플리케이션의 특정 부분을 검사하기 위한 AIE 창형 이벤트 추적

- 교착 상태를 방지하기 위한 FIFO 크기 조정 안내

- AIE 시뮬레이터가 보고하는 노드를 선택하여 시뮬레이터 VCD 파일의 크기를 줄이고 시뮬레이션 속도를 향상

- AIE 시뮬레이터는 이제 어떤 AIE에 메모리 액세스 위반이 있는지, 이것이 그래프 C 코드의 줄과 어떻게 대응하는지 보여주는 보고서(Vitis Analyzer에서 확인 가능)를 생성

- 추적 보기 데이터 시각화가 이제 AIE-ML 어레이도 지원

- Versal AI Engine을 타겟팅하는 FIR 필터 구성에 대한 새로운 데이터 형식 지원

- Versal Adaptive SoC의 DSP58에 최적화된 두 가지 새로운 부동 소수점 함수

- Versal AI Engine을 타겟팅하는 모든 Vitis 모델 컴포저 라이브러리 함수에 대한 반응 시간 단축

- 기타 개선 사항:

- HLS 커널 블록 개선 사항

- Vitis 모델 컴포저 허브 개선 사항

- MATLAB 도구 버전 R2021a, R2021b, R2022a 지원

- 성능 개선 사항2: 2022.2에 비해 2023.1에서 평균 지연율 5.2% 개선

- Vitis HLS 도구에서 L1 라이브러리 함수를 쉽게 다운로드, 확인, 인스턴스화하는 쉬운 방법

- Vitis HLS 도구 내에서 AXI 트랜잭션 및 버스트 보고에 대한 지원 강화

Vitis 소프트웨어 플랫폼 2022.2 릴리스 하이라이트:

Versal™ AIE(AI Engine) 어레이를 위한 새로운 Vitis™ 라이브러리 함수

- DSP 라이브러리 함수 - 기능 강화

- Solver 라이브러리 함수

- 비전 라이브러리 함수

- 초음파 라이브러리 함수

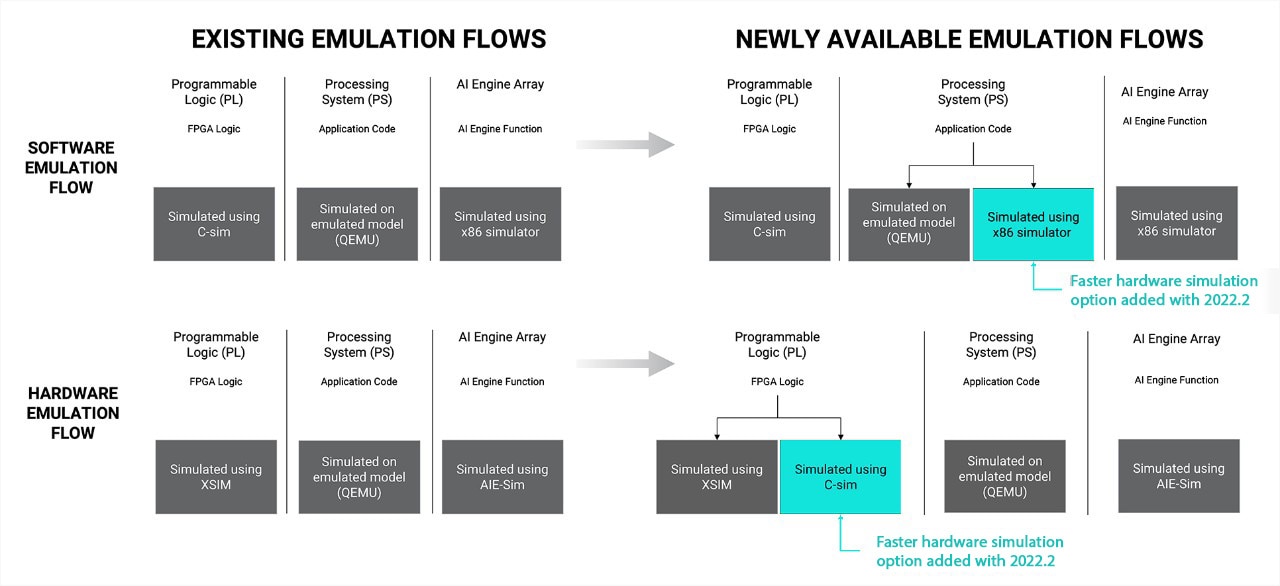

Versal AI Core 및 AI Edge 시리즈의 설계 흐름 개선 사항

- AI 엔진 어레이에서 커널의 상대적 배치 제어 - 성능 및 활용성 향상

- AIE x86 시뮬레이터 개선 사항 - x86 시뮬레이터에서 교착 상태 조건의 모델링 개선

- AIE API 개선 사항 - 기수 3/5 FFT 및 행렬 'x' 벡터 API 추가

- Versal 설계를 위한 프로파일링 및 디버깅 기능 강화 - 교착 상태 감지, 대용량 추적 데이터 수집, RTL/Python 테스트 벤치 지원

- Vitis의 이종 설계를 위한 새로운 시뮬레이션 옵션

Vitis의 범주별 새로워진 사항

아래 섹션을 확장하여 AMD Vitis 소프트웨어 플랫폼 2022.2의 새로운 기능과 개선 사항에 대해 자세히 알아보세요. 지원되는 플랫폼, 변경된 동작 및 알려진 문제에 대한 자세한 내용은 애플리케이션 가속 흐름 및 임베디드 소프트웨어 개발 흐름에 대한 Vitis 소프트웨어 플랫폼 2022.2 릴리스 노트를 참조하세요.

DSP 라이브러리 함수

- AI 엔진의 SSR(슈퍼 샘플링 속도) FIR 필터 구현에서 이제 계수 재로드 기능과 동적 포인트 크기 지원

- AI 엔진 어레이를 타겟팅하는 FFT 함수에 FFT 윈도잉 요소 추가

Solver 라이브러리 함수

- QR(구적 회전) 분해

- 숄레스키 분해

비전 라이브러리 함수

- AI 엔진 어레이를 타겟팅하는 4가지 새로운 비디오 함수

초음파 라이브러리 함수

- 의료 초음파 설계를 구축하는 데 도움이 되는 다양한 함수

- AI 엔진 어레이에서 커널의 상대적 배치를 제어하는 제약 조건을 추가하는 기능 - 이를 통해 사용자는 성능 및 활용성 향상 가능

- x86 시뮬레이터의 AIE 교착 상태 조건 모델링 개선

- 새로운 AIE API 추가 - 기수 3/5 FFT 및 행렬 'x' 벡터 API 추가

- HW 에뮬레이션에서 AI 엔진 프로파일링 보고서 생성

- AI 엔진 및 PL 기반 설계 모두에 XSDB(AMD 시스템 디버거)를 사용한 교착 상태 감지

- PLIO를 통한 AI 엔진 이벤트 추적의 XRT(Xilinx Runtime) 제어 연속 오프로드

- SW 에뮬레이션을 위해 x86 호스트 시스템에서 PS 애플리케이션 지원

- RTL 대신 HW 에뮬레이션을 위한 SystemC 기능 모델 허용

- 사용자가 간단한 RTL 테스트 벤치 또는 Python 스크립트 기반 트래픽 발생기로 AI 엔진 커널 시뮬레이션 가능

- Vitis™ Analyzer를 사용하여 HW 에뮬레이션 중에 AI 엔진 상태 분석 가능

Vitis 환경 2022.2의 새로운 시뮬레이션 옵션: 프로세서 시스템 x86 시뮬레이션 및 AI 엔진 x86 시뮬레이션: x86 시뮬레이터를 사용하여 프로그래밍 가능 로직 시뮬레이션 수행 가능

- Versal AI Engine 설계를 위한 기능

- AI Engine DSP 라이브러리 블록 설계에 그래프 제약 조건 추가 가능 - 활용성 및 성능 향상

- AI Engine 설계의 주기 근사 시뮬레이션을 위한 새로운 기능

- AI Engine 그래프 가져오기 블록이 RTP(런타임 파라미터) 포트를 자동으로 감지

- DSP 라이브러리 블록의 개선 사항 및 추가 사항

- 일반 기능

- PL 및 AIE 어레이를 사용하는 이종 시스템 설계에 지원되는 하드웨어 검증 흐름

- 이종 설계를 지원하도록 Vitis 모델 컴포저 허브 블록 업데이트

- 유효한 AI 엔진, HDL 및 HLS 하위 시스템의 자동 감지

- HDL 전용 설계 및 Versal 플랫폼용 HDL → AI Engine → HDL 설계를 위한 하드웨어 검증 흐름 개선

- 향상된 '태스크 수준 병렬성' 코딩 스타일 지원

- C 시뮬레이션 속도 향상 및 QoR개선

- 추가 성능 및 타이밍 개선 사항

- 버스트 추론 개선

- Unroll, Pipeline, Array_Partition 및 인라인 pragma의 자동 추론으로 성능 향상

- 타이밍 정확도 향상으로 더 높은 주파수에서 타이밍 종결 개선

- 기타 기능

- 분석 및 디버그: C 코드에 삽입된 printf를 이제 RTL내 합성 후에도 지원

- 사용 편의성: 주어진 트랜잭션 간격을 자동으로 달성하는 새로운 성능 pragma

- 이제 FFT 및 FIR IP에서 HLS::stream 인터페이스 지원

Vitis 소프트웨어 플랫폼 2022.1 릴리스 하이라이트:

Versal™ ACAP 및 AI Engine을 위한 Vitis™ 흐름 개선

- 정적 영역 1개와 DFX 영역 1개로 AMD 기반 DFX 플랫폼 지원

- AIE 프로파일링은 중단/교착 상태 감지를 지원하고 Vitis Analyzer에서 AI 엔진 상태(오류 이벤트 포함) 보기 보고서 생성

- x86sim, AIEsim 및 SW 에뮬레이션의 외부 트래픽 발생기는 훨씬 더 유연하며, 시뮬레이션 및 에뮬레이션 흐름에 매우 쉽게 삽입 가능

- Vitis 모델 컴포저가 하드웨어 검증, Linux 및 HW 에뮬레이션 지원

DC용 Vitis 및 Vitis HLS

- Vitis는 동적 영역 생성 프로세스에 대한 추가 보고 지원을 제공하며 흐름 보고 기능 향상에는 3개의 신규 또는 업데이트된 보고서가 포함됨

- Vitis는 성능 향상을 위해 메모리 리소스(권장) 또는 PL의 FIFO로 추적 오프로드 옵션으로 PL 프로파일링을 개선

- 런타임 프로파일을 표시하며 사용자에게는 Vitis HLS GUI가 계속 표시될 수 있는 새로운 타임라인 추적 뷰어를 이제 시뮬레이션 후 사용 가능

- Vitis HLS는 이제 새로운 성능 pragma 또는 set_performance_directive를 통해 더 높은 수준의 "스마트" 구조 유형 지원

- 성능을 위한 L3 API 개선 사항(커널 호출에 1mS 시간 절약)이 적용된 Vitis 그래프 라이브러리

Vitis의 범주별 새로워진 사항

아래 섹션을 확장하여 AMD Vitis 소프트웨어 플랫폼 2022.1의 새로운 기능과 개선 사항에 대해 자세히 알아보세요. 지원되는 플랫폼, 변경된 동작 및 알려진 문제에 대한 자세한 내용은 애플리케이션 가속 흐름 및 임베디드 소프트웨어 개발 흐름에 대한 Vitis 소프트웨어 플랫폼 2022.1 릴리스 노트를 참조하세요.

- 새로운 Genomics 가속기 라이브러리 추가(L1, L2 및 L3)

- 그래프 라이브러리, L3 성능 향상

- Vitis 데이터베이스 라이브러리, GQE 다기능 커널

- 비전 라이브러리에 새로운 함수 추가

- Vitis AIE 비전 라이브러리의 새로운 함수 추가/개선 사항

- Vitis AIE DSP 라이브러리, FIR 리샘플러가 FIR 분수 보간기 대체

- Vitis 코덱 라이브러리 새로운 API, API jxlEnc, API 'leptonEnc', API 'resize', API 'WebpEnc'

Vitis 데이터 압축 라이브러리

- ZLIB 압축 개선, 8KB 솔루션을 위한 맞춤형 옥타코어 압축

- ZLIB 압축 해제 개선, 8KB 파일 크기를 위한 맞춤형 IP

- 플랫폼 기능 쿼리 개선

- HBM 사용 편의성 개선, 커널 M_AXI에 대한 HMSS의 특정 S_AXI 진입점 선택 가능, 구성 파일에서 지원되는 RAMA 삽입

Vitis AI Engine 컴파일러

- AI 엔진 자동 중단/교착 상태 감지 및 하드웨어에서의 분석

- 자동 상태 출력 분석

- 자동 상태 출력 분석 - 버퍼

- 하드웨어에서 수동 상태 출력 분석

- 수동 상태 출력 분석

- AI 엔진 이벤트 추적 기능 향상

- 외부 트래픽 발생기 AIEsim

- HW의 AI 엔진 프로파일링 개선

- 브로드캐스트 창에 대한 AI 엔진 지원

- Vitis AI Engine 컴파일러 그래프 프로그래밍 모델 개선

- Vitis AI Engine 컴파일러 - ADF 그래프의 PLIO/GMIO

Vitis HLS

- 분석 기능 개선, 새로운 타임라인 추적 뷰어

- 코딩 스타일 개선, 블록 스트림 유형에 대한 어레이 분할 지원

- pragma 추상화, 새로운 성능 pragma(및 지시문)

- Vitis Core "원 라이너", Vitis HLS - 새로운 타임라인 추적 뷰어, 새로운 성능 pragma, 블록 스트림 지원 창

- 새로운 뷰어 도입

- 설계에 남아 있는 모든 함수(모듈로 변환된 함수)의 런타임 프로파일 표시

- 공동 시뮬레이션 후 데이터 흐름 영역의 동작을 확인하는 데 특히 유용

- Vitis HLS에 기본 제공 - 더는 xsim 파형 뷰어를 실행할 필요 없음(외부 도구)

Vitis Analyzer

- Vitis Analyzer 개선, 타임라인 맞춤형 저장/복원

- 보고 기능 개선, report_qor_assessment, xclbin 클러킹 정보, Vivado 자동화 요약

- 프로파일링 개선, 새로운 PL 프로파일링 인프라 활성화, 여러 메모리 모니터를 삽입하기 위해 여러 trace_memory 옵션 추가 가능(HW 전용), SLR0~DDR0의 모든 CU에 대한 추적 데이터를 오프로드하고 SLR1~DDR1의 모든 CU에 대해서도 추적 데이터를 오프로드하기 위한 v++ 링커용 샘플 구성 파일

Vitis IDE

- Versal용 Bootgen GUI 업데이트

- 툴체인 업데이트

- XSCT, 지원 STAPL, 링커 스크립트 생성 명령 추가

- 시스템 컴파일 흐름, 시스템 컴파일 문서 참조

Vitis 에뮬레이션

- 자동 재시작을 위한 소프트웨어 에뮬레이션 지원과 상시 실행 커널을 위한 메일박스 지원 추가

- sw-emu 중(1) 프리 러닝 커널 불필요

- 외부 트래픽 발생기에 대한 소프트웨어 에뮬레이션 지원 추가

- 하드웨어 에뮬레이션은 스트리밍 IP에 HLS C 소스 코드 함수 모델 사용 가능

- 장치 수를 조사하기 위한 API xrt::system 추가

- 메시지 로깅을 위한 API xrt::message 추가

- XRT 네이티브 API 호스트 코드에 이제

-std=c++17 이상 필요 - 동기 작업의 비동기 실행을 위한 실험용 xrt::queue API 추가

- xbutil은 AIE 교착 상태 시나리오를 디버깅하는 데 도움이 되는 AIE FIFO 카운터 표시 가능

- xbutil --legacy 옵션 제거

- xclbinutil --info에서 임베디드 플랫폼에 대한 클럭 정보 제공

- ARM의 xbutil은 SOM 이미지 로드 가능

- xbtop 독립형 유틸리티는 linux top과 같은 출력 표시(레거시 xbutil -top 대체)

- XRT 유틸리티는 Tab 키를 사용하여 Bash에서 자동 완성 지원

- Alveo 플랫폼 업데이트, 안정성 향상을 위한 플랫폼 업데이트, 카드 관리 업데이트, SC 펌웨어 업데이트 도구

- 임베디드 플랫폼인 새로운 VCK190 DFX 플랫폼: xilinx_vck190_base_dfx_202210_1, 임베디드 플랫폼은 이제 Vitis와 함께 설치되며, Vivado에서 새로운 맞춤형 예제 설계 추가: MPSoC용 Vitis 플랫폼

- 확장성 및 사용 편의성을 위한 Vitis 모델 컴포저 허브 블록의 주요 개선 사항

- 하드웨어 검증 흐름은 이제 베어 메탈 외에도 Linux를 지원

- "AIE-HDL" 및 "HDL-AIE" 블록에 HDL 게이트웨이 블록이 더는 포함되지 않음

- 2022.1은 이제 인터넷에 접속할 수 없는 고객을 위해 예제 스냅샷과 함께 제공 이 도구는 GitHub에서 예제의 새 개정판을 다운로드하라는 메시지를 사용자에게 표시(사용 가능한 경우)

- 사용 편의성을 위해, 코드 생성에 포함되지 않은 유틸리티 블록의 배경색은 이제 흰색으로 표시

- 사용 편의성을 위해 라이브러리 브라우저 개선 및 재구성

- RHEL 8.x 지원

- MATLAB 지원 - R2021a 및 R2021b

Vitis 소프트웨어 플랫폼 2021.2 릴리스 하이라이트:

- 새로운 도메인별 개발 환경

- Kria™ SOM, Alveo™ U30/U50 및 VCK5000 Versal™ 개발 카드의 Vitis™ 비디오 분석 SDK: 자세히 알아보기 >

- Vitis Libs를 통한 Varium™ C1100 카드의 Vitis 블록체인 솔루션: 자세히 알아보기 >

- VCK5000 및 Varium C1100 카드에 대한 포괄적인 전체 흐름 지원

- 개선된 핵심 도구 기능

- Vitis AI Engine 컴파일러 C/C++ 고수준 추상화 API, 자동 pragma 추론, 영역 그룹 제약 조건

- Vitis AI Engine x86 시뮬레이터 개선 사항: 추적 보고서, 메모리 액세스 위반 및 교착 상태 감지

- Vitis HLS EoU, 타이밍 및 QoR 개선, 사용자 제어 버스트 추론을 위한 HLS API

- 더 나은 타임라인 추적 보고서, 데이터 시각화, 중단 분석을 위해 Vitis Analyzer 개선

- AI 엔진 그래프 제어를 위한 AI 엔진용 Vitis XRT의 다중 프로세스 및 멀티스레드 지원

- Vitis IDE 및 에뮬레이션은 AI 엔진 추적, AI 엔진 애플리케이션을 위한 SW 에뮬레이션을 지원

- DSP, 데이터 분석, 비전, 압축, 데이터베이스, 그래프, 보안을 포괄하는 다양한 영역의 새로운 39개 C/C++ 라이브러리, 총 1000개가 넘는 라이브러리 함수, 데이터베이스, 그래프, 보안 등

- Vitis 모델 컴포저

- 병렬 컴파일을 통해 컴파일/시뮬레이션 시간 3배 단축, 컴파일 시간 7배 단축

- 새로운 하드웨어 검증 흐름 및 개선된 기능적 공동 시뮬레이션

Vitis의 범주별 새로워진 사항

아래 섹션을 확장하여 AMD Vitis 소프트웨어 플랫폼 2021.2의 새로운 기능과 개선 사항에 대해 자세히 알아보세요. 지원되는 플랫폼, 변경된 동작 및 알려진 문제에 대한 자세한 내용은 애플리케이션 가속 흐름 및 임베디드 소프트웨어 개발 흐름에 대한 Vitis 소프트웨어 플랫폼 2021.2 릴리스 노트를 참조하세요.

참고: Vitis 가속 라이브러리는 별도로 다운로드할 수 있습니다. 또한 GitHub에서 다운로드하거나 Vitis IDE 내에서 직접 다운로드할 수도 있습니다.

| 라이브러리 | 2021.1 | 2021.2 | 21.2의 새로운 함수 |

|---|---|---|---|

| xf_blas | 167 | 167 | 0 |

| xf_codec | 3 | 3 | 0 |

| xf_DataAnalytics | 33 | 36 | 3 |

| xf_database | 62 | 65 | 3 |

| xf_compression | 78 | 93 | 15 |

| xf_dsp | 94 | 96 | 2 |

| xf_graph | 53 | 59 | 6 |

| xf_hpc | 37 | 37 | 0 |

| xf_fintech | 116 | 116 | 0 |

| xf_security | 135 | 140 | 5 |

| xf_solver | 11 | 11 | 0 |

| xf_sparse | 11 | 11 | 0 |

| xf_utils_hw | 55 | 57 | 2 |

| xf_opencv | 147 | 150 | 3 |

| 합계 | 1002 | 1041 | 39 |

참고: 비전의 경우 각 API에 다양한 유형에 대한 여러 테스트가 있으므로 L*/테스트의 하위 폴더 수만 세면 됩니다.

Vitis 비전 라이브러리

- PL(프로그래밍 가능 로직)

- CLAHE TMO를 통한 포괄적인 모노 이미지 처리(ISP)

- RGB-IR과 RGB-IR 이미지 처리(ISP) 파이프라인

- GTM(글로벌 톤 매핑)과 GTM을 사용하는 ISP 파이프라인

| 새로운 기능 | 범주 | 고객/전략 | 부문 | 설명 |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | 자동차, ISM | •4x4 RGB-IR 디모자이킹 지원 •주로 실내 모니터링 시스템용 •저조도 감시 카메라 |

| 모노(CCCC) | ISP | 전략 | 자동차, ISM, A&D | •머신 비전 •저조도 응용 분야 |

| GTM(글로벌 톤 매핑) | ISP | 전략 | 자동차, ISM, A&D | •개선된 다이나믹 레인지 및 대비 •LTM(로컬 톤 매핑) 대비 저비용 버전 |

| Dense Optical Flow TV-L1 | CV | NTT | ISM | •광학 흐름에 대한 견고성 향상(조도, 노이즈, 오클루전 대응) |

AIE(AI 엔진)

- BlobFromImage

- 배치 크기 3을 지원하는 백투백 Filter2D

| 새로운 기능 | 범주 | 고객/전략 | 부문 | 설명 |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | 자동차, ISM | •4x4 RGB-IR 디모자이킹 지원 •주로 실내 모니터링 시스템용 •저조도 감시 카메라 |

| ML+X | ISP | 전략 | 자동차, ISM, A&D | •ML 간섭 전처리 |

| 가우스 피라미드 | CV | 전략 | 자동차, ISM, A&D | •다중 스케일 이미지 처리의 기본 |

| 박스 필터 | CV | 전략 | 자동차, ISM, A&D | •원활한 로우패스 필터의 기본 |

Vitis 데이터 분석 라이브러리

- Vitis 라이브러리를 기반으로 한 Vitis 블록체인 솔루션

- 즉시 사용 가능한 Ethereum용 채굴 솔루션

- 오픈 소스, C++를 사용하는 Vitis Libs를 통한 사용 및 배포 용이

- Vitis Libs를 통한 유연성 및 확장성

- 여러 코인을 유연하게 채굴 가능

- 맞춤화 및 하드웨어로 컴파일

- 고도로 최적화된 설계

- 라이브러리에 CSV 파서 API 추가

- CSV 파서는 쉼표로 구분된 값 파일을 구문 분석하고 DataFrame API와 쉽게 연결할 수 있는 객체 스트림 생성 가능

Vitis 그래프 라이브러리

- 새 L2 라이브러리 추가

- 번호 다시 매기기를 사용하는 Louvain

- 번호 다시 매기기

- 코사인 유사도에 대해 '가중치' 기능 지원

Vitis 데이터베이스 라이브러리

- GQE는 다중 카드 지원과 함께 비동기 입출력 기능을 지원하기 시작합니다.

- 비동기 지원을 통해 FPGA는 입력 데이터의 일부가 준비되는 즉시 처리를 시작할 수 있습니다.

- 다중 카드 지원을 통해 작업에 적합한 여러 개의 Alveo 카드를 식별할 수 있습니다.

Vitis 데이터 압축 라이브러리

- ZSTD 멀티코어 압축

- 새로운 ZSTD 멀티코어 아키텍처를 생성하고 쿼드코어를 사용하여 1GB/s 이상의 처리율 제공

- ZSTD 압축 해제 최적화

- 성능(20% 증가) 및 리소스(30% 미만 감소)를 위해 최적화된 ZSTD 압축 해제

- IBM을 위한 GZIP/ZLIB 스트림 코어 개선

- 맞춤형 정적 및 동적 압축 스트리밍 IP(4KB 및 8KB)

- TUSER 포트에 압축 크기를 제공하는 기능 추가

- IBM을 위한 GZIP/ZLIB 압축 해제 개선

- 지연율을 1.5K 사이클 미만으로 줄이기 위해 최적화된 허프만 디코더

- 리소스를 6.9K로 대폭 감소(기존 > 9K)

- ADLR32 체크섬 기능 추가

- GZIP 시스템 컴파일러 PoC

- GZIP 압축 솔루션용 시스템 컴파일러 PoC를 생성하고 OpenCL 호스트에 대해 벤치마킹

Vitis DSP 라이브러리

- 2021부터 GitHub에서 DSPLib 제공

- Fast Fourier Transform (FFT/iFFT)

- 포인트 크기가 32k로 증가(데이터 형식에 따라 다름)

- 스트림 API와 윈도우 API 모두 지원

- 병렬 출력(0~4)

- 처리율을 높이고 지원되는 포인트 크기의 범위 확장

- FIR 필터

- 단일 속도 비대칭/대칭 FIR에 대한 초기 스트림 지원

- DDS/믹서

- 2021.2의 새로운 라이브러리 유닛

Vitis 보안 라이브러리

- KECCAK-256(해시 함수) 및 CRC32C(체크섬 함수) 릴리스

Vitis 유틸리티 라이브러리

- HW 문제를 디버깅하기 위해 2개 Data-Mover 구현 추가

- LoadDdrToStreamWithCounter: AXI 스트림을 통해 PL의 DDR에서 AI 엔진으로 데이터를 로드하고, AI 엔진으로 전송하는 데이터 수를 기록합니다.

- StoreStreamToMasterWithCounter: AXI 스트림을 통해 AI 엔진에서 데이터를 수신하여 PL의 DDR에 저장하고, DDR로 전송하는 데이터 수를 기록합니다.

AI 엔진 API

- 효율적인 AI 엔진 내장 함수로 변환되는 형식과 연산을 제공하는 C++ 헤더 전용 라이브러리로 구현

- 제네릭 프로그래밍을 가능하게 하는 파라미터화 가능한 데이터 형식 제공

- 다양한 데이터 형식에 대해 균일한 방식으로 가장 일반적인 연산 구현

- 더 높은 수준의 프리미티브를 최적화된 AI 엔진 내장 함수로 투명하게 변환

- AI 엔진 아키텍처 전반의 이식성 향상

AI 엔진 API는 AI 엔진 커널 프로그래밍을 위한 주요 방법이 될 것입니다.

높은 수준의 최적화

AI 엔진 컴파일러 최적화 옵션

- --xlopt=0, 최적화 미적용

- --xlopt=1, 힙 크기의 자동 계산, LLVM IR 분석을 통한 가이드 생성

- --xlopt=2, 자동 인라이닝, 풀린 루프에 대한 루프 필링, pragma 삽입

성능 향상을 위해 --xlopt=2 도입, 기본값은 --xlopt=1로 유지

- 자동 인라인

- 함수가 __inline 또는 inline으로 선언되지 않았더라도 실용적이고 가능하다면 함수를 자동으로 인라인

- 자동 pragma 삽입

- 자동으로 커널 코드에 pragma 삽입 (자세한 내용은 다음 슬라이드 참조)

pragma 추론

커널 최적화에 필요

- 효과적이고 정확한 chess pragma를 추가하는 사용자의 책임 완화

2021.2에서 다섯 가지 pragma 자동 추론 지원

- 성능 관련:

- 맨 안쪽 루프와 트립 카운트가 알려진 외부 루프의 경우 chess_prepare_for_pipelining

- 트립 카운트가 알려진 루프의 경우 chess_loop_range

- 트립 카운트가 알려진 맨 안쪽 루프의 경우 chess_unroll_loop/chess_flatten_loop

- 정확성 관련:

- 트립 카운트가 언롤 계수의 배수가 아닌 경우 chess_unroll_loop_preamble

그래프 프로그래밍 모델 PLIO 및 GMIO 업데이트

모델 변경 사항:

- "simulation::platform" 사용 변경

- 그래프에서 PLIO/GMIO 객체와의 상호 작용, 위치가 입력/출력을 결정

- 그래프에서 전역 PLIO/GMIO 객체의 변경 사항

- 그래프 connect<> 문 주변의 변경 사항

ADF 그래프의 PLIO/GMIO

현재

- PLIO, GMIO, simulation::platform, connection을 전역 범위에서 작성

GMIO gm0(“GMIO_In0”, 64, 1);

GMIO gm1(“GMIO_In1”, 64, 1);

…

GMIO gm7(“GMIO_In7”, 64, 1);

PLIO pl0(“PLIO_Out0”, plio_32_bits, “data/output0.txt”, 250.0);

PLIO pl1(“PLIO_Out1”, plio_32_bits, “data/output1.txt”, 250.0);

…

PLIO pl7(“PLIO_Out7”, plio_32_bits, “data/output7.txt”, 250.0);

simulation::platform<8,8> plat(&gm0, &gm1,…, &gm7, &pl0, &pl1,…, &pl7,);

subgraph g;

connect<> net0(plat.src[0], g.in[0]);

connect<> net1(plat.src[1], g.in[1]);

…

connect<> net7(plat.src[7], g.in[7]);

connect<> net8(g.out[0], plat.sink[0]);

connect<> net9(g.out[1], plat.sink[1]);

…

connect<> net15(g.out[7], plat.sink[7]);

대체 방법

- 최상위 그래프를 만들고 PLIO, GMIO 및 연결을 내부로 이동

- for 루프 내에서 연결 관리 허용

class topgraph

{

input_gmio gm[8];

output_plio pl[8];

subgraph sg;

topgraph()

{

for (i=0; i<8; i++)

{

gm[i] = input_gmio::create(“GMIO_In”+std::to_string(i), 64, 1);

pl[i] = output_plio::create(“PLIO_Out”+std::to_string(i), plio_32_bits, “data/output”+std::to_string(i)+”.txt”, 250.0);

connect<>(gm[i].out[0], sg.in[i]);

connect<>(sg.out[i], pl[i].in[0]);

}

}

};

topgraph g;

영역 그룹 제약 조건 개선

ADF 그래프 또는 제약 조건 파일에서 플래그를 사용하여 매퍼와 라우터를 제어하는 기능

- -contain_routing - true로 지정하면 nodeGroup에 포함된 노드 간의 네트워크를 포함한 모든 라우팅을 영역 그룹 내에 포함됩니다.

- -exclusive_routing - true로 지정하면 nodeGroup의 노드 간 네트워크를 제외한 모든 라우팅이 영역 그룹에서 제외됩니다.

- -exclusive_placement - true로 지정하면 nodeGroup에 포함되지 않은 모든 노드가 영역 그룹 경계 상자 내에 배치되지 않습니다.

스냅샷

스냅샷은 모든 커널 포트 관련 주석 및 데이터가 포함된 텍스트 파일입니다.

- 스트림, 패킷 스트림, 캐스케이드 스트림

- 윈도우, 버퍼

- RTP

모든 플랫폼 포트 포함

- PLIO, GMIO, RTP

사용자가 디버거를 사용하지 않고 커널 코드 계측 필요 없이 커널 포트에서 데이터 트래픽을 검사할 수 있습니다.

교착 상태 감지

- 이 상황이 입력 데이터 부족에서 기인하든, 불균형 FIFO 깊이에서 기인하든 관계없이 x86 시뮬레이션에서 교착 상태 감지

- x86 시뮬레이션 중에 --stop-on-deadlock 옵션을 지정하여 stop-on-deadlock 기능을 활성화해야 함

- 시뮬레이션이 교착 상태로 인해 멈추는 경우 -trace --timeout 옵션을 사용하여 다시 실행해야 한다는 오류 메시지 표시

메모리 액세스 위반 감지

메모리 액세스 위반 감지를 위한 Valgrind와의 통합

- 감지

- 읽기 및 쓰기 범위 이탈

- 초기화되지 않은 메모리 읽기

- 컴파일에 특정 플래그 불필요

- 시뮬레이션 플래그는 다음 중 하나일 수 있음

- --valgrind: 시뮬레이션이 평소와 같이 실행되며 valgrind에서 보고서를 표시

- --valgrind-gdb: 위와 동일하나 동시에 gdb 디버그 가능

추적 보고서

교착 상태 상황은 시뮬레이션 출력 저하와 버그 출처 분석에 어려움을 초래합니다.

x86 시뮬레이션 추적 옵션을 사용하면 시뮬레이터가 다양한 타임스탬프 정보를 기록할 수 있습니다.

- 커널 반복 시작/종료

- 스트리밍 중단 시작/종료

- 잠금 중단 시작/종료

x86 시뮬레이션과 AI 엔진 시뮬레이션의 타임스탬프는 서로 다릅니다.

사용자 제어 버스트 추론

- Vitis HLS 도구의 자동 버스트 추론을 충족하지 못하는 사용 사례의 경우, 사용자가 새로 도입된 수동 버스트 최적화 채택 가능

- 버스트 동작 수동 제어를 지원하는 새로운 클래스 'hls::burst_maxi'. 새로운 클래스와 함께 사용할 수 있도록 새로운 HLS API 제공

- 사용자는 AXI AMBA 프로토콜과 HLS 설계의 하드웨어 트랜잭션 수준 모델링 이해 필요

타이밍 및 QoR 개선 사항

- 사용자가 높은 수준의 처리율 제약 조건을 입력할 수 있도록 지원

- HLS 타이밍 추정 정확도 향상. HLS가 타이밍 종결을 보고할 때 Vivado의 RTL 합성도 타이밍을 충족할 것으로 예상

EoU 개선 사항

C 합성 보고서에 인터페이스 어댑터 보고서 추가

- 사용자는 인터페이스 어댑터가 설계에 미치는 리소스 영향을 알아야 합니다.

- 인터페이스 어댑터에는 설계 QoR에 영향을 주는 가변 속성이 있습니다.

- 이러한 속성 중 일부에는 사용자에게 보고해야 하는 사용자 컨트롤이 연결되어 있음

- bind_op 및 bind_storage 보고서의 텍스트 버전 제공

pragma 및 pragma에 대한 경고 목록을 표시하기 위해 합성 보고서에 새 섹션 추가

- 사용자는 추가되는 pragma 중 문제가 있는 pragma를 쉽게 이해 가능

분석 및 보고 개선 사항

함수 호출 그래프 뷰어에는 다음과 같은 몇 가지 새로운 기능이 있습니다.

- 새로운 마우스 드래그 기반 확대 및 축소 기능

- 전체 그래프를 표시하고 전체 그래프의 일부를 사용자가 확대할 수 있는 새로운 개요 기능

- 모든 함수와 루프가 해당 시뮬레이션 데이터와 함께 표시됨

이제 시뮬레이션 후 새로운 Timeline Trace Viewer(타임라인 추적 뷰어)를 사용할 수 있습니다. 이 뷰어는 설계의 런타임 프로파일을 보여주며, 사용자는 Vitis HLS GUI에서 작업을 계속할 수 있습니다.

링크 요약 개선

- AI 엔진, 플랫폼 및 컴퓨팅 유닛에 대한 클럭 주파수 정보 제공

- 시스템 다이어그램 및 플랫폼 다이어그램에서 클럭이라는 새 테이블 제공

플랫폼 내보내기 개선

- Vivado에서 XSA 내보내기에는 프로젝트에 로컬인 소스 파일 불필요

- Vivado에서 XSA 내보내기에는 프로젝트 구조 변경 없음

- 전체 IP 리포지토리를 패키징하는 대신 하드웨어 플랫폼 프로젝트에 사용되는 IP를 패키징

AI 엔진 애플리케이션 에뮬레이션 개선 사항

- aiesimulation을 통한 외부 테스트 벤치 통합 지원 제공

- x86 시뮬레이션을 통한 외부 테스트 벤치 통합 지원 제공

- x86 시뮬레이션을 통한 GDB 디버깅 지원

- x86 시뮬레이션을 위한 그래프의 커널 간 데이터 스냅샷 지원 제공

- x86 시뮬레이션에 대한 액세스 위반 검사 지원 제공

- x86 시뮬레이션에 대한 교착 상태에서 중지 지원

AI 엔진 추적 지원

AI 엔진 애플리케이션을 위한 SW 에뮬레이션 지원

Verilog/System Verilog의 외부 트래픽 발생기 지원

모니터 메모리로 프로파일링 모니터 삽입 확장

- 현재 프로파일링 모니터 로직은 커널/CU 포트 기반으로 삽입 가능 이 기능은 사용자에게 메모리 인터페이스에 직접 모니터 로직을 삽입할 수 있는 옵션을 제공

- 메모리 인터페이스에서 직접 달성한 메모리 대역폭의 시각화를 프로파일 요약 보고서에 반영 가능

- DDR 메모리 및 PLRAM 지원

- 하드웨어 흐름 지원

- 이 기능을 활성화하려면 연결 단계와 XRT를 모두 설정해야 함

- memory=all

- data_transfer_trace= coarse|fine 또는

- opencl_device_counter=true

모니터 메모리로 프로파일링 모니터 삽입 확장

- 메모리 인터페이스 모니터링을 활성화하는 vadd 예제

- 새로운 '메모리 뱅크 데이터 전송' 테이블 포함

Vitis Analyzer 개선 사항

OpenCL이 아닌 애플리케이션에 대해 생성된 제네릭 프로파일 요약 보고서

- XRT API 및 HAL API 애플리케이션에 대해 동일한 수준의 지원 제공

- 사용자가 생성하려는 보고서 유형을 선택하면 Vitis Analyzer에서 자동으로 생성 및 시각화

PL 이벤트 타임라인에 OpenCL 명령 추가

- 프로파일링은 오버헤드를 추가하며, XRT는 오버헤드 없이 타임라인 추적에 OpenCL 이벤트를 덤프하는 기능을 제공

- Vitis Analyzer는 XRT 출력을 처리하여 타임라인 추적 보기에 표시 가능

- xocl_debug=true는 xrt.ini에서 설정 필요

타임라인 추적 보고서의 신호 계층 구조 평면화

- 기본적으로 타임라인 추적 보고서는 신호 추적을 계층적 방식으로 표시

- Vitis Analyzer는 "신호 평면화" 기호를 토글하여 계층 구조 평면화 기능 제공

- 평면화된 타임라인 추적에 대해 파형 비교 지원

Vitis Analyzer - 데이터 시각화

- AI 엔진 설계에서 AI 엔진 커널에 대한 입력/출력 데이터 표시

- 타임라인과 함께 입력/출력 데이터를 표시하도록 AI 엔진 설계 디버깅 지원

- aiesimulator와 함께 작동

- 지원

- 윈도우/스트림/캐스케이드 데이터 형식

- 패킷 스트림

- 템플릿형 커널

- 데이터 덤프 유틸리티

Vitis Analyzer - AI 엔진 중단 분석

- Vitis Analyzer는 사용자가 중단의 근본 원인을 식별할 수 있도록 시각화 기능을 제공

- 지원

- 성능 지표

- 잠금 중단 분석

- 스트리밍 중단 분석

- 캐스케이드 중단 분석

- 메모리 중단 분석

- 지원 흐름

- aiesimulator

- HW 에뮬레이션

XRT(Xilinx 런타임 라이브러리):

- XRT API

- XRT 네이티브 API는 xrt::ip를 통한 사용자 관리 커널 제어를 지원

- XRT 유틸리티

- xbutil 및 xbmgmt 도구를 이제 기본적으로 사용

- 레거시 유틸리티를 사용하려면 xbutil --legacy 또는 xbmgmt --legacy를 레거시 하위 명령과 함께 사용

- 새로운 유틸리티인 xball

- 설치된 데이터 센터 카드의 전체 또는 필터링된 부분에 xbutil 또는 xbmgmt 명령 적용. 자세한 내용은 xball --help 참조

- 새로운 명령인 xbutil configure

- PCIe 호스트 메모리 및 PCIe 피어 투 피어 기능을 활성화, 비활성화 또는 구성 가능 자세한 내용은 XRT 문서 참조

- 모든 XRT 유틸리티는 이제 사용자 상호 작용 확인을 건너뛰기 위해 --force 옵션을 전역적으로 지원

- xbutil 및 xbmgmt 도구를 이제 기본적으로 사용

- 프로파일링

- 프로파일링 옵션이 활성화되면 프로파일 요약 보고서가 생성됨

- 적용 가능한 모든 요약표 및 지침은 xrt.ini 파일에서 활성화된 프로파일링 옵션을 기반으로 생성

- 설계에서 모니터가 메모리 리소스에 추가될 때 메모리 리소스에 대한 집계 정보를 위한 새로운 데이터 전송 요약표

- (1) AIE의 부동 소수점 예외, (2) 타일 실행 횟수, (3) 스트림 넣기 및 가져오기를 포함한 다양한 AIE 이벤트를 계산하기 위한 새로운 AIE 프로파일링 메트릭 세트

- 임베디드

- 모든 sptag를 지원하기 위한 zocl 메모리 관리자 개선

AI 엔진용 Vitis XRT의 다중 프로세스 지원

- 여러 프로세스가 동일한 AI 엔진 어레이 및 그래프에 대한 액세스를 공유할 수 있도록 액세스 모드를 정의하는 C 및 C++ API

- 원치 않는 액세스로부터 AI 엔진 어레이 및 그래프 보호

- AI 엔진 어레이 및 그래프 열기에 대한 세 가지 모드 지원

- 독점 모드(다른 프로세스의 액세스 방지)

- 기본 모드(다른 프로세스의 비파괴적 액세스만 허용)

- 공유 모드(비파괴적 액세스만 수행)

- 여러 프로세스 지원이 필요한 경우에 고려. 예:

- 다른 사람이 AI 엔진 어레이에 액세스하는 것을 방지(독점 액세스)

- 여러 사용자가 서로 다른 그래프를 개별적으로 제어(여러 애플리케이션 지원)

- 한 명의 기본 사용자가 그래프를 제어하고 다른 사용자는 실행 상태를 확인할 수 있도록 허용(기본 및 공유 액세스)

AI 엔진용 Vitis XRT의 지원 상태

C 및 C++ API

- C 버전 API

- AI 엔진 어레이:

- xrtAIEDeviceOpenExclusive(독점 모드)

- xrtAIEDeviceOpen(기본 모드)

- xrtAIEDeviceOpenShared(공유 모드)

- AI 엔진 그래프:

- xrtGraphOpenExclusive(독점 모드)

- xrtGraphOpen(기본 모드)

- xrtGraphOpenShared(공유 모드)

- AI 엔진 어레이:

- C++ 버전 API

- xrt::aie::device 클래스는 생성자에서 액세스 모드 지원

- enum class access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2 };

- xrt::graph 클래스는 생성자에서 액세스 모드 지원

- enum class access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2, none = 3 };

- xrt::aie::device 클래스는 생성자에서 액세스 모드 지원

- Alveo 카드용 최신 Vitis Target 플랫폼에 액세스하고 가속기 카드의 시작하기 섹션을 참조하세요.

- Vitis를 다운로드하고 Alveo 패키지 섹션을 참조하세요.

AI 엔진 DSP 라이브러리 - 새로운 블록

- AIE DDS

- AIE 믹서

병렬 컴파일

- 2021.1 대비 시간 단축(예를 들어, 다음 수치는 200MHz TX 체인에 해당)

- 컴파일 및 시뮬레이션 시간 3배 단축

- 컴파일 시간 7배 단축

- 시뮬레이션 후 부동 시간이 25초에서 약 0초로 단축

제약 조건 편집기 개선

- 2021.2 탐색 기능 개선

고정 크기 개선

가변 크기 블록 개선

기능적 공동 시뮬레이션 기능 개선

- AI 엔진 입력을 위한 Matlab 데이터 내보내기 - xmcVitisWrite

- Matlab으로 AI 엔진 데이터 가져오기 - xmcVitisRead

- Matlab으로 AI 엔진 데이터 가져오기 - xmcVitisRead

기타

- 입력이 없는 AI 엔진 또는 HLS 커널 블록 가져오기(소스 블록)

- 새로운 데이터 형식 지원

- AMD 데이터 형식 대신 AI 엔진 개발을 위한 Simulink 네이티브 int64 및 uint64, x_sfix64 및 x_ufix64

- AI 엔진 개발을 위한 accfloat 및 caccfloat

- Ubuntu 20.04 지원

- MATALB 20a, 20b, 21a 지원(MATLAB 21b는 미지원)

- 새로운 예제 추가

- 64개 커널을 사용하는 듀얼 스트림 SSR 필터 예제

- 의사 역행렬(64x32) - commslib 예제

- xmcLibraryPath 명령을 사용하여 맞춤형 DSPLib 위치를 가리킴

- 더 많은 개선 사항 및 버그 수정 사항

Vitis 소프트웨어 플랫폼 2021.1 릴리스 하이라이트:

- AMD Kria SOM(System-On-Module) KV260 Vision AI 스타터 키트 지원. ML(DPU 추론 엔진) + X(RTL 커널 및 Vitis HLS 기반 컴퓨터 비전 커널)의 전체 Vitis 흐름. 자세히 알아보기 >

- CPU/GPU를 통한 FPGA 및/또는 Versal ACAP에서 새로운 C/C++ Vision, DSP, 그래프(Louvain Modularity), 이미지 처리의 코덱, 압축(GZIP, Facebook ZSTD, ZLIB 전체 애플리케이션 가속) 성능 최적화 라이브러리 지원

- Versal ACAP 디바이스의 Vitis™ 핵심 개발 키트 설계 흐름 개선: AI 엔진 설계 추적 보고서를 위한 시각화 개선, GMIO를 통한 AI 엔진 이벤트 추적, 증분 재컴파일, 새로운 부팅 이미지 마법사 및 암호화된 AI 엔진 소스 파일 지원

- 새로운 Vitis 모델 컴포저 도구를 사용하면 MathWorks MATLAB 및 Simulink® 환경에서 빠르게 설계를 탐색하고 검증할 수 있어 AI 엔진 및 프로그래밍 가능 로직을 타겟팅하는 블록의 공동 시뮬레이션, 코드 생성, 테스트 벤치 생성이 가능

- 새로운 Vitis HLS Flow Navigator GUI를 통해 흐름 단계 및 보고서에 빠르게 액세스. 합성, 분석 및 디버그 보기를 일반 기본 컨텍스트로 병합

Vitis의 범주별 새로워진 사항

아래 섹션을 확장하여 AMD Vitis 소프트웨어 플랫폼 2021.1의 새로운 기능과 개선 사항에 대해 자세히 알아보세요. 지원되는 플랫폼, 변경된 동작 및 알려진 문제에 대한 자세한 내용은 애플리케이션 가속 흐름 및 임베디드 소프트웨어 개발 흐름에 대한 Vitis 소프트웨어 플랫폼 2021.1 릴리스 노트를 참조하세요.

참고: Vitis 가속 라이브러리는 별도로 다운로드할 수 있습니다. 또한 GitHub에서 다운로드하거나 Vitis IDE 내에서 직접 다운로드할 수도 있습니다.

AIE DSP

- GitHub에 설정된 Vitis 가속 라이브러리의 일부로 게시된 DSPLib

- DSPLib에는 많은 고급 신호 처리 애플리케이션에서 사용되는 공통 파라미터화 가능 DSP 기능이 포함되어 있습니다. 현재 모든 기능은 스트리밍 인터페이스를 지원하는 윈도우 인터페이스를 지원합니다.

FIR 필터

기능 |

네임스페이스 |

단일 속도, 비대칭 |

dsplib::fir::sr_asym::fir_sr_asym_graph |

단일 속도, 대칭 |

dsplib::fir::sr_sym::fir_sr_sym_graph |

보간 비대칭 |

dsplib::fir::interpolate_asym::fir_interpolate_asym_graph |

데시메이션, 반대역 |

dsplib::fir::decimate_hb::fir_decimate_hb_graph |

보간, 반대역 |

dsplib::fir::interpolate_hb::fir_interpolate_hb_graph |

데시메이션, 비대칭 |

dsplib::fir::decimate_asym::fir_decimate_asym_graph |

보간, 분수, 비대칭 |

dsplib::fir::interpolate_fract_asym:: fir_interpolate_fract_asym_graph |

데시메이션, 대칭 |

dsplib::fir::decimate_sym::fir_decimate_sym_graph |

FFT/iFFT - DSPLib에는 하나의 FFT/iFFT 솔루션이 포함되어 있습니다. 이는 구성 가능한 포인트 크기, 복소수 데이터 형식, 캐스케이드 길이 및 FFT/iFFT 기능을 갖춘 단일 채널, 단일 커널 DIT(Decimation in Time) 구현입니다.

기능 |

네임스페이스 |

단일 채널 FFT/iFFT |

dsplib::fft::fft_ifft_dit_1ch_graph |

행렬곱(GeMM) - DSPLib에는 하나의 행렬곱/GEMM(일반 행렬곱) 솔루션이 포함되어 있습니다. 이는 구성 가능한 입력 데이터 형식으로 2개의 행렬 A와 B의 행렬 곱셈을 지원하여 파생된 출력 데이터 유형을 생성합니다.

기능 |

네임스페이스 |

행렬곱/GeMM |

dsplib::blas::matrix_mult::matrix_mult_graph |

위젯 유틸리티 - 이러한 위젯은 DSPLib 함수의 입력에서 윈도우와 스트림 간 변환을 지원하고, 필요한 경우 DSPLib 함수의 출력에서 스트림과 윈도우 간 변환을 지원하며, 실수와 복소수 데이터 형식 간 변환을 위한 추가 위젯을 지원합니다.

기능 |

네임스페이스 |

스트림-윈도우/윈도우-스트림 |

dsplib::widget::api_cast::widget_api_cast_graph |

실수-복소수/복소수-실수 |

dsplib:widget::real2complex::widget_real2complex_graph |

Vitis 모델 컴포저에서는 DSP 라이브러리 함수가 지원되므로 사용자는 이러한 함수를 Matlab/Simulink 환경에 쉽게 연결하여 AI 엔진 DSP 라이브러리 평가 및 전반적인 AI 엔진 ADF 그래프 개발을 용이하게 할 수 있습니다.

Vitis HPC 라이브러리 릴리스에서는 FPGA의 HPC 애플리케이션을 위한 HLS 프리미티브, 사전 구축 커널 및 소프트웨어 API가 도입되었습니다. 해당하는 응용 분야는 다음과 같습니다.

2D 음향 RTM(역시간 마이그레이션) FDTD(유한 차분 시간 영역) 알고리즘, 순방향 커널과 역방향 커널 포함

3D 음향 RTM(역시간 마이그레이션) FDTD(유한 차분 시간 영역) 알고리즘, 순방향 커널 포함

MLP(Multilayer Perceptron) 구성 요소: 활성화 함수와 완전 연결 네트워크 커널

밀집 행렬 및 희소 행렬 모두에 대한 PCG(켤레기울기법) 솔버

- Versal AI Engine의 엄선된 비전 함수 최초 릴리스:

사용 가능한 함수

Filter2D

absdiff

accumulate

accumulate_weighted

addweighted

blobFromImage

colorconversion

convertscaleabs

erode

gaincontrol

gaussian

laplacian

pixelwise_mul

threshold

zero

xfcvDataMovers: 고해상도 이미지를 쉽게 타일링하고 AI 엔진 코어의 로컬 메모리로 전송할 수 있도록 하는 유틸리티 데이터 무버 두 가지 방식

- PL 커널 사용: 추가적인 PL 리소스 소비로 더 우수한 처리율

- GMIO 사용: PL 커널 버전보다 처리율이 낮지만, Versal NoC(네트워크 온 칩)를 사용하고 PL 리소스는 사용하지 않음

- 새로운 PL(프로그래밍 가능 로직) 함수 및 기능

- ISP 파이프라인 및 기능:

- 2020.2 비 HDR 파이프라인 업데이트

- 런타임에 일부 ISP 파라미터 변경 지원: 빨간색 및 파란색 채널에 대한 이득 파라미터, AWB 활성화/비활성화 옵션, R,G,B에 대한 감마 테이블, AWB 정규화를 위한 최솟값 및 최댓값을 계산하기 위한 %픽셀

- 파이프라인의 일부로 편입된 Gamma Correction과 색 공간 변환(RGB2YUYV)

- 새로운 2021.1 HDR 파이프라인: 2020.2 파이프라인 + HDR 지원

- 짧은 노출 프레임과 긴 노출 프레임 사이에 디지털 오버랩이 있는 센서를 지원하는 2개 노출에 대한 HDR 병합

- 4개 베이어 패턴 지원: RGGB, BGGR, GRBG, GBRB

- HDR 병합 + ISP 파이프라인(런타임 구성 사용)으로 RGB 출력 반환

- 추출 기능: HDR 추출 기능은 단일 디지털 중첩 스트림을 입력으로 취하고 2개의 출력 노출 프레임(SEF, LEF)을 반환하는 전처리 기능

- 짧은 노출 프레임과 긴 노출 프레임 사이에 디지털 오버랩이 있는 센서를 지원하는 2개 노출에 대한 HDR 병합

- 3DLUT: 색조, 채도 및 휘도와 같은 복잡한 색상 연산자를 제어하기 위한 입력-출력 매핑 제공

- CLAHE: Contrast Limited Adaptive Histogram Equalization은 거의 일정한 영역에서 대비가 과도하게 증폭되지 않도록 적응형 히스토그램 균등화를 수행하는 동안 대비를 제한하는 방법. 노이즈 증폭 문제도 완화

- 2020.2 비 HDR 파이프라인 업데이트

- Flip: 수평 및 수직선을 따라 이미지를 뒤집음

- 맞춤형 CCA: 결과물의 결함 검출을 위한 연결 성분 분석 알고리즘의 맞춤형 버전. 결과물의 결함 부분을 계산하는 것 외에도 결함 픽셀과 전체 결과물 픽셀을 계산

- Canny 업데이트: Canny 함수는 이제 모든 이미지 해상도를 지원

라이브러리 관련 변경 사항

- 모든 테스트가 OpenCV 3.4.2에서 OpenCV 4.4로 업그레이드

- Versal Edge 시리즈(VCK190)에 대한 지원 추가

- 선택한 파이프라인/기능에 대한 벤치마킹 자료가 포함된 새로운 벤치마킹 섹션 게시

2021.1 릴리스는 Two-Gram 텍스트 분석을 제공

TGP(Two Gram Predicate)는 2개 문자로 구성된 항을 가진 역색인을 검색하는 것입니다. 역색인을 설정한 데이터 세트의 경우 역색인의 각 레코드에서 일치하는 ID를 찾을 수 있습니다.

- 커뮤니티 탐지: Louvain Modularity

- 2홉 검색

해당 없음

- L2 커널을 이용한 배정밀도 SpMV(희소 행렬 밀집 벡터 곱셈) 구현 추가

2021.1 릴리스에서는 GQE에 다음 기능에 대한 얼리액세스 지원 제공

64비트 조인 지원: 이제 gqeJoin 커널 및 동반 gqePart 커널이 64비트 키와 페이로드로 확장되어 더 큰 규모의 데이터를 지원할 수 있습니다.

초기 Bloom-filter 지원: gqeJoin 커널은 이제 Bloom-filter 프로빙을 실행하는 모드로 제공됩니다. 이를 통해 초기 단계에서 데이터 크기를 최소화하는 것이 중요한 특정 다중 노드 흐름의 효율성이 향상됩니다.

두 기능 모두 현재 L3 순수 소프트웨어 API로 제공됩니다. 해당 L3 테스트 케이스를 확인하세요.

- GZIP 멀티코어 압축:

- 순수 스트리밍 전용 솔루션(프리 런닝 커널)인 새로운 GZIP 멀티코어 압축 스트리밍 가속기는 4KB, 8KB, 16KB, 32KB 등 다양한 블록 크기를 지원하는 여러 가지 버전으로 제공

- Facebook ZSTD 압축 코어:

- 블록 크기가 32KB인 새로운 Facebook ZSTD 싱글코어 압축 가속기. 더 높은 처리율을 위한 멀티코어 ZSTD 압축 준비 중

- GZIP 저지연율 압축 해제:

- GZIP 압축 해제의 새로운 버전은 각 블록의 지연율을 개선하고 리소스도 줄였으며(LUT 35% 감소, BRAM 83% 감소) FMax도 개선됨

- U50을 사용한 ZLIB 전체 애플리케이션 가속:

- 6개의 압축 코어를 탑재하여 PCIe 전체 대역폭을 포화시키는 U50 플랫폼용 L3 GZIP 솔루션. CPU libz.so 라이브러리를 가속화하는 효율적인 GZIP SW 솔루션과 함께 제공되어 재컴파일하지 않고도 최종 고객 소프트웨어에 원활한 Inflate 및 Deflate API 레벨 통합 제공

- Versal 플랫폼 지원

- AIE 지원 추가 - 위 내용 참조

- 2021.1 릴리스에서 제공하는 지원: * RIPEMD160 * BLS에 대한 초기 지원(완료되지 않음)

- 2021.1 릴리스에서는 Data-Mover가 이 라이브러리에 추가되었습니다. 다른 C++ 기반 API와는 달리 이 추가 기능은 HLS 기반 커널 설계에 대한 숙련도가 덜하고 스트림 기반 설계 테스트만을 원하는 사람들을 대상으로 합니다. Data-Mover는 사실상 커널 소스 코드 생성기로, AIE 디바이스에서와 같이 설계를 구동하거나 검증하기 위한 일반적인 헬퍼 커널 목록을 생성합니다.

- QoR 메트릭 생성(Vitis QoR 생성 API)

- 애플리케이션 커널에서 소요된 주기

- 중단 주기(VCD 파일에서 계산)

- 래퍼에서 오버헤드 사이클 측정(커널 자체가 아닌 다른 함수에서 소요되는 시간)

- 처리율

- 3단계 최적화 XLOPT=0, 1(기본값), 2

- xlopt=2에 대한 새로운 기능:

- 루프 융합, 단일 반복 외부 루프를 평활화하고 루프 필링 휴리스틱 개선

- "__restrict" 사용을 분석하고 지침 제공

- 증분 재컴파일: 그래프가 변경되지 않으면 수정된 커널만 재컴파일

- 패킷 교환 데이터 → 최대 32분할(기존에는 4개로 제한)

- 새로운 DMA FIFO 위치 제약 조건(릴리스 간 매퍼/라우터 변경은 성능에 영향을 미치지 않음)

- 새 컴파일의 제약 조건으로 매핑 솔루션 사용: 성능에 영향을 미치는 향후 매핑 변형 방지

- AIEsim 수준으로 x86 시뮬레이션 기능 지원

- ADF 그래프 내 PL 커널 폐기 시작(2021.2에서 완전 폐기)

- GUI의 새로운 "Flow Navigator"를 통해 흐름 단계 및 보고서에 빠르게 액세스. 컨텍스트별 "합성, 분석, 디버그" 보기를 일반 기본 컨텍스트로 병합

- BIND_OP 및 BIND_STORAGE 지시문에 대한 새로운 합성 보고서 섹션

- 새로운 합성 후 텍스트 보고서는 GUI 합성 보고서에 제공된 정보를 반영

- IP 내보내기 및 Vivado 구현 실행 위젯은 설정 및 제약 조건 파일을 Vivado로 전달하는 옵션으로 재설계됨

- II, 지연율 또는 DSP/BRAM 사용률 핫스팟을 감지하기 위한 선택적 히트맵으로 강조 표시할 수 있는 함수와 루프를 시각화하는 새로운 함수 호출 그래프 뷰어

- DSP 블록 네이티브 부동 소수점 연산에 대한 Versal 타이밍 보정 및 새로운 컨트롤(config_op의 -precision 옵션)

- Vitis HLS 마이그레이션 가이드(이전 UG1391)를 이제 UG1399의 한 장으로 수록

- 사용자 가이드의 새로운 방법론 섹션(UG1399 및 웹)

- 대체 플러시 가능 파이프라인 옵션 개선(FRP(Free Running Pipeline))

- Vitis에서 상단 포트 포인터를 이제 전역 메모리가 아닌 axi-lite 어댑터에 간단히 매핑 가능

- aggregate 지시문이 이제 최대 패킹을 위한 "-compact bit" 옵션 제공

- 도움말 메뉴에 "Leave Feedback(피드백 남기기)" 항목을 선택적 설문조사와 함께 다시 추가

- 일부 Linux 시스템에서 "Man Pages" 탭에 정보가 표시되지 않는 버그 수정

- Vitis에서 m_axi 인터페이스 재구성은 hls::vector 유형을 통해 수행되어야 함

- "auto, "uram", "bram" 또는 "lutram"일 수 있는 s_axilite 및 m_axi 데이터 스토리지에 대한 새로운 맞춤화 옵션을 통해 설계에서 RAM 사용률 조정 가능

- Vitis에서는 커널을 위한 새로운 연속("무한") 실행 모드 도입

- axi_lite 보조 클럭 옵션 복구

- Vivado IP 패키저에서 RTL 커널 패키징에 대한 지원 개선

- 적절한 방법론과 문서가 포함된 공개적이고 제품화된 기능

기본 흐름은 XRT 관리 커널

암호화된 AIE 소스 파일을 입력으로 지원

AIE 컴파일러는 암호화된 AIE 소스 파일을 허용할 수 있으며 v++는 나머지 흐름을 지원

- Versal 디바이스를 위한 부팅 이미지 생성 마법사 지원 추가

- AI 엔진 프로그래밍 및 디버깅을 위한 다양한 개선 사항

- 마이크로 코드 라벨 켜기 및 끄기 가능

- 소스 코드와 마이크로 코드 간의 정적 크로스 프로빙

- 마이크로 코드의 전체 보기

- 파이프라인 보기에서 데이터가 업데이트될 때마다 마지막 PC를 가시 영역에 가져오기

- 파이프라인 보기에서 명령어 데이터 정렬

- 분해 뷰에 "단일 명령어 모드" 작업 추가

- 플랫폼 프로젝트에 대한 기본 BIF 파일 생성 가능

- SD 및 eMMC용 프로그램 플래시에 RAW 모드 지원 추가

- AI 엔진 개발 흐름에 상황에 맞는 도움말 메시지 추가

- GCC 툴체인 버전을 10.2로 업그레이드

- 사용자는 Python/C++와 같은 외부 프로세스를 통해 AXI-MM 마스터/슬레이브를 에뮬레이션할 수 있습니다. 이를 통해 사용자는 AXI 마스터 또는 VIP를 개발하는 데 리소스를 투자하지 않고도 AXI 마스터/슬레이브의 빠른 설계 시간으로 설계를 에뮬레이션할 수 있습니다. AXI-MM 프로세스 간 통신은 두 개의 FPGA 간 칩-투-칩 연결을 에뮬레이션하는 데에도 도움이 될 수 있습니다.

- VCS에 대한 Versal 모델의 컴파일 활성화

- 플랫폼 개발자는 독립형 애플리케이션으로 플랫폼에서 하드웨어 에뮬레이션을 실행하여 초기 단계에서 플랫폼을 테스트할 수 있습니다.

- 사용자 범위 프로파일링 정보 및 사용자 이벤트 정보를 프로파일 요약 보고서에 집계

Vitis Analyzer는 중요한 타이밍 경로를 표시

Vitis Analyzer는 Vivado 프로젝트 또는 넷리스트를 열지 않고도 Vivado GUI 타이밍 보고서의 단순화된 버전을 표시합니다. 이를 통해 사용자는 실패한 타이밍 경로를 빠르게 탐색할 수 있습니다.

Vitis Analyzer의 다양한 전략 지원

실행된 여러 전략의 결과를 Vitis Analyzer에서 시각화할 수 있습니다.

- 프로파일링 및 디버그를 위한 새로운 xrt.ini 스위치

대용량 애플리케이션의 메모리 및 로딩 시간 절감

새로운 프로파일 도구는 대용량 csv 파일을 처리하는 데 필요한 리소스를 줄여서 로딩 시간과 충돌 문제 발생 빈도를 줄입니다.

PL 연속 추적 오프로딩 개선

DDR 또는 HBM을 메모리 리소스로 사용하여 추적 데이터 저장

대규모 데이터 오프로딩을 위한 순환 버퍼 지원

추적 버퍼 크기 및 오프로딩 간격은 xrt.ini에서 설정 가능

AIE 설계의 추적 보고서 시각화 개선

모든 AIE 입력을 표시(윈도우, 스트림, 캐스케이드 스트림 등)

모든 IO 데이터 형식 지원

- AIE 그래프 제어 및 실행을 위한 C++ API와 안정적인 네이티브 XRT API, 소프트웨어 에뮬레이션 및 추적 지원을 제공합니다.

- XRT는 $XILINX_XRT/include/CL/cl2xrt.hpp에서 사용자가 OpenCL API에서 XRT 네이티브 API로 이동하는 데 도움이 되는 새로운 헬퍼 API를 제공합니다.

- XRT 새로운 API xrt::device.get_info()는 장치 속성을 추출할 수 있습니다.

- 대폭 개선된 차세대 xbutil 및 xbmgmt 유틸리티가 이제 기본으로 제공됩니다.

- xbutil은 전원 상태를 보고할 수 있습니다

- xbmgmt는 런타임 clk 스케일을 지원하고 사용자 전원 임계값을 설정하여 보드와 서버를 보호합니다.

- sysfs, xbmgmt 및 xbutil은 Alveo 보드의 MAC 주소를 보고할 수 있습니다.

- xocl의 KDS 스케줄러가 리팩터링되어 여러 디바이스에서 여러 컴퓨팅 유닛을 동시에 사용하는 수백 개 프로세스의 처리율이 대폭 향상되었습니다. 레거시 셸의 경우 처리율이 약간 저하될 수 있습니다. 적절한 솔루션은 AR을 참조하세요.

- debugfs /sys/kernel/debug/xclmgmt/ 및 /sys/kernel/debug/xocl/을 통한 XRT 드라이버 디버그 추적 지원이 제공됩니다.

www.xilinx.com/alveo에서 Alveo 가속기 카드용 최신 Vitis Target 플랫폼에 액세스할 수 있습니다. 애플리케이션을 배포할 가속기 카드의 시작하기 섹션을 참조하세요.

자세한 내용과 최신 Vitis Target 플랫폼 릴리스에 대한 최신 정보는 제공 시 UG1120 - Alveo 데이터센터 가속기 카드 플랫폼 사용자 가이드에서 참조할 수 있습니다.

새로운 플랫폼

- Alveo U200 Gen3x16 XDMA 1RP

- 이름: xilinx_u200_gen3x16_xdma_1_202110_1

- 특징: 슬레이브 브리지, P2P, GT 커널, DDR Self-Refresh

- Alveo U50 Gen3x16 noDMA 1RP

- 이름: xilinx_u50_gen3x16_nodma_1_202110_1

- 특징: 슬레이브 브리지, P2P, GT 커널, 클럭 스로틀링

Vitis Embedded 플랫폼

- CK190 기본 플랫폼은 DDR과 LPDDR에서 ECC를 지원하며 제약 조건이 간결해졌습니다.

- MPSoC 기본 플랫폼은 CMA 크기를 1536M으로 늘렸습니다. 모든 Vitis-AI 모델은 이 CMA 크기로 실행할 수 있습니다.

- Embedded 플랫폼 생성 과정이 간소화되었습니다. 디바이스 트리 생성기는 ZOCL 노드를 자동으로 생성할 수 있고, XSCT는 BIF 파일을 생성할 수 있습니다. 기본 플랫폼 소스 파일이 줄어듭니다.

- Kubernetes(K8s) 클러스터 지원: 이제 Xilinx FPGA Resource Manager(XRM)를 Kubernetes와 함께 사용하여 서버에 연결된 여러 Alveo 가속기 카드 풀에서 CU(컴퓨팅 유닛)를 실행 및 관리하고 Alveo 카드를 사용하여 여러 서버로 애플리케이션을 확장할 수 있습니다.

- 포괄적인 제약 조건 편집기를 통해 사용자가 Vitis 모델 컴포저에서 AI 엔진 커널에 대한 제약 조건 지정 가능. 생성된 ADF 그래프에는 해당 제약 조건이 포함됨

- 라이브러리 브라우저에 AI 엔진 FFT 및 IFFT 블록 추가

- 사용자는 라이브러리 브라우저에서 다양한 AI 엔진 FIR 블록에 액세스 가능

- FIR 필터의 입력 포트를 사용하여 필터 계수 지정 가능

- 두 개의 새로운 유틸리티 블록인 "RTP 소스" 및 "가변 크기" 추가

- 개선된 AIE 커널 가져오기 블록에서 이제 템플릿형 AI 엔진 기능 가져오기도 지원

- 허브 블록에서 AI 엔진 설계용 AMD 플랫폼 지정 가능

- 허브 블록을 통해 사용자는 AIE 시뮬레이션을 실행한 후 언제든지 Vitis Analyzer 재실행 가능

- 이제 사용자가 Simulink Data Inspector를 사용하여 주기 근사 출력을 플로팅하고 각 출력에 대한 예상 처리율 확인 가능

- 그래프 헤더 파일만 사용하여 그래프를 블록으로 가져오는 사용성 향상

- 취소 버튼으로 진행률 표시줄 개선

- MATLAB 작업 디렉토리와 모델 디렉토리가 동일하지 않을 때 AI 엔진 커널 또는 설계 시뮬레이션을 가져오는 동안의 사용성 향상

- 새로운 TX 체인 200MHz 예제

- HLS, HDL 및 AI 엔진 블록을 사용한 설계를 보여 주는 새로운 2D FFT 예제

HDL

- SSR FIR(10배 이상 개선) 및 SSR FFT에 대한 시뮬레이션 속도 향상

- RAM 및 FIFO와 같은 메모리 블록에 대한 시뮬레이션 속도 향상

- 블랙박스 가져오기 흐름에서 VHDL 2008로 Questa 시뮬레이터 업데이트

일반

- 이제 Vitis 모델 컴포저에 DSP용 AMD System Generator의 모든 기능이 포함되어 있습니다. DSP용 AMD System Generator를 사용해 온 사용자는 Vitis 모델 컴포저를 사용하여 개발을 계속할 수 있습니다.

- MATLAB 지원 - R2020a, R2020b 및 R2021a

Vitis 소프트웨어 플랫폼 2020.2 릴리스 하이라이트:

- Vitis 2020.2는 Versal ACAP 플랫폼의 애플리케이션 가속 및 임베디드 소프트웨어 개발을 지원합니다.

- Vitis 핵심 개발 키트에는 이제 Versal AI Engine용 C/C++ 애플리케이션을 컴파일하기 위한 AI 엔진 컴파일러가 포함되어 있습니다. Versal AI Core 시리즈의 일부인 AI Engine은 컴퓨팅 집약적 애플리케이션을 위한 벡터 프로세서입니다.

- Vitis HLS는 가속 커널 컴파일(Vitis)과 C/C++에서 RTL IP 생성 흐름(Vivado)에 기본으로 제공됩니다.

- 13개의 성능 최적화 라이브러리에 걸쳐 600개 이상의 FPGA 가속 함수가 포함되어 있습니다. 2020.2에서는 고성능 컴퓨팅 애플리케이션을 가속화하기 위한 새로운 Vitis HPC 라이브러리와 데이터 분석, 그래프, BLAS, 희소 행렬, 보안 및 데이터베이스 라이브러리에 대한 여러 가지 개선 및 추가 사항이 도입되었습니다.

- 최종 FPGA 바이너리 생성을 위한 다중 구현 전략 평가 지원 및 Vitis 애플리케이션 내에서 보다 쉬운 RTL 커널 통합을 위한 개선 사항이 제공됩니다.

- 이 릴리스의 기타 개선 사항으로는 AI 엔진 애플리케이션 프로파일링 지원, Vitis 프로젝트를 위한 Git 버전 관리, Vitis Analyzer 내의 Vitis AI 프로파일러 데이터 통합, 에뮬레이션 모드 개선 등이 있습니다.

- MATLAB® 및 Simulink®용 애드온: DSP용 AMD 모델 컴포저 및 System Generator 통합. AI 엔진은 MATLAB 및 Simulink용 애드온의 새로운 도메인입니다.

각주

- 2023년 8월 10일, 1,000개의 Vitis L2/L3 코드 라이브러리 설계에 대해 Vitis HLS 릴리스 2023.2와 Vitis HLS 2023.1을 비교한 테스트를 기준으로 합니다. 테스트 중 시스템 구성: 인텔 제온 E5-2690 v4 @ 2.6GHz CPU, 256GB RAM, RedHat Enterprise Linux 8.6. 실제 성능은 다를 수 있습니다. 시스템 제조업체별 구성에 따라 다른 결과가 나올 수 있습니다. -VGL-04

- 벤치마크 테스트는 2023년 2월 12일 현재 1208개의 Vitis L1 라이브러리 C 코드 설계에 대해 수행되었습니다. 모든 설계는 CentOS Linux, SMT 활성화, 터보 부스트 비활성화 상태의 2P 인텔 제온 E5-2690 CPU를 탑재한 시스템을 사용하여 실행되었습니다. 하드웨어 구성은 소프트웨어 테스트 결과에 영향을 미치지 않을 것으로 예상됩니다. 결과는 소프트웨어 및 펌웨어 설정과 구성에 따라 달라질 수 있습니다.- VGL-03

- 2023년 8월 10일, 1,000개의 Vitis L2/L3 코드 라이브러리 설계에 대해 Vitis HLS 릴리스 2023.2와 Vitis HLS 2023.1을 비교한 테스트를 기준으로 합니다. 테스트 중 시스템 구성: 인텔 제온 E5-2690 v4 @ 2.6GHz CPU, 256GB RAM, RedHat Enterprise Linux 8.6. 실제 성능은 다를 수 있습니다. 시스템 제조업체별 구성에 따라 다른 결과가 나올 수 있습니다. -VGL-04

- 벤치마크 테스트는 2023년 2월 12일 현재 1208개의 Vitis L1 라이브러리 C 코드 설계에 대해 수행되었습니다. 모든 설계는 CentOS Linux, SMT 활성화, 터보 부스트 비활성화 상태의 2P 인텔 제온 E5-2690 CPU를 탑재한 시스템을 사용하여 실행되었습니다. 하드웨어 구성은 소프트웨어 테스트 결과에 영향을 미치지 않을 것으로 예상됩니다. 결과는 소프트웨어 및 펌웨어 설정과 구성에 따라 달라질 수 있습니다.- VGL-03