- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

- 2020.2

- 2020.1

Lo más destacado de la versión 2025.2 de AMD Vitis™ Software Platform

Flujo de diseño mejorado con los motores Versal™ AI Engine

- Mejoras en la API de AI Engine para la Serie Versal AI Edge y la Serie Versal AI Edge de 2.ª generación (AIE-ML y AIE-ML v2)

- Tipos de datos nuevos y mejorados

- Nuevo: Punto flotante por bloque MX6

- Nuevo: Punto flotante por bloque MX4

- Nuevos: cbfloat16 (emulado)

- Mejorados: cfloat y cbfloat16 (disponibles en funciones de FFT y multiplicación de matrices)

- Mejorado: cint16 y cint32 (ahora se pueden usar tipos cint16 de twiddle en FFT)

- Tipos de datos nuevos y mejorados

- Actualizaciones del modelo de programación

- Crear búfer compartido de solo lectura

- Acceso de lectura repetido al mosaico MEM (AIE-ML y AIE-ML v2)

- Compatibilidad con DMA-FIFO en AIE-ML y AIE-ML v2

- Los búferes ping-pong pueden abarcar dos mosaicos MEM adyacentes

(AIE-ML y AIE-ML v2) - Parámetros compartidos para la memoria local del mosaico

- Mejoras en la conmutación de paquetes para AIE-ML y AIE-ML v2

- Funciones nuevas y mejoradas de la biblioteca DSP para los motores Versal AI Engine

- Nueva suma acumulada

- Nueva distancia euclidiana

- Nueva aproximación de funciones (invocada mediante actualización de RTP o LUT)

- FIR TDM mejorado con conmutación de paquetes (ahorra PLIO)

- FFT 1D mejorado usando AI Engine + PL (reduce los recursos de PL necesarios)

- FIR mejorado (optimizaciones de rendimiento)

- Mapeador y enrutador mejorados de AI Engine: el compilador explorará diferentes huellas/diseños para una implementación más eficiente

Verificación más fácil de los diseños de Versal AI Engine

- Actualizaciones en el flujo de trabajo de simulación funcional de Vitis con compatibilidad para C++ (acceso anticipado)

- Hardware en el bucle mediante el banco de prueba en MATLAB® y Python (acceso anticipado)

Mejoras en Vitis Model Composer para diseños de DSP de AIE

- Actualizaciones de facilidad de uso para el flujo de diseño de velocidad de supermuestreo (SSR) con motores AI Engine (acceso anticipado)

- Bloques adicionales disponibles para AI Engine y HDL:

- AIE, AIE-ML, AIE-ML v2

- Nuevo: Aproximación de la función

- Nuevo: Correlación/Convolución

- Nuevo: Suma acumulada

- Bloques de biblioteca HDL

- Mejorado: FFT (SSR nativa de punto flotante añadido = 32, 64)

- Mejorado: FIR (admite interpolación de tasa fraccionaria con SSR)

- AIE, AIE-ML, AIE-ML v2

Actualizaciones de IDE de Vitis para desarrollo integrado

- API de Python™ para actualizar la configuración de compilación

- Ejecutar la API de Vitis™ en un entorno de Python

- Rastreo del PS visible de forma predeterminada para los núcleos compatibles

- Mejora de depuración: los valores actualizados ahora se resaltan en las vistas Ver y Registro

- Cancelar o finalizar tareas del backend

- Rutas unificadas de archivos BSP de la plataforma (Linux y Windows)

- Integración de IA en Theia (acceso anticipado): proporciona la infraestructura para que los desarrolladores usen su LLM y asistentes de código preferidos

- Creación de plataformas DFX con la API de Python

- Respaldar o compartir un espacio de trabajo

- Registro mejorado para archivos de configuración

- Nuevo componente “Proyecto de integración”

Novedades de Vitis por categoría

Expande las siguientes secciones para obtener más información sobre las nuevas funciones y mejoras de la versión 2025.2 de la plataforma de software AMD Vitis. Para obtener información sobre las plataformas compatibles, los cambios de comportamiento y los problemas conocidos, consulta las notas de la versión 2025.2 de la plataforma de software Vitis para ver el Flujo de aceleración de aplicaciones y el Flujo de desarrollo de software integrado.

Funciones mejoradas de la biblioteca DSP:

- Nueva suma acumulada

- Nueva distancia euclidiana

- Nueva aproximación de funciones (invocada mediante actualización de RTP o LUT)

- FIR TDM mejorado con conmutación de paquetes (ahorra PLIO)

- FFT 1D mejorado usando AIE + PL (reduce los recursos de PL necesarios)

- FIR mejorado (optimizaciones de rendimiento)

Se aplica a:

- Versal™ AI Core con AIE

- Versal AI Edge con AIE-ML

- Serie Versal AI Edge de 2.ª generación con AIE-ML v2

- Simulación funcional de subsistemas Vitis en C++ (acceso anticipado)

- Soporte mejorado de la medición de latencia y rendimiento en Vitis Analyzer para diseños de AI Engine

- Control de tiempo de ejecución de particiones AIE independientes

- Actualizaciones de facilidad de uso para el flujo de diseño de velocidad de supermuestreo (SSR) con motores AI Engine (acceso anticipado)

- Bloques adicionales disponibles para AI Engine y HDL:

- AIE, AIE-ML, AIE-ML v2

- Nuevo: Aproximación de la función

- Nuevo: Correlación/Convolución

- Nuevo: Suma acumulada

- Bloques de biblioteca HDL

- Mejorado: FFT (SSR nativa de punto flotante añadido = 32, 64)

- Mejorado: FIR (admite interpolación de tasa fraccionaria con SSR)

- Mejoras en el pragma de rendimiento

- El pragma de rendimiento ahora se optimizará en función del recuento de iteraciones calculado por CSIM.

- Las optimizaciones del pragma de rendimiento pueden convertirse en directivas dentro de un archivo de configuración.

- Control condicional de pragmas, incluido el pragma de rendimiento

- Nueva compatibilidad de IP

- SSR de tasa fraccionaria para FIR y FFT - Para FFT, la SSR en SPFP32 ahora admite hasta SSR = 64.

- Compatibilidad con ECC para búferes de flujo de datos implementados con Block RAM o UltraRAM

- Funciones fáciles de usar

- Compatibilidad con el reinicio automático en CSIM y CoSim

- Caché multipuerto para M-AXI

- Nuevas API para flujos AXI con señales laterales

Lo más destacado de la versión 2025.1 de la plataforma de software AMD Vitis™

Flujo de diseño mejorado con Versal AI Engines

- Funciones de biblioteca DSP nuevas y mejoradas, API de AI Engine y compatibilidad con nuevos tipos de datos

Serie Versal AI Core con AIE:

- GEMV y FFT mejorados para AI Engine con arquitectura lógica programable (PL) y AIE paralelo en 2D (ideal para canalizador polifásico)

- Convolución, correlación y clasificación SIMD bitónica vectorizada

Serie Versal AI Edge con AIE-ML:

- FFT para AIE-ML con arquitectura PL y AIE-ML paralelo en 2D (ideal para canalizador polifásico)

- Convolución, correlación y clasificación SIMD bitónica vectorizada

Serie Versal AI Edge de 2.ª generación con AIE-ML v2:

- PL v1 y 2D FFT AIE-ML v2 (ideal para canalizadores polifásicos)

- FIR con TDM (ideal para canalizadores polifásicos)

- GEMM/GEMV

- FIR de tasa única

- FIR de media banda

- FIR con remuestreo fraccional

- FIR de cambio de tasa

- FFT/iFFT

- DFT

- Mezclador de DDS

- Aproximación de la función

Actualizaciones de la programación de AI Engine:

- Especificaciones del parámetro de creación de mosaicos para la memoria local

- Tiempos de compilación reducidos cuando se cambia el banco de pruebas

- Canalización más rápida para el diseño con búferes ping-pong en DDR en AIE-ML

- Otras mejoras de acceso a la memoria en AIE-ML

Verificación más fácil de los diseños de Versal AI Engine

- Simulación funcional de subsistemas Vitis en MATLAB® y Python™

- Soporte mejorado de la medición de latencia y rendimiento en Vitis Analyzer para diseños de AI Engine

- Control de tiempo de ejecución de particiones AIE independientes

Mejoras en Vitis Model Composer para diseños de DSP de AIE

- Soporte para múltiples subsistemas AI Engine de nivel superior

- Bloques adicionales disponibles para AIE y HDL, lo que incluye FFT mejorado con modos SSR adicionales y multiplicadores complejos que pueden emplear menos recursos DSP58

Actualizaciones de IDE de Vitis para desarrollo integrado

- IDE unificado de Vitis (nueva interfaz gráfica de usuario), que será predeterminado. El IDE clásico de Vitis está obsoleto

- Compatibilidad con cadena de herramientas de terceros como GCC y ARMClang

- Ahora se pueden instalar herramientas de productividad de terceros a través de una utilidad de marketplace dentro del IDE de Vitis

Novedades de Vitis por categoría

Expande las siguientes secciones para obtener más información sobre las nuevas funciones y mejoras de la versión 2025.1 de la plataforma de software AMD Vitis. Para obtener información sobre las plataformas compatibles, los cambios de comportamiento y los problemas conocidos, consulta las notas de la versión 2025.1 de la plataforma de software Vitis para ver el Flujo de aceleración de aplicaciones y el Flujo de desarrollo de software integrado.

Serie Versal AI Core con AIE:

- GEMV y FFT mejorados para AI Engine con arquitectura lógica programable (PL) y AIE paralelo en 2D (ideal para canalizador polifásico)

- Convolución, correlación y clasificación SIMD bitónica vectorizada

Serie Versal AI Edge con AIE- ML:

- FFT para AIE-ML con arquitectura PL y AIE-ML paralelo en 2D (ideal para canalizador polifásico)

- Convolución, correlación y clasificación SIMD bitónica vectorizada

Serie Versal AI Edge de 2.ª generación con AIE-ML v2

- PL v1 y 2D FFT AIE-ML v2 (ideal para canalizadores polifásicos)

- FIR con TDM (ideal para canalizadores polifásicos)

- GEMM/GEMV

- FIR de tasa única

- FIR de media banda

- FIR con remuestreo fraccional

- FIR de cambio de tasa

- FFT/iFFT

- DFT

- Mezclador de DDS

- Aproximación de la función

- Simulación funcional de subsistemas Vitis en MATLAB® y Python™

- Soporte mejorado de la medición de latencia y rendimiento en Vitis Analyzer para diseños de AI Engine

- Control de tiempo de ejecución de particiones AIE independientes

Soporte para múltiples subsistemas AI Engine de nivel superior

Bloques adicionales disponibles para AI Engine y HDL

Motor de IA

- Clasificación bitónica (Serie Versal AI Core, Serie Versal AI Edge, Serie Versal AI Edge de 2.ª generación)

- DFT/FFT (Serie Versal AI Edge de 2.ª generación)

- FIR: tasa única, media banda, cambio de tasa, remuestreo fraccional (Serie Versal AI Edge de 2.ª generación)

- DDS/mezclador (Serie Versal AI Edge de 2.ª generación)

Biblioteca de HDL

- FFT mejorado: modos SSR adicionales

- SSR 8, 16, 32, 64 (punto flotante nativo)

- SSR 2, 4 (punto fijo)

- Multiplicador complejo mejorado: menos recursos DSP58

- Nuevo soporte para CFLOAT MAC

- Vector IFFT flotante: nuevo bloque

- Genera código C++ simple con Vitis HLS a partir de diseños MATLAB (.m) en R2025a

- Nuevas funciones de Vitis HLS de facilidad de uso

- Modelado de entradas de cable y AXI Lite que cambian durante la ejecución (E/S directa)

- Pragma de rendimiento para el diseño HLS de nivel superior (EA abierta)

- Compatibilidad con el multiplicador complejo de Versal a través de la biblioteca intrínseca dedicada

- Mejoras en la interfaz gráfica de usuario de Vitis HLS

- Compatibilidad inicial de C++17 a través de Clang 16

Lo más destacado de la versión 2024.2 de AMD Vitis™ Software Platform:

Mejoras en los diseños de DSP de AMD Versal AI Engine

- Estimaciones de latencia y rendimiento utilizando Vitis Analyzer

- Marca PLIO no disponibles usando Vitis Analyzer

- Rápida creación de prototipos de diseños de AMD Versal™ AI Engine

- Informes de las memorias heap, stack y del programa

Nuevas y mejoradas funciones de la biblioteca Vitis para motores Versal AI Engine

- Funciones mejoradas de la biblioteca DSP para AIE (disponibles en las Series Versal AI Core y Versal Premium)

- Funciones de filtro FIR con TDM (Time Division Multiplexed, multiplexación por división en el tiempo) derendimiento mejorado

- Versiones de mayor rendimiento de:

- GEMV (General Matrix Vector, vector de matriz general); y

- GEMM (General Matrix Multiply, multiplicación matricial general).

- IFFT 2D, particionado a través de AIE + PL para alto rendimiento

- Nuevas funciones de la biblioteca DSP para AIE-ML(disponibles en Versal AI Edge)

- Funciones de filtro FIR con TDM de rendimiento mejorado

- Compatibilidad con FFT de base 3 y 5

- GEMV

- GEMM

Nuevas funciones de facilidad de uso en el IDE de Vitis (nueva GUI)

- Nuevo terminal de serie: Monitorea los mensajes en serie desde el hardware

- Instala y explora extensiones de terceros

- Función de rastreo del PS (processing system, sistema de procesamiento) para depurar y optimizar el rendimiento de los sistemas integrados

Mejoras en Vitis Model Composer para diseños de DSP de AIE

- Actualizaciones de AI Engine DSP Library

- AIE (disponible en las Series Versal AI Core y Versal Premium)

- FFT de base mixta

- Mejoras de rendimiento de la FFT de Stockham

- FIR con TDM

- AIE-ML (disponible en la Serie Versal AI Edge)

- FIR con TDM

- DDS (síntesis digital directa; utilizada para la generación de forma de onda)

- Mezclador (utilizado para el cambio de frecuencia)

- AIE-MLv2 (disponible en la Serie Versal AI Edge de 2.ª generación)

- FIR

- DFT

- DDS

- Mezclador

- AIE (disponible en las Series Versal AI Core y Versal Premium)

- Tipos de datos adicionales para Vitis Model Composer

- Compatibilidad con cbfloat16

- Compatibilidad con tipos de datos adicionales para señales en cascada

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- Exporta diseños de kernel de AIE/HLS de Vitis Model Composer a Vitis como un subsistema de Vitis (VSS)

- Depura kernels de AIE/HLS integrados en Vitis Model Composer usando Vitis Debugger

- Actualizaciones de HDL Blockset en Vitis Model Composer

- Otras mejoras en Vitis Model Composer

- Tiempo de respuesta mejorado para la generación de código

- La simulación se ejecuta solo una vez para cualquier diseño

- Guarda configuraciones de bloques de Hub como un archivo JSON (útil para el procesamiento por lotes o la rápida creación de prototipos)

- Se agregó compatibilidad con MATLAB R2024a

- Se agregó compatibilidad con Red Hat Enterprise Linux (RHEL) 8.10 y 9.4

- Tiempo de respuesta mejorado para la generación de código

- Comprobaciones de reglas de diseño (DRC) para reemplazar consideracionesde diseño

Novedades de Vitis por categoría

Expande las secciones siguientes para obtener más información sobre las nuevas funciones y mejoras de la plataforma de software AMD Vitis 2024.2. Para obtener información sobre las plataformas compatibles, los cambios de comportamiento y los problemas conocidos, consulta las notas de la versión 2024.2 de la plataforma de software Vitis para ver el Flujo de aceleración de aplicaciones y el Flujo de desarrollo de software integrado.

Funciones mejoradas de la biblioteca DSP para AIE (disponibles en las Series Versal AI Core y Versal Premium)

- Funciones de filtro FIR con TDM derendimiento mejorado

- Versiones de mayor rendimiento de:

- GEMV (vector de matriz general)

- GEMM (multiplicación matricial general)

- IFFT 2D, particionado a través de AIE + PL para alto rendimiento

Nuevas funciones de la biblioteca DSP para AIE-ML(disponibles en Versal AI Edge)

- Funciones de filtro FIR con TDM derendimiento mejorado

- Compatibilidad con FFT de base 3 y 5

- GEMV (vector de matriz general)

- GEMM (multiplicación matricial general)

- Estimación de latencia y rendimiento con Vitis Analyzer

- Marca qué PLIO no están disponibles con Vitis Analyzer

- Actualizaciones de AI Engine DSP Library

- AIE (disponible en las Series Versal AI Core y Versal Premium)

- FFT de base mixta

- Mejoras de rendimiento de la FFT de Stockham

- FIR con TDM

- AIE-ML(disponible en la Serie Versal AI Edge)

- FIR con TDM

- DDS (Direct Digital Synthesis, síntesis digital directa; utilizada para la generación de forma de onda)

- Mezclador (utilizado para el cambio de frecuencia)

- AIE-MLv2 (disponible en la Serie Versal AI Edge de 2.ª generación)

- FIR

- DFT

- DDS

- Mezclador

- AIE (disponible en las Series Versal AI Core y Versal Premium)

- Tipos de datos adicionales para Vitis Model Composer

- Compatibilidad con cbfloat16

- Compatibilidad con tipos de datos adicionales para señales en cascada

- int8/uint8

- int16/uint16/cint16

- int32/uint32/cint32

- float/cfloat

- Exporta diseños de kernel de AIE/HLS de Vitis Model Composer a Vitis como un VSS (subsistema de Vitis)

- Depura kernels de AIE/HLS integrados en Vitis Model Composer usando Vitis Debugger

- Actualizaciones de HDL Blockset en Vitis Model Composer

- Otras mejoras en Vitis Model Composer

- Tiempo de respuesta mejorado para la generación de código

- La simulación se ejecuta solo una vez para cualquier diseño

- Guarda configuraciones de bloques de Hub como un archivo JSON (útil para el procesamiento por lotes o la rápida creación de prototipos)

- Se agregó compatibilidad con MATLAB R2024a

- Se agregó compatibilidad con Red Hat Enterprise Linux (RHEL) 8.10 y 9.4

- Comprobaciones de reglas de diseño (DRC) para reemplazar las consideraciones de diseño

- modelado de entradas escalares/cableadas que cambian durante la ejecución (E/S directa);

- compatibilidad con tipos de puntos flotantes de precisión arbitraria;

- asignación de código HLS a bloques DSP;

- Secuencia determinada por el usuario de ejecución de código

- Depurador HLS que muestra los tipos de datos de una manera fácil de usar (con la tecnología Prettyprint del depurador GNU)

Lo más destacado de la versión 2024.1 de AMD Vitis™ Software Platform:

Mejoras en los diseños de DSP de AMD Versal™ AI Engine

- Funciones mejoradas de la biblioteca DSP para la Serie AMD Versal AI Core

- Funciones de filtro FIR con multiplexación por división en el tiempo (TDM) para SSR>1

- FFT con twiddle de 32 bits

- FFT de base 3 mixta y base 5 mixta

- Producto de matrices de Kronecker

- Solucionador QRD basado en el hogar para mejor estabilidad

- DFT para SSR>1

- Nuevas funciones de la biblioteca DSP para la Serie AMD Versal AI Edge con AIE-ML

- Vector de matriz general (GEMV) compatible con SSR

- Multiplicación matricial general (GEMM) compatible con SSR

- Mejoras en la API del AIE

- Compatibilidad con FFT de base 3 y 5

- Mejoras en el simulador de AIE

- Compatibilidad de simulación de ciclo aproximado para diseños de motor de IA con PL, sin necesidad de un núcleo IP del CIPS (Control, Interface, and Processing System; control, interfaz y procesamiento de sistema)

- Compatibilidad con el analizador de AMD Vitis para la emulación de hardware con simuladores de terceros como VCS, Questa, Xcelium y Riviera

Mejoras clave en Vitis Unified Software Platform

- Nueva compatibilidad para dispositivos: SoC adaptable VP1902 de AMD Versal™ Premium y procesador AMD MicroBlaze™ V

- Desarrollo mejorado de aplicaciones integradas y generación de BSP (Board Support Package, paquete de soporte de placa) para entornos Windows®

- Flujo administrado por el usuario para depurar aplicaciones integradas compiladas externamente

- Nueva GUIde Bootgen

- Permite compilaciones incrementales para el proyecto de plataforma

Mejoras clave en AMD Vitis IDE (nueva GUI)

- Compatibilidad agregada para el procesamiento de depuración jerárquica de subsistemas

- Compatibilidad agregada para la exportación y la importación de proyectos/espacio de trabajo

- Compatibilidad agregada para intérprete de Python y API

- Nueva página de vista previa de funciones

- Nueva notificación de cambio de archivo para proyectos de plataforma de AIE integrados

Novedades de Vitis por categoría

Expande las secciones siguientes para obtener más información sobre las nuevas funciones y mejoras de la plataforma de software AMD Vitis 2024.1. Para obtener información sobre las plataformas compatibles, los cambios de comportamiento y los problemas conocidos, consulta las notas de la versión 2024.1 de la plataforma de software Vitis para ver el Flujo de aceleración de aplicaciones y el Flujo de desarrollo de software integrado.

Funciones mejoradas de la biblioteca DSP para la Serie AMD Versal AI Core

- Funciones de filtro FIR con multiplexación por división en el tiempo (TDM) para SSR>1

- FFT con twiddle de 32 bits

- FFT de base 3 mixta y base 5 mixta

- Producto de matrices de Kronecker

- Solucionador QRD basado en el hogar para mejor estabilidad

- DFT para SSR>1

Nuevas funciones de la biblioteca DSP para la Serie AMD Versal AI Edge con AIE-ML

- Vector de matriz general (GEMV) compatible con SSR

- Multiplicación matricial general (GEMM) compatible con SSR

Mejoras en la API del AIE

Compatibilidad con FFT de base 3 y 5

Mejoras en AI Engine Simulator

- Compatibilidad de simulación de ciclo aproximado para diseños de motores de IA con PL, sin necesidad de CIPS

- Compatibilidad con el analizador de Vitis para la emulación de hardware con simuladores de terceros como VCS, Questa, Xcelium y Riviera

- Exporte tablas desde el analizador de Vitis al formato CSV

- Nuevas funciones de DSP compatibles para AIE y AIE-ML dentro de AMD Vitis Model Composer

- Funciones de filtro FIR con TDM

- Para crear canalizadores polifásicos a 1 GSPS y rendimientos superiores

- DFT/IDFT, compatibles con SSR

- Transformaciones optimizadas para rendimiento/latencia en pequeños tamaños

- FFT/IFFT, amplia compatibilidad para twiddle de CINT32-bit

- FFT/IFFT de base mixta, compatible con AIE-ML

- Mejoras de facilidad de uso en el bloque de Model Composer Hub

- Mejoras en el flujo de validación de hardware

- Compatibilidad agregada de estas versiones de SO y MATLAB® con la versión 2024.1:

- RHEL 9

- MATLAB R2023a y R2023b

Nuevos ejemplos de diseñodisponibles en GitHub.

Un nuevo pragma de símbolos simplifica el código HLS en C++ para filtros de imágenes y videos.

Los nuevos wizards de función de biblioteca aprovechan el repositorio GitHub de las bibliotecas de AMD Vitis.

- Crea IP “Solver” y “Vision” (compatibles con OpenCV) para la herramienta de diseño AMD Vivado.

- Ejecuta los ejemplos de biblioteca disponibles.

El pragma para la interfaz de memoria (ap_memory) ahora puede agrupar puertos para AMD Vivado IP Integrator.

La nueva comparación de componentes HLS muestra métricas lado a lado para dos o más componentes.

Compatibilidad con el código RTL de usuario-proveedor para reemplazar una función en C++ (flujo de caja negra).

Code Analyzer ahora puede desagregar miembros de estructuras en C++ para ajustar con precisión el análisis de rendimiento.

Nuevo control de usuario para la codificación de FSM global de HLS y la selección de un estado seguro.

Acceso a desinfectantes de Clang durante la simulación de C para realizar comprobaciones de dirección e inicialización.

Lo más destacado de la versión 2023.2 de Vitis™ Software Platform:

Mejoras en los diseños de DSP de Versal™ AI Engine

- Nuevas funciones de biblioteca DSP

- Nueva compatibilidad de API para funciones de DSP

- Nuevas funciones en el compilador y los simuladores del motor de IA

Nuevo software Vitis Embedded independiente

- Un instalador independiente más pequeño para diseñadores que escriben código C en el subsistema integrado de Arm®

- Se proporcionan todas las funciones integradas, incluidas las utilidades como Bootgen y XSCT

Nuevo Vitis Unified Integrated Design Environment

- GUI y CLI (Command Line Interface, interfaz de línea de comandos) coherentes en todos los flujos de trabajo de Vitis

- La GUI basada en Eclipse Theia de última generación proporciona una mejor flexibilidad y funciones fáciles de usar para mejorar la eficiencia del trabajo

Novedades de Vitis por categoría

Expande las secciones siguientes para obtener más información sobre las nuevas funciones y mejoras de la plataforma de software Vitis 2023.2. Para obtener información sobre las plataformas compatibles, los cambios de comportamiento y los problemas conocidos, consulta las notas de la versión 2023.2 de la plataforma de software Vitis para ver el Flujo de aceleración de aplicaciones y el Flujo de desarrollo de software integrado.

Nuevas funciones de la biblioteca DSP para motores de IA

- FFT de base mixta

- Transformada discreta de Fourier (DFT)

- Multiplicación matricial y de vectores general (GEMV)

Nueva compatibilidad de API para funciones de DSP

- IP de FFT con tipos de datos de twiddle de cint32

- Compatibilidad de cint16 para API FFT de base 4

- “fix2flt” y “flt2fix” vectorizados implementados en la API

Nueva compatibilidad de API para AIE-ML

- Las API ahora son compatibles con tipos de datos int32/cint32 en la función sliding_mul()

- Las API ahora son compatibles con tipos de datos <float> en la función sliding_mul()

- Se proporcionan todas las rutinas de las API de AIE necesarias para ser compatibles con la multiplicación de matriz dispersa

Principales actualizaciones de componentes:

- U-Boot 2024.1

- Arm Trusted Firmware 2.10

- Kernel de Linux 6.6_LTS

- QEMU 8.1

- Xen 4.18

- OpenAMP 2023.10

BSP caducos:

- AMD MicroBlaze™: VCU118, KCU105, KC705, AC701

- Zynq: zc706

- AMD Versal™: VMK180-EMMC, VMK180-OSPI

- Zynq MP: ZCU111

BSP nuevos (XSCT):

- BSP (Board Support Package, paquete de soporte de placa) de producción VEK280 con una nueva capa física de Ethernet

Nuevo BSP de flujo basado en SDT (System Device Tree, árbol de dispositivos del sistema):

- ZCU102, ZCU104, ZCU105, ZCU216

- ZCU208, ZCU208-sdfec, ZCU670

- VCK190

- VMK180

- VPK120

- VPK180

- VEK280

- El compilador de AIE ahora es compatible con matrices 2D y 3D como entradas o salidas

- Vitis Analyzer ahora genera un informe de guía para ajustar el tamaño de FIFO

- Nueva compatibilidad para el kernel del simulador de múltiples procesos y la aceleración del analizador de VCD (value change dump, volcado de cambio de valor)

- Interfaz externa con el entorno MATLAB® y los generadores de tráfico Python

- Modelo AXI Stream mejorado compatible con ciclos de vacío/espera en la alineación PLIO

- Comprobación de reglas de diseño mejorada

- Descarga de rastreo del motor de IA mediante la depuración a alta velocidad

- Compatibilidad con la creación de perfiles de hardware en NoC (network on chip, red en chip) y DDRMC (DDR Memory Controller, controlador de memoria DDR) en el entorno Vitis

- La herramienta de Vitis ahora es compatible con el rastreo AIE-ML para la tarjeta aceleradora de AI Inference Alveo™ V70 y VEK280

- Actualizaciones del bloque de motor de IA

- Compatibilidad para importar gráficos AIE-ML como bloques en Vitis Model Composer

- Nuevas funciones de DSPlib para la implementación de AIE y AIE-ML en Vitis Model Composer

- Trazado de salida de simulador de AIE para señales internas en la herramienta Simulink®

- Actualizaciones de bloques de kernel HLS

- Generación automática de banco de prueba

- Amplia compatibilidad con tipos de datos para bloques de kernel HLS

- Integración de Vitis Model Composer y la herramienta Vitis

- Generación de archivos .xo y libadf.a directamente desde Vitis Model Composer

- Otras mejoras

- Compatibilidad con versiones de la herramienta MATLAB®: R2021a, R2021b actualización 6, R2022a actualización 6, R2022b

- Topologías adicionales compatibles para el flujo de validación de hardware

- Nuevos ejemplos adicionales disponibles en GitHub

- Nuevo IDE unificado de Vitis para componentes HLS

- Nuevos requisitos de licencia de Vitis HLS

- Nueva función de analizador de código para obtener estimaciones de rendimiento antes de ejecutar la síntesis de C

- Mejoras en la interfaz AXI:

- Compatibilidad para canales laterales HLS de AXI Stream

- Compatibilidad para el almacenamiento en caché maestro de AXI configurable por el usuario

- Otras mejoras:

- Nuevo informe de complejidad de código para permitir la identificación de problemas de tamaño de diseño durante la síntesis de C

- Mejoras en el tiempo de compilación: Mejora media del tiempo de compilación del 20 % en la versión 2023.2 en comparación con 2023.11

Lo más destacado de la versión 2023.1 de Vitis Software Platform:

Nuevas funciones de biblioteca Vitis™ para las matrices Versal™ AI Engine (AIE)

- Funciones de biblioteca DSP; más configuraciones de filtros FIR

- Funciones de biblioteca de solucionadores; mejoras para un mayor rendimiento

Mejoras de flujo de diseño para la Serie Versal AI Core y Serie AI Edge

- Compatibilidad del compilador de AIE para matrices 2D y 3D como entradas/salidas

- Compatibilidad de la guía del simulador de AIE para el dimensionamiento FIFO a fin de evitar condiciones de bloqueo

- Mejoras en los informes de estado de AIE

- Nueva GUI predeterminada para el analizador Vitis

Compatibilidad para la exportación del entorno Vitis al entorno Vivado™

- Permite a los equipos de desarrollo de herramientas de Vitis y Vivado trabajar en paralelo en función de un punto de control de interfaz común

Novedades de Vitis por categoría

Expande las secciones siguientes para obtener más información sobre las nuevas funciones y mejoras de la plataforma de software AMD Vitis 2023.1. Para obtener información sobre las plataformas compatibles, los cambios de comportamiento y los problemas conocidos, consulta las notas de la versión 2023.1 de la plataforma de software Vitis para ver el Flujo de aceleración de aplicaciones y el Flujo de desarrollo de software integrado.

Biblioteca DSP: filtros FIR

- FIR de remuestreo fraccionario, FIR de tasa única, FIR de media banda y FIR de cambio de tasa mejorados para admitir anchos de bits de coeficiente mayores que el ancho de bit de datos

- El FIR de remuestreo fraccionario también es compatible con la operación SSR, ya que usa múltiples mosaicos AIE e incorpora la función de recarga de coeficiente

Solver Library

- Rendimiento de API mejorado con diseños de streaming de alto rendimiento (~300 mosaicos)

- Compatibilidad de descomposición QR y de Cholesky con las funciones de los motores de datos 4D para ayudar a leer o escribir datos de las matrices de AIE

- El compilador de AIE ahora es compatible con las matrices 2D y 3D como entradas o salidas, además de 1D.

- El compilador de AIE es compatible con construcciones de gráficos dentro de gráficos (subgráficos) y construcciones de puertos condicionales.

- Nuevas API de conversión de datos de AIE CINT-to-CFLOAT.

- Mejora de los informes de estado de AIE para generar un archivo que incluya información sobre mosaicos, eventos y registros adicionales en los mosaicos AIE-ML y AIE en el diseño.

- Descarga de rastreo de eventos de AIE a través de HSDP (high-speed differential pairs, pares diferenciales de alta velocidad) en lugar de almacenarlo en la memoria de los dispositivos Versal.

- Compatibilidad con la creación de perfiles de hardware en NoC y DDRMC en el entorno Vitis.

- Rastreo de eventos con ventana de AIE para inspeccionar una parte específica de una aplicación.

- Guía sobre el dimensionamiento FIFO para evitar interbloqueos.

- Capacidad de seleccionar los nodos que el simulador de AIE informa para reducir el tamaño del archivo VCD del simulador y acelerar la simulación.

- El simulador de AIE ahora genera un informe (visible en el analizador de Vitis) que muestra qué AIE tiene violaciones de acceso a la memoria y cómo estas corresponden a las líneas en el código gráfico de C.

- La visualización de datos en la vista de rastreo ahora también es compatible con la matriz AIE-ML.

- Nueva compatibilidad de los tipos de datos para configuraciones de filtro FIR dirigidas a motores Versal AI Engine.

- Dos nuevas funciones de punto flotante optimizadas para DSP58s en los SoC adaptables de Versal.

- Tiempo de respuesta más rápido para todas las funciones de la biblioteca de Vitis Model Composer dirigidas a motores Versal IA Engine.

- Otras mejoras:

- Mejoras en los bloques de kernel HLS

- Mejoras en Vitis Model Composer Hub

- Compatibilidad para la versión R2021a, R2021b y R2022a de la herramienta MATLAB.

- Mejoras en el rendimiento2: mejoras de latencia promedio del 5,2 % en la versión 2023.1 en comparación con 2022.2.

- Una forma sencilla de descargar, ver y crear instancias con las funciones de las bibliotecas de L1 en la herramienta Vitis HLS.

- Compatibilidad mejorada para transacciones AXI e informes de ráfaga dentro de la herramienta Vitis HLS.

Lo más destacado de la versión 2022.2 de Vitis Software Platform:

Nuevas funciones de biblioteca Vitis™ para las matrices Versal™ AI Engine (AIE)

- Funciones mejoradas de la biblioteca DSP

- Funciones de Solver Library

- Funciones de Vision Library

- Funciones de Ultrasound Library

Mejoras de flujo de diseño para la Serie Versal AI Core y Serie AI Edge

- Controla la colocación relativa de kernels en la matriz de motor de IA: mayor rendimiento y mejor utilización

- Mejoras del simulador x86 de AIE: modelado mejorado de las condiciones de interbloqueo en el simulador x86

- Mejoras de API de AIE: se agregaron API de matriz “x” vector y FFT de base 3 y 5

- Compatibilidad mejorada de creación de perfiles y depuración para diseños de Versal: detección de interbloqueos, recopilación de datos de rastreo más grande, compatibilidad para bancos de pruebas de RTL/Python

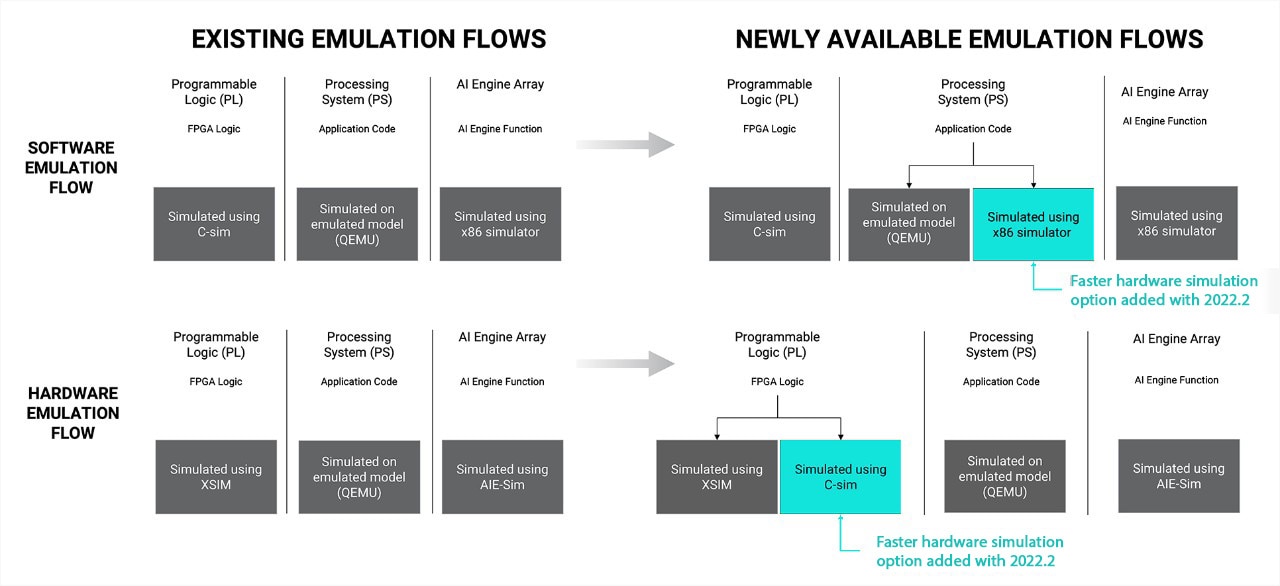

- Nuevas opciones de simulación para diseños heterogéneos en Vitis

Novedades de Vitis por categoría

Expande las secciones siguientes para obtener más información sobre las nuevas funciones y mejoras de la plataforma de software AMD Vitis 2022.2. Para obtener información sobre las plataformas compatibles, los cambios de comportamiento y los problemas conocidos, consulta las notas de la versión 2022.2 de la plataforma de software Vitis para ver el Flujo de aceleración de aplicaciones y el Flujo de desarrollo de software integrado.

Funciones de la biblioteca DSP

- La implementación del filtro FIR de superfrecuencia de muestreo (SSR) en el motor de IA ahora es compatible con la función de recarga de coeficiente y el tamaño de punto dinámico

- Se agregó el elemento de ventana de FFT a la función FFT dirigida a la matriz de motor de IA

Funciones de Solver Library

- Descomposición de rotación en cuadratura (QR)

- Descomposición de Cholesky

Funciones de Vision Library

- Cuatro nuevas funciones de video dirigidas a la matriz de motor de IA

Funciones de Ultrasound Library

- Varias funciones para ayudar a construir diseños de ultrasonidos médicos

- Capacidad de agregar restricciones para controlar la ubicación relativa de los kernels en la matriz de motor de IA: esto permite a los usuarios obtener un mayor rendimiento y una mejor utilización

- Modelado mejorado de las condiciones de interbloqueo de AIE en el simulador x86

- Nueva API de AIE: se agregaron API de matriz “x” vector y FFT de base 3 y 5

- Generación de informes de creación de perfiles de motor de IA en la emulación de hardware

- Detección de interbloqueo mediante XSDB (AMD System Debugger) para diseños basados en el motor de IA y PL

- Descarga continua controlada por Xilinx Runtime (XRT) del rastreo de eventos del motor de IA a través de PLIO

- Compatible con la aplicación PS en la máquina host x86 para la emulación de software

- Permite modelos funcionales SystemC para la emulación de hardware en lugar de RTL

- Permite a los usuarios simular el kernel del motor de IA con un banco de prueba RTL simple o un generador de tráfico basado en scripts de Python

- El estado del motor de IA se puede analizar durante la emulación de hardware con el analizador Vitis™

Nuevas opciones de simulación del entorno de Vitis versión 2022.2: simulación x86 del sistema del procesador y simulación x86 del motor de IA. La simulación lógica programable se puede realizar utilizando el simulador x86.

- Funciones de diseño de Versal AI Engine

- Capacidad para agregar restricciones de gráficos a los diseños de bloques de AI Engine DSP Library: mejor utilización y rendimiento

- Nueva compatibilidad para la simulación de ciclo aproximado de diseños de AI Engine

- El bloque de importación de gráficos de AI Engine detecta automáticamente los puertos RTP (Run Time Parameter, parámetro de tiempo de ejecución)

- Mejoras y adiciones en los bloques de la biblioteca DSP

- Funciones generales

- Flujo de validación de hardware compatible con diseños de sistemas heterogéneos que utilizan matriz PL y AIE

- Actualización del bloque Vitis Model Composer Hub para brindar compatibilidad con un diseño heterogéneo

- Detección automática de subsistemas válidos de AI Engine, HDL y HLS

- Flujo de validación de hardware mejorado para diseños solo de HDL y diseños HDL → AI Engine → HDL para plataformas Versal

- Compatibilidad mejorada de estilo de codificación “paralelismo de tareas”.

- Permite una simulación de C más rápida y una mejor QoR (Quality of Results, calidad de los resultados).

- Mejoras adicionales de rendimiento y sincronización.

- Inferencia de ráfaga mejorada.

- Inferencia automática de desenrollamiento, canalización, creación de particiones de matrices y pragmas insertados para un mejor rendimiento.

- Precisión de sincronización mejorada que da como resultado un mejor cierre de sincronización a frecuencias más altas.

- Otras funciones

- Análisis y depuración: printf insertada en código en C ahora compatible incluso después de la síntesis en el RTL.

- Facilidad de uso: nuevo pragma de rendimiento para lograr automáticamente un intervalo de transacción determinado.

- Las interfaces HLS::stream ahora son compatibles con la IP de FFT y FIR.

Lo más destacado de la versión 2022.1 de Vitis Software Platform:

Mejora de Vitis™ Flow para Versal™ ACAP y AI Engine

- Compatibilidad con la plataforma base DFX (Dynamic Function Exchange, intercambio de funciones dinámicas) de AMD con una región estática y una región de DFX

- El perfil de AIE es compatible con la detección de paradas/interbloqueos y genera una vista de estados de AI Engine (incluidos los eventos de error) en Vitis Analyzer

- Los generadores de tráfico externos en la emulación de software, x86sim y AIEsim son mucho más flexibles y se pueden insertar muy fácilmente en los flujos de simulación y emulación

- Vitis Model Composer es compatible con la validación de hardware y la emulación de Linux y hardware

Vitis para DC y Vitis HLS

- Vitis proporciona compatibilidad adicional para la generación de informes del proceso de generación de regiones dinámicas y las mejoras en los informes de flujo incluyen tres informes nuevos o actualizados

- Vitis mejora la creación de perfiles de PL con la opción de descargar el rastreo a los recursos de memoria (preferido) o FIFO en la PL para un mejor rendimiento

- Ahora está disponible después de la simulación un nuevo visor de rastreo de línea de tiempo para mostrar el perfil del tiempo de ejecución y permitir al usuario permanecer en la GUI de Vitis HLS

- Vitis HLS ahora es compatible con un tipo de construcción “inteligente” de nivel superior a través del nuevo pragma de rendimiento o la directiva set_performance_directive

- Vitis Graph Library con mejoras de API L3 (1 ms de tiempo ahorrado para la llamada al kernel) a fin de obtener un mejor rendimiento

Novedades de Vitis por categoría

Expande las secciones siguientes para obtener más información sobre las nuevas funciones y mejoras de la plataforma de software AMD Vitis 2022.1. Para obtener información sobre las plataformas compatibles, los cambios de comportamiento y los problemas conocidos, consulta las notas de la versión 2022.1 de la plataforma de software Vitis para ver el Flujo de aceleración de aplicaciones y el Flujo de desarrollo de software integrado.

- Se agregó una nueva biblioteca de acelerador genómica (L1, L2 y L3)

- Graph Library con mejoras en L3 para el rendimiento

- Vitis Database Library con kernel multifuncional GQE

- Nuevas funciones agregadas en Vision Library

- Nuevas funciones en Vitis AIE Vision Library con adiciones y mejoras

- Vitis AIE DSP Library; el remuestreo de FIR reemplaza al interpolador fraccionario de FIR

- Nuevas API, API jxlEnc, API “leptonEnc”, API “resize” y API “WebpEnc” en Vitis Codec Library

Vitis Data Compression Library

- Mejora de compresión ZLIB con compresión Octa-Core personalizada para la solución de 8 KB

- Mejora de descompresión ZLIB con una IP personalizada para el tamaño de archivo de 8 KB

- Mejora de compatibilidad de consulta de la plataforma

- Mejora de HBM fácil de usar, capacidad para elegir un punto de entrada S_AXI específico al HMSS (HBM Memory Subsystem, subsistema de memoria de HBM) para un kernel M_AXI, inserción de RAMA (Random Access Memory Attachment, datos adjuntos de la memoria de acceso aleatorio) compatible desde los archivos de configuración

Vitis AI Engine Compiler

- Detección y análisis en hardware de parada/interbloqueo automático del motor de IA

- Análisis de la salida de estado automatizada

- Análisis de la salida de estado automatizada: búferes

- Análisis en hardware de la salida de estado manual

- Análisis de la salida de estado manual

- Mejoras de rastreo de eventos del motor de IA

- Generadores de tráfico externos AIEsim

- Mejoras en hardware de la creación de perfiles del motor de IA

- Compatibilidad del motor de IA para ventanas de difusión

- Modelo de programación gráfica mejorado de Vitis AI Engine Compiler

- Vitis AI Engine Compiler: PLIO/GMIO en gráficos ADF

HLS de Vitis

- Mejoras de análisis, nuevo visor de rastreo de línea de tiempo

- Mejoras de estilo de codificación; compatibilidad con la creación de particiones por matrices para el tipo Transmisión de bloques

- Abstracción de pragma, nuevo pragma de rendimiento (y directiva)

- Vitis Core “one liner”, Vitis HLS: nuevo visor de rastreo de línea de tiempo, nuevo pragma de RENDIMIENTO, ventanas compatibles con la transmisión de bloques

- Nuevo visor introducido

- Muestra el perfil en tiempo de ejecución de todas las funciones vigentes en tu diseño, es decir, aquellas que se convierten en módulos.

- Especialmente útil para ver el comportamiento de las regiones de flujo de datos después de la simulación conjunta.

- Nativo de Vitis HLS: no hay necesidad de iniciar el visor de forma de onda xsim (herramienta externa).

Vitis Analyzer

- Mejora en Vitis Analyzer; guardar/restaurar la personalización de la línea de tiempo

- Mejora en la creación de informes; información de sincronización xclbin, report_qor_assessment, resumen de automatización de Vivado

- Mejora en la creación de perfiles; nueva infraestructura de creación de perfiles de PL habilitada, se pueden agregar varias opciones de trace_memory a fin de insertar varios monitores de memoria (solo hardware), archivo de configuración de muestra para el enlazador v++ a fin de descargar datos de rastreo de todas las UP en SLR0 a DDR0 e igual para todas las UP en SLR1 a DDR1

Vitis IDE

- GUI de Bootgen actualizada para Versal

- Actualización de la cadena de herramientas

- XSCT (Xilin Software Command Tool), compatibilidad con STAPL, agrega el comando de generación de scripts del enlazador

- Sistema de compilación de flujo; consulta la documentación de compilación del sistema

Emulación de Vitis

- Agrega compatibilidad con Software Emulation para el reinicio automático y compatibilidad con el buzón para los kernels en ejecución permanente

- El kernel de ejecución libre no necesita while(1) para sw-emu

- Agrega compatibilidad con Software Emulation para el generador de tráfico externo

- Hardware Emulation puede utilizar el modelo de función de código fuente C de HLS para el streaming de la IP.

- Agrega xrt::system de API para sondear el número de dispositivos

- Agrega xrt::message de API para registrar mensajes

- El código host de la API nativa de XRT ahora requiere

-std=c++17 o superior - Agrega API experimentales xrt::Queue para la ejecución asíncrona de operaciones síncronas

- xbutil puede mostrar contadores FIFO de AIE, lo que ayuda a depurar situaciones de interbloqueo de AIE

- La opción xbutil --legacy se eliminó

- xclbinutil --info proporciona información de sincronización para plataformas integradas

- xbutil en ARM puede cargar imágenes de SOM (system on module, sistema en módulo)

- Utilidad independiente xbtop para mostrar el comando superior de Linux como salida (reemplazando al xbutil -top heredado)

- Las utilidades XRT son compatibles con la finalización automática en Bash con la tecla de tabulación

- Actualizaciones de la plataforma de Alveo; actualizaciones de plataforma para mejorar la estabilidad, actualizaciones de gestión de tarjetas, herramienta de actualización de firmware por SC (Satellite Controller, controlador de satélite)

- Plataforma de Embedded; nueva plataforma DFX VCK190: xilinx_vck190_base_dfx_202210_1, las plataformas integradas ahora están instaladas en Vitis; Vivado agrega un nuevo diseño personalizable de ejemplo: plataforma de Vitis para MPSoC

- Revisión importante del bloque de hub de Vitis Model Composer para escalabilidad y facilidad de uso.

- El flujo de validación de hardware ahora es compatible con Linux además del hardware físico.

- Los bloques “AIE to HDL” y “HDL to AIE” ya no incluyen los bloques de puerta de enlace HDL.

- La versión 2022.1 ahora se envía con una instantánea de los ejemplos para los clientes que no tienen acceso a Internet. La herramienta le pedirá al usuario que descargue una nueva revisión de los ejemplos de GitHub si está disponible.

- Para facilitar su uso, los bloques de utilidad que no forman parte de la generación de código ahora se presentan con un color de fondo blanco.

- Navegador de biblioteca mejorado y reorganizado para la facilidad de uso.

- Compatibilidad con RHEL 8.x.

- Compatibilidad con MATLAB: R2021a y R2021b.

Lo más destacado de la versión 2021.2 de Vitis Software Platform:

- Nuevos entornos de desarrollo específicos del dominio

- SDK (software development kit, kit de desarrollo de software) de Vitis™ Video Analytics en el SoM Kria™, y la tarjeta de desarrollo Alveo™ U30/U50 y VCK5000 Versal™: Obtener más información >

- Solución de cadena de bloques de Vitis en la tarjeta Varium™ C1100 con bibliotecas Vitis: Obtener más información >

- Compatibilidad de flujo completo de extremo a extremo para tarjetas VCK5000 y Varium C1100

- Funciones de herramientas principales mejoradas

- API de abstracción de alto nivel en C/C++ de Vitis AI Engine Compiler, inferencia automática de pragmas, restricciones de grupos de área

- Mejoras en el simulador x86 de Vitis AI Engine: informe de rastreo, violación de acceso a la memoria y detección de interbloqueo

- Mejoras en EoU, sincronización y QoR de Vitis HLS, API de HLS para realizar inferencias de ráfaga controladas por el usuario

- Vitis Analyzer mejorado para un mejor informe de rastreo de la línea de tiempo, visualización de datos y análisis de paradas

- Vitis XRT para compatibilidad con procesos múltiples y subprocesos de motor de IA para el control de gráficos del motor de IA

- Rastreo de motor de IA compatible con Vitis IDE y Vitis Emulation; emulación de software para aplicaciones de motor de IA

- Treinta y nueve bibliotecas de C/C++ nuevas en diversos dominios que cubren DSP, Data Analytics, Vision, Compression, Database, Graph, Security y entre otras; más de 1000 funciones de biblioteca en total

- Model Composer Vitis

- Tres veces más tiempo de compilación/simulación y siete veces mayor reducción de tiempo de compilación con la compilación paralela

- Nuevo flujo de validación de hardware y simulación conjunta funcional mejorada

Novedades de Vitis por categoría

Expande las secciones siguientes para obtener más información sobre las nuevas funciones y mejoras de la plataforma de software AMD Vitis 2021.2. Para obtener información sobre las plataformas compatibles, los cambios de comportamiento y los problemas conocidos, consulta las notas de la versión 2021.2 de la plataforma de software Vitis para ver el Flujo de aceleración de aplicaciones y el Flujo de desarrollo de software integrado.

Nota: Las bibliotecas Vitis Accelerated Library están disponibles como descarga independiente. Se pueden descargar desde GitHub o directamente desde el IDE de Vitis también.

| Biblioteca | 2021.1 | 2021.2 | Nuevas funciones en 21.2 |

|---|---|---|---|

| xf_blas | 167 | 167 | 0 |

| xf_codec | 3 | 3 | 0 |

| xf_DataAnalytics | 33 | 36 | 3 |

| xf_database | 62 | 65 | 3 |

| xf_compression | 78 | 93 | 15 |

| xf_dsp | 94 | 96 | 2 |

| xf_graph | 53 | 59 | 6 |

| xf_hpc | 37 | 37 | 0 |

| xf_fintech | 116 | 116 | 0 |

| xf_security | 135 | 140 | 5 |

| xf_solver | 11 | 11 | 0 |

| xf_sparse | 11 | 11 | 0 |

| xf_utils_hw | 55 | 57 | 2 |

| xf_opencv | 147 | 150 | 3 |

| Total | 1002 | 1041 | 39 |

Nota: Para Vision Library, solo se debe contar el número de subcarpetas en L*/tests, porque cada API tiene múltiples pruebas para diferentes tipos

Vitis Vision Library

- Lógica programable (PL)

- Procesamiento de imágenes monocromáticas de extremo a extremo (ISP) con CLAHE TMO (Contrast Limited Adaptive Histogram Equalization-based Tone Mapping Operator, operador de mapeo de tonos basado en la ecualización de histogramas adaptables limitados por contraste)

- RGB-IR junto con la canalización de procesamiento de imágenes RGB-IR (ISP)

- GTM (Global Tone Mapping, mapeo de tonos global) junto con una canalización de ISP con GTM

| Nuevas funciones | Cat. | Cliente/estratégico | Segmentos | Descripción |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | Automoción, ISM | • Compatible con interpolación cromática RGB-IR 4 x 4 • Principalmente para el sistema de monitoreo en cabina • Cámara de vigilancia con poca luz |

| Monocromático (CCCC) | ISP | Estratégico | Automoción, ISM, A&D | • Visión artificial • Aplicaciones con poca luz |

| Mapeo de tonos global (GTM) | ISP | Estratégico | Automoción, ISM, A&D | • Contraste y rango dinámico mejorados • Versión de menor costo en comparación con el mapeo de tonos local (LTM) |

| Flujo óptico denso TV-L1 | CV | NTT | ISM | • Robustez mejorada (contra la iluminación, el ruido, las oclusiones) para el flujo óptico |

Motor de IA (AIE)

- BlobFromImage

- Filtro 2D back to back compatible con tamaño de lote tres

| Nuevas funciones | Cat. | Cliente/estratégico | Segmentos | Descripción |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | Automoción, ISM | • Compatible con interpolación cromática RGB-IR 4 x 4 • Principalmente para el sistema de monitoreo en cabina • Cámara de vigilancia con poca luz |

| ML+X | ISP | Estratégico | Automoción, ISM, A&D | • Preprocesamiento de interferencias de ML |

| Pirámide Gaussiana | CV | Estratégico | Automoción, ISM, A&D | • Fundamental para el procesamiento de imágenes multiescala |

| Filtro de caja | CV | Estratégico | Automoción, ISM, A&D | • Fundamental para filtro de suavizado de paso bajo |

Vitis Data Analytics Library

- Solución de cadena de bloque de Vitis basada en bibliotecas de Vitis

- Soluciones de minería listas para usar en Ethereum

- De código abierto y fácil de usar e implementar con las bibliotecas de Vitis usando C++

- Flexible y escalable con las bibliotecas de Vitis

- Flexibilidad para minar múltiples monedas

- Para personalizar y compilar en hardware

- Diseño altamente optimizado

- Adición de API del analizador CSV en la biblioteca

- El analizador CSV puede analizar archivos de valor separados por comas y generar un stream de objetos que se pueden conectar fácilmente con las API de DataFrame

Vitis Graph Library

- Nuevas bibliotecas L2 agregadas

- Louvain con renumeración

- Renumeración

- La función “weight” es compatible con la similitud coseno

Vitis Database Library

- Inicio GQE compatible con la función de entrada/salida asíncrona, junto con compatibilidad multitarjeta.

- La compatibilidad asíncrona permitirá que la FPGA comience a procesar tan pronto como una parte de los datos de entrada esté lista.

- La compatibilidad multitarjeta permite identificar múltiples tarjetas Alveo que son adecuadas para trabajar.

Vitis Data Compression Library

- Compresión de varios núcleos ZSTD

- Se creó una nueva arquitectura de varios núcleos ZSTD y se proporcionó un rendimiento de >1 Gb/s utilizando cuatro núcleos.

- Optimización de descompresión ZSTD

- Descompresión ZSTD optimizada para el rendimiento (aumento de un 20 %) y los recursos (reducción del <30 %)

- Mejora de núcleo de stream GZIP/ZLIB para IBM

- IP de streaming de compresión estática y dinámica personalizada (4 KB y 8 KB)

- Funcionalidad agregada para proporcionar tamaño comprimido en el puerto TUSER

- Mejora en la descompresión GZIP/ZLIB para IBM

- Decodificador Huffman optimizado para reducir la latencia en <1,5 K ciclos

- Se redujeron los recursos significativamente a 6,9 K (antes era >9 K)

- Funcionalidad de suma de comprobación ADLR32 agregada

- PoC (Proof of Concept, prueba de concepto) del compilador de sistema GZIP

- Se creó una PoC de compilador de sistema para la solución de compresión de GZIP y se comparó con el host en OpenCL.

Vitis DSP Library

- DSPLib en GitHub desde el 2021

- Transformada rápida de Fourier (FFT/iFFT)

- Aumento del tamaño del punto a 32 K (dependiente del tipo de datos)

- Compatibilidad para la API de stream, así como la API de ventana

- Potencia paralela (de 0 a 4)

- Permite un mayor rendimiento y extiende el rango de tamaños de puntos compatibles

- Filtros FIR

- Compatibilidad de stream inicial para FIR asimétrico/simétrico de tasa única

- DDS/mezclador

- Nueva unidad de biblioteca en la versión 2021.2

Vitis Security Library

- Se lanzan las funciones KECCAK-256 (función hash) y CRC32C (función de suma de comprobación)

Vitis Utilities Library

- Se agregan dos implementaciones de motor de datos para depurar el problema en hardware.

- LoadDdrToStreamWithCounter: para cargar datos desde la DDR de PL hasta el motor de IA a través del stream de AXI y registrar el recuento de datos que se envía al motor de IA.

- StoreStreamToMasterWithCounter: para recibir datos del motor de IA a través del stream de AXI y guardarlos en la DDR de PL, así como registrar el recuento de datos que se envían a la DDR.

API de motor de AI

- Implementada como biblioteca solo de encabezados de C++ que proporciona tipos y operaciones que se traducen en intrínsecas eficientes de motor de IA.

- Proporciona tipos de datos parametrizables que permiten la programación genérica.

- Implementa las operaciones más comunes de una manera uniforme para diferentes tipos de datos.

- Traduce de forma transparente las primitivas de alto nivel en intrínsecas optimizadas de motor de IA.

- Mejora la portabilidad en las arquitecturas del motor de IA.

La API de motor de IA será el método principal para la programación del kernel de motor de IA.

Optimizaciones de alto nivel

Opciones de optimización del compilador de motor de IA

- --xlopt=0, sin optimización aplicada.

- --xlopt=1, cálculo automático del tamaño de la pila, generación de guía a partir del análisis de LLVM IR (LLVM Intermediate representation, representación intermedia de LLVM).

- --xlopt=2, inserción automática, peeling de bucle para bucles desenrollados e inserción de pragmas.

Introducción de --xlopt=2 para mejorar el rendimiento; el valor predeterminado sigue siendo --xlopt=1.

- Inserción automática

- Inserta automáticamente funciones si es práctico y posible hacerlo, incluso si las funciones no se declaran como __inline o inline.

- Inserción automática de pragmas

- Inserta pragmas en el código del kernel automáticamente (ver siguiente diapositiva para obtener más detalles).

Inferencia de pragmas

Necesaria para optimizar los kernels.

- Alivia la responsabilidad del usuario de agregar pragmas de ajedrez efectivos y correctos.

Compatibilidad para inferir automáticamente cinco pragmas en la versión 2021.2.

- Para el rendimiento:

- chess_prepare_for_pipelining para el bucle más interno, y bucles exteriores con recuento de iteraciones conocido

- chess_loop_range para bucles con recuento de iteraciones conocido

- chess_unroll_loop/chess_flatten_loop para bucles más internos con recuento de iteraciones conocido

- Para la corrección:

- chess_unroll_loop_preamble cuando el recuento de iteraciones no es un múltiplo del factor de desenrollado

Modelo de programación gráfica PLIO y GMIO actualizado

Los cambios de modelo incluyen las siguientes modificaciones

- Cambios en el uso de “simulación::platform”

- Interacción con objetos PLIO/GMIO en el gráfico; la posición determina la entrada/salida

- Cambios de objetos globales PLIO/GMIO en el gráfico

- Cambios alrededor de las declaraciones graph connect<>

PLIO/GMIO en gráficos ADF

Actual

- Escribe PLIO, GMIO, simulation::platform y conexiones a escala global

GMIO gm0(“GMIO_In0”, 64, 1);

GMIO gm1(“GMIO_In1”, 64, 1);

…

GMIO gm7(“GMIO_In7”, 64, 1);

PLIO pl0(“PLIO_Out0”, plio_32_bits, “data/output0.txt”, 250.0);

PLIO pl1(“PLIO_Out1”, plio_32_bits, “data/output1.txt”, 250.0);

…

PLIO pl7(“PLIO_Out7”, plio_32_bits, “data/output7.txt”, 250.0);

simulation::platform<8,8> plat(&gm0, &gm1,…, &gm7, &pl0, &pl1,…, &pl7,);

subgraph g;

connect<> net0(plat.src[0], g.in[0]);

connect<> net1(plat.src[1], g.in[1]);

…

connect<> net7(plat.src[7], g.in[7]);

connect<> net8(g.out[0], plat.sink[0]);

connect<> net9(g.out[1], plat.sink[1]);

…

connect<> net15(g.out[7], plat.sink[7]);

Método alternativo

- Crea un gráfico de nivel superior e incorpora PLIO, GMIO y las conexiones

- Permite la gestión de conexiones dentro para el bucle

class topgraph

{

input_gmio gm[8];

output_plio pl[8];

subgraph sg;

topgraph()

{

for (i=0; i<8; i++)

{

gm[i] = input_gmio::create(“GMIO_In”+std::to_string(i), 64, 1);

pl[i] = output_plio::create(“PLIO_Out”+std::to_string(i), plio_32_bits, “data/output”+std::to_string(i)+”.txt”, 250.0);

connect<>(gm[i].out[0], sg.in[i]);

connect<>(sg.out[i], pl[i].in[0]);

}

}

};

topgraph g;

Mejoras en las restricciones del grupo de área

Posibilidad de utilizar indicadores en el gráfico ADF o un archivo de restricciones para controlar el mapeador y el enrutador

- -contain_routing: cuando el valor TRUE especificado asegura que todo el enrutamiento, incluidas las redes entre los nodos contenidos en el grupo nodeGroup, está contenido dentro del grupo de área.

- -exclusive_routing: cuando el valor TRUE especificado asegura que todo el enrutamiento, sin incluir las redes entre los nodos del grupo nodeGroup, está excluido del grupo de área.

- -exclusive_placement: cuando el valor TRUE especificado evita que todos los nodos no incluidos en el grupo nodeGroup se coloquen dentro del cuadro delimitador del grupo de área.

Instantáneas

Las instantáneas son archivos de texto que contienen comentarios y datos relativos a todos los puertos del kernel.

- streams, streams de paquetes, streams en cascada

- ventanas, búfer

- RTP

Incluye también todos los puertos de plataforma

- PLIO, GMIO, RTP

Permite a los usuarios inspeccionar el tráfico de datos en los puertos del kernel sin usar el depurador y sin requerir la instrumentación del código del kernel.

Detección de interbloqueo

- Detecta interbloqueos en simulaciones x86, ya sea que esta situación se deba a datos de entrada insuficientes o a una profundidad FIFO desequilibrada en una ruta reconvergente.

- La función stop-on-deadlock debe habilitarse durante la simulación x86 especificando la opción --stop-on-deadlock.

- Si la simulación se detiene debido a un interbloqueo, el mensaje de error indica que se la debe volver a ejecutar con la opción -trace --timeout.

Detección de violación de acceso a la memoria

Integración en Valgrind para la detección de violación de acceso a la memoria

- Detecte

- lectura y escritura fuera de los límites

- lectura de la memoria no inicializada

- No se requiere un indicador específico para la compilación

- Los indicadores de simulación pueden ser:

- --valgrind: la simulación se ejecuta como de costumbre y Valgrind muestra un informe

- --valgrind-gdb: igual que la anterior, pero con depuración gdb al mismo tiempo

Informe de rastreo

La situación de interbloqueo da como resultado una salida de simulación deficiente y dificultades para analizar el origen del error.

La opción de rastreo de la simulación x86 permite al simulador registrar información con varias marcas de tiempo:

- Inicio/fin de iteraciones del kernel

- Inicio/fin de las paradas de stream

- Inicio/fin de la parada de bloqueo

Las marcas de tiempo son diferentes en la simulación x86 y la simulación del motor de IA.

Inferencia de ráfaga controlada por el usuario

- Para casos de uso que no satisfacen la inferencia automática de ráfaga de la herramienta Vitis HLS, el usuario puede adoptar la optimización de ráfagas manual recientemente introducida.

- La nueva clase “hls::burst_maxi” compatible con el comportamiento de ráfaga de control manual. Se proporcionan nuevas API de HLS para usarlas junto con la nueva clase.

- El usuario necesita entender el protocolo AXI AMBA y el modelado de nivel de transacciones de hardware en el diseño de HLS.

Mejoras de sincronización y QoR

- Proporciona compatibilidad para que el usuario ingrese restricciones de rendimiento de alto nivel.

- Mejora la precisión de la estimación de sincronización de HLS. Cuando HLS informa el cierre de la sincronización, la síntesis de RTL en Vivado también debe esperar cumplir con la sincronización.

Mejoras de EoU

Agrega el informe de adaptadores de interfaz en los informes de síntesis de C.

- Los usuarios necesitan conocer el impacto en los recursos que tienen los adaptadores de interfaz en su diseño.

- Los adaptadores de interfaz tienen propiedades variables que impactan en la QoR del diseño.

- Algunas de estas propiedades tienen controles de usuario asociados que se deben reportar a los usuarios.

- Se proporcionan versiones de texto de los informes bind_op y bind_storage.

Agrega una nueva sección en el informe de síntesis para mostrar la lista de pragmas y advertencias sobre ellos.

- El usuario puede entender fácilmente cuál de los pragmas agregados tiene problemas.

Mejoras en el análisis y la presentación de informes

El visor gráfico de llamada de funciones tiene algunas funciones nuevas.

- Nueva compatibilidad para acercar o alejar basada en el arrastre del mouse.

- Nueva función de visión general que muestra el gráfico completo y permite al usuario acercar partes del gráfico general.

- Todas las funciones y todos los bucles se muestran junto con sus datos de simulación.

Un nuevo visor de rastreo de línea de tiempo está ahora disponible después de la simulación. Este visor muestra el perfil de tiempo de ejecución de tu diseño y permite al usuario permanecer en la GUI de Vitis HLS.

Mejora del resumen del enlace

- Proporciona información de frecuencia de reloj para el motor de IA, la plataforma y las unidades de procesamiento.

- Proporciona una nueva tabla llamada Relojes en el diagrama de sistema y el diagrama de plataforma.

Mejora de la exportación de la plataforma

- Exportación XSA desde Vivado sin necesidad de que los archivos de origen sean locales para el proyecto.

- Exportación XSA desde Vivado sin cambios en la estructura del proyecto.

- Empaqueta las IP que se utilizan en el proyecto de la plataforma de hardware en lugar de empaquetar todo el repositorio de IP.

Mejoras en la emulación de aplicaciones del motor de IA

- Proporciona compatibilidad para la integración del banco de prueba externo con la simulación de AIE.

- Proporciona compatibilidad para la integración del banco de prueba externo con la simulación x86.

- Compatibilidad para la depuración de GDB con la simulación x86.

- Proporciona compatibilidad para instantáneas de datos entre los kernels en un gráfico para la simulación x86.

- Proporciona compatibilidad para la comprobación de violación de acceso en la simulación x86.

- Proporciona compatibilidad para detenerse en el interbloqueo en la simulación x86.

Compatible con AI Engine Trace

Compatible con Software Emulation para aplicaciones de motor de IA

Compatible con el generador de tráfico externo en Verilog/System Verilog

Extiende la inserción de monitoreo de perfiles a la memoria de monitoreo

- Actualmente, la lógica de monitoreo de perfiles se puede insertar en la base del puerto de kernel/UP. Esta función proporciona al usuario la opción de insertar la lógica de monitoreo en la interfaz de memoria directamente.

- La visualización del ancho de banda de memoria lograda directamente en las interfaces de memoria se puede reflejar en el informe de resumen de perfiles.

- La memoria DDR y PLRAM son compatibles.

- Compatible con el flujo de hardware.

- Para habilitar esta función, es necesario configurar tanto la fase de enlace como la xrt.

- memory=all

- data_transfer_trace= coarse|fine o

- opencl_device_counter=true

Extiende la inserción de monitoreo de perfiles a la memoria de monitoreo

- Un ejemplo de vadd que permite el monitoreo de la interfaz de memoria

- Se incluye la nueva tabla “Memory Bank Data Transfer” (transferencia de datos del banco de memoria)

Mejoras de Vitis Analyzer

Informe de resumen de perfiles genéricos generado para aplicaciones ajenas a OpenCL

- Proporciona el mismo nivel de compatibilidad para las aplicaciones de la API de XRT y la API de HAL (hardware abstraction layer, capa de abstracción de hardware).

- Los usuarios seleccionan qué tipos de informes quieren crear, la herramienta los genera automáticamente y los visualiza en Vitis Analyzer.

Agrega comandos de OpenCL a la línea de tiempo de eventos de PL

- La creación de perfiles agregará sobrecarga y XRT proporciona compatibilidad para volcar los eventos OpenCL en el rastreo de la línea de tiempo sin sobrecarga.

- Vitis Analyzer puede procesar la salida XRT y mostrarla en la vista de rastreo de la línea de tiempo.

- xocl_debug=true necesita configurarse en xrt.ini.

Aplana la jerarquía de señales en el informe de rastreo de la línea de tiempo

- De forma predeterminada, el informe de rastreo de la línea de tiempo muestra el rastreo de la señal de manera jerárquica.

- Vitis Analyzer proporciona compatibilidad para aplanar la jerarquía mediante el cambio del símbolo “Flatten Signal” (Aplanar señal).

- La comparación de la forma de onda es compatible con el rastreo de línea de tiempo aplanado.

Vitis Analyzer: visualización de datos

- Muestra los datos de entrada/salida de los kernels del motor de IA en un diseño de motor de IA

- Ayuda a depurar diseños de motor de IA para mostrar datos de entrada/salida junto con la línea de tiempo

- Funciona con AIE Simulator

- Compatible con

- Tipos de datos de ventana/stream/cascada

- Streams de paquetes

- Kernels en plantilla

- Utilidad de volcado de datos

Vitis Analyzer: análisis de paradas del motor de IA

- Vitis Analyzer proporciona compatibilidad de visualización para permitir a los usuarios identificar la causa raíz de las paradas.

- Compatibilidad

- Indicadores de rendimiento

- Análisis de paradas por interbloqueo

- Análisis de paradas de stream

- Análisis de paradas de cascada

- Análisis de paradas de memoria

- Flujo compatible

- AIE Simulator

- Emulación de hardware

Xilinx Runtime Library (XRT):

- API de XRT

- La API nativa de XRT es compatible con el control del kernel administrado por el usuario con xrt::ip.

- Utilidades de XRT

- Las herramientas xbutil y xbmgmt ahora vienen predeterminadas.

- Para usar las utilidades heredadas, utiliza xbutil --legacy o xbmgmt --legacy con subcomandos heredados.

- Nueva utilidad, xball

- Aplica comandos xbutil o xbmgmt a todas las tarjetas de centro de datos instaladas o a una parte de ellas mediante filtros. Consulta xball --help para más detalles.

- Un nuevo comando, xbutil configure

- Permite habilitar, deshabilitar o configurar la memoria host PCIe y las funciones entre pares de PCIe. Consulta la documentación de XRT para obtener más detalles.

- Todas las utilidades de XRT ahora son compatibles globalmente con la opción --force para omitir la confirmación interactiva del usuario.

- Las herramientas xbutil y xbmgmt ahora vienen predeterminadas.

- Creación de perfiles

- Se genera un informe de resumen de perfil cuando se habilita cualquier opción de creación de perfiles.

- Todas las tablas de resumen y las orientaciones aplicables se generan en función de las opciones de creación de perfiles permitidas en el archivo xrt.ini.

- Nueva tabla de resumen de transferencia de datos para agregar información sobre un recurso de memoria cuando se agregan monitores a los recursos de memoria en el diseño.

- Nuevos conjuntos de métricas de creación de perfiles de AIE para contar diferentes eventos de AIE, entre ellos, (1) excepciones de punto flotante en AIE, (2) recuentos de ejecución de mosaicos, y (3) comunicación de entrega y obtención de stream.

- Incorporado

- Mejoras del gestor de memoria de zocl para ser compatible con cualquier sptag.

Compatibilidad de procesos múltiples de Vitis XRT para motores de IA

- API C y C++ a fin de definir modos de acceso para múltiples procesos y compartir el acceso a la misma matriz y los mismos gráficos de motor de IA.

- ¬Protege los gráficos y la matriz de motor de IA del acceso no deseado.

- Compatibilidad con tres modos para abrir los gráficos y la matriz de motor de IA

- Modo exclusivo (evitar el acceso de cualquier otro proceso)

- Modo primario (solo permite que otros procesos accedan de forma no destructiva)

- Modo compartido (solo acceso no destructivo)

- Para tenerlos en cuenta cuando se necesita compatibilidad con múltiples procesos. Por ejemplo:

- Evitar que otros accedan a la matriz de motor de IA (acceso exclusivo).

- Múltiples usuarios que controlan diferentes gráficos por separado (compatibilidad con múltiples aplicaciones).

- Un usuario principal que controla el gráfico y permite que otros sondeen el estado de ejecución (acceso primario y compartido).

Estado de compatibilidad de Vitis XRT para motores de IA

API C y C++

- API versión C

- Para matriz de motor de IA:

- xrtAIEDeviceOpenExclusive (modo exclusivo)

- xrtAIEDeviceOpen (modo primario)

- xrtAIEDeviceOpenShared (modo compartido)

- Para gráfico de motor de IA:

- xrtGraphOpenExclusive (modo exclusivo)

- xrtGraphOpen (modo primario)

- xrtGraphOpenShared (modo compartido)

- Para matriz de motor de IA:

- API versión C++

- Modo de acceso compatible con la clase xrt::aie::device en el constructor

- enum class access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2 };

- Modo de acceso compatible con la clase xrt::graph en el constructor

- enum class access_mode : uint8_t { exclusive = 0, primary = 1, shared = 2, none = 3 };

- Modo de acceso compatible con la clase xrt::aie::device en el constructor

- Accede a las últimas plataformas Vitis Target Platform para tarjetas Alveo y consulta la sección Introducción de la tarjeta aceleradora.

- Descarga Vitis y consulta la sección Paquetes de Alveo.

AI Engine DSP Library: nuevos bloques

- AIE DDS

- Mezclador de AIE

Compilación paralela

- Tiempos reducidos en comparación con la versión 2021.1 (por ejemplo, las siguientes cifras son para la cadena TX de 200 MHz):

- Tiempo de compilación y simulación reducido tres veces

- Tiempo de compilación reducido siete veces

- Tiempo de inactividad después de la simulación reducido de 25 s a ~0 s

Mejora de Constraint Editor

- Navegación mejorada en la versión 2021.2

Mejoras de tamaño fijo

Mejoras de bloques de tamaño variable

Compatibilidad mejorada de simulación conjunta funcional

- Exportar datos Matlab para entrada en motor de IA – xmcVitisWrite

- Importar datos de motor de IA en Matlab – xmcVitisRead

- Importar datos de motor de IA en Matlab – xmcVitisRead

Otros

- Importar un bloque de kernel del motor de IA o HLS sin entrada (bloque de origen)

- Compatibilidad con nuevos tipos de datos

- Datos nativos int64 y uint64 de Simulink para el desarrollo del motor de IA en lugar de los tipos de datos de AMD, x_sfix64 y x_ufix64

- accfloat y caccfloat para desarrollo de motores de IA

- Compatibilidad para Ubuntu 20.04

- Compatibilidad para MATALB 20a, 20b, 21a (no compatible con MATLAB 21b)

- Adición de nuevos ejemplos

- Ejemplo de filtro SSR de doble stream con 64 kernels

- Pseudo inversa (64 x 32): ejemplo de commslib

- Utiliza el comando xmcLibraryPath para apuntar a una ubicación DSPLib personalizada

- Muchas más mejoras y correcciones de errores

Lo más destacado de la versión 2021.1 de Vitis Software Platform:

- Compatible con el kit de inicio de AI para visión KV260 de los SoM (System-on-Modules, sistemas en módulo) de AMD Kria. El flujo completo de Vitis para ML (motor de inferencia DPU) + X (kernel RTL y kernels de visión artificial basados en Vitis HLS). Obtener más información >

- Compatibilidad con las nuevas bibliotecas de C/C++ optimizadas para el rendimiento Vision, DSP, Graph (modularidad de Louvain), Codec en el procesamiento de imágenes y de compresión (GZIP, Facebook ZSTD, aceleración de toda la aplicación ZLIB) en FPGA o Versal ACAP a través de CPU/GPU.

- Flujo de diseño mejorado del kit de desarrollo de núcleo de Vitis™ en dispositivos Versal ACAP: mejoras de visualización para el informe de rastreo de diseño del motor de IA, rastreo de eventos del motor de IA a través de GMIO, recompilación incremental, nuevo wizard de imagen de inicio y compatibilidad con archivos de origen del motor de IA cifrados.

- La nueva herramienta Vitis Model Composer permite una rápida exploración y verificación del diseño dentro del entorno MATALB y Simulink® de MathWorks, lo que permite la simulación conjunta de bloques dirigidos a motores de IA y lógica programable, generación de código y creación de bancos de prueba.

- Nueva GUI de Vitis HLS Flow Navigator para un acceso rápido a las fases de flujo y los informes. Fusiona las vistas de síntesis, análisis y depuración en un contexto general predeterminado.

Novedades de Vitis por categoría

Expande las secciones siguientes para obtener más información sobre las nuevas funciones y mejoras de la plataforma de software AMD Vitis 2021.1. Para obtener información sobre las plataformas compatibles, los cambios de comportamiento y los problemas conocidos, consulta las notas de la versión 2021.1 de la plataforma de software Vitis para ver el Flujo de aceleración de aplicaciones y el Flujo de desarrollo de software integrado.

Nota: Las bibliotecas Vitis Accelerated Library están disponibles como descarga independiente. Se pueden descargar desde GitHub o directamente desde el IDE de Vitis también.

DSP de AIE

- DSPLib publicada como parte del conjunto de bibliotecas aceleradas de Vitis en GitHub.

- DSPLib contiene funciones de DSP parametrizables comunes utilizadas en muchas aplicaciones avanzadas de procesamiento de señales. Todas las funciones actualmente admiten interfaces de ventana compatibles con la interfaz de streaming.

Filtros FIR

Función |

Espacio de nombres |

Tasa única, asimétrico |

dsplib::fir::sr_asym::fir_sr_asym_graph |

Tasa única, simétrico |

dsplib::fir::sr_sym::fir_sr_sym_graph |

Interpolación asimétrica |

dsplib::fir::interpolate_asym::fir_interpolate_asym_graph |

Diezmación, media banda |

dsplib::fir::decimate_hb::fir_decimate_hb_graph |

Interpolación, media banda |