概要

AMD Vitis™ HLS で直感的な設計と生産性向上が可能になる

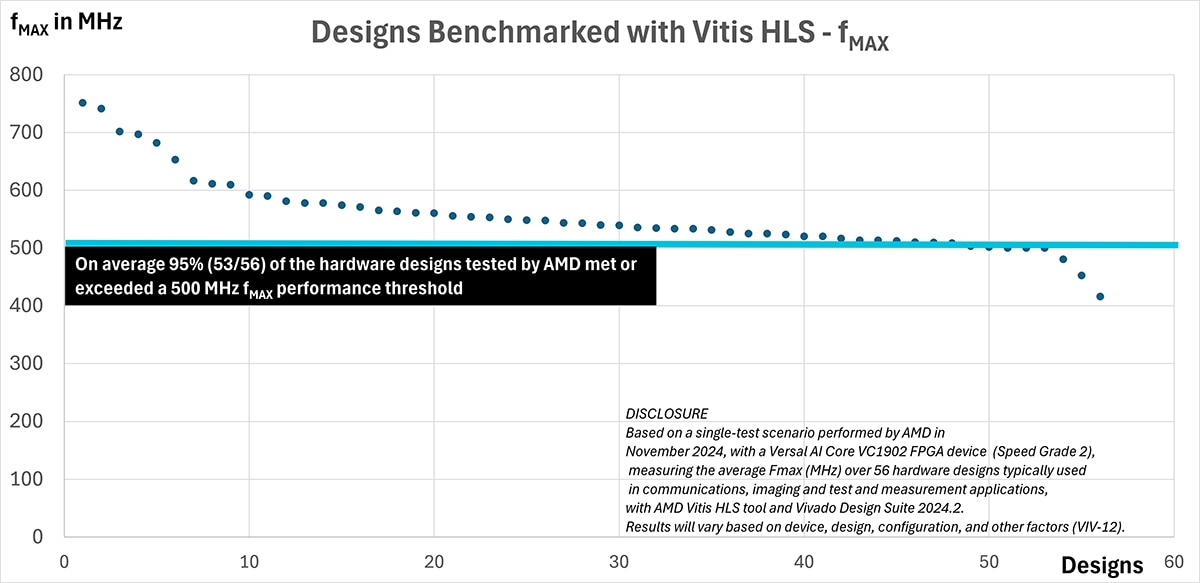

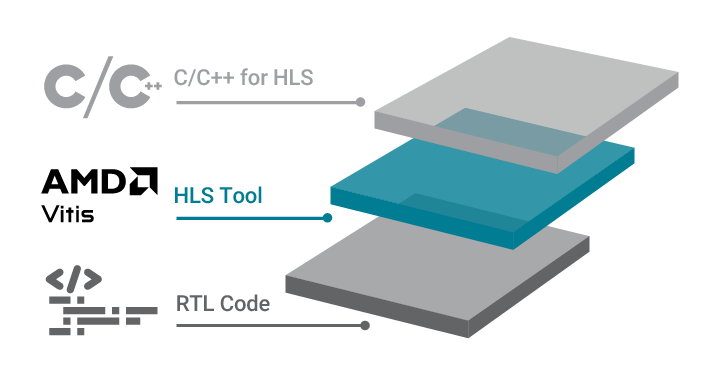

AMD Vitis™ HLS ツールを使用すると、C/C++ で定義した関数を RTL に合成することで、複雑な FPGA アルゴリズムを簡単に作成できます。このツールは、合成/配置配線用の Vivado™ Design Suite およびヘテロジニアス システムの設計や活用のための Vitis 統合ソフトウェア プラットフォームと密接に統合されています。

- Vitis HLS フローを使用することで、C コードに指示子を適用して目的の実装に応じた RTL を生成できる。

- C ソース コードからさまざまなデザイン アーキテクチャを構築でき、高品質の RTL を生成できる。

- C シミュレーションを使用してデザインを検証できるため、通常の RTL ベースのシミュレーションよりもすばやくイテレーションを実行できる。

- Vitis HLS ツールには、デザインの最適化をサポートするための豊富な解析およびデバッグ機能がある。

AMD Vitis™ HLS のパフォーマンス プラグマ

AMD Vitis HLS には、高い QoR を実現するための新しい最上位レベルのパフォーマンス プラグマが追加されています。この新機能の使用方法については、技術モジュールを参照してください。

設計手法

Vitis HLS プログラミング モデル

Vitis HLS の C コードは、AMD アダプティブ SoC および FPGA アーキテクチャの特性を最大限に活かすように設計されています。

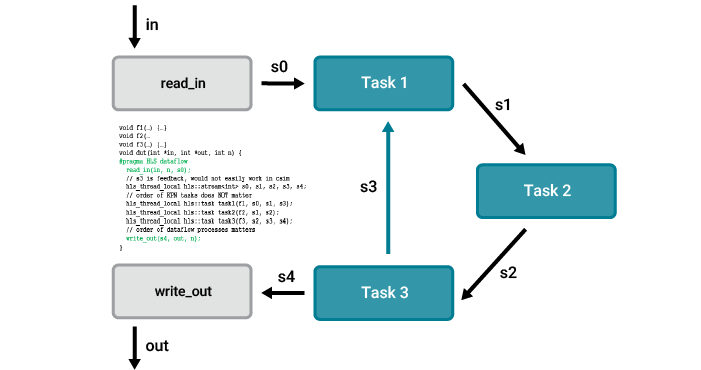

Vitis HLS ツールは並列プログラミング構造をサポートしているため、要件に応じた実装をモデル化できます。たとえば次のような構造があります。

- プロセスレベルでの並列処理を可能にする HLS タスク

- データレベルの並列化を可能にする HLS ベクター

- 同時タスク間の通信を可能にする HLS ストリーム

- 合成プラグマ(パイプライン、アンロール、配列分割、インターフェイス プロトコルなど) を使用して結果を制御できる。

- 詳細は、Vitis 高位合成ユーザー ガイドの「HLS プログラミング ガイド」セクションを参照。

MATLAB から HLS 対応の C++ コードに変換

MATLAB® で作成した関数は、MATLAB R2025a に含まれる MathWorks HDL Coder のコード生成機能によって、AMD Vitis™ HLS 向けの C++ コードに変換できます。

生成された合成可能な C++ コードは、Vitis™ HLS の入力として使用できます。このワークフローを活用することで、(通常 MATLAB で行われる) 高レベルなアルゴリズム デザインを、低レベルな RTL 実装へと効率よく変換できます。

MATLAB と HDL Coder を使用してテストベンチを作成し、その後、HDL Coder のコード生成機能で Vitis HLS に取り込み、AMD のアダプティブ SoC や FPGA 上でシミュレーションや合成を実行します。

詳細は、MathWorks 社の HDL Coder のページをご覧ください。

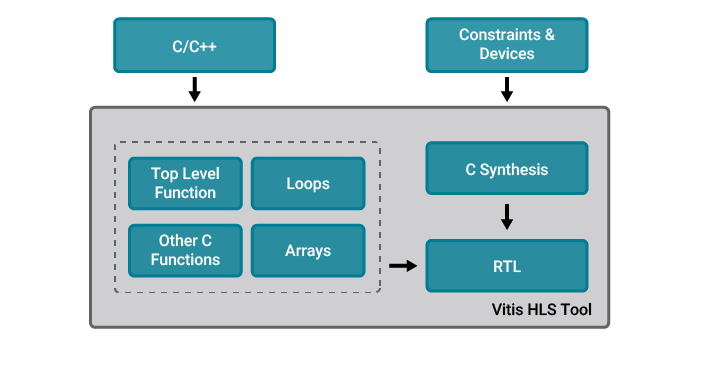

C から RTL への変換

Vitis HLS ツールは、C コードのさまざまな部分を異なる方法で合成します。

- C/C++ コードの最上位関数の引数が RTL I/O ポートに合成され、インターフェイス合成のハードウェア プロトコルを使用して自動的に実装される。

- その他の C 関数は RTL ブロックに合成される。デザインの階層構造は維持される。

- C 関数のループは、パフォーマンス向上のためそのままループとして残すか、パイプライン処理される。

- C コードの配列は、ライブラリ内の任意のメモリ リソース (BRAM、LUTRAM、URAM など) に合成できる。

- レイテンシ、開始間隔、ループの反復レイテンシ、リソース使用率などのパフォーマンス指標は合成レポートで確認できる。

- Vitis HLS ツールのプラグマ指示子や最適化指示子を使用して、C/C++ コードの合成結果を制御できる。

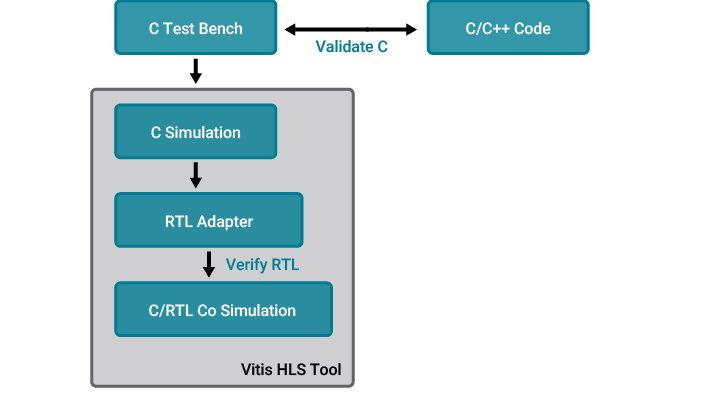

シミュレーションおよび検証

Vitis HLS ツールにはビルトインのシミュレーション フローがあり、検証時間を短縮できます。

- C シミュレーションでは C コードの機能が検証される。このステップは C テストベンチを使用し、すぐに完了する。

- C/RTL 協調シミュレーションでは、C テストベンチを再利用して生成済みの RTL を検証する。つまり、RTL が C ソース コードと機能的に同じであるかを検証。

- このフローには、解析、デバッグ、波形表示機能が統合されており、一般的なシミュレータをサポート。

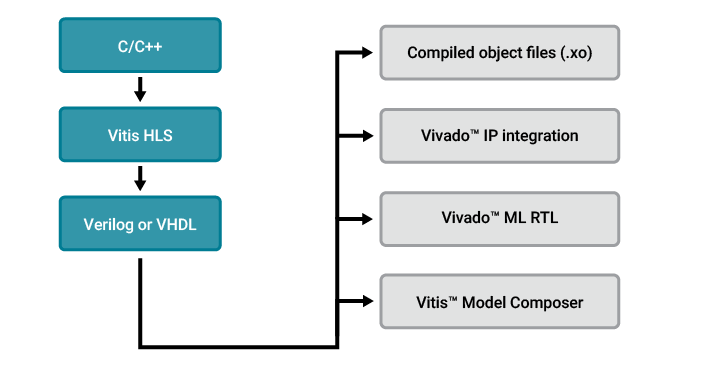

IP エクスポート

Vitis HLS ツールの出力は、コンパイル済みのオブジェクト ファイル (.xo) にパッケージ化、または RTL IP にエクスポート可能な RTL インプリメンテーションです。

- コンパイル済みのオブジェクト ファイル (.xo) を使用して、Vitis アプリケーション開発フローで使用するためのハードウェア アクセラレーション関数を作成する。

- 次の 3 つ方法で RTL IP を使用可能。

- Vivado™ IP インテグレーター ツールを使用して追加

- Vivado IDE で RTL ブロックとしてインポート

- DSP アプリケーションでは、Vitis Model Composer でシングル ブロックセットとして使用

最新情報

- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

2025.2 リリースのハイライト

- パフォーマンス プラグマの強化

- パフォーマンス プラグマが、CSIM で算出されたトリップカウントに基づいて最適化される

- パフォーマンス プラグマの最適化は、コンフィギュレーション ファイル内のディレクティブに変換可能

- プラグマの条件付き制御 (パフォーマンス プラグマを含む)

- 新しい IP サポート

- FIR/FFT でフラクショナル レート SSR に対応 (FFT は SPFP32 SSR = 最大 64 までサポート)

- ECC を備えたデータフロー バッファーを、ブロック RAM または UltraRAM で実装可能

- 使いやすさが向上

- CSIM および CoSim の自動再起動をサポート

- M-AXI 用マルチ ポート キャッシュ

- 側帯波信号に対応する AXI ストリーム用の新しい API

2025.1 リリースのハイライト

- HDL Coder と MATLAB R2025a を使用して、MATLAB (.m) デザインから Vitis HLS 向けの C++ コードを生成

- 使いやすさを追求した Vitis HLS の新機能

- 実行中に変化するワイヤ入力や AXI Lite 入力のモデリングに対応 (Direct I/O)

- トップレベル HLS デザイン向け性能最適化プラグマ (オープン EA)

- 専用の組込みライブラリを介した Versal 複素乗算器のサポート

- Vitis HLS GUI の改善

- Clang 16 による C++17 の初期サポート

2024.2 リリースのハイライト

Vitis HLS バージョン 2024.2 には、HLS デザインの開発およびデバッグを支援する多数の機能が追加されています。

- 実行中に変化するスカラー/ワイヤ入力のモデリング (ダイレクト I/O)

- 任意精度の浮動小数点型をサポート

- HLS コードの DSP ブロックへのマッピング

- ユーザーが任意に決定できるコード実行シーケンス

- データ型をわかりやすく表示する HLS デバッガー (GNU デバッガーの Pretty Print 技術を使用)

2024.1 リリースのハイライト

- 新しいステンシル プラグマにより、イメージおよびビデオ フィルター用の HLS C++ コードが簡素化

新しいライブラリ関数ウィザードで AMD Vitis ライブラリの GitHub リポジトリを利用可能

- AMD Vivado 設計ツール用の Solver および Vision (OpenCV 互換) IP を作成

- ライブラリ サンプルを実行

AMD Vivado IP インテグレーターでメモリ インターフェイスのプラグマ (ap_memory) を使用してポートをバンドル可能

新しい HLS コンポーネント比較機能では、2 つ以上のコンポーネントのメトリクスを並べて表示可能

ユーザーが提供する RTL コードで C++ 関数を置き換えることが可能 (ブラック ボックス フロー)

コード アナライザー機能では、C++ の構造体を細分化して解析し、パフォーマンスを微調整可能

HLS グローバル FSM エンコーディングやセーフ ステートの選択をユーザーが制御可能

C シミュレーション時に Clang サニタイザーを利用してアドレスや初期化をチェック

2023.2 リリースのハイライト

- HLS コンポーネント対応の新しい Vitis™ Unified IDE

- 新しい Vitis HLS ライセンス要件

- C 合成前の性能を予測する新しいコード アナライザー機能

- AXI インターフェイスが強化:

- HLS AXI ストリームのサイドチャネルに対応

- AXI マスターのキャッシングをユーザーが設定可能

- その他の機能強化:

- 新しいコード複雑度レポートで、C 合成中にデザイン サイズの問題を特定可能

- コンパイル時間の改善: 2023.2 バージョンでは、2023.1 と比較して平均で約 20% のコンパイル時間を短縮できる1

2023.1 リリースのハイライト

- 性能向上2: 2023.1 では 2022.2 よりも平均 5.2% のレイテンシが向上

- Vitis HLS ツールで L1 ライブラリ関数を簡単にダウンロード、表示、インスタンシエート可能。ビデオを視聴

- Vitis HLS ツールでの AXI トランザクションとバースト レポート機能のサポートが強化

2022.2 リリースのハイライト

- データ処理アプリケーション向けにタスクレベルの並列処理コードを記述するための新しい方法

- 新しい hls::task を使用することで、タスクレベルの並列処理を明示的に定義できる

- 純粋なストリーミング デザイン (パケット交換など) のモデル化が容易

- 性能とタイミングが向上

- Unroll、Pipeline、Array_Partition、inline の各プラグマを自動で推論し、パフォーマンスを向上させる

- 解析およびデバッグが強化

- 生成された RTL コードに C ソースの print ステートメントを合成する新機能

- RTL シミュレーションでコード ブロックの実行および変数の値をトレースできる

- 使いやすさ向上

- FFT および FIR IP で HLS::stream インターフェイスがサポートされる

2022.1 リリースのハイライト

- 新しいタイムライン トレース ビューアー

- デザインに含まれるすべての生存関数 (モジュール化された関数など) のランタイム プロファイルを表示

- 特に、協調シミュレーション後にデータフロー領域のビヘイビアーを確認するのに便利Vitis™ HLS にネイティブ対応 - XSIM 波形ビューアーの起動が不要になった

- 新しいパフォーマンス プラグマ

- スループット目標を #pragma hls performance で指定する

- 最小限のリソースで要件を満たすように模索する

- 実行された変換を示す。目標を達成できない場合は、その制限要因を示す

- ストリーム オブ ブロック タイプで Array Partition をサポート

- hls::stream の強化 (各要素は配列)

- 大規模な配列処理を小さく分割してパイプライン処理可能

2021.2 リリースのハイライト

- ユーザー制御のバースト推論

- 新たに手動のバースト最適化機能を利用可能

- バースト動作を手動で制御するために新しいクラスの「hls::burst_maxi」が追加。これに伴い、新しい HLS API を提供

- ユーザーは、HLS デザインの AXI AMBA プロトコルおよびハードウェア トランザクション レベル モデリングについて理解している必要がある

- タイミングおよび QoR の機能強化:

- HLS のタイミング見積もり精度が向上。HLS がタイミング クロージャをレポートするときには、Vivado™ の RTL 合成でもタイミングを満たしている

- EoU の機能強化

- C 合成レポートにインターフェイス アダプター レポートを追加

- インターフェイス アダプターがデザインに与えるリソース インパクトについて、ユーザーが把握する必要がある

- インターフェイス アダプターにはデザインの QoR に影響を与える可変のプロパティがある

- 合成レポートに新しいセクションが追加され、プラグマ リストとプラグマに関する警告を表示

- 解析およびレポート機能の強化

- マウス ドラッグによる拡大/縮小機能

- グラフ全体を表示し、部分的に拡大表示できる Overview 機能

- シミュレーション データと共にすべての関数とループが表示される

- シミュレーション後に Timeline Trace ビューアーが利用可能になりました。このビューアーでデザインのランタイム プロファイルを表示できます。ユーザーは Vitis HLS GUI からそのままアクセス可能です。

2021.1 リリースのハイライト

- フローのフェーズやレポートにすばやくアクセスできる新しい Flow Navigator GUI 合成、解析、デバッグの各ビューを一般的なデフォルト コンテキストに統合

- BIND_OP および BIND_STORAGE ディレクティブ用の新しい合成レポート セクション

- 合成後の新しいテキスト レポートには、GUI 合成レポートに提供される情報が反映される

- IP エクスポートや Vivado™ インプリメンテーション run のウィジェットが新しくなり、設定ファイルや制約ファイルを Vivado へ渡すオプションが追加されている

- 関数やループを可視化するための新しい関数呼び出しグラフ ビューアーでは、II、レイテンシ、DSP/BRAM の使用率をオプションのヒートマップでハイライトできる

- DSP ブロックのネイティブ浮動小数点演算用に Versal™ タイミング キャリブレーションと新しい制御機能 (config_op の -precision オプション)

- 代替のフラッシュ可能なパイプライン オプションが改善 (フリーランニング パイプライン、通称 「frp」)

- Vitis では、m_axi インターフェイスの再形成を hls::vector 型で実行する必要がある

- s_axilite および m_axi データ ストレージ用の新たなカスタマイズ オプション ("auto"、"uram"、"bram"、"lutram") を使用して、デザイン内の RAM 使用率を微調整できる

- Vitis では、カーネル用に継続的に動作する新モードをサポート (つまり「終わらない」)

- セカンダリ クロック オプションの axi_lite が再び利用可能に

採用事例

Vitis HLS カスタマー成功事例: Intuitive Surgical 社

外科用ロボットの世界的リーダーである Intuitive Surgical 社では、高性能な画像処理要件の一部を満たすために FPGA を活用しています。

同社がプロトタイプ開発で必要としていた機能のひとつが、4K 解像度で 60FPS に対応した画像ワーピング処理でした。この設計には厳しいレイテンシ要件があり、かつ開発期間も限られていたことから、Vitis HLS を用いて実装することを決定しました。コードは AMD の Vitis HLS チームによる技術サポートを受けながら、一から開発されました。設計期間は約 2 週間で、目標としていた性能も達成されました。

「画像ワーピングは FPGA 上での実装が非常に複雑で、RTL で開発する場合は数か月かかることもあります。Vitis HLS を利用することで、設計を短期間で実現できました。最適化の余地は残っていたものの、ここまで迅速にプロトタイプを完成できたのは驚くべきことであり、HLS のメリットを実感する結果となりました。この手法により迅速な反復開発が可能となり、AMD の HLS チームの支援やプラグマの調整を通じて、デザインをこれまでにないスピードで FPGA SoC 上で動作させることができました。弊社ではこれまでも画像処理機能に HLS を活用しており、今後も継続して活用していく予定です。」

- Azhar Sufi、Intuitive Surgical 社ファームウェア イメージング部門シニア マネージャー

Vitis HLS で効率的に設計空間を探索

「AMD Vitis™ HLS ツールを使用する主な利点は、設計空間を探索する機能だと思います。最適化指示子 (パイプライン、アンローリングなど) を使用することで、さまざまなアーキテクチャや実装を短時間で生成できますVHDL/Verilog を使用して手動でコーディングする場合には到底不可能な作業です。Vitis HLS では、HDL コードの協調シミュレーションを実行して HDL コードが機能的に正しいことを検証できることが魅力の一つです。」Dr. Frank Kesel - プフォルツハイム大学教授 (ドイツ)

ケース スタディ

リソース

脚注

- 2023 年 8 月 10 日に実施したテストに基づいています。このテストでは、Vitis HLS のリリース 2023.2 と 2023.1 を使用して、Vitis L2/L3 コード ライブラリ デザイン 1000 個を対象に比較しました。テスト システムは、Intel Xeon E5-2690 v4 @ 2.6 GHz CPU、256 GB RAM、RedHat Enterprise Linux 8.6 で構成されています。実際のパフォーマンスは異なる可能性があります。システム メーカーの構成によって、異なる結果が生じる場合があります。-VGL-04

- 2023 年 2 月 12 日時点で存在する 1208 個すべての Vitis L1 ライブラリの C コード デザインに対してベンチマーク テストを実施しました。すべてのデザインは、CentOS Linux を搭載した 2 つの Intel Xeon E5-2690 CPU を使用し、SMT が有効で Turbo Boost が無効に設定されたシステムを使用して実行しました。ハードウェアの構成がソフトウェアのテスト結果に影響を与えることはないと考えます。ソフトウェアやファームウェアの設定や構成によって結果が異なる可能性があります - VGL-03

- 2023 年 8 月 10 日に実施したテストに基づいています。このテストでは、Vitis HLS のリリース 2023.2 と 2023.1 を使用して、Vitis L2/L3 コード ライブラリ デザイン 1000 個を対象に比較しました。テスト システムは、Intel Xeon E5-2690 v4 @ 2.6 GHz CPU、256 GB RAM、RedHat Enterprise Linux 8.6 で構成されています。実際のパフォーマンスは異なる可能性があります。システム メーカーの構成によって、異なる結果が生じる場合があります。-VGL-04

- 2023 年 2 月 12 日時点で存在する 1208 個すべての Vitis L1 ライブラリの C コード デザインに対してベンチマーク テストを実施しました。すべてのデザインは、CentOS Linux を搭載した 2 つの Intel Xeon E5-2690 CPU を使用し、SMT が有効で Turbo Boost が無効に設定されたシステムを使用して実行しました。ハードウェアの構成がソフトウェアのテスト結果に影響を与えることはないと考えます。ソフトウェアやファームウェアの設定や構成によって結果が異なる可能性があります - VGL-03