개요

직관적인 설계 및 생산성을 위한 AMD Vitis™ HLS

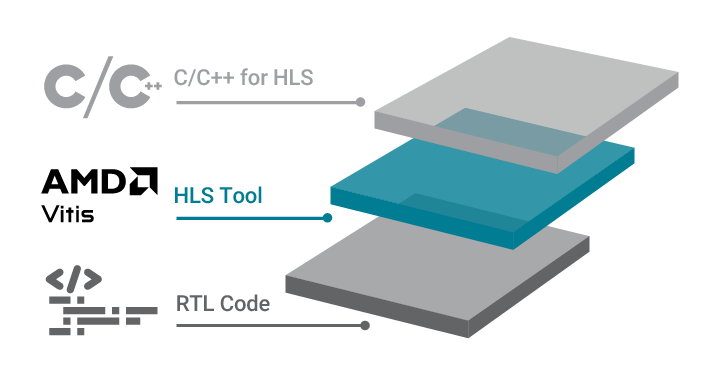

AMD Vitis™ HLS 도구를 사용하면 C/C++ 함수를 RTL로 합성하여 복잡한 FPGA 알고리즘을 쉽게 만들 수 있습니다. Vitis HLS 도구는 합성 및 배치/경로를 위한 Vivado™ Design Suite와 이종 시스템 설계 및 애플리케이션을 위한 Vitis™ 통합 소프트웨어 플랫폼과 긴밀히 통합되어 있습니다.

- 사용자는 Vitis HLS 흐름을 사용하여 C 코드에 지시문을 적용함으로써 원하는 구현에 맞는 RTL을 만들 수 있습니다.

- C 소스 코드에서 여러 설계 아키텍처를 만들 수 있으며 고품질의 CbC(Correct-by-Construction) RTL 경로가 활성화됩니다.

- C 시뮬레이션은 설계를 검증하는 데 사용할 수 있으며 기존의 RTL 기반 시뮬레이션보다 더 빠른 반복이 가능합니다.

- Vitis HLS 도구는 설계 최적화를 용이하게 하는 다양한 분석 및 디버깅 도구 세트를 갖추고 있습니다.

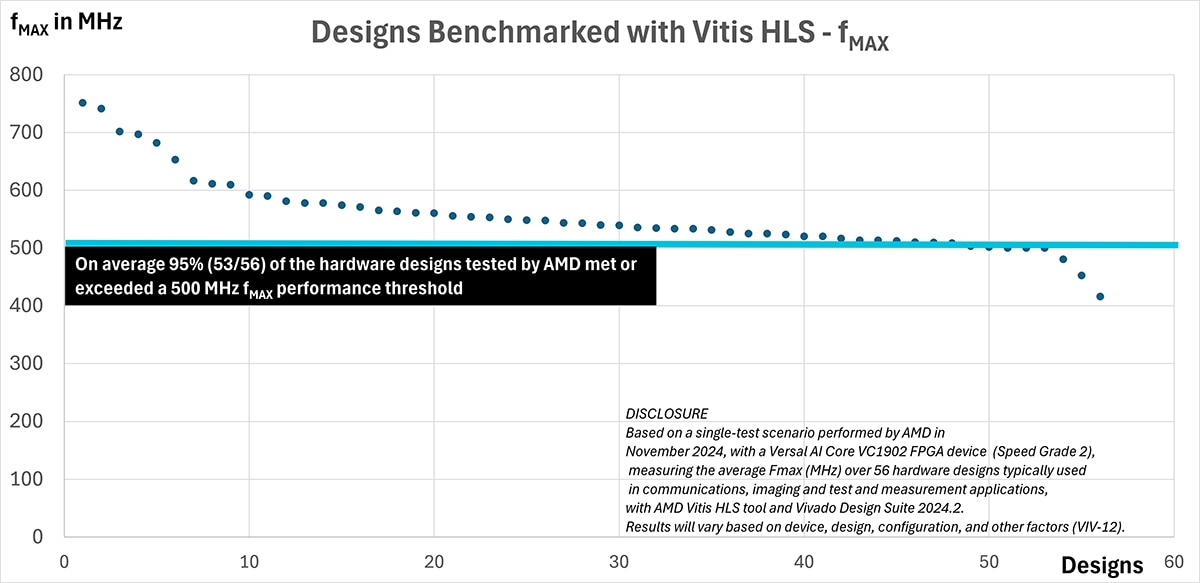

AMD Vitis™ HLS 성능 Pragma

AMD Vitis HLS는 높은 QoR을 달성하는 데 도움이 되는 최고 수준의 새로운 성능 pragma를 제공합니다. 이 새로운 기능을 사용하는 방법에 대한 자세한 내용은 기술 모듈을 참조하세요.

설계 방법론

Vitis HLS 프로그래밍 모델

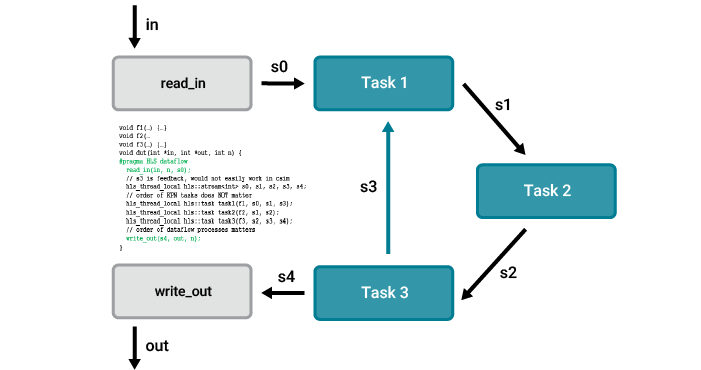

Vitis HLS C 코드는 AMD 적응형 SoC 및 FPGA 아키텍처가 제공하는 이점과 특성을 활용하는 데 중점을 두고 있습니다.

Vitis HLS 도구는 원하는 구현을 모델링하기 위해 병렬 프로그래밍 구조를 지원합니다. 해당 구조는 다음과 같습니다.

- 프로세스 수준 동시성을 허용하는 HLS 작업

- 데이터 수준 병렬화를 허용하는 HLS 벡터

- 동시 작업 간의 통신을 허용하는 HLS 스트림

- 결과를 통제하기 위해 합성 pragma를 사용할 수 있습니다. 이러한 pragma에는 파이프라인, 언롤, 어레이 분할 및 인터페이스 프로토콜이 포함됩니다.

- 자세한 내용은 Vitis HLS(High-Level Synthesis) 사용자 가이드의 "HLS 프로그래머 가이드" 섹션을 참조하세요.

MATLAB에서 HLS C++로 코드 생성

MATLAB®에서 개발된 기능은 MATLAB R2025a에서 제공되는 MathWorks HDL 코더의 코드 생성 기능을 통해 AMD Vitis™ HLS 친화적 C++ 코드로 합성할 수 있습니다.

이렇게 생성된 합성 가능한 C++ 코드는 Vitis™ HLS에 대한 입력으로 사용할 수 있습니다. 이 워크플로는 높은 수준의 알고리즘 설계(일반적으로 MATLAB에서 수행됨)에서 낮은 수준의 RTL 구현으로 번역 프로세스를 신속하게 처리할 수 있습니다.

MATLAB 및 HDL 코더를 사용하여 테스트 벤치를 설계 및 생성한 다음 HDL 코더의 코드 생성 기능을 사용하여 AMD 적응형 SoC 및 FPGA에서 시뮬레이션 및 합성을 위해 Vitis HLS에 입력하면 됩니다.

자세한 내용은 MathWorks HDL Coder 페이지를 참조하세요.

C-RTL 변환

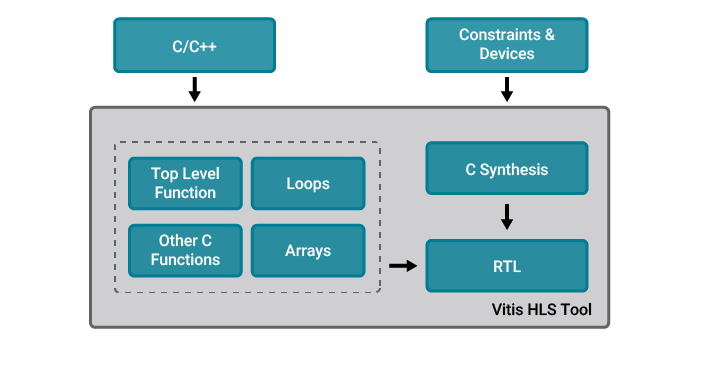

Vitis HLS 도구는 C 코드의 다양한 부분을 다르게 합성합니다.

- C/C++ 코드의 최상위 함수 인수는 RTL I/O 포트로 합성되며 인터페이스 합성 하드웨어 프로토콜로 자동 구현됩니다.

- 기타 C 함수는 RTL 블록으로 합성되어 설계 계층 구조를 유지합니다.

- C 함수 루프는 성능 향상을 위해 롤링 또는 파이프라인 방식으로 유지됩니다.

- C 코드의 어레이는 BRAM, LUTRAM 및 URAM과 같은 모든 메모리 리소스를 타겟팅할 수 있습니다.

- 지연율, 시작 간격, 루프 반복 지연율 리소스 사용률 등의 성능 지표는 합성 보고서를 통해 검토할 수 있습니다.

- Vitis HLS 도구 pragma와 최적화 지시문을 사용하면 C/C++ 코드에 대한 합성 결과를 구성할 수 있습니다.

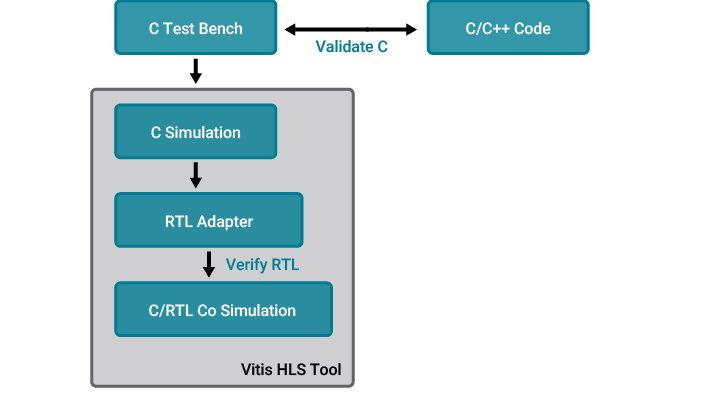

시뮬레이션 및 검증

Vtis HLS 도구는 시뮬레이션 흐름이 내장되어 있어 검증 시간을 단축할 수 있습니다.

- C 시뮬레이션은 C 코드의 기능을 검증합니다. 이 단계는 빠르게 진행되며 C 테스트 벤치를 사용합니다.

- C/RTL 공동 시뮬레이션은 C 테스트 벤치를 재사용해 생성된 RTL에 대한 검증을 수행하여 RTL이 C 소스 코드와 기능적으로 동일한지 확인합니다.

- 이 흐름에는 통합 분석, 디버그, 파형 보기 기능은 물론 인기 시뮬레이터 지원도 포함되어 있습니다.

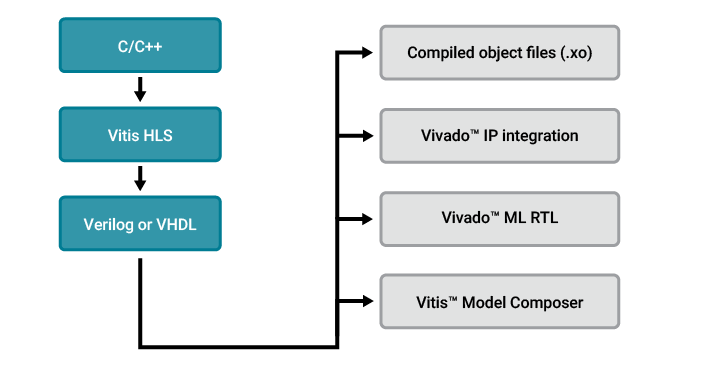

IP 내보내기

Vitis HLS 도구의 출력은 컴파일된 객체 파일(.xo)로 패키징하거나 RTL IP로 내보낼 수 있는 RTL 구현입니다.

- 컴파일된 객체 파일(.xo)은 Vitis 애플리케이션 개발 흐름에서 사용할 하드웨어 가속 함수를 만드는 데 사용됩니다.

- RTL IP는 세 가지 방법으로 사용할 수 있습니다.

- Vivado™ IP Integrator 도구를 사용하여 추가

- Vivado IDE에서 RTL 블록으로 가져옴

- DSP 애플리케이션용 Vitis 모델 컴포저에서 단일 블록 세트로 사용

새로워진 사항

- 2025.2

- 2025.1

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

2025.2 릴리스 하이라이트

- 성능 Pragma 개선 사항

- 이제 성능 Pragma를 CSIM이 계산한 트립 수를 기준으로 최적화

- 성능 Pragma 최적화를 구성 파일의 지시어로 변환 가능

- 성능 Pragma를 포함한 Pragma에 대한 조건부 제어

- 새로운 IP 지원

- FIR 및 FFT에 대한 분수 속도 SSR - FFT의 경우 SPFP32의 SSR이 이제 SSR=64까지 지원합니다.

- 블록 RAM 또는 UltraRAM으로 구현된 데이터 흐름 버퍼에 대한 ECC 지원

- 사용 편의성 기능

- CSIM 및 CoSim에서 자동 재시작 지원

- M-AXI용 멀티 포트 캐시

- 사이드밴드 신호를 사용하는 AXI 스트림을 위한 새로운 API

2025.1 릴리스 하이라이트

- HDL 코더 및 MATLAB R2025a를 사용하여 MATLAB(.m) 설계에서 Vitis HLS 친화적 C++ 코드 생성

- 새로운 Vitis HLS 사용 편의성 기능

- 실행 중 변경되는 와이어 입력 및 AXI Lite 입력 모델링(직접 I/O)

- 최상위 HLS 설계를 위한 Performance pragma(얼리 액세스 공개)

- 전용 내장 라이브러리를 통한 Versal Complex Multiplier 지원

- Vitis HLS GUI 개선 사항

- Clang 16을 통한 초기 C++ 17 지원

2024.2 릴리스 하이라이트

Vitis HLS 버전 2024.2에는 사용자가 HLS 설계를 더욱 쉽게 개발하고 디버깅할 수 있도록 지원하는 다음과 같은 여러 기능이 포함되어 있습니다.

- 실행 중 변경되는 스칼라/와이어 입력 모델링(직접 I/O)

- 임의 정밀도 부동 소수점 유형 지원

- DSP 블록에 HLS 코드 매핑

- 사용자가 결정하는 코드 실행 순서

- 사용자 친화적인 방식으로 데이터 형식을 보여 주는 HLS 디버거(GNU 디버거의 자동 서식 지정 기술 사용)

2024.1 릴리스 하이라이트

- 새로운 스텐실 pragma가 이미지 및 비디오 필터용 HLS C++ 코드를 단순화

새로운 라이브러리 함수 마법사가 AMD Vitis 라이브러리 GitHub 리포지토리 활용

- AMD Vivado 설계 도구용 "Solver" 및 "Vision"(OpenCV 호환) IP 생성

- 사용 가능한 라이브러리 예제 실행

메모리 인터페이스용 pragma(ap_memory)가 이제 AMD Vivado IP Integrator용 포트를 번들로 구성 가능

새로운 HLS 구성 요소 비교에서는 2개 이상의 구성 요소에 대한 지표가 나란히 표시됨

C++ 함수를 대체하는 사용자-공급자 RTL 코드 지원(블랙박스 흐름)

코드 분석기가 이제 C++ 구조체 멤버를 분해하여 성능 분석을 미세 조정 가능

HLS 전역 FSM 인코딩 및 안전 상태 선택을 위한 새로운 사용자 컨트롤

C 시뮬레이션 중 Clang 새니타이저에 액세스하여 주소 및 초기화 검사 수행

2023.2 릴리스 하이라이트

- HLS 구성 요소를 위한 새로운 Vitis™ 통합 IDE

- 새로운 Vitis HLS 라이선스 요구 사항

- C 합성을 실행하기 전에 성능 추정치를 얻기 위한 새로운 코드 분석기 기능

- AXI 인터페이스 개선 사항:

- HLS AXI 스트림 사이드 채널 지원 개선 사항

- 사용자 구성 가능 AXI 마스터 캐싱 지원

- 기타 개선 사항:

- C 합성 중에 설계 크기 문제를 식별할 수 있는 새로운 코드 복잡성 보고서

- 컴파일 시간 개선: 2023.1에 비해 2023.2에서 평균 컴파일 시간 20% 개선1

2023.1 릴리스 하이라이트

- 성능 개선 사항2: 2022.2에 비해 2023.1에서 평균 지연율 5.2% 개선

- Vitis HLS 도구에서 L1 라이브러리 함수를 쉽게 다운로드, 확인, 인스턴스화하는 쉬운 방법. 동영상 시청하기

- Vitis HLS 도구 내에서 AXI 트랜잭션 및 버스트 보고에 대한 지원 강화

2022.2 릴리스 하이라이트

- 데이터 처리 애플리케이션을 위한 "태스크 수준 병렬" 코드를 작성하는 새로운 방법

- 사용자가 새로운 hls::task 함수를 사용하여 태스크 수준 병렬성을 명시적으로 정의 가능

- 순수 스트리밍 설계(예: 패킷 스위칭)를 위한 모델링이 용이함

- 성능 및 타이밍 개선 사항

- 성능 향상을 위해 도구가 자동으로 언롤, 파이프라인, 어레이 분할 및 인라인 pragma를 추론

- 분석 및 디버그 개선 사항

- 생성된 RTL 코드에서 C 소스의 print 문을 합성하는 새로운 기능

- RTL이 시뮬레이션되면 코드 블록의 실행과 변수 값을 추적 가능

- 사용 편의성

- 이제 FFT 및 FIR IP에 대한 hls::stream 인터페이스 지원

2022.1 릴리스 하이라이트

- 새로운 타임라인 추적 뷰어

- 설계에 남아 있는 모든 함수(모듈로 변환된 함수)의 런타임 프로파일 표시

- 공동 시뮬레이션 후 데이터 흐름 영역의 동작을 확인하는 데 특히 유용 Vitis™ HLS에 기본 제공 - 더는 xsim 파형 뷰어를 실행할 필요 없음

- 새로운 성능 pragma

- #pragma hls performance를 사용하여 처리율 목표 HLS

- HLS는 가능한 한 최소한의 리소스를 사용하여 목표 달성 시도

- HLS는 수행된 변환을 나타내며, 목표를 달성할 수 없는 경우 제한 요인을 표시

- 블록 스트림 유형에 대한 어레이 분할 지원

- 각 요소가 어레이인 hls::stream 개선

- 대규모 어레이 처리를 더 작고 파이프라인화된 부분으로 나누는 데 사용 가능

2021.2 릴리스 하이라이트

- 사용자 제어 버스트 추론

- 사용자가 새로 도입된 수동 버스트 최적화 채택 가능

- 버스트 동작 수동 제어를 지원하도록 새로운 클래스 'hls::burst_maxi' 추가. 새로운 클래스와 함께 사용할 수 있도록 새로운 HLS API 제공

- 사용자는 AXI AMBA 프로토콜과 HLS 설계의 하드웨어 트랜잭션 수준 모델링 이해 필요

- 타이밍 및 QoR 개선 사항

- HLS 타이밍 추정 정확도 향상. HLS가 타이밍 종결을 보고할 때 Vivado™ RTL 합성도 타이밍을 충족할 것으로 예상

- EoU 개선 사항

- C 합성 보고서에 인터페이스 어댑터 보고서 추가

- 사용자는 인터페이스 어댑터가 설계에 미치는 리소스 영향을 알아야 합니다.

- 인터페이스 어댑터에는 설계 QoR에 영향을 주는 가변 속성이 있습니다.

- pragma 및 pragma에 대한 경고 목록을 표시하기 위해 합성 보고서에 새 섹션 추가

- 분석 및 보고 개선 사항

- 새로운 마우스 드래그 기반 확대 및 축소 기능

- 전체 그래프를 표시하고 전체 그래프의 일부를 사용자가 확대할 수 있는 새로운 개요 기능

- 모든 함수와 루프가 해당 시뮬레이션 데이터와 함께 표시됨

- 이제 시뮬레이션 후 새로운 Timeline Trace Viewer(타임라인 추적 뷰어)를 사용할 수 있습니다. 이 뷰어는 설계의 런타임 프로파일을 보여주며, 사용자는 Vitis HLS GUI에서 작업을 계속할 수 있습니다.

2021.1 릴리스 하이라이트

- GUI의 새로운 "Flow Navigator"를 통해 흐름 단계 및 보고서에 빠르게 액세스. 컨텍스트별 "합성, 분석, 디버그" 보기를 일반 기본 컨텍스트로 병합

- BIND_OP 및 BIND_STORAGE 지시문에 대한 새로운 합성 보고서 섹션

- 새로운 합성 후 텍스트 보고서는 GUI 합성 보고서에 제공된 정보를 반영

- IP 내보내기 및 Vivado™ 구현 실행 위젯은 설정 및 제약 조건 파일을 Vivado로 전달하는 옵션으로 재설계됨

- II, 지연율 또는 DSP/BRAM 사용률 핫스팟을 감지하기 위한 선택적 히트맵으로 강조 표시할 수 있는 함수와 루프를 시각화하는 새로운 함수 호출 그래프 뷰어

- DSP 블록 네이티브 부동 소수점 연산에 대한 Versal™ 타이밍 보정 및 새로운 컨트롤(config_op의 -precision 옵션)

- 대체 플러시 가능 파이프라인 옵션 개선(FRP(Free Running Pipeline))

- Vitis에서 m_axi 인터페이스 재구성은 hls::vector 유형을 통해 수행되어야 함

- "auto, "uram", "bram" 또는 "lutram"일 수 있는 s_axilite 및 m_axi 데이터 스토리지에 대한 새로운 맞춤화 옵션을 통해 설계에서 RAM 사용률 조정 가능

- Vitis에서는 커널을 위한 새로운 연속("무한") 실행 모드 도입

- axi_lite 보조 클럭 옵션 복구

성공 스토리

Vitis HLS 고객 성공 사례: Intuitive Surgical

수술용 로봇 분야의 세계적인 선두 업체인 Intuitive Surgical은 FPGA를 사용하여 일부 고성능 이미징 요구 사항을 구현합니다.

프로토타입을 제작하는 데 필요한 기능 중 하나는 초당 60프레임(FPS)의 4K 해상도를 위한 이미지 워핑 기능이었습니다. 설계에는 엄격한 지연율 요구 사항이 있었습니다. Intuitive Surgical은 시간 제약으로 인해 Vitis HLS를 사용하여 이 기능을 구현하기로 결정했습니다. 이 코드는 AMD Vitis HLS 팀의 기술 지원을 통해 완전히 새롭게 개발되었습니다. 전체 설계 프로세스는 약 2주가 걸렸으며 성능 목표가 달성되었습니다.

"이미지 워핑은 FPGA에서 복잡한 작업이며 RTL을 사용하여 구현할 경우 몇 개월이 소요될 수 있습니다. Vitis HLS 기반 접근 방식을 통해 설계를 신속하게 구현할 수 있었습니다. 설계가 완전히 최적화되지는 않았지만 프로토타입 제작 속도는 놀라울 정도였고, HLS의 장점을 잘 보여 주었습니다. 이 방법은 빠른 반복에 도움이 되었고 AMD HLS 팀의 지원과 애플리케이션에 대한 조정으로 전례 없는 시간 내에 FPGA SoC에서 성공적으로 설계를 설정하고 실행할 수 있었습니다. 이미징 기능에 HLS를 활용해 왔고 앞으로도 계속 활용할 계획입니다."

- Azhar Sufi, Intuitive Surgical 펌웨어 - 이미징 선임 관리자

Vitis HLS로 더욱 빨라진 설계 공간 탐색

"AMD Vitis™ HLS 도구의 주요 장점은 설계 공간 탐색 기능인 것 같습니다. 최적화 지시문(파이프라이닝, 언롤링 등)을 사용하면 적절한 시간 내에 다양한 아키텍처와 구현을 생성할 수 있습니다. VHDL/Verilog를 사용하여 수동으로 코딩하는 경우에는 이 작업을 수행할 수 없습니다. Vitis HLS의 유용한 기능은 HDL 코드가 기능적으로 올바른지 확인하기 위해 HDL 코드의 공동 시뮬레이션과 검증을 수행할 수 있다는 것입니다." Frank Kesel 박사 - 독일 포르츠하임 대학교 교수

고객 사례 연구

리소스

각주

- 2023년 8월 10일, 1,000개의 Vitis L2/L3 코드 라이브러리 설계에 대해 Vitis HLS 릴리스 2023.2와 Vitis HLS 2023.1을 비교한 테스트를 기준으로 합니다. 테스트 중 시스템 구성: 인텔 제온 E5-2690 v4 @ 2.6GHz CPU, 256GB RAM, RedHat Enterprise Linux 8.6. 실제 성능은 다를 수 있습니다. 시스템 제조업체별 구성에 따라 다른 결과가 나올 수 있습니다. -VGL-04

- 벤치마크 테스트는 2023년 2월 12일 현재 1208개의 Vitis L1 라이브러리 C 코드 설계에 대해 수행되었습니다. 모든 설계는 CentOS Linux, SMT 활성화, 터보 부스트 비활성화 상태의 2P 인텔 제온 E5-2690 CPU를 탑재한 시스템을 사용하여 실행되었습니다. 하드웨어 구성은 소프트웨어 테스트 결과에 영향을 미치지 않을 것으로 예상됩니다. 결과는 소프트웨어 및 펌웨어 설정과 구성에 따라 달라질 수 있습니다.- VGL-03

- 2023년 8월 10일, 1,000개의 Vitis L2/L3 코드 라이브러리 설계에 대해 Vitis HLS 릴리스 2023.2와 Vitis HLS 2023.1을 비교한 테스트를 기준으로 합니다. 테스트 중 시스템 구성: 인텔 제온 E5-2690 v4 @ 2.6GHz CPU, 256GB RAM, RedHat Enterprise Linux 8.6. 실제 성능은 다를 수 있습니다. 시스템 제조업체별 구성에 따라 다른 결과가 나올 수 있습니다. -VGL-04

- 벤치마크 테스트는 2023년 2월 12일 현재 1208개의 Vitis L1 라이브러리 C 코드 설계에 대해 수행되었습니다. 모든 설계는 CentOS Linux, SMT 활성화, 터보 부스트 비활성화 상태의 2P 인텔 제온 E5-2690 CPU를 탑재한 시스템을 사용하여 실행되었습니다. 하드웨어 구성은 소프트웨어 테스트 결과에 영향을 미치지 않을 것으로 예상됩니다. 결과는 소프트웨어 및 펌웨어 설정과 구성에 따라 달라질 수 있습니다.- VGL-03