Programmable Logic

Unparalleled flexibility to build low-latency proprietary processing functions that can adapt with evolving and diverse algorithms.

Heterogeneous acceleration from cloud to edge

General-purpose Versal™ adaptive SoCs combine programmable logic with embedded Arm® application and real-time CPU cores, a programmable network on chip, high-speed serial transceivers, programmable I/O, and a broad offering of hard IP.

The Versal Prime Series features mid-range devices while the Versal Premium Series features high-end devices.

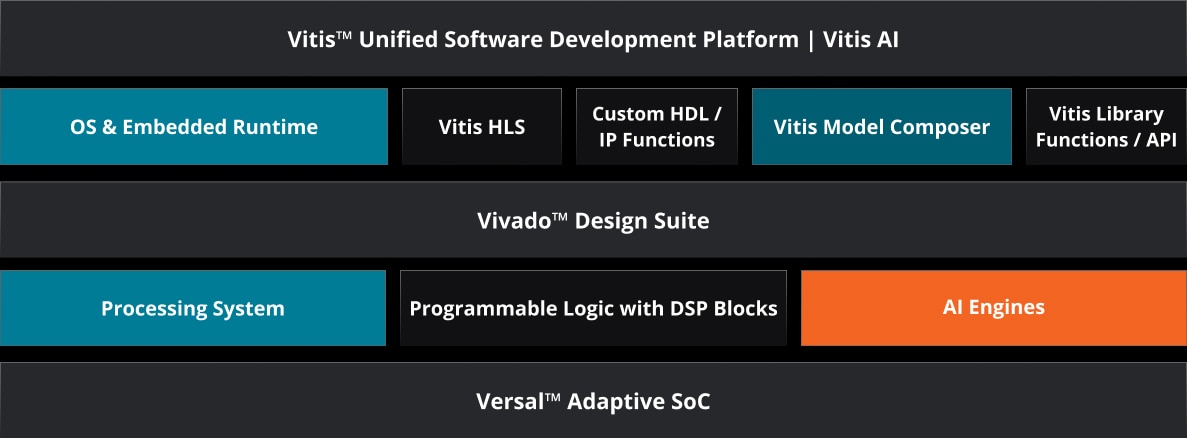

Specialized Versal adaptive SoCs supplement the base architecture from the general-purpose Versal portfolio with advanced capabilities such as AI Engines for both DSP and machine learning workloads, integrated RF-ADCs/RF-DACs, expanded DSP hard IP, or high-bandwidth memory.

AMD provides leadership software and hardware development environments for designing with adaptive SoCs and FPGAs, offering a comprehensive set of familiar and powerful tools, libraries, and methodologies.

This primarily includes the AMD Vivado™ Design Suite, which helps hardware designers reduce compile times and design iterations while more accurately estimating power. In addition, the AMD Vitis™ unified software platform enables building advanced, performance-optimized system designs (including high-performance DSP with AI Engine technology) using AMD adaptive SoCs and FPGAs, along with other tools (compilers, simulators, etc.), IP, and solutions.

These environments reduce development time while allowing developers to achieve high performance per watt. They also enable both automation and user control to all types of developers from AI scientists, application and algorithm engineers, embedded software developers, and traditional hardware developers.

Go to Vivado for Versal web page to learn more about the significant improvements made in the Vivado Design Suite.

Join the Versal portfolio notification list and be the first to receive updates.