Versal RF Series

Enables precise, wideband-spectrum observability with 18 GHz RF-ADCs and RF-DACs, providing up to 80 TOPS of DSP performance¹² in a SWaP-optimized design with commonly used DSP functions implemented as hard IP.

Performant. Predictable. Proven.

Accelerated by the demands for AI, the need for increased data processing and faster connectivity makes efficiency crucial to minimizing the delay from data to insights. The AMD adaptive SoC and FPGA portfolio has a proven track record and will help you meet your product goals through unparalleled system-level efficiencies and supply chain resiliency. Choose AMD and unlock the future of adaptive computing solutions.

AMD Versal™ adaptive SoCs help you innovate faster with advanced IP, modern tools, and powerful hardware.

The AMD global supply strategy delivers consistent products and short lead times.

AMD offers long-term stability, outstanding technical support, and a future-ready roadmap you can rely on.

AMD devices provide flexible connectivity, optimized system performance and efficiency, security, and reliability. Transform your next design with innovative solutions built around the AMD adaptive compute portfolio.

Enhance responsiveness, data processing, functional safety, and security in L2-L4 applications with AMD Versal AI Edge Series Gen 2 devices, which support a wide range of sensors, flexible real-time signal processing, and target 3X TOPS/W of AI inference performance vs. the 1st-generation Versal AI Edge Series.1

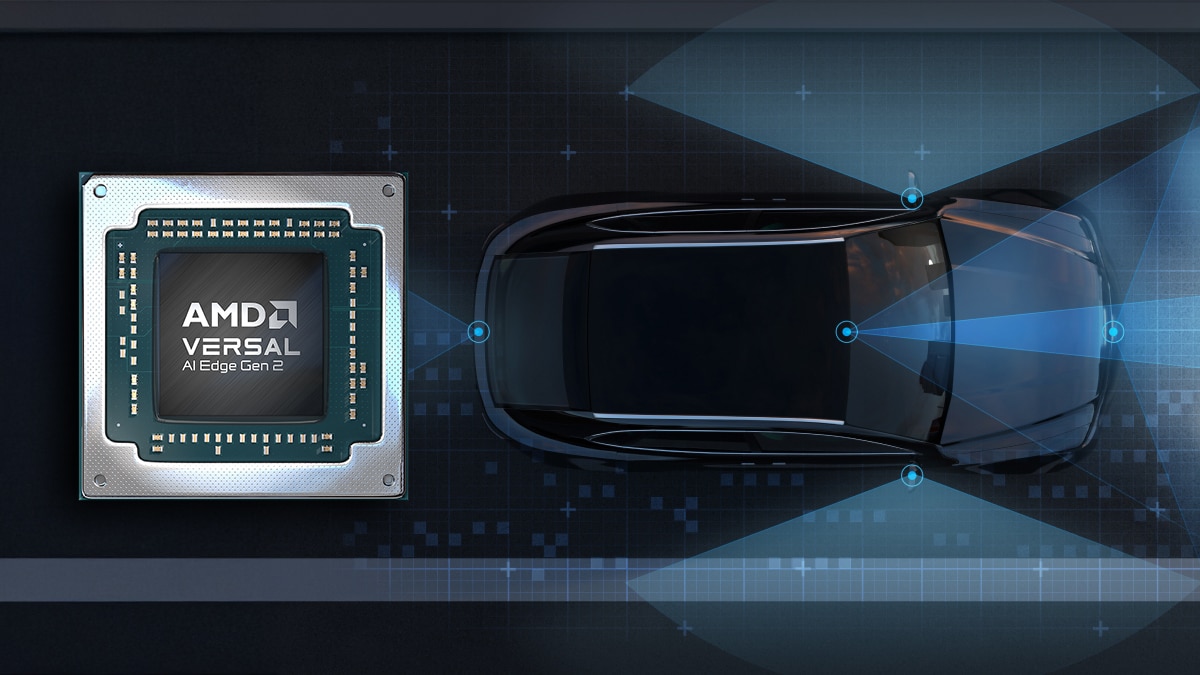

Modern RF applications require wide spectrum coverage, high sample rates with enhanced signal processing, and optimized SWaP. AMD Zynq™ UltraScale+™ RFSoC, Versal RF devices, and the Mercury Systems System-in-Package (SiP) cater to the full range of electromagnetic spectrum operations (EMSO).

In healthcare, applications demand quality, reliability, security, safety, and product longevity. With Versal AI Edge Series Gen 2 devices, you can build the next wave of products without compromise, unlocking critical insights and delivering transformational outcomes.

From capturing content to enabling virtual production and creating live events, the enhanced video and graphics capabilities of Versal Prime Series Gen 2 devices enable Broadcast and Pro AV equipment suppliers to deliver even more compelling experiences.

Safeguarding your product against an evolving threat landscape is essential. Modern designs must be resilient in the face of side-channel attacks, bitstream tampering, firmware manipulation, glitch attacks, and supply chain vulnerabilities.

To learn how AMD FPGAs and adaptive SoCs offer a comprehensive defense strategy, read our white paper. To view AMD security comparisons versus the competition, visit the AMD Security Lounge.

The AMD multi-faceted strategy embraces technological innovation, diversifies the supply chain, and enhances supply resiliency and agility.

The optimized hard IP in Versal adaptive SoCs results in higher system-level performance-per-watt.2 The AMD Versal RF Series offers 3X more compute per area compared to competing FPGAs.3 In addition, Versal AI Edge Series Gen 2 and Prime Series Gen 2 achieve 10X scalar compute and 3X TOPS/watt compared to previous generation architectures.1,4 Learn about the system-level benefits of the AMD Versal architecture and comparative performance to competing programmable-logic based devices in our white paper.

Build fast, efficient designs with the AMD Versal programmable NoC architecture.

AMD Versal adaptive SoCs support a fully programmable network on chip (NoC), implemented as hard IP, across the entire portfolio. Hardware designers can benefit from up to 58% lower write latency, up to a 60% reduction in logic utilization, and up to a 50% reduction in development time versus competing FPGAs using a soft IP solution.5,6,7 Developers who are new to the Versal programmable NoC should check out the NoC related videos which are part of the Vivado for Versal video series.

Innovative world-class AMD lidless packaging with stiffener ring technology reduces thermal resistance by up to 11X8 and helps lower power consumption. Reduce your product size and weight and support a wide ambient temperature range. With innovative packaging for thermal performance, AMD packaging tackles FPGA thermal demands in edge and high-performance deployments.

AMD Versal adaptive SoCs provide the fastest LPDDR5 memory connectivity,9 up to 2X faster secure data transactions versus competing FPGAs,10 and enhanced host connectivity. AMD Versal Premium Series Gen 2 offers the industry’s first adaptive SoC with PCIe® Gen 6 and CXL® 3.1, scaling data transfer rates to 64 Gb/s to support memory- and data-intensive workloads.11

AMD oversees the entire manufacturing supply chain, from raw materials to fabrication, and ensures that all suppliers adhere to high business continuity plan (BCP) standards. AMD delivers consistent product availability, predictable lead times, transparency, and reduced risk.

Together with our supply chain and industry partners, AMD embraces the opportunity to meet demand while driving social and environmental progress in the supply chain through supply chain responsibility. Discover the AMD approach to reducing global supply chain risk with agility and strategic foresight.

The AMD adaptive computing portfolio integrates security and reliability features to help ensure your designs will address the applications of tomorrow.

The Versal programmable NoC is available across the entire Versal portfolio and is designed to provide a high-bandwidth path for both vertical and horizontal traffic across the entire device.

AMD lidless packages with stiffener ring, combined with AMD etch patterns enable the development of optimum thermal solutions.

AMD minimizes risk through partnerships, geographically diverse manufacturing, and assurance programs across the entire supply chain.

Yes. Developers should review the AMD security white paper and then visit the lounge to learn more about the AMD advantage.

Developers should review the AMD Design Conversion for FPGAs and SoCs Methodology Guide and also assess the level of difficulty of conversion on a module-by-module basis. Critical functions that may require factory support can be upleveled through local support channels.

Tell us how we can help you make the easy switch to AMD.

Sign up for the latest product news.