Overview

With a streamlined design flow, Vivado Design Suite enables traditional FPGA developers to achieve design closure quickly with Versal adaptive SoCs

Meet FMAX Targets

New P&R and clocking algorithms let designers meet timing for the most complex designs.

Fast Compile & Flexible Boot

Reduce compile time1,2 and boot the PS first for fast design closure and system bring-up.

Top-Level RTL Flows

Use traditional RTL flows to unlock system performance on Versal devices.

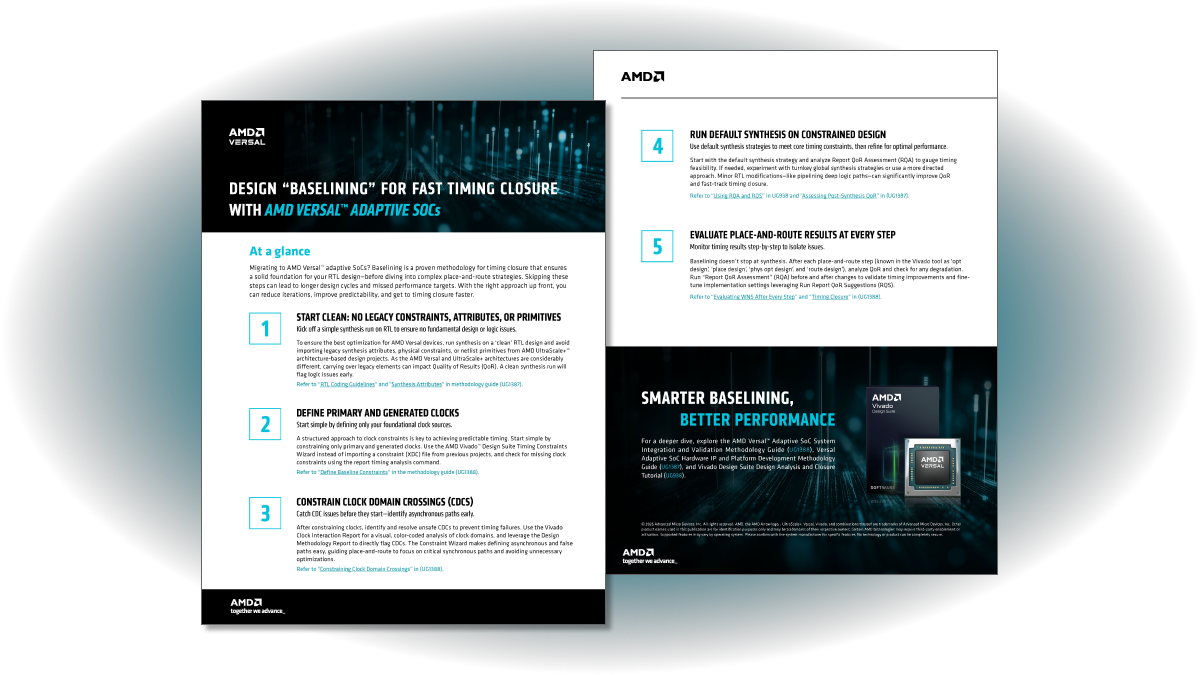

Improve Your Quality of Results with AMD Versal™ Adaptive SoCs

Vivado Enhancements for Versal

Average Performance Improvement Over 2024.1 3,4

Meet FMAX Targets

Versal™ adaptive SoCs enable a new paradigm of system design while building on proven FPGA methodologies. Capabilities within the Versal architecture and Vivado Design Suite to achieve timing closure include:

- Compilation flows that reduce routing congestion

- Auto-calibration of clock regions to minimize clock-skew

- New clock buffer technology for targeted skew reduction

- Enhanced die-to-die connectivity for SSIT-based devices

The latest enhancements in Vivado tools coupled with built-in silicon features enable both automation and user control to meet timing closure.

Compile Time Improvements1,2

Fast Compile

Versal™ adaptive SoCs provide greater logic resources and hard IP for more complex designs. But with increased complexity comes potentially long compile times. Vivado™ Design Suite now features the Advanced Flow to accelerate compilation by up to 2X over previous releases with enhancements at every implementation stage:

- Automatic partitioning for parallel place and route

- Smarter placement to reduce congestion

- Advanced routing algorithms for faster timing closure

Top-Level RTL Flows

With Versal adaptive SoCs, hardware developers can map their designs using a block-based system approach using IP Integrator or stay in their top-level RTL for ease of migration of previous generation FPGA designs using two new features:

- The modular NoC flow eases design entry by allowing instantiation via RTL and IP integrator environments using a system level approach.

- The new Versal transceivers wizard provides an RTL wrapper created around GT primitives and allows for basic customization.

While IP integrator is still leveraged for various IP blocks in the Versal adaptive SoC flow, the top-level RTL flow allows for flexibility of importing designs with complex topologies.

Flexible Processor Boot

The Vivado Design Suite provides options to configure the processing system to boot first for applications that need fast OS startup, strict power sequencing control, or dynamic reconfiguration of the PL without interrupting software runtime. The new Segmented Configuration flow:

- Boots processors, memory, and OS first

- Defers PL configuration to a later stage

- Delivers a PL PDI (config file) via Linux® or U-Boot at runtime

Segmented configuration is available in the 2025.1 release. Please refer to the GitHub tutorials for more details.

Resources

Webinars and How-To Videos

GitHub Tutorials

Training Courses

Documentation

Vivado Design Suite

Download the latest release of the Vivado Design Suite to access the latest features

Power Design Manager

Download the latest release to ensure accurate power data for UltraScale+ and Versal devices

Contact Us

Sign up to receive the latest news on hardware tools or get in touch with a Vivado Design Suite expert for questions or feedback

Footnotes

- Based on a single-test scenario performed by AMD in December 2024, measuring the average compile times (hours/minutes) over 124 designs targeting Versal Stacked Silicon Interconnect (SSI) technology devices using Vivado Design Suite 2024.2 vs. Vivado Design Suite 2024.1. Compile time results will vary based on device, design, configuration, and other factors (VIV-011)

- Based on a single-test scenario performed by AMD in December 2024, with measuring the average compile times (hours/minutes) over 151 designs targeting Versal monolithic devices using Vivado Design Suite 2024.2 vs. Vivado Design Suite 2024.1. Compile time results will vary based on device, design, configuration, and other factors. (VIV-010)

- Based on AMD worst negative slack performance testing in April 2025, using Vivado Design Suite 2024.2 vs. 2024.1. Stated results are a geomean average over 153 monolithic designs. Results may vary based on device, design, configuration, software, and other factors (VIV-013)

- Based on AMD worst negative slack performance testing in April 2025, using Vivado Design Suite 2024.2 vs. 2024.1. Stated results are a geomean average over 125 SSI designs. Results may vary based on device, design, configuration, software, and other factors (VIV-014)

- Based on a single-test scenario performed by AMD in December 2024, measuring the average compile times (hours/minutes) over 124 designs targeting Versal Stacked Silicon Interconnect (SSI) technology devices using Vivado Design Suite 2024.2 vs. Vivado Design Suite 2024.1. Compile time results will vary based on device, design, configuration, and other factors (VIV-011)

- Based on a single-test scenario performed by AMD in December 2024, with measuring the average compile times (hours/minutes) over 151 designs targeting Versal monolithic devices using Vivado Design Suite 2024.2 vs. Vivado Design Suite 2024.1. Compile time results will vary based on device, design, configuration, and other factors. (VIV-010)

- Based on AMD worst negative slack performance testing in April 2025, using Vivado Design Suite 2024.2 vs. 2024.1. Stated results are a geomean average over 153 monolithic designs. Results may vary based on device, design, configuration, software, and other factors (VIV-013)

- Based on AMD worst negative slack performance testing in April 2025, using Vivado Design Suite 2024.2 vs. 2024.1. Stated results are a geomean average over 125 SSI designs. Results may vary based on device, design, configuration, software, and other factors (VIV-014)