Descripción general

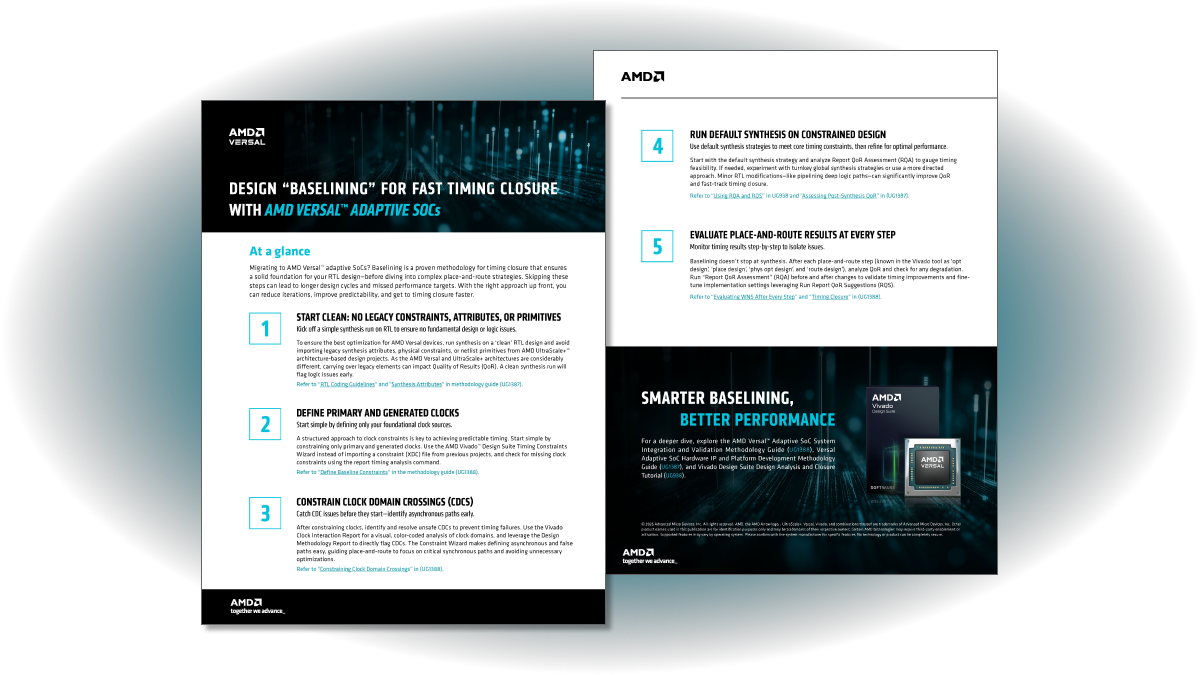

Con un flujo de diseño optimizado, Vivado Design Suite permite a los desarrolladores de FPGA tradicionales cerrar el diseño rápidamente con los SoC adaptables de Versal

Cumple los objetivos de FMAX

Los nuevos algoritmos de P&R y sincronización permiten a los diseñadores cumplir los plazos para los diseños más complejos.

Compilación rápida y arranque flexible

Reduce el tiempo de compilación1, 2 e inicia primero el sistema PS para cerrar rápidamente el diseño y poner en marcha el sistema.

Flujos RTL de nivel superior

Utiliza flujos RTL tradicionales para desbloquear el rendimiento del sistema en dispositivos Versal.

Mejora la calidad de los resultados con los SoC adaptables AMD Versal™

Mejoras de Vivado para Versal

Mejora promedio del rendimiento sobre 2024.1 3, 4

Cumple los objetivos de FMAX

Los SoC adaptables Versal™ permiten un nuevo paradigma de diseño de sistemas, a la vez que se basan en metodologías FPGA probadas. Las capacidades de la arquitectura Versal y Vivado Design Suite para lograr el cierre de temporización incluyen las siguientes:

- Flujos de compilación que reducen la congestión de enrutamiento

- Calibración automática de las regiones del reloj para minimizar la desviación del reloj

- Nueva tecnología de búfer de reloj para reducir la inclinación

- Conectividad de chip a chip mejorada para dispositivos basados en SSIT

Las últimas mejoras en las herramientas de Vivado, junto con las funciones de silicio integradas, permiten tanto la automatización como el control del usuario para cumplir con el cierre de temporización.

Mejoras en el tiempo de compilación1, 2

Compilación rápida

Los SoC adaptables Versal™ proporcionan mayores recursos lógicos y una IP sólida para diseños más complejos. Sin embargo, con una mayor complejidad, los tiempos de compilación son potencialmente largos. Vivado™ Design Suite ahora incluye Advanced Flow para acelerar la compilación hasta dos veces más con respecto a las versiones anteriores, con mejoras en cada fase de implementación:

- Partición automática para ubicación y ruta paralelas

- Colocación más inteligente para reducir la congestión

- Algoritmos de enrutamiento avanzados para un cierre de temporización más rápido

Flujos RTL de nivel superior

Con los SoC adaptables Versal, los desarrolladores de hardware pueden asignar sus diseños mediante un enfoque de sistema basado en bloques mediante el integrador de IP o permanecer en su RTL de nivel superior para facilitar la migración de diseños FPGA de la generación anterior mediante dos nuevas funciones:

- El flujo NoC (red en chip) modular facilita la entrada de diseños, ya que permite la creación de instancias a través de entornos de integración RTL e IP mediante un enfoque a nivel de sistema.

- El nuevo asistente de transceptores Versal proporciona un contenedor RTL creado alrededor de primitivos GT y permite una personalización básica.

Aunque el integrador de IP sigue aprovechando varios bloques IP en el flujo SoC adaptable de Versal, el flujo RTL de nivel superior permite la flexibilidad de importar diseños con topologías complejas.

Arranque flexible del procesador

Vivado Design Suite proporciona opciones para configurar el sistema de procesamiento a fin de que se inicie primero en aplicaciones que necesitan un inicio rápido del sistema operativo, un control estricto de la secuencia de alimentación o una reconfiguración dinámica del PL, sin interrumpir el tiempo de ejecución del software. El nuevo flujo de configuración segmentada:

- Arranca primero los procesadores, la memoria y el sistema operativo

- Retrasa la configuración de PL a una fase posterior

- Proporciona un PDI (archivo de configuración) de PL a través de Linux® o U-Boot en tiempo de ejecución

La configuración segmentada está disponible en la versión 2025.1. Consulta los tutoriales de GitHub para obtener más información.

Recursos

Webinars y videos explicativos

Tutoriales de GitHub

Cursos de capacitación

Documentación

Vivado Design Suite

Descarga la última versión de Vivado Design Suite para acceder a las funciones más recientes

Power Design Manager

Descarga la última versión a fin de garantizar datos de alimentación precisos para dispositivos UltraScale+ y Versal

Comunícate con nosotros

Regístrate para recibir las últimas noticias sobre herramientas de hardware o comunícate con un experto de Vivado Design Suite si tienes preguntas o comentarios

Notas al pie

- Basado en una situación de prueba única realizada por AMD al mes de diciembre del 2024, en la que se midieron los tiempos de compilación promedio (horas/minutos) de más de 124 diseños dirigidos a dispositivos con tecnología de interconexión de silicio apilado (SSI) Versal que utilizaban Vivado Design Suite 2024.2 frente a Vivado Design Suite 2024.1. Los resultados de tiempo de compilación variarán según el dispositivo, el diseño, la configuración y otros factores (VIV-011)

- Basado en una situación de prueba única realizada por AMD al mes de diciembre del 2024, en la que se midieron los tiempos de compilación promedio (horas/minutos) de más de 151 diseños dirigidos a dispositivos monolíticos Versal que utilizaban Vivado Design Suite 2024.2 frente a Vivado Design Suite 2024.1. Los resultados del tiempo de compilación variarán según el dispositivo, el diseño, la configuración y otros factores. (VIV-010)

- Basado en las pruebas de rendimiento del peor margen de demora negativo de AMD en abril del 2025 utilizando Vivado Design Suite 2024.2 frente a 2024.1. Los resultados declarados son un promedio de media geométrica de más de 153 diseños monolíticos. Los resultados pueden variar según el dispositivo, el diseño, la configuración, el software y otros factores (VIV-013)

- Basado en las pruebas de rendimiento del peor margen de demora negativo de AMD en abril del 2025 utilizando Vivado Design Suite 2024.2 frente a 2024.1. Los resultados declarados son un promedio de media geométrica de más de 125 diseños de SSI. Los resultados pueden variar según el dispositivo, el diseño, la configuración, el software y otros factores (VIV-014)

- Basado en una situación de prueba única realizada por AMD al mes de diciembre del 2024, en la que se midieron los tiempos de compilación promedio (horas/minutos) de más de 124 diseños dirigidos a dispositivos con tecnología de interconexión de silicio apilado (SSI) Versal que utilizaban Vivado Design Suite 2024.2 frente a Vivado Design Suite 2024.1. Los resultados de tiempo de compilación variarán según el dispositivo, el diseño, la configuración y otros factores (VIV-011)

- Basado en una situación de prueba única realizada por AMD al mes de diciembre del 2024, en la que se midieron los tiempos de compilación promedio (horas/minutos) de más de 151 diseños dirigidos a dispositivos monolíticos Versal que utilizaban Vivado Design Suite 2024.2 frente a Vivado Design Suite 2024.1. Los resultados del tiempo de compilación variarán según el dispositivo, el diseño, la configuración y otros factores. (VIV-010)

- Basado en las pruebas de rendimiento del peor margen de demora negativo de AMD en abril del 2025 utilizando Vivado Design Suite 2024.2 frente a 2024.1. Los resultados declarados son un promedio de media geométrica de más de 153 diseños monolíticos. Los resultados pueden variar según el dispositivo, el diseño, la configuración, el software y otros factores (VIV-013)

- Basado en las pruebas de rendimiento del peor margen de demora negativo de AMD en abril del 2025 utilizando Vivado Design Suite 2024.2 frente a 2024.1. Los resultados declarados son un promedio de media geométrica de más de 125 diseños de SSI. Los resultados pueden variar según el dispositivo, el diseño, la configuración, el software y otros factores (VIV-014)